Изобретение относится к области радиоэлектроники и может быть использовано в качестве прецизионного устройства усиления широкополосных сигналов.

В современной радиоэлектронной аппаратуре находят применение операционные усилители (ОУ), выполненные на основе входного дифференциального каскада с симметричной активной нагрузкой в виде источников опорного тока [1-9]. Их основное достоинство - повышенный коэффициент усиления по напряжению, который обеспечивается двумя каскадами усиления.

Для работы в условиях космического пространства, в экспериментальной физике необходимы радиационно-стойкие ОУ с несколькими дифференциальными входами, обеспечивающими функциональное преобразование нескольких аналоговых сигналов. Мировой опыт проектирования устройств данного класса показывает, что решение этих задач возможно с использованием биполярно-полевого технологического процесса [10], обеспечивающего формирование р-канальных полевых и высококачественных n-р-n биполярных транзисторов с радиационной стойкостью до 1 Мрад и потоком нейтронов до 1013 н/см2. Однако для таких ОУ необходима специальная схемотехника, учитывающая ограничения биполярно-полевой технологии [10].

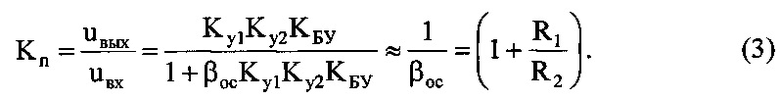

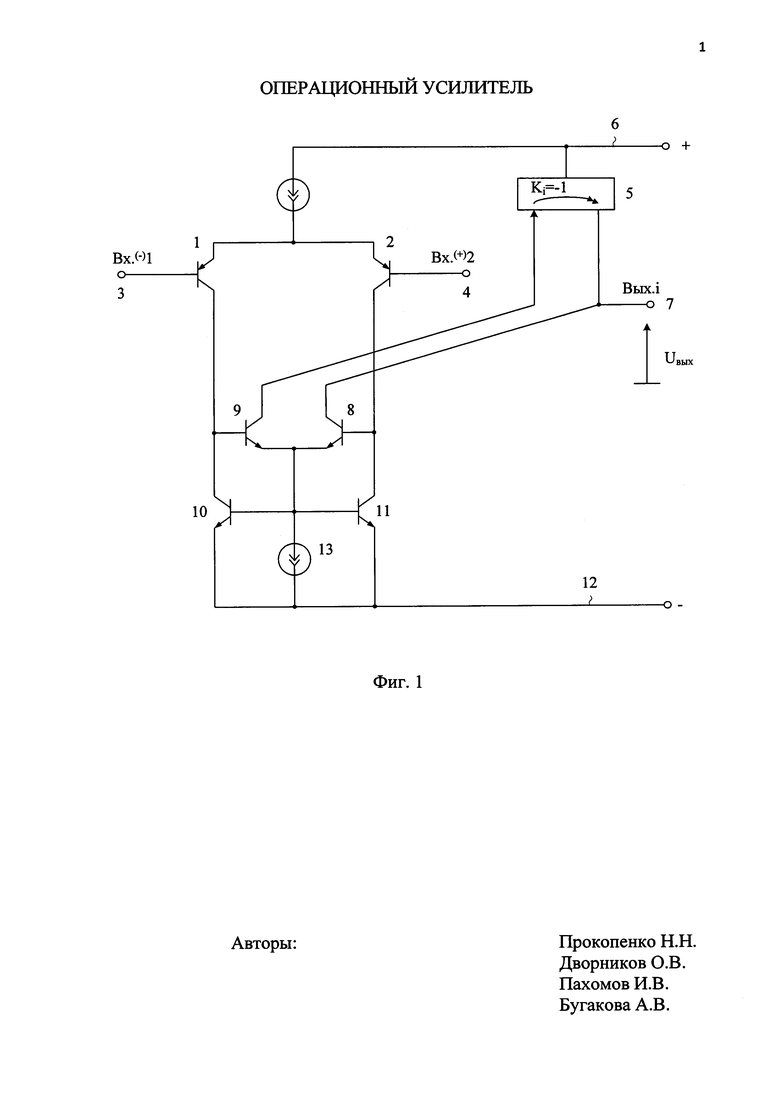

Ближайшим прототипом заявляемого устройства является операционный усилитель по патенту US 3.614.645, fig. 1. Кроме этого, данная архитектура ОУ приведена в патенте 7.411.541, fig. 2, а также в монографии [9]. ОУ-прототип содержит (фиг. 1) первый 1 и второй 2 входные биполярные транзисторы, базы которых связаны с соответствующими первым 3 и вторым 4 входами операционного усилителя, токовое зеркало 5, согласованное с первой 6 шиной источника питания, выход которого связан с токовым выходом операционного усилителя 7 и коллектором первого 8 выходного транзистора, а вход соединен с коллектором второго 9 выходного транзистора, первый 10 вспомогательный транзистор, база которого подключена к базе второго 11 вспомогательного транзистора и соединена с объединенными эмиттерами первого 8 и второго 9 выходных транзисторов, а также подключена ко второй 12 шине источника питания через вспомогательный двухполюсник 13, причем коллектор первого 10 вспомогательного транзистора соединен с базой второго 9 выходного транзистора, коллектор второго 11 вспомогательного транзистора соединен с базой первого 8 выходного транзистора, эмиттеры первого 10 и второго 11 вспомогательных транзисторов связаны со второй 12 шиной источника питания.

Существенный недостаток известного ОУ состоит в том, что в нем не обеспечивается дифференциальное преобразование нескольких входных напряжений. Кроме этого, в известной схеме ОУ для установления статического режима транзисторов входного каскада необходим специальный функциональный узел - источник опорного тока, существенно влияющий на статические параметры устройства. В конечном итоге, это снижает прецизионность известного ОУ.

Основная задача предполагаемого изобретения состоит в создании высокостабильного с несколькими входами симметричного по входам и промежуточному каскаду ОУ, не содержащего классических источников опорного тока, устанавливающих статический режим транзисторов входного и промежуточного каскадов. Это позволяет повысить прецизионность ОУ в условиях дестабилизирующих факторов, а также расширяет его функциональные возможности в сравнении с классическими ОУ.

Поставленная задача достигается тем, что в операционном усилителе фиг. 1, содержащем первый 1 и второй 2 входные биполярные транзисторы, базы которых связаны с соответствующими первым 3 и вторым 4 входами операционного усилителя, токовое зеркало 5, согласованное с первой 6 шиной источника питания, выход которого связан с токовым выходом операционного усилителя 7 и коллектором первого 8 выходного транзистора, а вход соединен с коллектором второго 9 выходного транзистора, первый 10 вспомогательный транзистор, база которого подключена к базе второго 11 вспомогательного транзистора и соединена с объединенными эмиттерами первого 8 и второго 9 выходных транзисторов, а также подключена ко второй 12 шине источника питания через вспомогательный двухполюсник 13, причем коллектор первого 10 вспомогательного транзистора соединен с базой второго 9 выходного транзистора, коллектор второго 11 вспомогательного транзистора соединен с базой первого 8 выходного транзистора, эмиттеры первого 10 и второго 11 вспомогательных транзисторов связаны со второй 12 шиной источника питания, предусмотрены новые элементы и связи - в схему введены первый 14 и второй 15 дополнительные полевые транзисторы с управляющим pn-переходом, исток первого 14 дополнительного полевого транзистора соединен с эмиттером первого 1 входного биполярного транзистора, исток второго 15 дополнительного полевого транзистора соединен с эмиттером второго 2 входного биполярного транзистора, затвор первого 14 дополнительного полевого транзистора соединен с первым 16 дополнительным входом операционного усилителя, затвор второго 15 дополнительного полевого транзистора соединен со вторым 17 дополнительным входом операционного усилителя, сток первого 14 дополнительного полевого транзистора соединен с базой второго 9 выходного транзистора, сток второго 15 дополнительного полевого транзистора соединен с базой первого 8 выходного транзистора, причем тип проводимости первого 1 и второго 2 входных биполярных транзисторов соответствует типу проводимости первого 8 и второго 9 выходных транзисторов, а коллекторы первого 1 и второго 2 входных биполярных транзисторов связаны с первой 6 шиной источника питания.

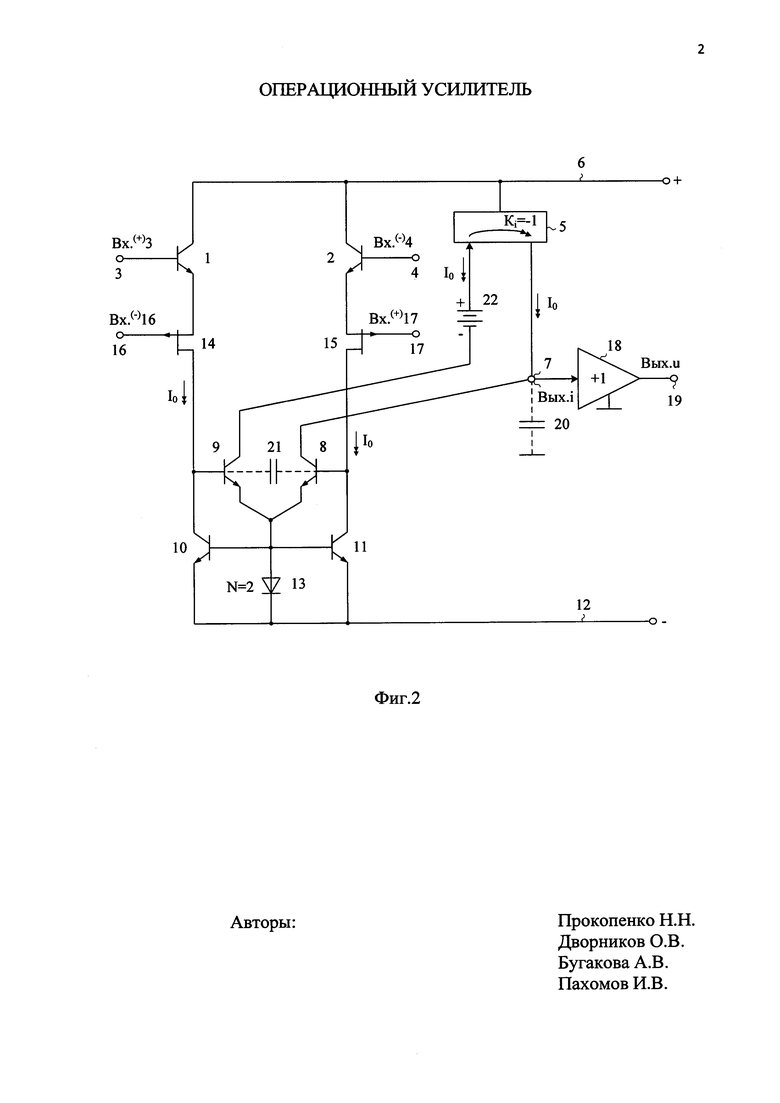

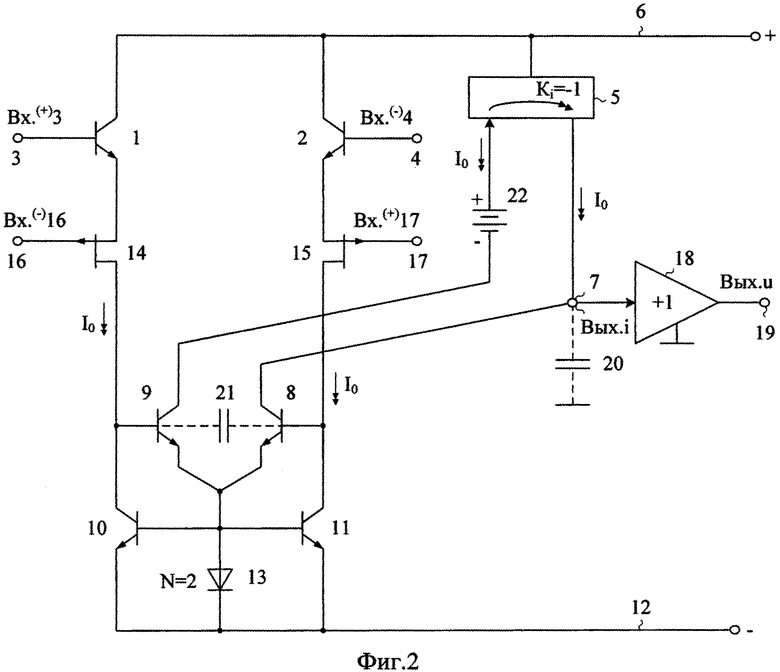

На чертеже фиг. 1 показана схема ОУ-прототипа, а на чертеже фиг. 2 - схема заявляемого устройства в соответствии с п. 1 и п. 2 формулы изобретения.

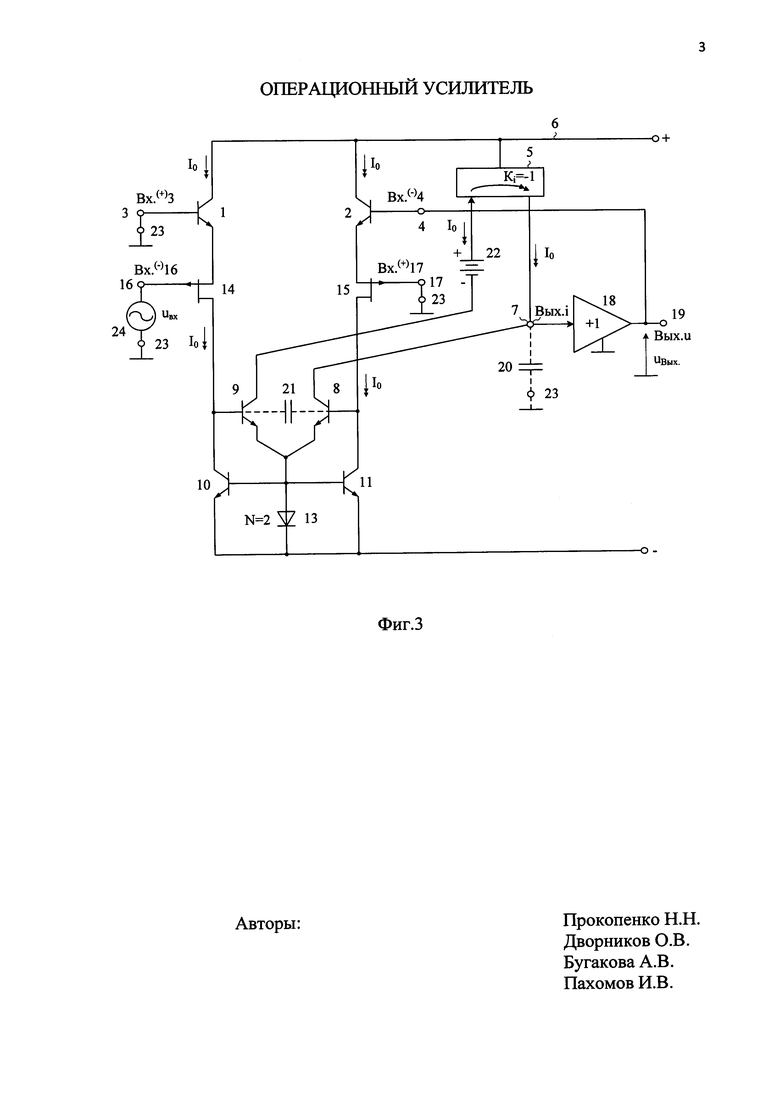

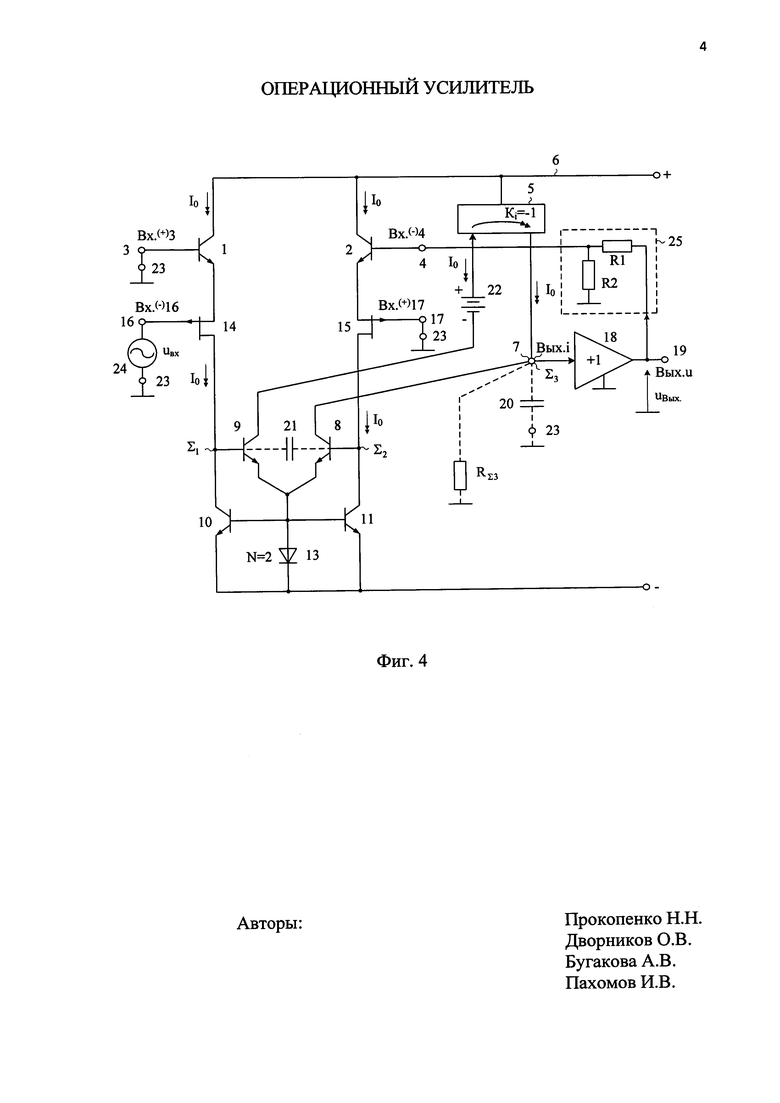

На чертеже фиг. 3 приведена схема заявляемого устройства в соответствии с п. 3, а на чертеже фиг. 4 - п. 4 формулы изобретения.

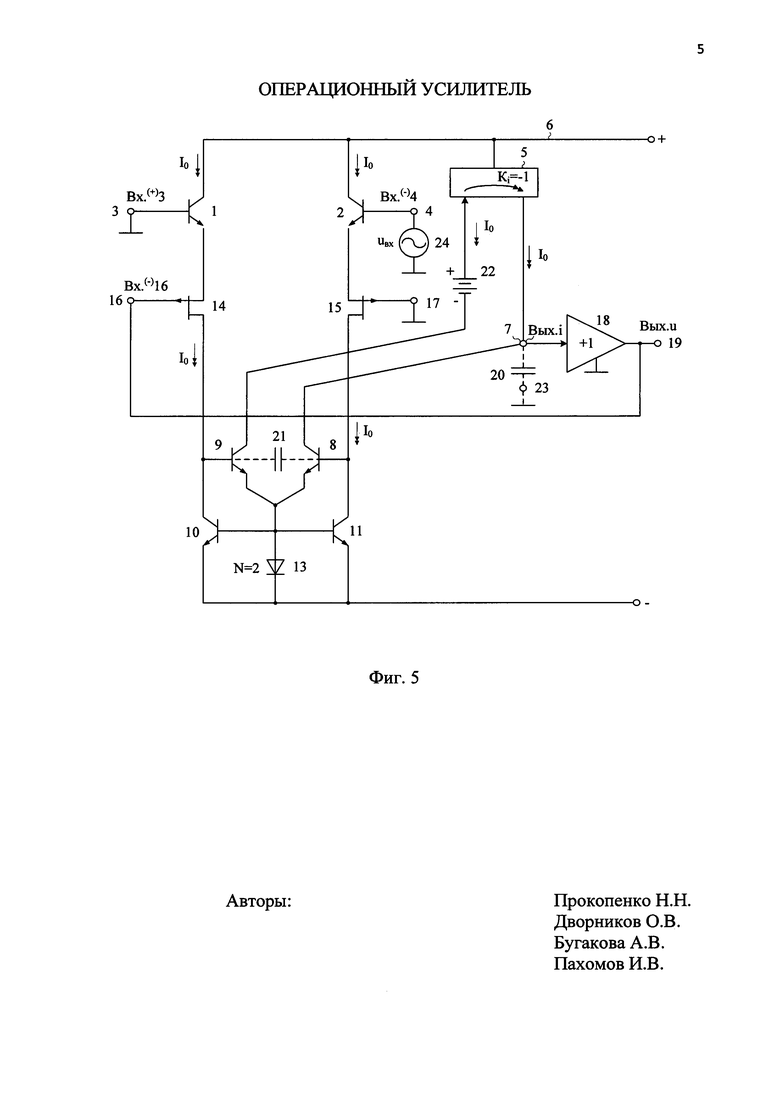

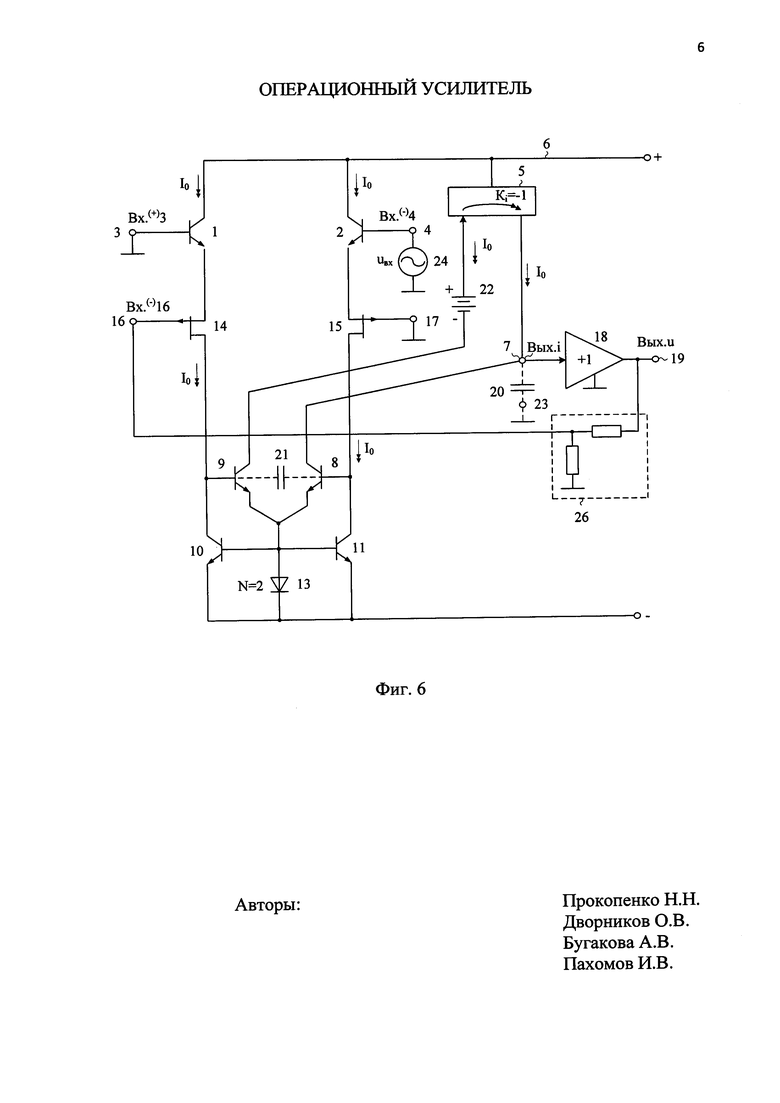

На чертеже фиг. 5 представлена схема заявляемого устройства в соответствии с п. 5, а на чертеже фиг. 6 в соответствии с п. 6 формулы изобретения.

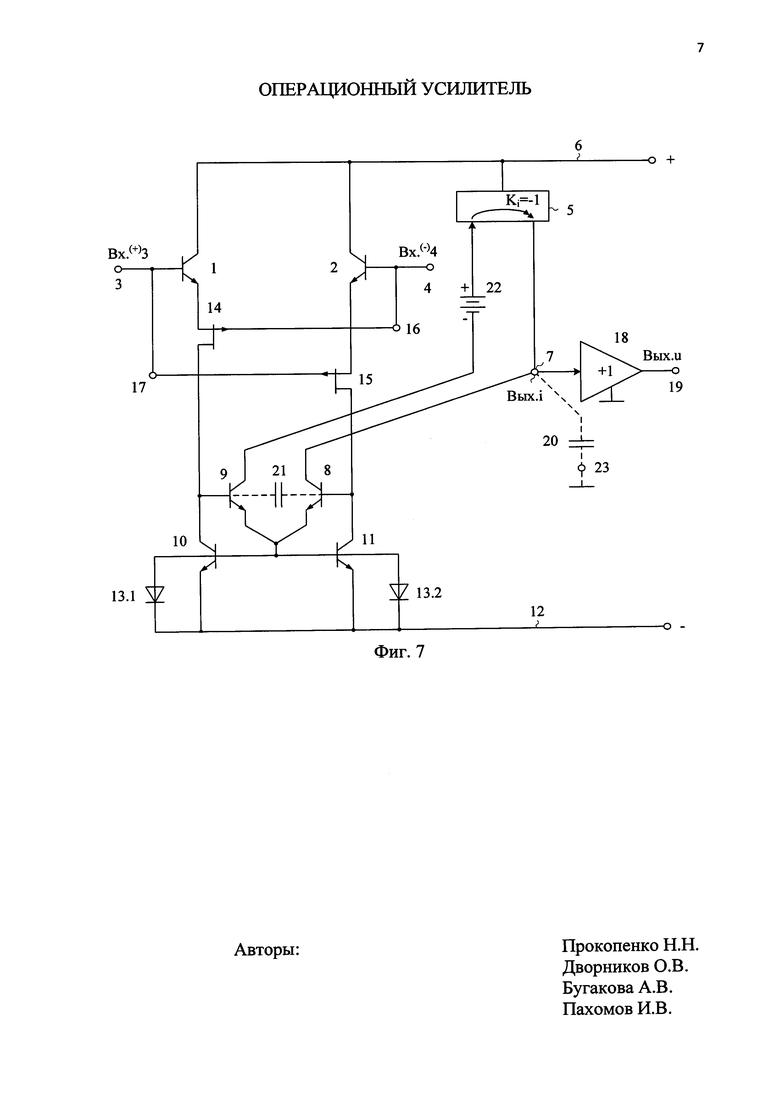

На чертеже фиг. 7 представлена схема заявляемого устройства в соответствии с п. 7 формулы изобретения.

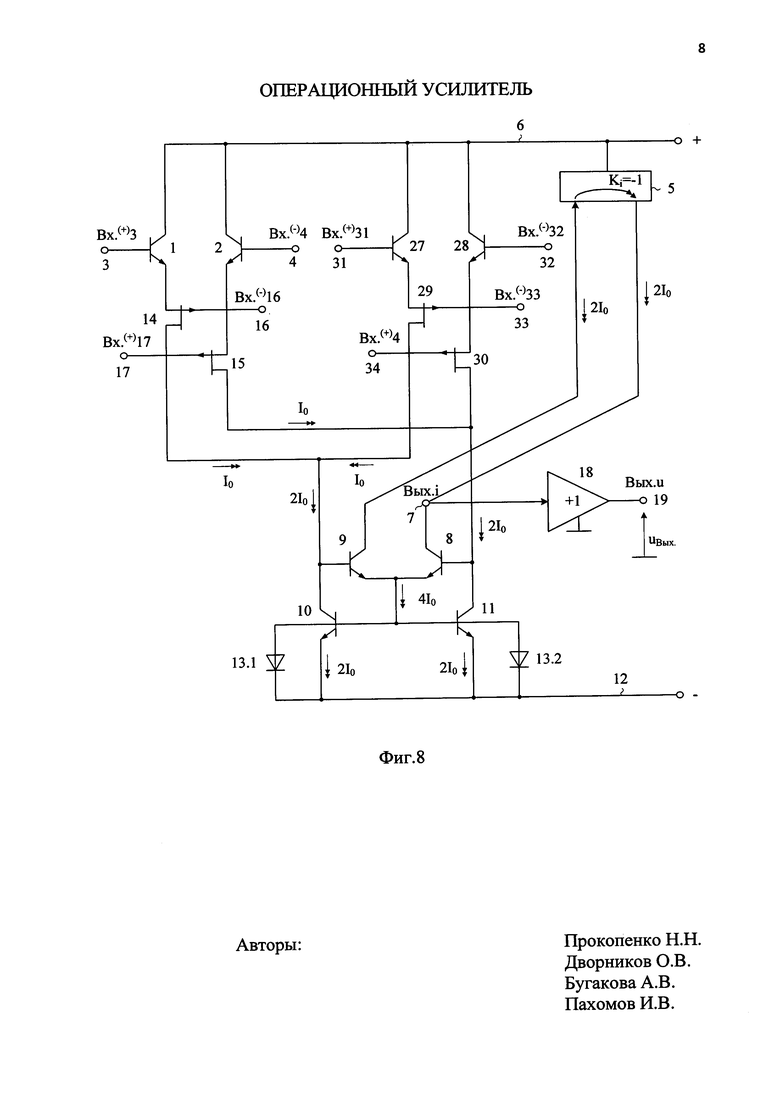

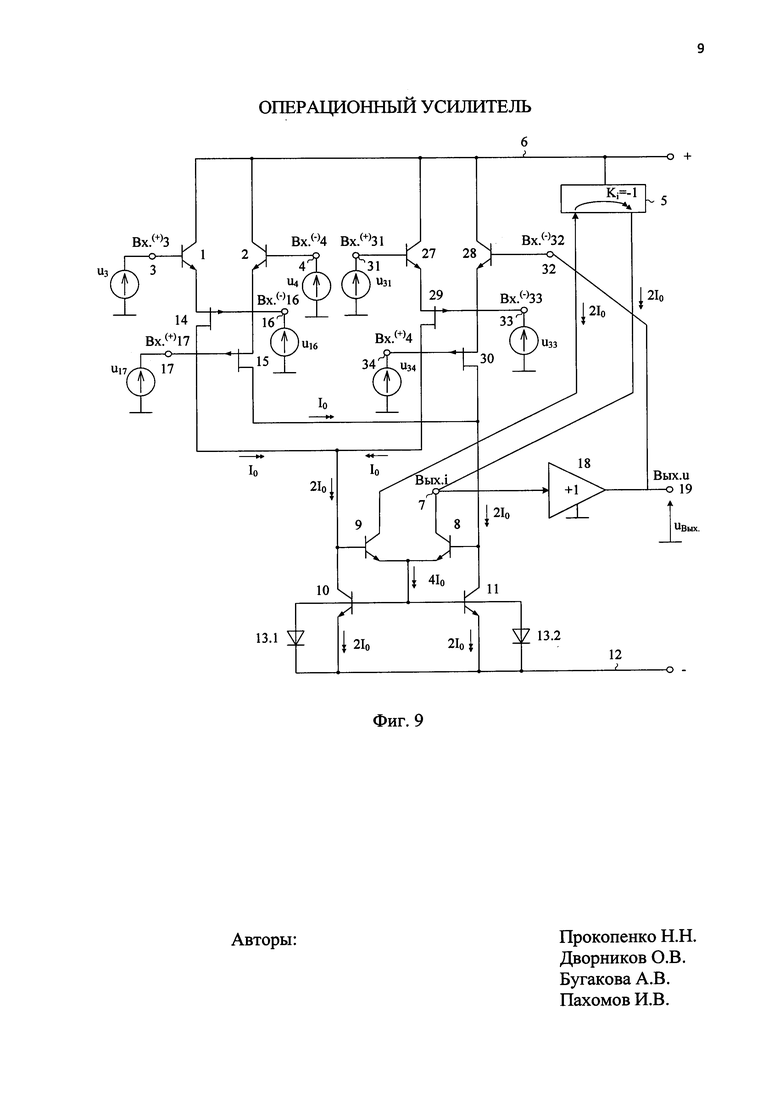

На чертеже фиг. 8 приведена схема заявляемого устройства в соответствии с п. 8, а на чертеже фиг. 9 в соответствии с п. 9 формулы изобретения.

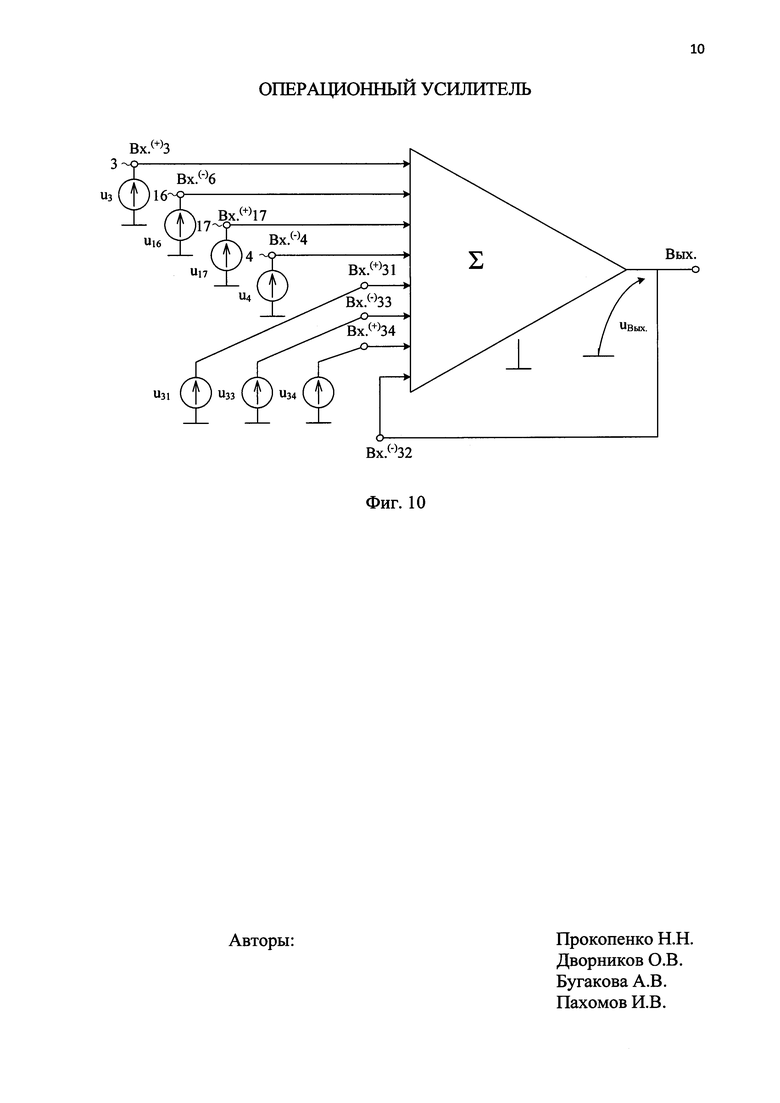

На чертеже фиг. 10 представлена функциональная схема заявляемого устройства фиг. 9.

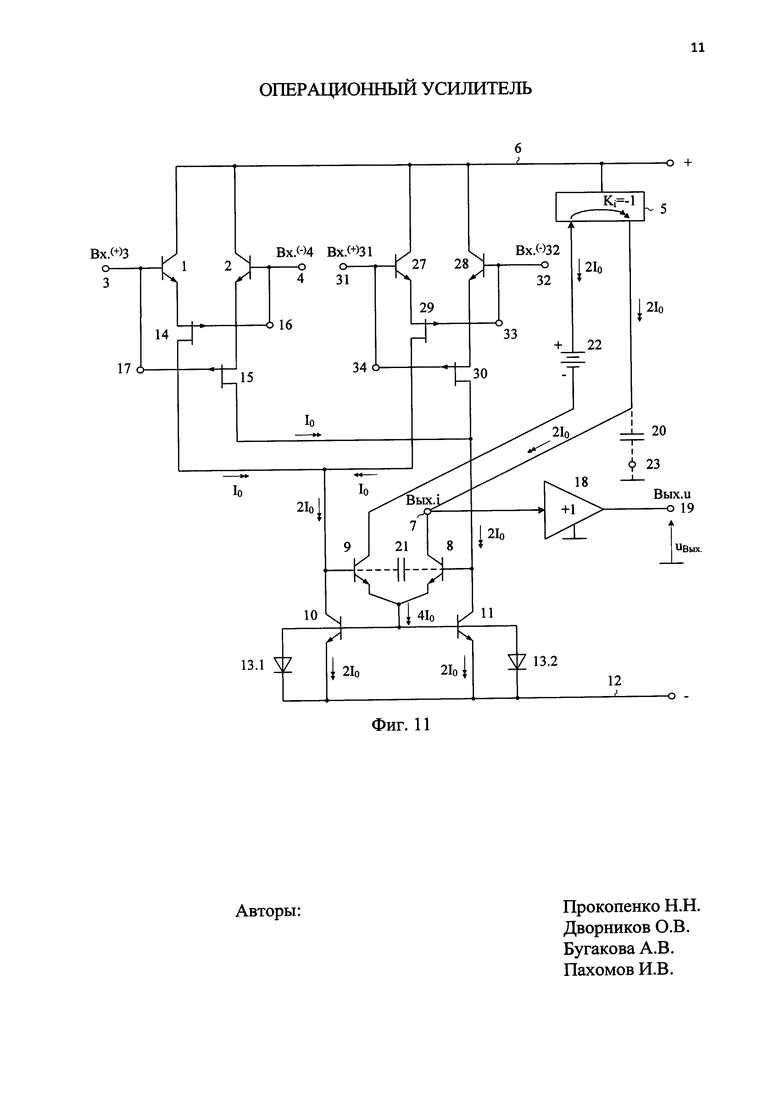

На чертеже фиг. 11 представлена схема заявляемого устройства в соответствии с п. 10 формулы изобретения.

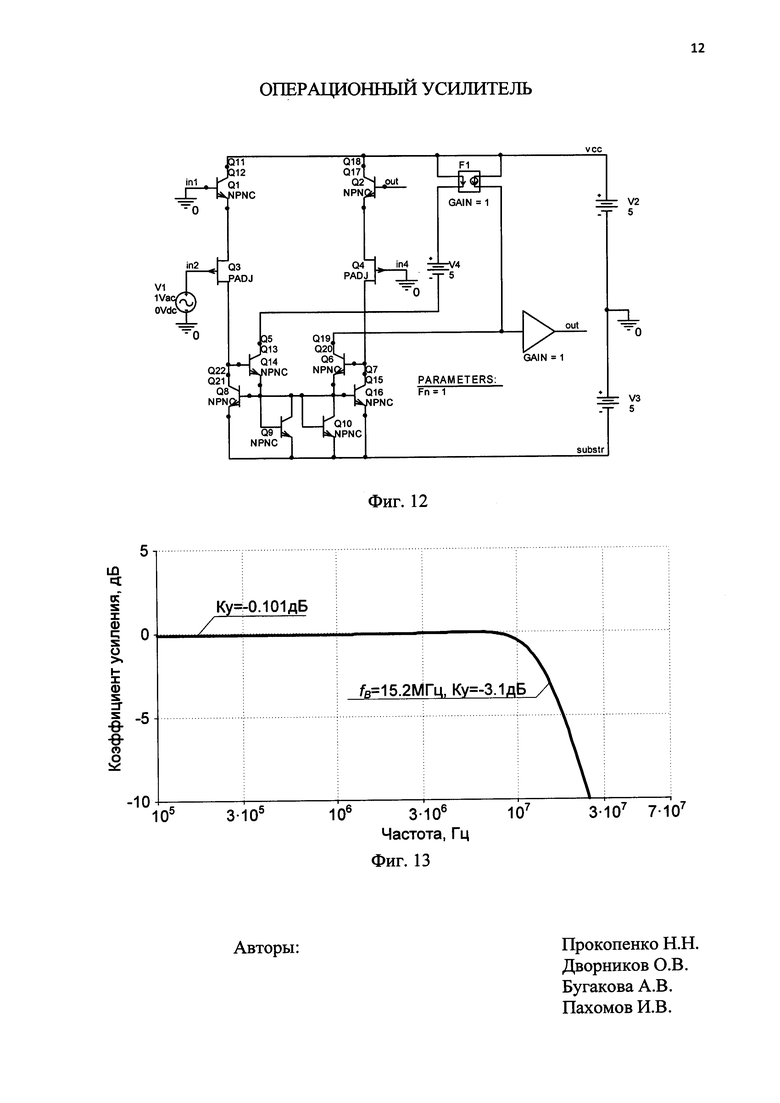

На чертеже фиг. 12 приведена схема заявляемого устройства фиг. 3 в режиме инвертирующего усилителя в среде PSpice на радиационно-зависимых моделях интегральных транзисторов АБМК_1_4 НПО «Интеграл» (г. Минск), которая использовалась для моделирования амплитудно-частотных характеристик ОУ со 100% обратной связью. Из этой характеристики, а также анализа фазовых соотношений в схеме следует, что коэффициент усиления по напряжению ОУ фиг. 12 равен минус единице.

На чертеже фиг. 13 показаны амплитудно-частотные характеристики операционного усилителя фиг. 12 со 100% отрицательной обратной связью.

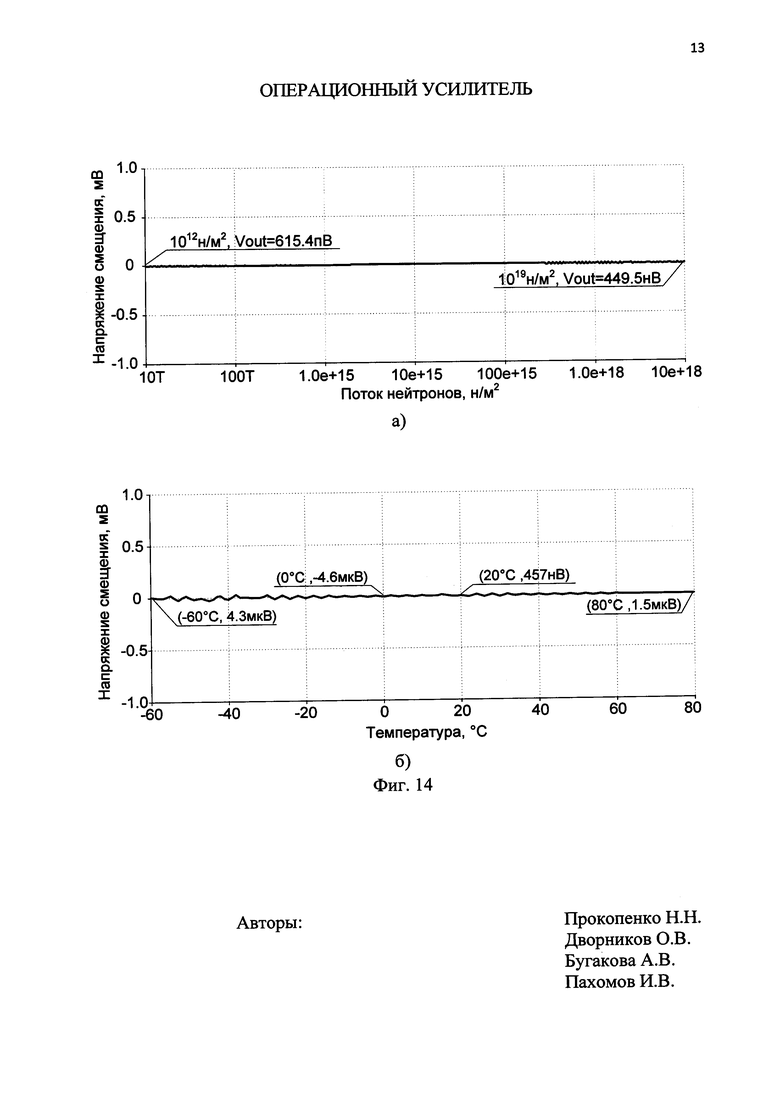

На чертеже фиг. 14 приведена зависимость напряжения смещения нуля ОУ фиг. 12 от потока нейтронов (а) и температуры в диапазоне минус 60-80°С (б). Данные характеристики получены для случая, когда элементы схемы обладают высокой идентичностью, т.е. данные графики показывают предельные возможности заявляемого ОУ.

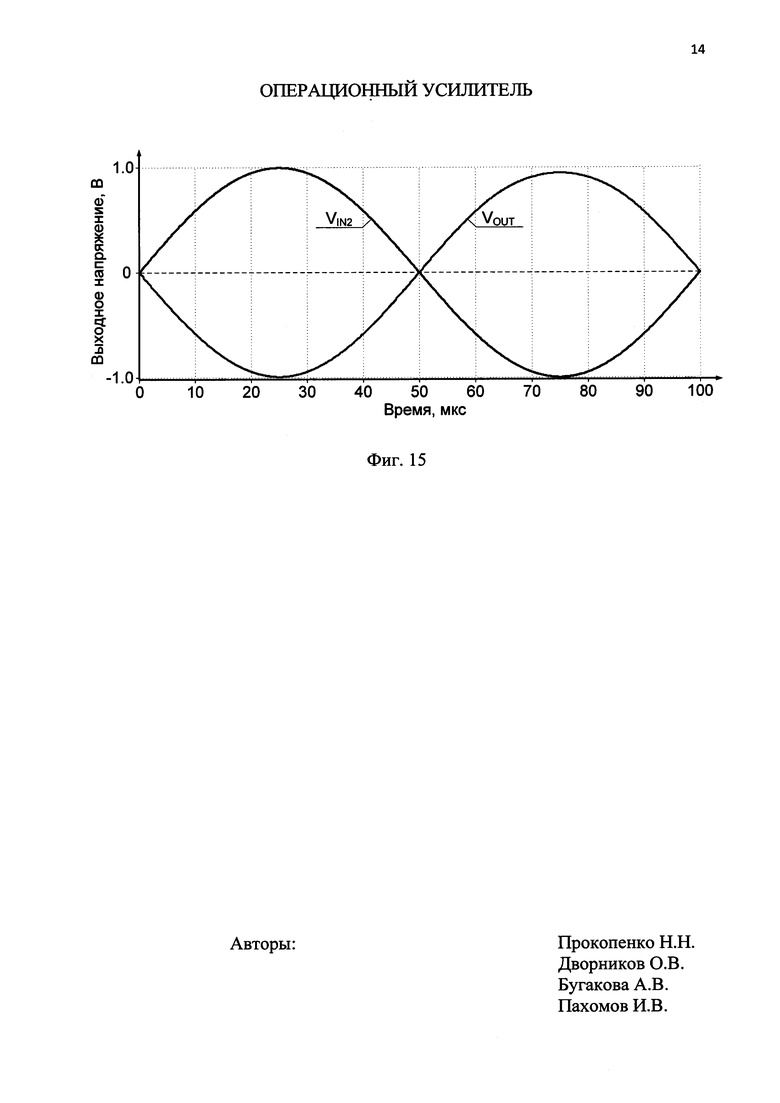

На чертеже фиг. 15 приведены временные характеристики входного и выходного синусоидального напряжения схемы фиг. 12, которые показывают, что выходное напряжение заявляемого устройства противофазно его входному напряжению.

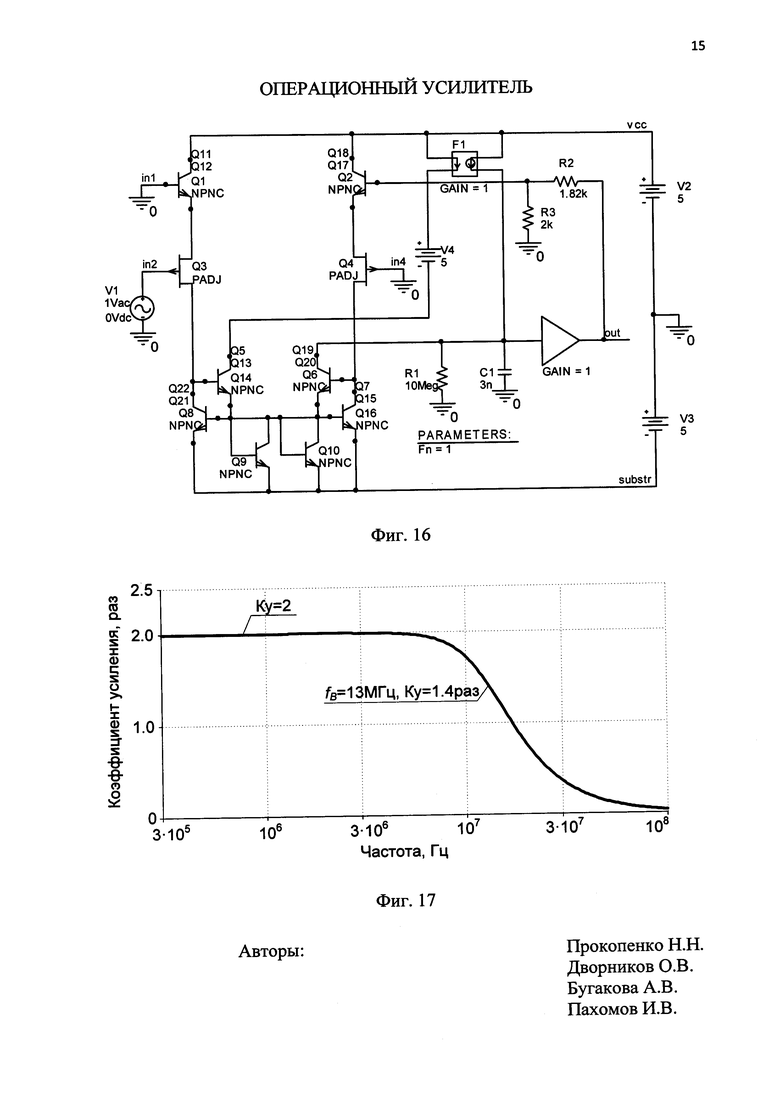

На чертеже фиг. 16 приведена схема заявляемого устройства фиг. 4 в среде PSpice на радиационно-зависимых моделях интегральных транзисторов АБМК_1_4 НПО «Интеграл» (г. Минск).

На чертеже фиг. 17 показаны амплитудно-частотные характеристики операционного усилителя фиг. 16 для случая, когда коэффициент передачи четырехполюсника обратной связи 26 равен 0,5, а его коэффициент усиления в данной схеме включения Kу=-2.

На чертеже фиг. 18 приведена схема заявляемого устройства фиг. 2 в среде PSpice на радиационно-зависимых моделях интегральных транзисторов АБМК_1_4 НПО «Интеграл» (г. Минск) для случая, когда входной сигнал подается на первый 16 дополнительный вход ОУ, а общая обратная связь отсутствует.

На чертеже фиг. 19 показаны амплитудно-частотные характеристики разомкнутого операционного усилителя фиг. 18 (без отрицательной обратной связи).

Операционный усилитель фиг. 2 содержит первый 1 и второй 2 входные биполярные транзисторы, базы которых связаны с соответствующими первым 3 и вторым 4 входами операционного усилителя, токовое зеркало 5, согласованное с первой 6 шиной источника питания, выход которого связан с токовым выходом операционного усилителя 7 и коллектором первого 8 выходного транзистора, а вход соединен с коллектором второго 9 выходного транзистора, первый 10 вспомогательный транзистор, база которого подключена к базе второго 11 вспомогательного транзистора и соединена с объединенными эмиттерами первого 8 и второго 9 выходных транзисторов, а также подключена ко второй 12 шине источника питания через вспомогательный двухполюсник 13, причем коллектор первого 10 вспомогательного транзистора соединен с базой второго 9 выходного транзистора, коллектор второго 11 вспомогательного транзистора соединен с базой первого 8 выходного транзистора, эмиттеры первого 10 и второго 11 вспомогательных транзисторов связаны со второй 12 шиной источника питания. В схему введены первый 14 и второй 15 дополнительные полевые транзисторы с управляющим pn-переходом, исток первого 14 дополнительного полевого транзистора соединен с эмиттером первого 1 входного биполярного транзистора, исток второго 15 дополнительного полевого транзистора соединен с эмиттером второго 2 входного биполярного транзистора, затвор первого 14 дополнительного полевого транзистора соединен с первым 16 дополнительным входом операционного усилителя, затвор второго 15 дополнительного полевого транзистора соединен со вторым 17 дополнительным входом операционного усилителя, сток первого 14 дополнительного полевого транзистора соединен с базой второго 9 выходного транзистора, сток второго 15 дополнительного полевого транзистора соединен с базой первого 8 выходного транзистора, причем тип проводимости первого 1 и второго 2 входных биполярных транзисторов соответствует типу проводимости первого 8 и второго 9 выходных транзисторов, а коллекторы первого 1 и второго 2 входных биполярных транзисторов связаны с первой 6 шиной источника питания.

Коррекция амплитудно-частотной характеристики ОУ фиг. 2 может обеспечиваться корректирующими конденсаторами 20 или 21. Для уменьшения влияния напряжения Эрли первого 8 и второго 9 выходных транзисторов на напряжение смещения нуля ОУ предусмотрена цепь смещения 22, которая может быть выполнена в виде стабилитрона, резистора или нескольких прямосмещенных р-n переходов. Вспомогательный двухполюсник 13 выполнен на чертеже фиг. 2 в виде двух параллельно включенных р-n переходов (N=2).

На чертеже фиг. 2, в соответствии с п. 2 формулы изобретения, к токовому выходу операционного усилителя 7 подключен вход дополнительного буферного усилителя 18, выход которого 19 является потенциальным выходом операционного усилителя.

На чертеже фиг. 3, в соответствии с п. 3 формулы изобретения потенциальный выход операционного усилителя 19 связан со вторым 4 входом операционного усилителя, первый 3 вход операционного усилителя и второй 17 дополнительный вход операционного усилителя соединены с общей шиной 23 источников питания, а первый 16 дополнительный вход операционного усилителя является первым инвертирующим входом операционного усилителя. Кроме этого, на чертеже фиг. 3 предусмотрена общая шина источников питания 23, относительно которой подается входное 24 и снимается выходное 19 напряжения ОУ.

На чертеже фиг. 4, в соответствии с п. 4 формулы изобретения, потенциальный выход операционного усилителя 19 связан со вторым 4 входом операционного усилителя через первый 25 четырехполюсник обратной связи, который выполнен в частном случае на основе резисторов R1 и R2.

На чертеже фиг. 5, в соответствии с п. 5 формулы изобретения, потенциальный выход операционного усилителя 19 связан с первым 16 дополнительным входом операционного усилителя, первый 3 вход операционного усилителя и второй 17 дополнительный вход операционного усилителя связаны с общей шиной 23 источника питания, а второй 4 вход операционного усилителя является вторым инвертирующим входом операционного усилителя.

На чертеже фиг. 6, в соответствии с п. 6 формулы изобретения, потенциальный выход операционного усилителя 19 связан с первым 16 дополнительным входом операционного усилителя через второй 26 четырехполюсник обратной связи.

На чертеже фиг. 7, в соответствии с п. 7 формулы изобретения, первый 16 дополнительный вход операционного усилителя соединен со вторым 4 входом операционного усилителя, а второй 17 дополнительный вход операционного усилителя подключен в первому 3 входу операционного усилителя.

На чертежах фиг. 7, фиг. 8, фиг. 9, фиг. 11 вспомогательный двухполюсник 13 выполнен в виде двух параллельно включенных р-n переходов 13.1 и 13.2.

На чертеже фиг. 8, в соответствии с п. 8 формулы изобретения, в схему введены первый 27 и второй 28 дополнительные биполярные транзисторы, а также третий 29 и четвертый 30 дополнительные полевые транзисторы, база первого 27 дополнительного биполярного транзистора связана с третьим 31 дополнительным входом операционного усилителя, база второго 28 дополнительного биполярного транзистора связана с четвертым 32 дополнительным входом операционного усилителя, затвор третьего 29 дополнительного полевого транзистора связан с пятым 33 дополнительным входом операционного усилителя, затвор четвертого 30 дополнительного полевого транзистора связан с шестым 34 дополнительным входом операционного усилителя, коллекторы первого 27 и второго 28 дополнительных биполярных транзисторов подключены к первой 6 шине источника питания, эмиттер первого 27 дополнительного биполярного транзистора связан с истоком первого 29 дополнительного полевого транзистора, эмиттер второго 28 дополнительного биполярного транзистора связан с истоком четвертого 30 дополнительного полевого транзистора, сток третьего 29 дополнительного полевого транзистора подключен к базе второго 9 выходного транзистора, сток четвертого 30 дополнительного полевого транзистора подключен к базе первого 8 выходного транзистора.

На чертеже фиг. 9, в соответствии с п. 9 формулы изобретения, потенциальный выход операционного усилителя 19 связан с четвертым 32 дополнительным входом операционного усилителя.

На чертеже фиг. 10 представлена функциональная схема ОУ фиг. 9 и показаны его входные и выходные сигналы.

На чертеже фиг. 11, в соответствии с п. 10 формулы изобретения, первый 16 дополнительный вход операционного усилителя соединен со вторым 4 входом операционного усилителя, второй 17 дополнительный вход операционного усилителя связан с первым 3 входом операционного усилителя, шестой 34 дополнительный вход операционного усилителя связан с третьим 31 дополнительным входом операционного усилителя, пятый 33 дополнительный вход операционного усилителя соединен с четвертым 32 дополнительным входом операционного усилителя.

Рассмотрим работу ОУ фиг. 4, который в данной схеме включения является инвертирующим усилителем с высоким входным сопротивлением по первому 16 дополнительному входу. Это одна из существенных особенностей заявляемого устройства.

Статический режим транзисторов схемы фиг. 4 устанавливается за счет соответствующего выбора геометрических размеров и топологии первого 14 и второго 15 дополнительных полевых транзисторов. Ток стока первого 14 и второго 15 дополнительных полевых транзисторов Ic14=Ic15=I0 определяется по их стоко-затворной характеристике при напряжении затвор-исток, равном напряжению эмиттер-база (Uэб≈0,7 В) первого 1 и второго 2 входных биполярных транзисторов. Таким образом, для обеспечения статического режима в схеме фиг. 4 не требуются какие-либо другие источники опорного тока. В этом состоит одна из ее замечательных особенностей.

Токи стоков первого 14 и второго 15 дополнительных полевых транзисторов Ic14=Ic15=I0 определяют статический режим первого 10 и второго 11 вспомогательных транзисторов за счет местной отрицательной обратной связи по синфазному сигналу (первый 8 и второй 9 выходные транзисторы). Если в качестве вспомогательного двухполюсника 13 использовать два параллельно включенных р-n перехода, идентичных эмиттерным р-n переходам первого 10 и второго 11 вспомогательных транзисторов, то коллекторные токи первого 8 и второго 9 выходных транзисторов будут соответствовать току I0, который определяется геометрией первого 14 и второго 15 дополнительных полевых транзисторов. Таким образом, промежуточный каскад ОУ также не требует использования каких-либо традиционных источников опорного тока.

Дополнительный источник напряжения 22 (резистор, р-n переходы и т.п.) включен для согласования статических режимов первого 8 и второго 9 выходных транзисторов по напряжению коллектор-база. Его применение позволяет уменьшить влияние эффекта Эрли первого 8 и второго 9 выходных транзисторов на напряжение смещения нуля ОУ (Uсм).

Рассмотрим далее зависимость коэффициента передачи по напряжению схемы фиг. 4 от параметров элементов.

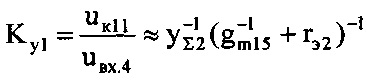

Усиление по петле отрицательной обратной связи ОУ фиг. 4 при единичном коэффициенте передачи токового зеркала 5 определяется формулой

где  ,

,

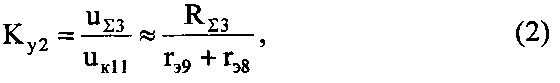

- коэффициент передачи четырехполюсника отрицательной обратной связи 25;

- коэффициент передачи четырехполюсника отрицательной обратной связи 25;

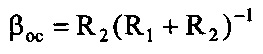

- коэффициенты передачи по напряжению первого, второго и третьего каскадов ОУ;

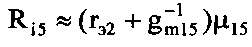

- коэффициенты передачи по напряжению первого, второго и третьего каскадов ОУ;

gm15 - крутизна стоко-затворной характеристики полевого транзистора 15;

RΣ3 - эквивалентное сопротивление в высокоимпедансном узле Σ3;

rэi - сопротивление прямосмещенного эмиттерного р-n перехода i-го транзистора.

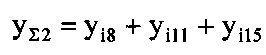

При этом в формуле (2) эквивалентная проводимость в высокоимпедансном узле Σ2:

,

,

где yi8 - входная проводимость транзистора 8 по цепи базы,

yi11 - выходная проводимость транзистора 11 по цепи коллектора,

yi15 - выходная проводимость транзистора 15 по цепи стока.

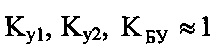

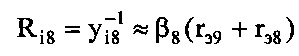

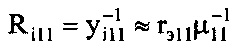

Причем

,

,

,

,

,

,

где μi - коэффициент внутренней обратной связи i-го транзистора в схеме с общей базой 11 (общим затвором, 15).

В результате анализа схемы фиг. 4 (с учетом ее высокой симметрии) можно найти, что при Т>>1 модуль коэффициента передачи по напряжению ОУ

При этом усилитель фиг. 4 является инвертирующим, а его коэффициент передачи по напряжению определяется отношением резисторов R1 и R2 (3).

При 100% отрицательной обратной связи схема фиг. 4 является инвертирующим повторителем входного напряжения с Kу≈-1.

Если входной сигнал подать на первый 3 вход или на второй 17 дополнительный вход, а первый 16 дополнительный вход подключить к общей шине, то в схеме фиг. 4 реализуется неинвертирующее усиление входного сигнала с коэффициентом передачи, который определяется формулой (3).

Аналогичными свойствами обладают и схемы ОУ фиг. 5 и фиг. 6.

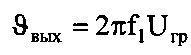

Особенность схемы фиг. 7 состоит в том, что она может иметь повышенное быстродействие в связи с тем, что ее входной каскад характеризуется более широким диапазоном активной работы (напряжение ограничения Uгр). Это связано с тем, что максимальная скорость нарастания выходного напряжения ОУ с однополюсной частотной коррекцией (С21) определяется формулой

,

,

где f1 - частота единичного усиления ОУ.

В схеме фиг. 8 введен второй многоканальный входной дифференциальный каскад на транзисторах 27, 28, 29 и 30. Общее число входов в таком ОУ возрастает до восьми, что позволяет обеспечить преобразование (алгебраическое суммирование и т.п.), как минимум, семи разных входных сигналов (фиг. 10).

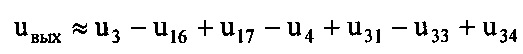

Так, выходное напряжение в схеме фиг. 9 при достаточно большом петлевом усилении Т>>1 можно найти по формуле

,

,

где uij - напряжение на ij-том входе ОУ.

В схеме фиг. 11 два входных дифференциальных каскада реализованы соответственно на транзисторах 1, 2, 14, 15 и 27, 28, 29, 30 с расширенным диапазоном активной работы. Данная схема ОУ имеет только 4 входа, но характеризуется повышенным быстродействием и при однополюсной частотной коррекции (С21).

Представленная на чертеже фиг. 13 амплитудно-частотная характеристика коэффициента усиления по напряжения замкнутого ОУ фиг. 12 показывает, что схема фиг. 12 является инвертирующим усилителем с коэффициентом передачи минус единица, а также характеризуется повышенным входным сопротивлением, которое определяется свойствами полевого транзистора Q3 по цепи затвора.

Предлагаемые схемотехнические решения имеют малые значения систематической составляющей напряжения смещения нуля при температурных и радиационных воздействиях (фиг. 14).

Амплитудно-частотная характеристика фиг. 17 ОУ фиг. 16 показывает, что за счет изменения резисторов обратной связи R2, R3 можно обеспечить инвертирующий коэффициент усиления Kу=-2 при высоком входном сопротивления по цепи затвора транзистора Q3. Петлевое усиление в заявляемом ОУ обеспечивается двумя каскадами усиления и принимает значения в диапазоне 80 дБ (фиг. 19), что достаточно для многих применений.

Таким образом, предлагаемое устройство имеет существенные преимущества в сравнении с известными и может найти широкое применение в широкополосных системах обработки различных сигналов.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент US 7.411.451, fig. 2

2. Патент US 4.607.232

3. Патент US 3.614.645, fig. 1, fig. 2

4. Патент US 5.963.085, fig. 3

5. Патент US 4.271.394, fig. 3

6. Патент US 4.069.460, fig. 1

7. Патент US 4.359.693, fig. 1

8. Патент US 4.348.602, fig. 1

9. Операционные усилители / И. Достал; Москва : Пер. с англ., Мир, 1982. - 512 с. (рис. 13.13б, стр. 77)

10. Элементная база радиационно-стойких информационно-измерительных систем : монография / Н.Н. Прокопенко, О.В. Дворников, С.Г. Крутчинский; под общ. ред. д.т.н., проф. Н.Н. Прокопенко; ФГБОУ ВПО «Южно-Рос. гос. ун-т. экономики и сервиса». - Шахты : ФГБОУ ВПО «ЮРГУЭС», 2011. - 208 с.

| название | год | авторы | номер документа |

|---|---|---|---|

| Операционный усилитель на основе широкозонных полупроводников | 2023 |

|

RU2822157C1 |

| Арсенид-галлиевый операционный усилитель с повышенным коэффициентом усиления и малым уровнем систематической составляющей напряжения смещения нуля | 2023 |

|

RU2820562C1 |

| Арсенид-галлиевый операционный усилитель с малым напряжением смещения нуля | 2023 |

|

RU2812914C1 |

| ПРЕЦИЗИОННЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ ДЛЯ РАДИАЦИОННО-СТОЙКОГО БИПОЛЯРНО-ПОЛЕВОГО ТЕХНОЛОГИЧЕСКОГО ПРОЦЕССА | 2014 |

|

RU2571569C1 |

| РАДИАЦИОННО-СТОЙКИЙ МУЛЬТИДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ ДЛЯ РАБОТЫ ПРИ НИЗКИХ ТЕМПЕРАТУРАХ | 2016 |

|

RU2628131C1 |

| Прецизионный арсенид-галлиевый операционный усилитель с малым уровнем систематической составляющей напряжения смещения нуля и повышенным коэффициентом усиления | 2023 |

|

RU2813370C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ ПИТАНИЯ | 2015 |

|

RU2613842C1 |

| Арсенид-галлиевый операционный усилитель для работы в широком диапазоне температур | 2023 |

|

RU2814685C1 |

| Арсенид-галлиевый операционный усилитель на основе "перегнутого" каскода | 2023 |

|

RU2820341C1 |

| ПРЕЦИЗИОННЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ РАДИАЦИОННО СТОЙКОГО БИПОЛЯРНО-ПОЛЕВОГО ТЕХНОЛОГИЧЕСКОГО ПРОЦЕССА | 2014 |

|

RU2568384C1 |

Изобретение относится к области радиоэлектроники и может быть использовано в качестве прецизионного устройства усиления широкополосных сигналов. Технический результат заключается в повышении прецизионности операционного усилителя в условиях дестабилизирующих факторов. Операционный усилитель содержит первый и второй входные биполярные транзисторы, базы которых связаны с соответствующими первым и вторым входами операционного усилителя, токовое зеркало согласовано с первой шиной источника питания, выход которого связан с токовым выходом операционного усилителя и коллектором первого выходного транзистора. Коллектор второго вспомогательного транзистора соединен с базой первого выходного транзистора, эмиттеры первого и второго вспомогательных транзисторов связаны со второй шиной источника питания, первый и второй дополнительные полевые транзисторы с управляющим pn-переходом, а коллекторы первого и второго входных биполярных транзисторов связаны с первой шиной источника питания. 9 з.п. ф-лы, 17 ил.

1. Операционный усилитель, содержащий первый (1) и второй (2) входные биполярные транзисторы, базы которых связаны с соответствующими первым (3) и вторым (4) входами операционного усилителя, токовое зеркало (5) согласовано с первой (6) шиной источника питания, выход которого связан с токовым выходом операционного усилителя (7) и коллектором первого (8) выходного транзистора, а вход соединен с коллектором второго (9) выходного транзистора, первый (10) вспомогательный транзистор, база которого подключена к базе второго (11) вспомогательного транзистора и соединена с объединенными эмиттерами первого (8) и второго (9) выходных транзисторов, а также подключена ко второй (12) шине источника питания через вспомогательный двухполюсник (13), причем коллектор первого (10) вспомогательного транзистора соединен с базой второго (9) выходного транзистора, коллектор второго (11) вспомогательного транзистора соединен с базой первого (8) выходного транзистора, эмиттеры первого (10) и второго (11) вспомогательных транзисторов связаны со второй (12) шиной источника питания, отличающийся тем, что в схему введены первый (14) и второй (15) дополнительные полевые транзисторы с управляющим pn-переходом, исток первого (14) дополнительного полевого транзистора соединен с эмиттером первого (1) входного биполярного транзистора, исток второго (15) дополнительного полевого транзистора соединен с эмиттером второго (2) входного биполярного транзистора, затвор первого (14) дополнительного полевого транзистора соединен с первым (16) дополнительным входом операционного усилителя, затвор второго (15) дополнительного полевого транзистора соединен со вторым (17) дополнительным входом операционного усилителя, сток первого (14) дополнительного полевого транзистора соединен с базой второго (9) выходного транзистора, сток второго (15) дополнительного полевого транзистора соединен с базой первого (8) выходного транзистора, причем тип проводимости первого (1) и второго (2) входных биполярных транзисторов соответствует типу проводимости первого (8) и второго (9) выходных транзисторов, а коллекторы первого (1) и второго (2) входных биполярных транзисторов связаны с первой (6) шиной источника питания.

2. Операционный усилитель по п. 1, отличающийся тем, что к токовому выходу операционного усилителя (7) подключен вход дополнительного буферного усилителя (18), выход которого (19) является потенциальным выходом операционного усилителя.

3. Операционный усилитель по п. 2, отличающийся тем, что потенциальный выход операционного усилителя (19) связан со вторым (4) входом операционного усилителя, первый (3) вход операционного усилителя и второй (17) дополнительный вход операционного усилителя соединены с общей шиной (23) источников питания, а первый (16) дополнительный вход операционного усилителя является первым инвертирующим входом операционного усилителя.

4. Операционный усилитель по п. 3, отличающийся тем, что потенциальный выход операционного усилителя (19) связан со вторым (4) входом операционного усилителя через первый (25) четырехполюсник обратной связи.

5. Операционный усилитель по п. 2, отличающийся тем, что потенциальный выход операционного усилителя (19) связан с первым (16) дополнительным входом операционного усилителя, первый (3) вход операционного усилителя и второй (17) дополнительный вход операционного усилителя связаны с общей шиной (23) источника питания, а второй (4) вход операционного усилителя является вторым инвертирующим входом операционного усилителя.

6. Операционный усилитель по п. 5, отличающийся тем, что потенциальный выход операционного усилителя (19) связан с первым (16) дополнительным входом операционного усилителя через второй (26) четырехполюсник обратной связи.

7. Операционный усилитель по п. 1, отличающийся тем, что первый (16) дополнительный вход операционного усилителя соединен со вторым (4) входом операционного усилителя, а второй (17) дополнительный вход операционного усилителя подключен в первому (3) входу операционного усилителя.

8. Операционный усилитель по п. 2, отличающийся тем, что в схему введены первый (27) и второй (28) дополнительные биполярные транзисторы, а также третий (29) и четвертый (30) дополнительные полевые транзисторы, база первого (27) дополнительного биполярного транзистора связана с третьим (31) дополнительным входом операционного усилителя, база второго (28) дополнительного биполярного транзистора связана с четвертым (32) дополнительным входом операционного усилителя, затвор третьего (29) дополнительного полевого транзистора связан с пятым (33) дополнительным входом операционного усилителя, затвор четвертого (30) дополнительного полевого транзистора связан с шестым (34) дополнительным входом операционного усилителя, коллекторы первого (27) и второго (28) дополнительных биполярных транзисторов подключены к первой (6) шине источника питания, эмиттер первого (27) дополнительного биполярного транзистора связан с истоком первого (29) дополнительного полевого транзистора, эмиттер второго (28) дополнительного биполярного транзистора связан с истоком четвертого (30) дополнительного полевого транзистора, сток третьего (29) дополнительного полевого транзистора подключен к базе второго (9) выходного транзистора, сток четвертого (30) дополнительного полевого транзистора подключен к базе первого (8) выходного транзистора.

9. Операционный усилитель по п. 8, отличающийся тем, что потенциальный выход операционного усилителя (19) связан с четвертым (32) дополнительным входом операционного усилителя.

10. Операционный усилитель по п. 8, отличающийся тем, что первый (16) дополнительный вход операционного усилителя соединен со вторым (4) входом операционного усилителя, второй (17) дополнительный вход операционного усилителя связан с первым (3) входом операционного усилителя, шестой (34) дополнительный вход операционного усилителя связан с третьим (31) дополнительным входом операционного усилителя, а пятый (33) дополнительный вход операционного усилителя соединен с четвертым (32) дополнительным входом операционного усилителя.

| Станок для изготовления деревянных ниточных катушек из цилиндрических, снабженных осевым отверстием, заготовок | 1923 |

|

SU2008A1 |

| ПРЕЦИЗИОННЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2390916C1 |

| US 3614645 A, 19.10.1971 | |||

| ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2010 |

|

RU2414808C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ ПИТАНИЯ | 2011 |

|

RU2441316C1 |

| ПРЕЦИЗИОННЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2011 |

|

RU2455757C1 |

Авторы

Даты

2017-04-03—Публикация

2015-10-13—Подача