Изобретение относится к области радиотехники и может быть использовано в качестве малошумящего устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения, например, в арсенид-галлиевых операционных усилителях (ОУ), компараторах и т.п., в т.ч. работающих в широком диапазоне температур и воздействия радиации.

Известны схемы классических дифференциальных усилителей (ДУ) на полевых транзисторах с управляющим p-n переходом (JFet) [1-15], которые стали основой многих аналоговых микросхем.

Для работы в широком диапазоне температур при жестких ограничениях на уровень шумов перспективно использование арсенид-галлиевых полевых транзисторов (JFet) [16]. ДУ данного класса активно применяются в структуре малошумящих аналоговых интерфейсов для обработки сигналов датчиков. Однако ряд технологических процессов накладывает существенные ограничения на типы применяемых транзисторов. Так, например, ОАО «Минский НИИ радиоматериалов» допускает применение арсенид-галлиевых полевых и арсенид-галлиевых pnp-биполярных транзисторов. Для построения ОУ в данном элементном базисе нужна специальная схемотехника.

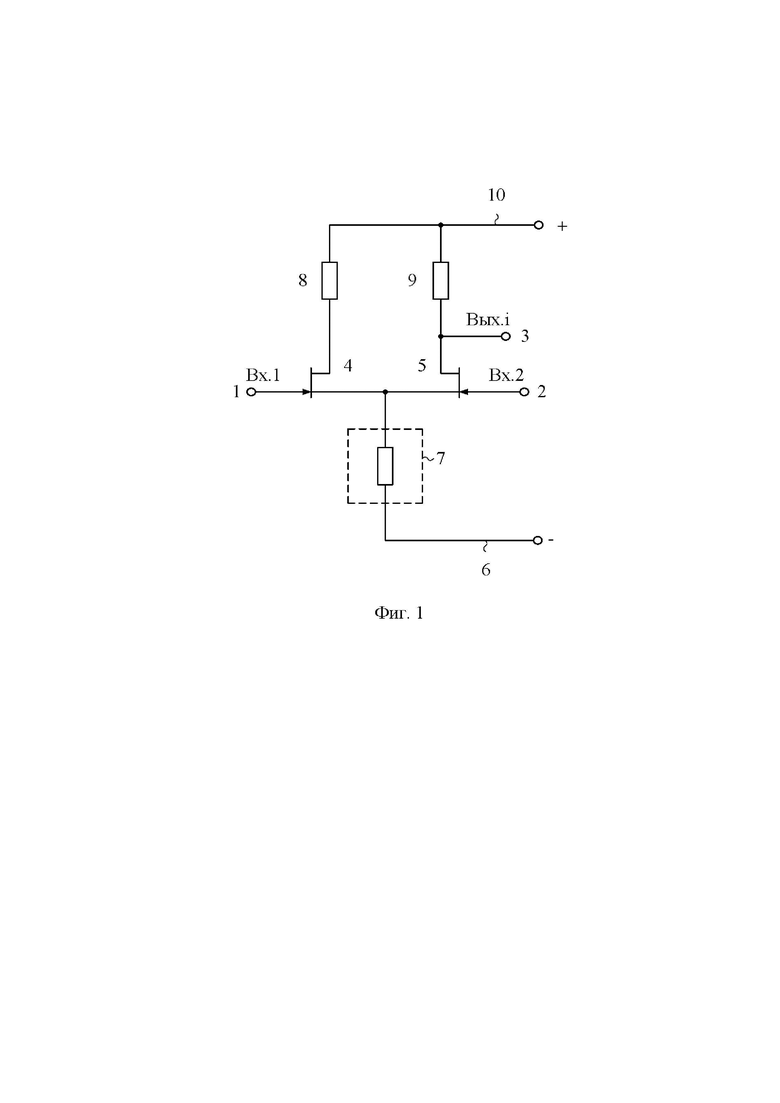

Ближайшим прототипом (фиг. 1) заявляемого устройства является классический входной дифференциальный усилитель в структуре схемы ОУ, представленной в патенте ЕР 0293486 (fig.1), который содержит первый 1 и второй 2 входы, токовый выход 3 устройства, первый 4 и второй 5 входные полевые транзисторы, объединенные истоки которых соединены с первой 6 шиной источника питания через токостабилизирующий двухполюсник 7, причем сток первого 4 входного полевого транзистора соединен с первым выводом первого 8 резистора нагрузки, а сток второго 5 входного полевого транзистора соединен с токовым выходом 3 устройства и первым выводом второго 9 резистора нагрузки, затвор первого 4 входного полевого транзистора соединен с первым 1 входом устройства, а затвор второго 5 входного полевого транзистора связан со вторым 2 входом устройства, вторую 10 шину источника питания.

Существенный недостаток известного ДУ фиг. 1 состоит в том, что при его реализации в рамках арсенид-галлиевых технологических процессов его коэффициент усиления по напряжению оказывается небольшим (особенно при работе входных транзисторов в микрорежиме). Прежде всего, это связано с малыми значениями крутизны GaAs JFET.

Основная задача предполагаемого изобретения состоит в создании условий, при которых в ДУ фиг. 1 обеспечивается повышение коэффициента усиления по напряжению при работе GaAs транзисторов с малыми статическими токами.

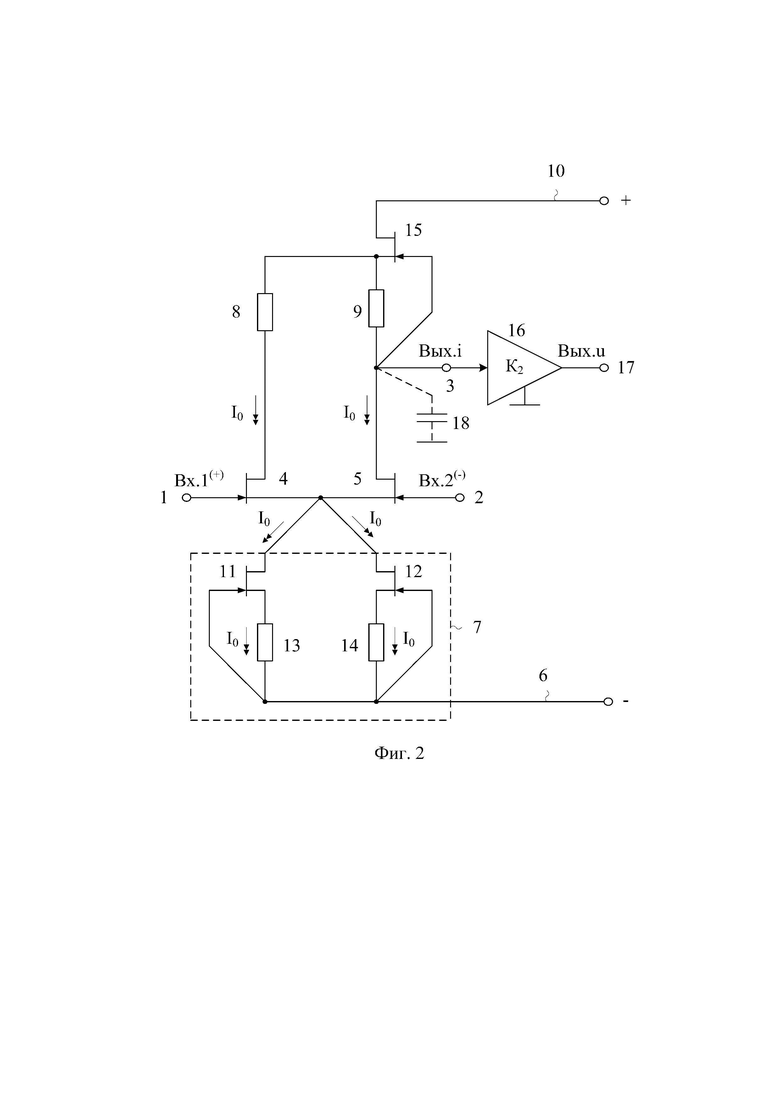

Поставленная задача решается тем, что в дифференциальном усилителе фиг. 1, содержащем первый 1 и второй 2 входы, токовый выход 3 устройства, первый 4 и второй 5 входные полевые транзисторы, объединенные истоки которых соединены с первой 6 шиной источника питания через токостабилизирующий двухполюсник 7, причем сток первого 4 входного полевого транзистора соединен с первым выводом первого 8 резистора нагрузки, а сток второго 5 входного полевого транзистора соединен с токовым выходом 3 устройства и первым выводом второго 9 резистора нагрузки, затвор первого 4 входного полевого транзистора соединен с первым 1 входом устройства, а затвор второго 5 входного полевого транзистора связан со вторым 2 входом устройства, вторую 10 шину источника питания, предусмотрены новые элементы и связи – токостабилизирующий двухполюсник 7 содержит первый 11 и второй 12 вспомогательные полевые транзисторы, затворы которых подключены к первой 6 шине источника питания, исток первого 11 вспомогательного полевого транзистора связан с первой 6 шиной источника питания через первый 13 вспомогательный резистор, исток второго 12 вспомогательного полевого транзистора соединен с первой 6 шиной источника питания через второй 14 вспомогательный резистор, стоки первого 11 и второго 12 вспомогательных полевых транзисторов соединены с объединенными истоками первого 4 и второго 5 входных полевых транзисторов, причем вторые выводы первого 8 и второго 9 резисторов нагрузки связаны с истоком дополнительного полевого транзистора 15, затвор которого подключен к стоку второго 5 входного полевого транзистора, а сток связан со второй 10 шиной источника питания.

На фиг. 1 представлена схема ДУ-прототипа, а на фиг. 2 – схема заявляемого устройства в соответствии с п. 1 и п. 2 формулы изобретения.

На фиг. 3 показан статический режим в ОУ с заявляемым входным GaAs дифференциальным усилителем фиг. 2 при R1÷R2 = 5,3 кОм, I1÷I2 = 500 мкА, V1 = 5 В, C1 = 3 пФ, Vcc=Vee=±10 В.

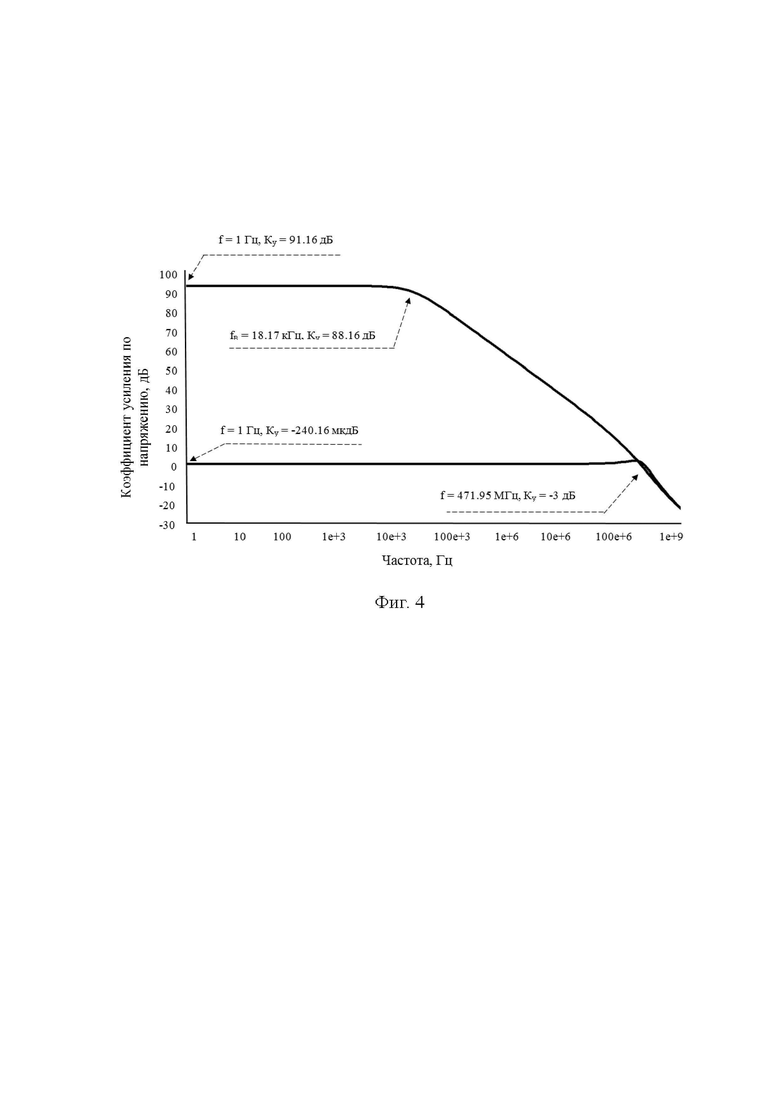

На фиг. 4 приведена амплитудно-частотная характеристика коэффициента усиления по напряжению ОУ с заявляемым входным GaAs дифференциальным усилителем – прототипом фиг. 3 при R1÷R2 = 5,8 кОм, I1÷I2 = 500 мкА, V1 = 5 В, C1 = 3 пФ, Vcc=Vee=±10 В.

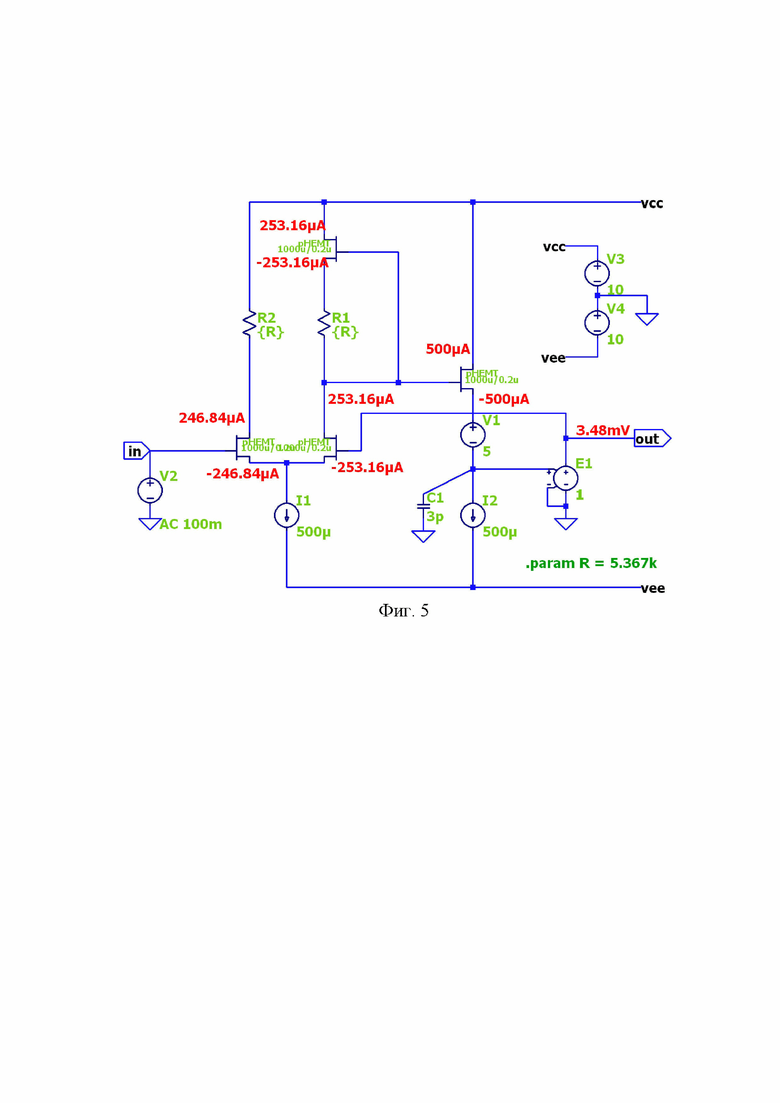

На фиг. 5 представлен статический режим в ОУ с GaAs входным дифференциальным усилителем – прототипом фиг. 1 при R1÷R2 = 5,3 кОм, I1÷I2 = 500 мкА, V1 = 5 В, C1 = 3 пФ, Vcc=Vee=±10 В.

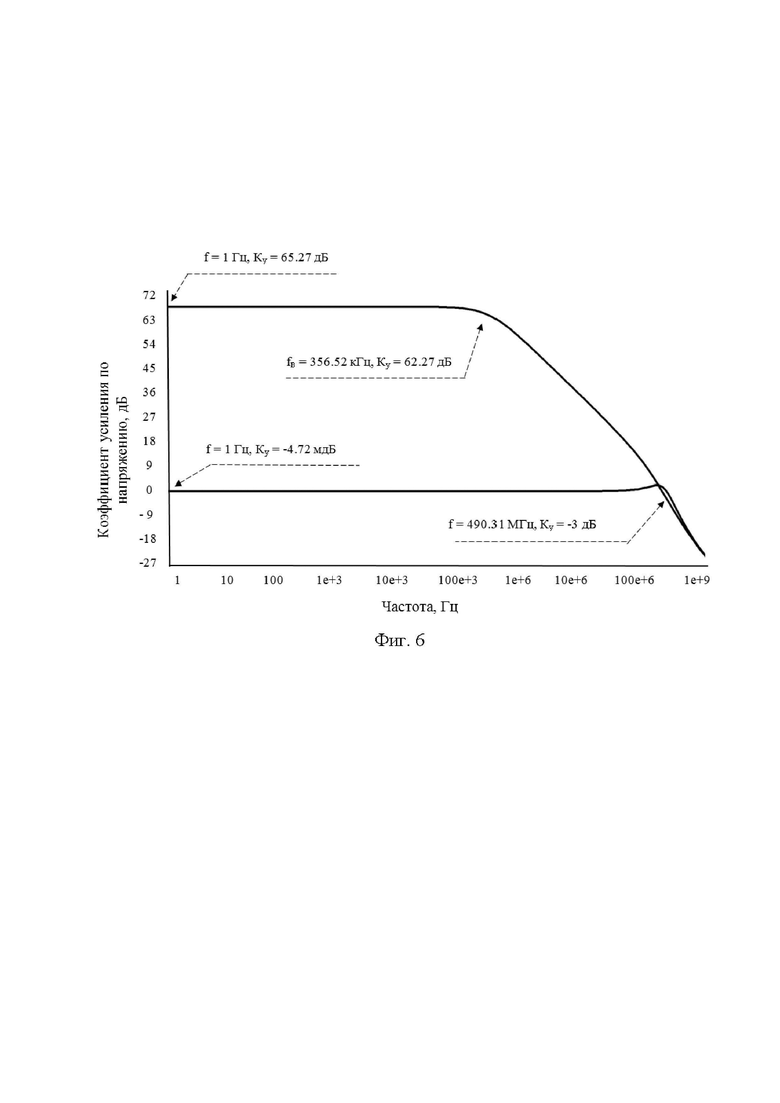

На фиг. 6 показана амплитудно-частотная характеристика коэффициента усиления по напряжению ОУ с GaAs входным дифференциальным усилителем – прототипом фиг. 5 при R1÷R2 = 5,8 кОм, I1÷I2 = 500 мкА, V1 = 5 В, C1 = 3 пФ, Vcc=Vee=±10 В, из которой следует что Ку известной схемы имеет величину порядка 65 дБ.

На фиг. 7 приведена схема заявляемого ДУ фиг. 2 в структуре операционного усилителя по п. 2 формулы изобретения, в которой выходной неинвертирующий буферный усилитель 16 реализован на арсенид-галлиевом входном полевом транзисторе 19, источнике опорного тока 21, цепи смещения потенциалов 20 и вспомогательном буферном усилителе 22.

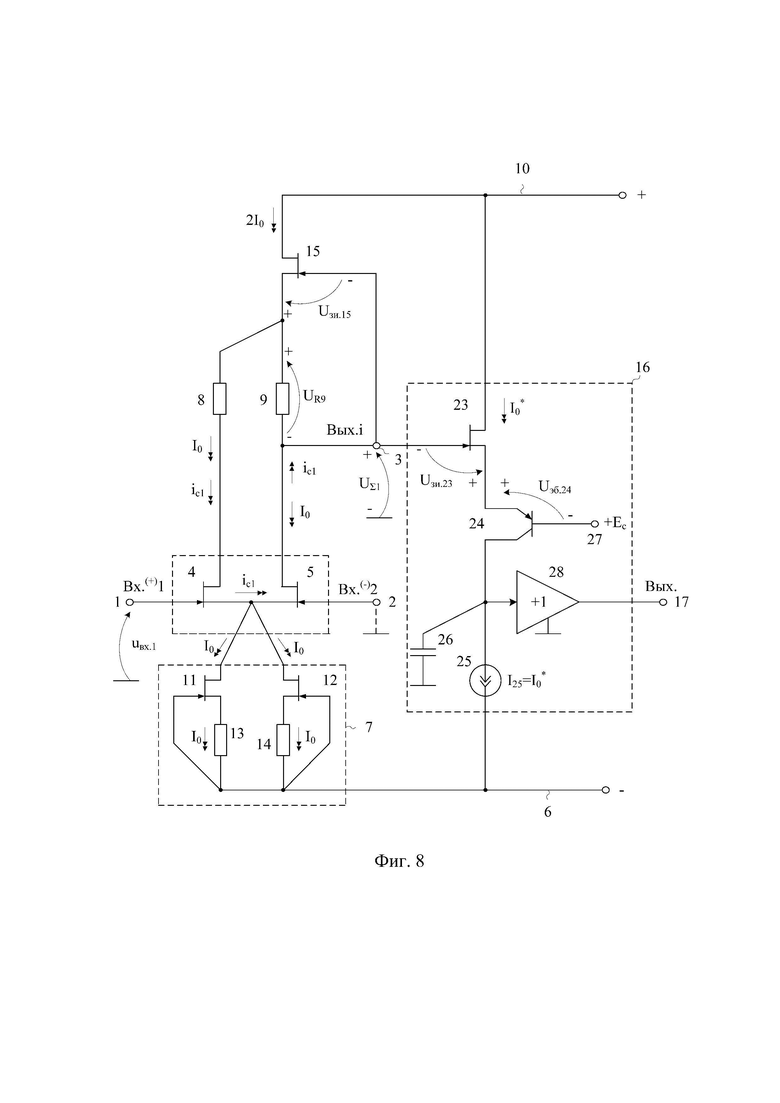

На фиг. 8 приведена схема заявляемого ДУ фиг. 2 в структуре операционного усилителя по п. 2 формулы изобретения, в которой выходной неинвертирующий буферный усилитель 16 реализован на арсенид-галлиевом входном полевом транзисторе 23, арсенид-галлиевом выходном биполярном p-n-p транзисторе 24, источнике опорного тока 25, корректирующем конденсаторе 26, источнике напряжения смещения 27 и согласующем буферном усилителе 28. Схема фиг. 8 позволяет получить более высокие значения коэффициента усиления по напряжению ОУ (до 91 дБ), чем схема фиг. 7.

Дифференциальный усилитель на арсенид-галлиевых полевых транзисторах фиг. 2 содержит первый 1 и второй 2 входы, токовый выход 3 устройства, первый 4 и второй 5 входные полевые транзисторы, объединенные истоки которых соединены с первой 6 шиной источника питания через токостабилизирующий двухполюсник 7, причем сток первого 4 входного полевого транзистора соединен с первым выводом первого 8 резистора нагрузки, а сток второго 5 входного полевого транзистора соединен с токовым выходом 3 устройства и первым выводом второго 9 резистора нагрузки, затвор первого 4 входного полевого транзистора соединен с первым 1 входом устройства, а затвор второго 5 входного полевого транзистора связан со вторым 2 входом устройства, вторую 10 шину источника питания. Токостабилизирующий двухполюсник 7 содержит первый 11 и второй 12 вспомогательные полевые транзисторы, затворы которых подключены к первой 6 шине источника питания, исток первого 11 вспомогательного полевого транзистора связан с первой 6 шиной источника питания через первый 13 вспомогательный резистор, исток второго 12 вспомогательного полевого транзистора соединен с первой 6 шиной источника питания через второй 14 вспомогательный резистор, стоки первого 11 и второго 12 вспомогательных полевых транзисторов соединены с объединенными истоками первого 4 и второго 5 входных полевых транзисторов, причем вторые выводы первого 8 и второго 9 резисторов нагрузки связаны с истоком дополнительного полевого транзистора 15, затвор которого подключен к стоку второго 5 входного полевого транзистора, а сток связан со второй 10 шиной источника питания.

На чертеже фиг. 2, в соответствии с п. 2 формулы изобретения, токовый выход 3 устройства связан со входом дополнительного буферного усилителя напряжения 16, выход 17 которого является потенциальным выходом устройства. На чертеже фиг. 2 корректирующий конденсатор 18 обеспечивает устойчивость операционного усилителя, но в ряде случаев может отсутствовать.

На фиг. 7 приведена схема заявляемого ДУ фиг. 2 в структуре операционного усилителя по п. 2 формулы изобретения, в которой дополнительный буферный усилитель напряжения 16 содержит первый арсенид-галлиевый входной полевой транзистор 19, цепь смещения потенциалов 20, включенную между истоком первого арсенид-галлиевого входного полевого транзистора 19 и источником опорного тока 21, причем общий узел цепи смещения 20 и источника опорного тока 21 соединен со входом вспомогательного буферного усилителя 22, выход которого является потенциальным выходом 17 устройства.

На фиг. 8 приведена схема заявляемого ДУ фиг. 2 в структуре операционного усилителя по п. 2 формулы изобретения, в которой дополнительный буферный усилитель напряжения 16 содержит второй арсенид-галлиевый входной полевой транзистор 23, и выходной арсенид-галлиевый биполярный транзистор 24, исток второго арсенид-галлиевого входного полевого транзистора 23 соединен с эмиттером выходного арсенид-галлиевого биполярного транзистора 24, коллектор выходного арсенид-галлиевого биполярного транзистора 24 соединен с источником опорного тока 25 и корректирующим конденсатором 26, база выходного арсенид-галлиевого биполярного транзистора 24 соединена с источником напряжения смещения 27, коллектор выходного арсенид-галлиевого биполярного транзистора 24 соединен с согласующим буферным усилителем 28, выход которого является потенциальным выходом 17 устройства.

Рассмотрим работу ДУ фиг. 2.

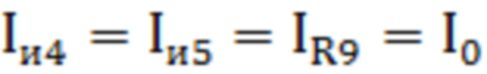

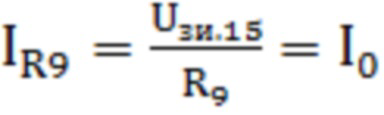

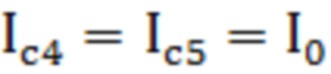

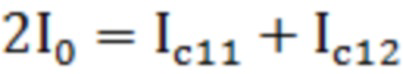

В статическом режиме, например, при подключении первого 1 и второго 2 входов ДУ фиг. 2 к общей шине источников питания, статические токи истоков первого 4 и второго 5 входных полевых транзисторов, а также первого 11 и второго 12 вспомогательных полевых транзисторов определяются численными значениями идентичных сопротивлений первого 13 и второго 14 вспомогательных резисторов

(1)

(1)

, (2)

, (2)

, (3)

, (3)

, (4)

, (4)

, (5)

, (5)

где Iиi – ток истока i-го полевого транзистора; Uзи.11, Uзи.12, Uзи.15 – напряжение затвор-исток соответствующих первого 11 и второго 12 вспомогательных полевых транзисторов и дополнительного полевого транзистора 15 в рабочей точке при токе истока, равном заданному значению I0.

Таким образом, в схеме фиг. 2 за счет выбора идентичных значений сопротивлений первого 13 и второго 14 вспомогательных резисторов, а также второго 9 резистора нагрузки, при известных стоко-затворных характеристиках JFET обеспечивается заданный статический режим по току.

Если на вход 1 подается положительное входное напряжение uвх относительно входа 2, то это вызывает увеличение тока через первый 4 входной полевой транзистор и уменьшение на такую же величину тока стока второго 5 входного полевого транзистора. В результате ток истока дополнительного полевого транзистора 15 не изменяется. При подключении второго вывода первого 8 резистора к истоку дополнительного полевого транзистора 15 обеспечивается передача переменного напряжения на стоке второго 5 входного полевого транзистора в цепь стока первого 4 входного полевого транзистора. Как следствие, изменение напряжения на токовом выходе 3 устройства приводит в заявляемой схеме фиг. 2 к такому же изменению напряжения на стоке первого 4 входного полевого транзистора. Это повышает эквивалентное выходное сопротивление токового выхода 3 устройства и, как следствие, увеличивает коэффициент усиления по напряжению заявляемого ДУ (Ку) при малых значениях крутизны первого 4 и второго 5 входных полевых транзисторов. Сравнительный анализ графиков фиг. 4 и фиг. 6 показывает, что предлагаемое схемотехническое решение фиг. 2 дает повышение Ку на 26 дБ, т.е. более чем в 10 раз.

Существенная особенность предлагаемого ДУ фиг. 2 и операционных усилителей на его основе (фиг. 7, фиг. 8) состоит в том, что при выборе сопротивлений первого 8 и второго 9 резисторов нагрузки, а также первого 13 и второго 14 вспомогательных резисторов одинаковыми, в GaAs ОУ (фиг. 2, фиг. 7, фиг. 8) обеспечиваются малые значения систематической составляющей напряжения смещения нуля (на уровне 1,4 мкВ, фиг. 3). В то же время ОУ с входным каскадом-прототипом имеет Uсм=3,48 мВ, что значительно превышает Uсм ОУ с заявляемым входным ДУ.

В частном случае GaAs буферный усилитель 16 может выполняться в виде неинвертирующего истокового повторителя напряжения (фиг. 7) или BJT JFET GaAs транзисторного каскада (фиг. 8).

Таким образом, заявляемое устройство имеет существенные преимущества в сравнении с ДУ-прототипом, что позволяет рекомендовать его для практического использования в аналоговых GaAs схемах.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент RU 2710296, 2019 г.

2. Авт.св. СССР 537435, 1976 г.

3. Патентная заявка RU 2020134402, 2020 г.

4. Патент US 5.291.149, fig. 3, 1994 г.

5. Патент RU 2679970, fig. 2, 2019 г.

6. Патент RU 2624565, fig. 1, 2016 г.

7. Патент RU 2571399, fig. 2, 2014 г.

8. Авт.св. СССР 437193, 1972 г.

9. Патентная заявка US 2006/01255222, 2006 г.

10. Патент US 4.121.169, fig. 5, fig. 6, 1978 г.

11. Патент US 9.668.045, 2017 г.

12. Патент US 9.888.315, 2018 г.

13. Патент US 9.167.327, 2015 г.

14. Патент EP 0293488, fig. 1, 1988 г.

15. Патент US 5.166.553, fig. 14, 1992 г.

16. Shur, Michael S., “GaAs Devices and Circuits”, Springer Science+Business Media, New York, 1987, 677 p. DOI 10.1007/978-1-4899-1989-2.

| название | год | авторы | номер документа |

|---|---|---|---|

| Операционный усилитель на основе широкозонных полупроводников | 2023 |

|

RU2822157C1 |

| БИПОЛЯРНО-ПОЛЕВОЙ АРСЕНИД-ГАЛЛИЕВЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ | 2023 |

|

RU2796638C1 |

| Многоканальный дифференциальный усилитель на арсенид-галлиевых полевых и биполярных транзисторах | 2022 |

|

RU2792710C1 |

| Прецизионный арсенид-галлиевый операционный усилитель с малым уровнем систематической составляющей напряжения смещения нуля и повышенным коэффициентом усиления | 2023 |

|

RU2813370C1 |

| Арсенид-галлиевый операционный усилитель на основе "перегнутого" каскода | 2023 |

|

RU2820341C1 |

| Арсенид-галлиевый операционный усилитель с повышенным коэффициентом усиления и малым уровнем систематической составляющей напряжения смещения нуля | 2023 |

|

RU2820562C1 |

| Арсенид-галлиевый операционный усилитель с малым напряжением смещения нуля | 2023 |

|

RU2812914C1 |

| АРСЕНИД-ГАЛЛИЕВЫЙ ВХОДНОЙ ДИФФЕРЕНЦИАЛЬНЫЙ КАСКАД КЛАССА АВ БЫСТРОДЕЙСТВУЮЩЕГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ | 2022 |

|

RU2786943C1 |

| АРСЕНИД-ГАЛЛИЕВЫЙ ВЫХОДНОЙ КАСКАД УСИЛИТЕЛЯ МОЩНОСТИ | 2021 |

|

RU2767976C1 |

| ДВУХТАКТНЫЙ АРСЕНИД-ГАЛЛИЕВЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ С МАЛОЙ ЗОНОЙ НЕЧУВСТВИТЕЛЬНОСТИ АМПЛИТУДНОЙ ХАРАКТЕРИСТИКИ | 2022 |

|

RU2789482C1 |

Изобретение относится к области радиотехники. Технический результат - повышение коэффициента усиления по напряжению. Для этого в дифференциальном усилителе на арсенид-галлиевых полевых транзисторах токостабилизирующий двухполюсник (7) содержит первый (11) и второй (12) вспомогательные полевые транзисторы, затворы которых подключены к первой (6) шине источника питания, исток первого (11) вспомогательного полевого транзистора связан с первой (6) шиной источника питания через первый (13) вспомогательный резистор, исток второго (12) вспомогательного полевого транзистора соединен с первой (6) шиной источника питания через второй (14) вспомогательный резистор, стоки первого (11) и второго (12) вспомогательных полевых транзисторов соединены с объединенными истоками первого (4) и второго (5) входных полевых транзисторов, причем вторые выводы первого (8) и второго (9) резисторов нагрузки связаны с истоком дополнительного полевого транзистора (15), затвор которого подключен к стоку второго (5) входного полевого транзистора, а сток связан со второй (10) шиной источника питания. 3 з.п. ф-лы, 8 ил.

1. Дифференциальный усилитель на арсенид-галлиевых полевых транзисторах, содержащий первый (1) и второй (2) входы, токовый выход (3) устройства, первый (4) и второй (5) входные полевые транзисторы, объединенные истоки которых соединены с первой (6) шиной источника питания через токостабилизирующий двухполюсник (7), причем сток первого (4) входного полевого транзистора соединен с первым выводом первого (8) резистора нагрузки, а сток второго (5) входного полевого транзистора соединен с токовым выходом (3) устройства и первым выводом второго (9) резистора нагрузки, затвор первого (4) входного полевого транзистора соединен с первым (1) входом устройства, а затвор второго (5) входного полевого транзистора связан со вторым (2) входом устройства, вторую (10) шину источника питания, отличающийся тем, что токостабилизирующий двухполюсник (7) содержит первый (11) и второй (12) вспомогательные полевые транзисторы, затворы которых подключены к первой (6) шине источника питания, исток первого (11) вспомогательного полевого транзистора связан с первой (6) шиной источника питания через первый (13) вспомогательный резистор, исток второго (12) вспомогательного полевого транзистора соединен с первой (6) шиной источника питания через второй (14) вспомогательный резистор, стоки первого (11) и второго (12) вспомогательных полевых транзисторов соединены с объединенными истоками первого (4) и второго (5) входных полевых транзисторов, причем вторые выводы первого (8) и второго (9) резисторов нагрузки связаны с истоком дополнительного полевого транзистора (15), затвор которого подключен к стоку второго (5) входного полевого транзистора, а сток связан со второй (10) шиной источника питания.

2. Дифференциальный усилитель на арсенид-галлиевых полевых транзисторах по п. 1, отличающийся тем, что токовый выход (3) устройства связан со входом дополнительного буферного усилителя напряжения (16), выход (17) которого является потенциальным выходом устройства.

3. Дифференциальный усилитель на арсенид-галлиевых полевых транзисторах по п. 1, отличающийся тем, что дополнительный буферный усилитель напряжения (16) содержит первый арсенид-галлиевый входной полевой транзистор (19), цепь смещения потенциалов (20), включенную между истоком первого арсенид-галлиевого входного полевого транзистора (19) и источником опорного тока (21), причем общий узел цепи смещения (20) и источника опорного тока (21) соединен со входом вспомогательного буферного усилителя (22), выход которого является потенциальным выходом (17) устройства.

4. Дифференциальный усилитель на арсенид-галлиевых полевых транзисторах по п. 2, отличающийся тем, что дополнительный буферный усилитель напряжения (16) содержит второй арсенид-галлиевый входной полевой транзистор (23) и выходной арсенид-галлиевый биполярный транзистор (24), исток второго арсенид-галлиевого входного полевого транзистора (23) соединен с эмиттером выходного арсенид-галлиевого биполярного транзистора (24), коллектор выходного арсенид-галлиевого биполярного транзистора (24) соединен с источником опорного тока (25) и корректирующим конденсатором (26), база выходного арсенид-галлиевого биполярного транзистора (24) соединена с источником напряжения смещения (27), коллектор выходного арсенид-галлиевого биполярного транзистора (24) соединен с согласующим буферным усилителем (28), выход которого является потенциальным выходом (17) устройства.

| Газовая вагранка | 1968 |

|

SU293486A1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С РАСШИРЕННЫМ ДИАПАЗОНОМ АКТИВНОЙ РАБОТЫ | 2007 |

|

RU2331971C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С РАСШИРЕННЫМ ДИАПАЗОНОМ АКТИВНОЙ РАБОТЫ | 2007 |

|

RU2333593C1 |

| Дифференциальный усилитель | 1985 |

|

SU1314440A1 |

Авторы

Даты

2022-04-25—Публикация

2021-10-06—Подача