Изобретение относится к области аналоговой микроэлектроники и может быть использовано в качестве быстродействующих двухтактных буферных усилителей и выходных каскадов, работающих на емкостную нагрузку, в различных аналоговых устройствах (операционных усилителях, драйверах линий связи и т.п.).

Известно значительное количество схем двухтактных буферных усилителей (БУ), которые реализуются на комплементарных биполярных (BJT) или полевых (JFet, КМОП, КНИ, КНС и др.) транзисторах [1-29], а также при их совместном включении. Вышеназванные схемотехнические решения БУ наиболее популярны как в зарубежных, так и в российских аналоговых микросхемах, реализуемых на основе типовых технологических процессов [1-29].

Ближайшим прототипом заявляемого устройства является буферный усилитель (фиг. 1), представленный в патенте фирмы Japan Radio US 5.497.124, fig.25. Схема БУ-прототипа фиг. 1 содержит вход 1 и выход 2 устройства, первый 3 выходной полевой транзистор, исток которого связан с выходом 2 устройства, а сток соединен с первым 4 токовым выходом устройства, согласованным с первой 5 шиной источника питания, второй 6 выходной полевой транзистор, исток которого связан с выходом 2 устройства, а сток соединен со вторым 7 токовым выходом устройства, согласованным со второй 8 шиной источника питания, первый 9 и второй 10 нелинейные двухполюсники.

БУ-прототип перспективен для использования в качестве выходных каскадов ОУ с потенциальной отрицательной обратной связью [29] (когда используются только выход 2 устройства), а также входных каскадов ОУ с токовой отрицательной обратной связью [28,29], когда используется первый 4 и второй 7 токовые выходы устройства. В последнем случае к величине напряжения смещения нуля БУ предъявляются повышенные требования [28].

Наличие паразитных емкостей Cа и Сb в цепи затвора первого 3 и второго 6 выходных полевых транзисторов не позволяет получить высокое быстродействие в БУ-прототипе при наличии емкости в цепи нагрузки Сн и импульсном изменении входного сигнала большой амплитуды. В этом режиме первый 9 (второй 10) нелинейный двухполюсник запирается и изменение потенциала на затворе первого 3 (второго 6) выходного полевого транзистора имеет «пилообразный» характер:

(1)

(1)

(2)

(2)

где Ia, Ib – токи двухполюсников Ia и Ib.

Данный недостаток присущ всем модификациям буферного усилителя [1-29], содержащим в своей структуре последовательно включенные входные истоковые (или эмиттерные) повторители и выходные истоковые (или эмиттерные) повторители. Такая двухкаскадная архитектура БУ не перспективна для применения в быстродействующих ОУ. Кроме этого, входной (Iвх) статический ток БУ-прототипа фиг. 1 (Iвх=Ib-Ia) зависит от согласованности токов источников опорного тока Ia и Ib. Поэтому в известной схеме БУ недоиспользуются свойства КМОП транзисторов, которые имеют экстремально малые значения токов затвора.

Основная задача предполагаемого изобретения состоит в создании БУ на комплементарных полевых транзисторах, обеспечивающего (при высокой линейности амплитудной характеристики) малые значения систематической составляющей напряжения смещения нуля, малые входные токи, соответствующие токам затвора первого 3 и второго 6 выходных полевых транзисторов, а также высокое быстродействие при наличии емкостной нагрузки и обработке импульсных входных сигналов большой амплитуды.

Поставленная задача достигается тем, что в буферном усилителе фиг. 1, содержащем вход 1 и выход 2 устройства, первый 3 выходной полевой транзистор, исток которого связан с выходом 2 устройства, а сток соединен с первым 4 токовым выходом устройства, согласованным с первой 5 шиной источника питания, второй 6 выходной полевой транзистор, исток которого связан с выходом 2 устройства, а сток соединен со вторым 7 токовым выходом устройства, согласованным со второй 8 шиной источника питания, первый 9 и второй 10 нелинейные двухполюсники, предусмотрены новые связи - затворы первого 3 и второго 6 выходных полевых транзисторов соединены со входом 1 устройства, исток первого 3 выходного полевого транзистора связан с выходом 2 устройства через первый 9 нелинейный двухполюсник, а исток второго 6 выходного полевого транзистора связан с выходом 2 устройства через второй 10 нелинейный двухполюсник.

На чертеже фиг. 1 показан буферный усилитель-прототип по патенту US 5.497.124, fig.25.

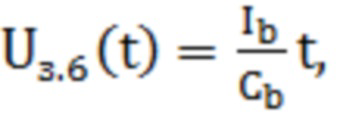

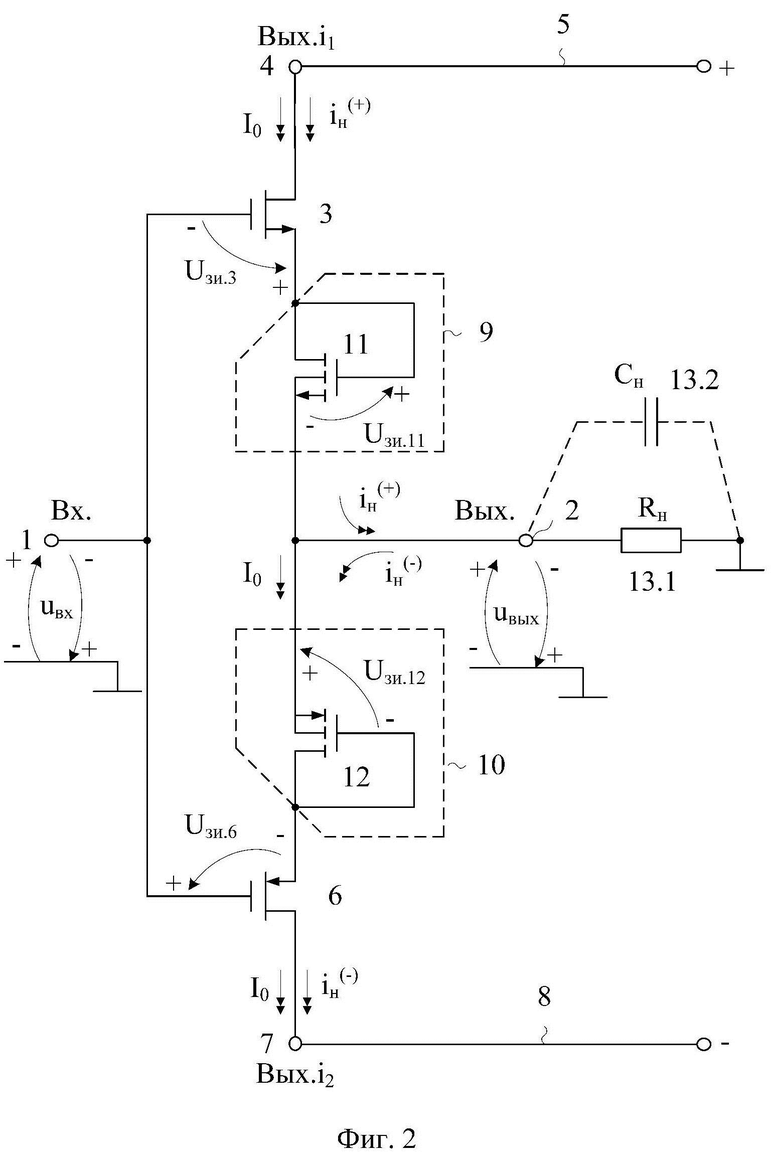

На чертеже фиг. 2 представлена схема заявляемого быстродействующего двухтактного буферного усилителя в соответствии с п. 1 и п. 2 формулы изобретения.

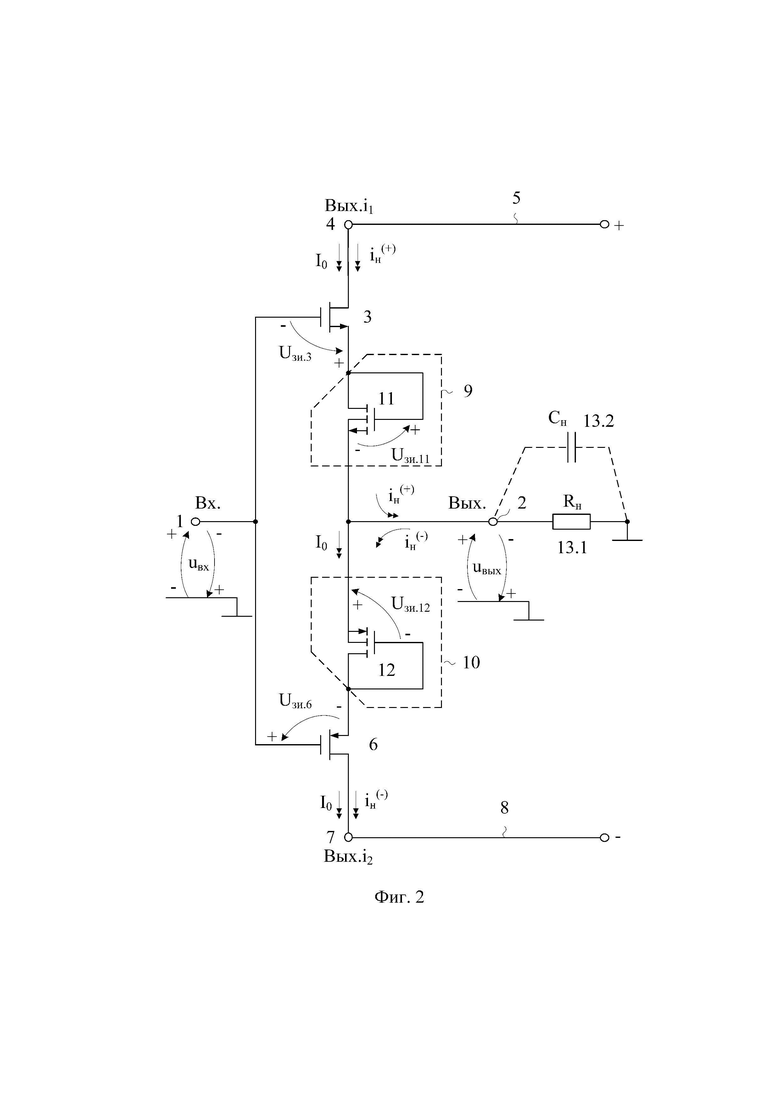

На чертеже фиг. 3 приведена схема заявляемого устройства в соответствии с п. 3 формулы изобретения.

На чертеже фиг. 4 показана схема заявляемого двухтактного буферного усилителя в соответствии с п. 4 и п.5 формулы изобретения.

На чертеже фиг. 5 представлена схема заявляемого двухтактного буферного усилителя в соответствии с п. 6 формулы изобретения.

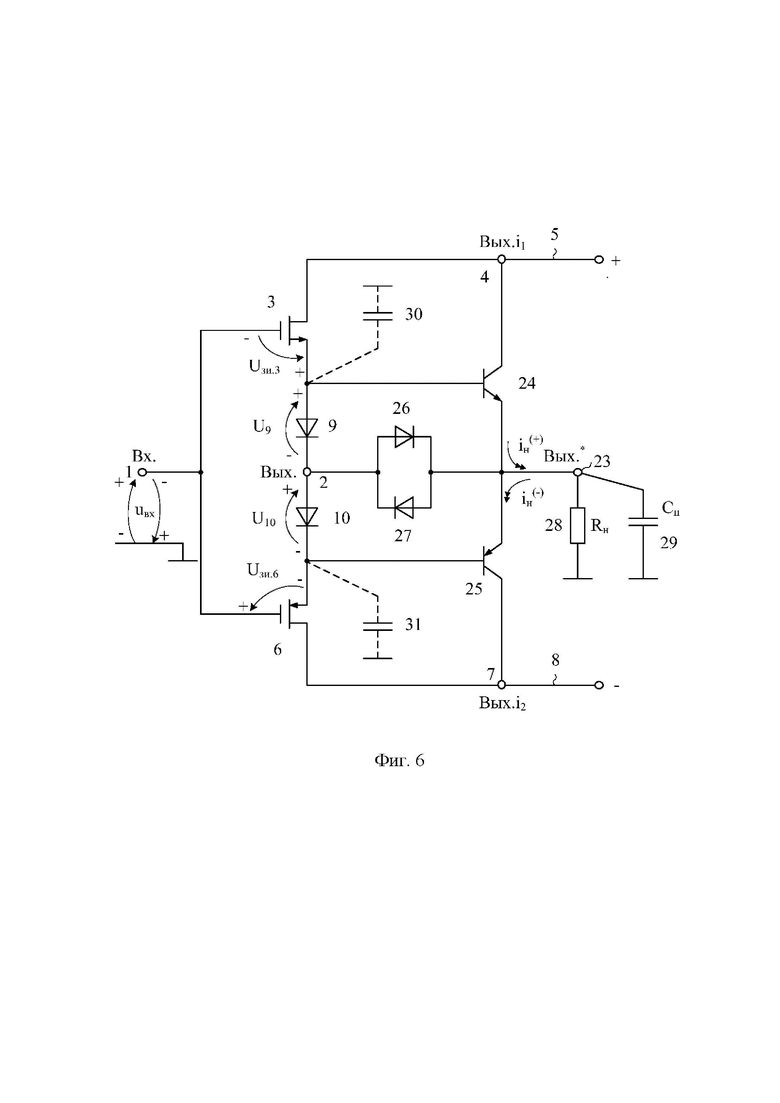

На чертеже фиг. 6 приведена схема двухтактного буферного усилителя на комплементарных полевых транзисторах в соответствии с п. 7 формулы изобретения.

На чертеже фиг. 7 показана схема двухтактного буферного усилителя на комплементарных полевых транзисторах в соответствии с п. 8 формулы изобретения.

На чертеже фиг. 8 представлена схема для моделирования буферного усилителя на чертеже фиг. 4 в среде LTspice при t=27oC, +Vcc=-Vee=5 В, Rload=1 МОм на моделях полевых и биполярных транзисторов базовых матричных кристаллов АО «Интеграл» (г. Минск) [30-32].

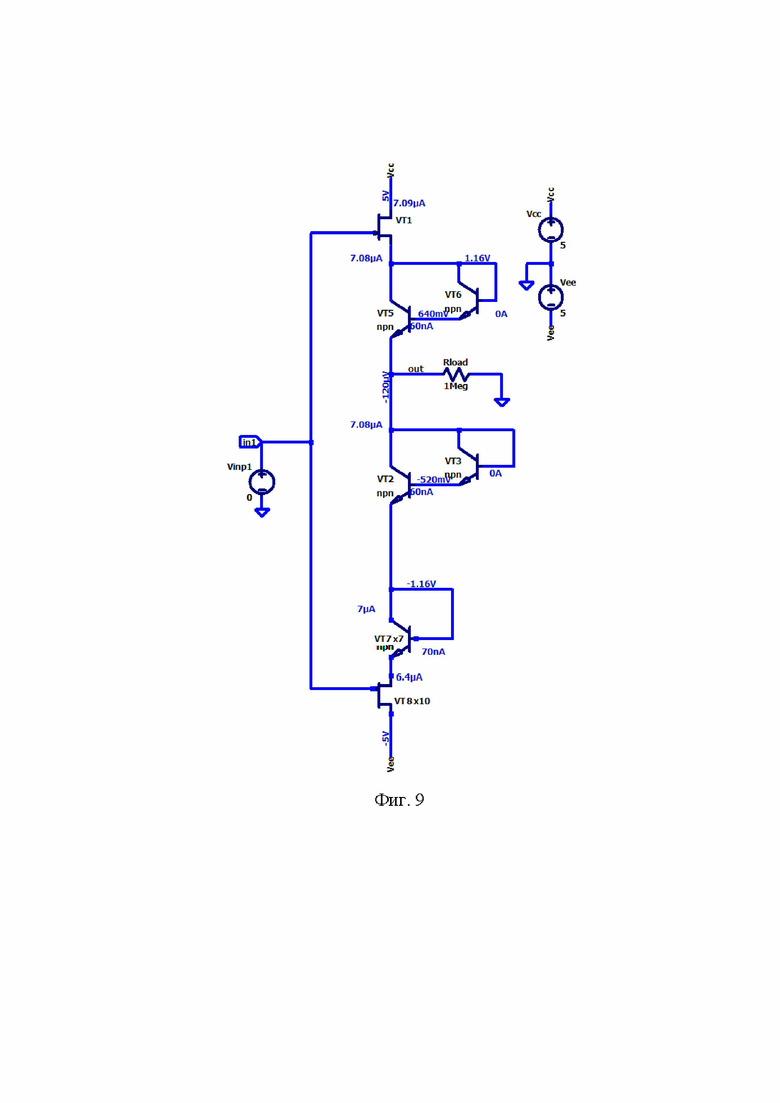

На чертеже фиг. 9 приведена схема для моделирования напряжения смешщения нуля буферного усилителя на чертеже фиг. 5 в среде LTspice при t=27oC, +Vcc=-Vee=5 В, Rload=1 МОм, числе параллельно включенных транзисторов VT7 N1=7 и числе параллельно включенных транзисторов VT8 N2=10.

На чертеже фиг. 10 показана амплитудная характеристика буферного усилителя на чертеже фиг. 9 при Rload= 5кОм/ 10кОм/1 Мом.

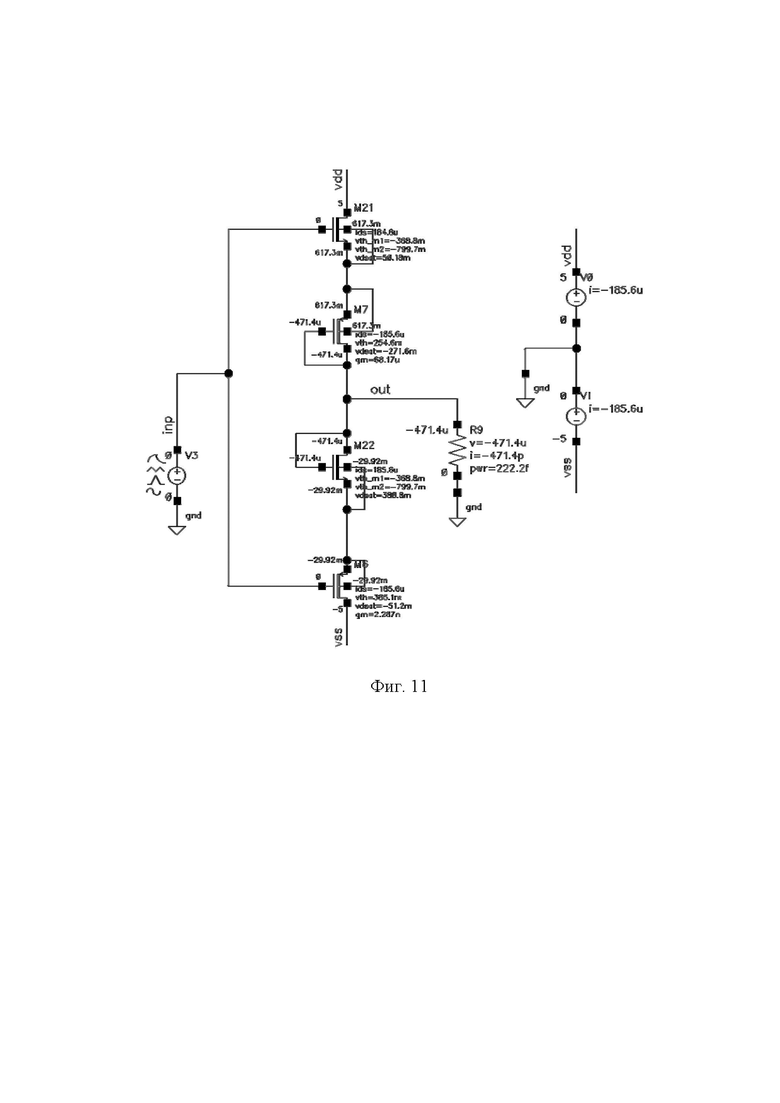

На чертеже фиг. 11 представлен статический режим буферного усилителя фиг. 2 в среде моделирования Cadence на элементах техпроцесса XB06 (X-fab) для случая, когда транзистора М21, М22 имеют встроенный n-канал, а транзисторы М7 и М6 встроенный p-канал. Данное моделирование показывает, что при выбранных параметрах транзисторов систематическая составляющая напряжения смещения нуля равна -417,4 мкВ.

На чертеже фиг. 12 приведена амплитудно-частотная характеристика буферного усилителя фиг. 11.

На чертеже фиг. 13 показана зависимость выходного напряжения буферного усилителя фиг. 11 от входного напряжения.

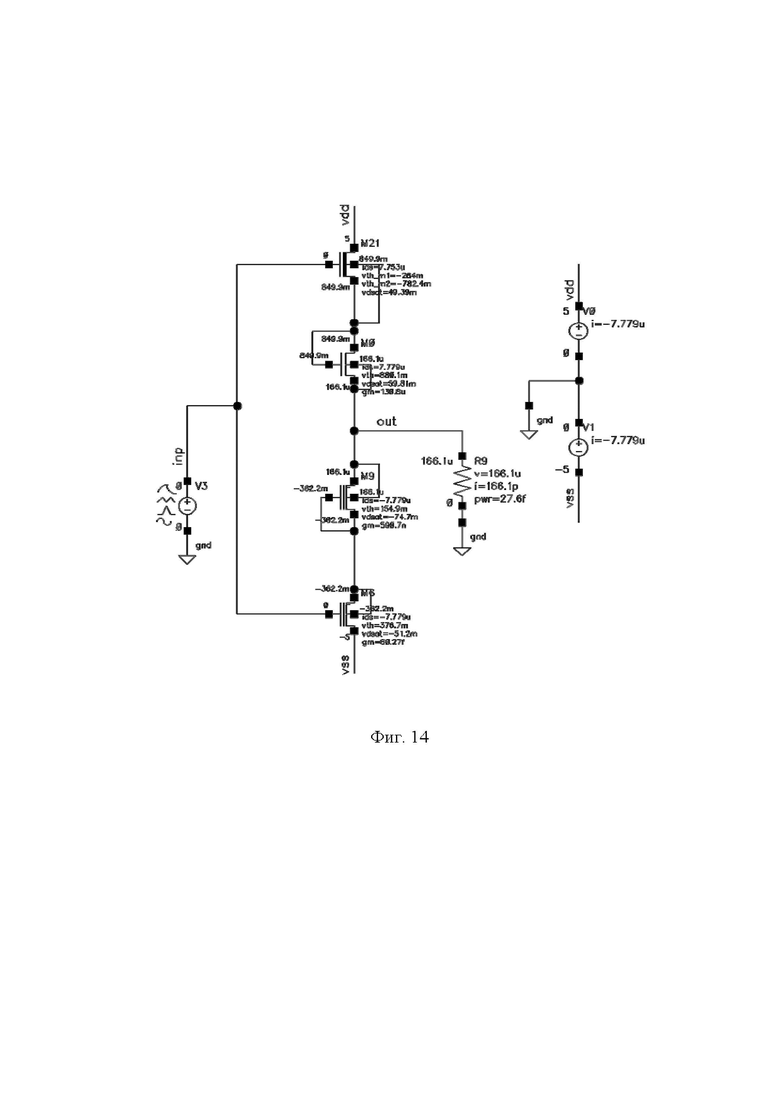

На чертеже фиг. 14 представлен статический режим буферного усилителя фиг. 2 в среде моделирования Cadence на элементах техпроцесса XB06 (X-fab) для случая, когда транзистор М21 имеет встроенный n-канал, транзисторы М6, М9 встроенный p-канал, а М0 - индуцированный n-канал. Данное моделирование показывает, что при выбранных параметрах транзисторов систематическая составляющая напряжения смещения нуля равна 166,1 мкВ.

На чертеже фиг. 15 показана амплитудно-частотная характеристика буферного усилителя фиг. 14.

На чертеже фиг. 16 приведена зависимость выходного напряжения буферного усилителя фиг. 14 от входного напряжения.

Быстродействующий двухтактный буферный усилитель на комплементарных полевых транзисторах фиг. 2 содержит вход 1 и выход 2 устройства, первый 3 выходной полевой транзистор, исток которого связан с выходом 2 устройства, а сток соединен с первым 4 токовым выходом устройства, согласованным с первой 5 шиной источника питания, второй 6 выходной полевой транзистор, исток которого связан с выходом 2 устройства, а сток соединен со вторым 7 токовым выходом устройства, согласованным со второй 8 шиной источника питания, первый 9 и второй 10 нелинейные двухполюсники. Затворы первого 3 и второго 6 выходных полевых транзисторов соединены со входом 1 устройства, исток первого 3 выходного полевого транзистора связан с выходом 2 устройства через первый 9 нелинейный двухполюсник, а исток второго 6 выходного полевого транзистора связан с выходом 2 устройства через второй 10 нелинейный двухполюсник.

На чертеже фиг. 2, в соответствии с п. 2 формулы изобретения, в качестве первого 3 и второго 6 выходных полевых транзисторов используются КМОП полевые транзисторы со встроенным каналом, причем первый 9 и второй 10 нелинейные двухполюсники выполнены на первом 11 и втором 12 КМОП транзисторах с индуцированным каналом, затвор первого 11 КМОП транзистора с индуцированным каналом связан с его стоком, а затвор второго 12 КМОП транзистора с индуцированным каналом подключен к его стоку. К выходу 2 устройства подключается нагрузка, содержащая в частном случае резистивную (13.1) и емкостную (13.2) составляющие.

На чертеже фиг. 3, в соответствии с п. 3 формулы изобретения, в качестве первого 9 и второго 10 нелинейных двухполюсников используются первый 14 и второй 15 биполярные транзисторы, причем база первого 14 биполярного транзистора соединена с его коллектором, а база второго 15 биполярного транзистора подключена к его коллектору.

На чертеже фиг. 4, в соответствии с п. 4 формулы изобретения, в качестве первого 3 и второго 6 выходных полевых транзисторов используются полевые транзисторы с управляющим p-n переходом.

Кроме этого, на чертеже фиг. 4, в соответствии с п. 5 формулы изобретения, первый 9 нелинейный двухполюсник выполнен в виде первого 16 прямосмещенного p-n перехода на биполярном транзисторе, база которого соединена с коллектором, а второй 10 нелинейный двухполюсник реализован в виде второго 17 прямосмещенного p-n перехода на биполярном транзисторе, база которого соединена с коллектором.

На чертеже фиг. 5, в соответствии с п. 6 формулы изобретения, первый 9 нелинейный двухполюсник выполнен на основе первого 18 и второго 19 вспомогательных биполярных транзисторах, причем база первого 18 вспомогательного биполярного транзистора соединена с его коллектором и подключена к коллектору второго 19 вспомогательного биполярного транзистора, а эмиттер первого 18 вспомогательного биполярного транзистора соединен с базой второго 19 вспомогательного биполярного транзистора, кроме этого второй 10 нелинейный двухполюсник выполнен на третьем 20, четвертом 21 и пятом 22 вспомогательных биполярных транзисторах, причем база третьего 20 вспомогательного биполярного транзистора соединена с его коллектором и подключена к коллектору четвертого 21 вспомогательного биполярного транзистора, эмиттер третьего 20 вспомогательного биполярного транзистора подключен к базе четвертого 21 вспомогательного биполярного транзистора, а эмиттер четвертого 21 вспомогательного биполярного транзистора соединен с коллектором и базой пятого 22 вспомогательного биполярного транзистора.

На чертеже фиг. 6, в соответствии с п. 7 формулы изобретения, устройство содержит вспомогательный потенциальный выход 23, который связан с эмиттерами первого 24 и второго 25 дополнительных выходных биполярных транзисторов, коллектор первого 24 дополнительного выходного биполярного транзистора подключен к первому 4 токовому выходу устройства, коллектор второго 25 дополнительного выходного биполярного транзистора соединен со вторым 7 токовым выходом устройства, база первого 24 дополнительного выходного биполярного транзистора соединена с истоком первого 3 входного полевого транзистора со встроенным каналом, база второго 25 дополнительного выходного биполярного транзистора подключена к истоку второго 6 выходного полевого транзистора со встроенным каналом, а между выходом 2 устройства и вспомогательным потенциальным выходом 23 включены два встречно-параллельно включенных вспомогательных p-n перехода 26 и 27. Элементы 28 и 29 моделируют свойства нагрузки, а конденсаторы 30 и 31 – паразитные емкости в истоках первого 3 и второго 6 выходных полевых транзисторов.

На чертеже фиг. 7, в соответствии с п. 8 формулы изобретения, устройство содержит вспомогательный потенциальный выход 23, который связан с эмиттерами первого 24 и второго 25 дополнительных выходных биполярных транзисторов, коллектор первого 24 дополнительного выходного биполярного транзистора подключен к первому 4 токовому выходу устройства, коллектор второго 25 дополнительного выходного биполярного транзистора соединен со вторым 7 токовым выходом устройства, база первого 24 дополнительного выходного биполярного транзистора соединена с истоком первого 3 входного полевого транзистора со встроенным каналом, база второго 25 дополнительного выходного биполярного транзистора подключена к истоку второго 6 выходного полевого транзистора со встроенным каналом, а между выходом 2 устройства и вспомогательным потенциальным выходом 23 включен согласующий резистор 32.

Рассмотрим работу предлагаемого БУ фиг. 4.

Особенность схемы БУ фиг. 4 состоит в том, что статический режим первого 3 и второго 6 выходных полевых транзисторов по току определяется характеристиками первого 9 и второго 10 нелинейных двухполюсников (транзисторов 16 и 17), что позволяет за счет изменения их геометрических параметров (ширины и длины канала) выбирать заданные значения токов стоков (Ic3, Ic6) данных активных элементов:

Ic3 = Ic6 = Iскв = I0,

где Iскв – сквозной ток БУ.

Введение новых элементов и связей между ними в соответствии с формулой изобретения позволяют получить малые значения систематической составляющей напряжения смещения нуля, например, в схеме БУ фиг. 2. Возможности подстройки величины напряжения смещения нуля БУ (Uсм) продемонстрированы в схеме фиг. 5 и на чертежах фиг. 8 и фиг. 9.

За счет оптимизации (целенаправленного изменения) параметров первого 9 и второго 10 нелинейных двухполюсников могут быть получены малые значения Uсм (фиг. 9) (на уровне десятков микровольт, без учета технологического разброса параметров элементов).

Таким образом, заявляемый БУ допускает параметрическую оптимизацию параметров, например, по критерию минимизации напряжения смещения нуля, которое в реальных схемах обеспечивается за счет оптимального выбора структуры первого 9 и второго 10 нелинейных двухполюсников, например, так, как это сделано на чертеже фиг. 5.

Предлагаемый буферный усилитель может стать основой достаточно мощных выходных каскадов и драйверов, обеспечивающих быстрый перезаряд емкости нагрузки Сн при импульсном входном сигнале. Например, в схеме фиг. 6 при импульсном изменении Uвх паразитный конденсатор 30 в цепи истока первого 3 выходного полевого транзистора быстро заряжается через выходное сопротивление этого транзистора, что практически не приводит к задержке сигнала на базе выходного силового транзистора 24, который может обеспечить большие токи заряда конденсатора 29 (Сн). При отрицательном импульсе на входе 1 второй паразитный конденсатор 31 быстро заряжается через выходное сопротивление второго 6 выходного полевого транзистора, что позволяет получить значительные токи в нагрузке Сн. Аналогичными свойствами обладает и схема на чертеже фиг. 7.

Повышение быстродействия классических двухтактных буферных усилителей на комплементарных полевых транзисторах, содержащих в своей структуре входные истоковые повторители [1-29], ограничиваются сверху нелинейными процессами перезаряда паразитных конденсаторов в цепи базы выходных биполярных транзисторов. В заявляемом устройстве эта проблема не возникает.

Напряжение смещения нуля БУ на чертеже фиг. 4 определяется уравнением

Uсм = Uзи.3 – Uэб.16 ≈ Uзи.6 – Uэб.17,

где Uэб.16 и Uэб.17 – напряжения эмиттер-база транзисторов 16 и 17, входящих в структуру первого 9 и второго 10 нелинейных двухполюсников;

Uзи.3, Uзи.6 – напряжения затвор-исток первого 3 и второго 6 выходных полевых транзисторов.

За счет рационального построения первого 9 и второго 10 нелинейных двухполюсников (например, так, как это сделано на чертеже фиг. 5), а также изменения ширины канала первого 3 и второго 6 выходных полевых транзисторов можно получить Uсм на уровне 100 микровольт (фиг. 10).

Аналогичные результаты по Uсм могут быть получены при использовании в БУ КМОП транзисторов техпроцесса XFab (фиг. 16 и фиг.14). Моделирование данных схем показывает, что у КМОП БУ напряжение смещения нуля лежит в диапазоне десятков-сотен микровольт. При этом КМОП БУ обеспечивают верхнюю граничную частоту в гигагерцовом диапазоне частот (фиг. 12, фиг. 15), а их амплитудная характеристика при высокоомной нагрузке линейна при входных напряжениях, близких к напряжениям питания (фиг. 13, фиг.16).

При увеличении положительного напряжения на входе 1 (фиг. 4) приращение тока в нагрузке Rн обеспечивает первым 3 выходным транзистором через первый 9 нелинейный двухполюсник, обладающий относительно малым дифференциальным сопротивлением

где  – температурный потенциал,

– температурный потенциал,

I9 – статический ток первого 9 нелинейного двухполюсника (p-n перехода 16).

Как следствие, заявляемый БУ имеет относительно малые значения выходного сопротивления.

Следует особенно отметить, что заявляемый БУ обеспечивает более быстрый, чем БУ-прототип, а также БУ-аналоги, перезаряд емкости конденсатора нагрузки Сн. Это связано с тем, что при низком сопротивлении источника импульсного сигнала в его схеме не образуются нелинейные режимы перезаряда его паразитных конденсаторов (Ca, Cb, фиг. 1).

Таким образом, компьютерное моделирование в среде LTspice и оптимизация заявляемых схем БУ (фиг. 2 - фиг. 7) показывает, что предлагаемый буферный усилитель, схемотехника которого адаптирована на применение в диапазоне низких температур и воздействия проникающей радиации [30-32], имеет существенные достоинства в сравнении с известными вариантами построения БУ.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент US 6.215.357, fig. 3, 2001 г.

2. Патент US 5.351.012, 1994 г.

3. Патент US 5.973.534, 1999 г.

4. Патент US 5.197.124, fig. 25, 1993 г.

5. Патент US 7.764.123, fig. 3, 2010 г.

6. Патент US № 6.268.769 fig.3, 2001 г.

7. Патент US № 6.420.933, 2002 г.

8. Патент US № 5.223.122, 1993 г.

9. Патентная заявка US № 2004/0196101, 2004 г.

10. Патентная заявка US № 2005/0264358 fig.1, 2005 г.

11. Патентная заявка US № 2002/0175759, 2002 г.

12. Патент US № 5.049.653 fig.8, 1991 г.

13. Патент US № 4.837.523, 1989 г.

14. Патент US № 5.179.355, 1993 г.

15. Патент Японии JP 10.163.763, 1991 г.

16. Патент Японии JP 10.270.954, 1992 г.

17. Патент US № 5.170.134 fig.6, 1992 г.

18. Патент US № 4.540.950, 1985 г.

19. Патент US № 4.424.493, 1984 г.

20. Патент Японии JP 6310950, 2018 г.

21. Патент US № 5.378.938, 1995 г.

22. Патент US № 4.827.223, 1989 г.

23. Патент US № 6.160.451, 2000 г.

24. Патент US № 4.639.685, 1987 г.

25. А.св. СССР 1506512, 1986 г.

26. Патент US № 5.399.991, 1995 г.

27. Патент US № 6.542.032, 2003 г.

28. M. Djebbi, A. Assi and M. Sawan. An offset-compensated wide-bandwidth CMOS current-feedback operational amplifier // CCECE 2003 - Canadian Conference on Electrical and Computer Engineering. Toward a Caring and Humane Technology (Cat. No.03CH37436), 2003, pp. 73-76 vol.1. DOI: 10.1109/CCECE.2003.1226347

29. N.N. Prokopenko, A.S. Budyakov, J.M. Savchenko, S.V. Korneev. Maximum rating of Voltage Feedback and Current Feedback Operational Amplifiers in Linear and Nonlinear Modes // Proceeding of the Third International Conference on Circuits and Systems for Communications – ICCSC’06, Politehnica University, Bucharest, Romania: July 6-7, 2006, pp.149-154.

30. Элементная база радиационно-стойких информационно-измерительных систем: монография / Н.Н. Прокопенко, О.В. Дворников, С.Г. Крутчинский; под общ. Ред. Д.т.н. проф. Н.Н. Прокопенко; ФГБОУ ВПО «Южно-Рос. Гос. Ун-т экономики и сервиса». – Шахты: ФГБОУ ВПО «ЮРГУЭС», 2011. – 208 с.

31. O. V. Dvornikov, V. L. Dziatlau, N. N. Prokopenko, K. O. Petrosiants, N. V. Kozhukhov and V. A. Tchekhovski. The accounting of the simultaneous exposure of the low temperatures and the penetrating radiation at the circuit simulation of the BiJFET analog interfaces of the sensors // 2017 International Siberian Conference on Control and Communications (SIBCON), Astana, Kazakhstan, 2017, pp. 1-6. DOI: 10.1109/SIBCON.2017.7998507.

32. Проектирование низкотемпературных и радиационно-стойких аналоговых микросхем для обработки сигналов датчиков: монография / Н.Н. Прокопенко, О.В. Дворников, А.В. Бугакова. – М.: СОЛОН-Пресс, 2021. – 200 с.

| название | год | авторы | номер документа |

|---|---|---|---|

| БИПОЛЯРНО-ПОЛЕВОЙ БУФЕРНЫЙ УСИЛИТЕЛЬ | 2018 |

|

RU2677401C1 |

| ВЫХОДНОЙ КАСКАД BIJFET ОПЕРАЦИОННОГО УСИЛИТЕЛЯ | 2017 |

|

RU2668981C1 |

| БИПОЛЯРНО-ПОЛЕВОЙ АРСЕНИД-ГАЛЛИЕВЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ | 2023 |

|

RU2796638C1 |

| АРСЕНИД-ГАЛЛИЕВЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ | 2021 |

|

RU2771316C1 |

| Буферный усилитель для работы при низких температурах | 2018 |

|

RU2687161C1 |

| АРСЕНИД-ГАЛЛИЕВЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ | 2022 |

|

RU2784046C1 |

| БУФЕРНЫЙ УСИЛИТЕЛЬ НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ С УПРАВЛЯЮЩИМ P-N ПЕРЕХОДОМ ДЛЯ РАБОТЫ ПРИ НИЗКИХ ТЕМПЕРАТУРАХ | 2018 |

|

RU2684489C1 |

| ДВУХТАКТНЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ НА КОМПЛЕМЕНТАРНЫХ БИПОЛЯРНЫХ ТРАНЗИСТОРАХ | 2022 |

|

RU2786191C1 |

| БИПОЛЯРНО-ПОЛЕВОЙ БУФЕРНЫЙ УСИЛИТЕЛЬ ДЛЯ РАБОТЫ ПРИ НИЗКИХ ТЕМПЕРАТУРАХ | 2018 |

|

RU2670777C9 |

| ДВУХТАКТНЫЙ АРСЕНИД-ГАЛЛИЕВЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ С МАЛОЙ ЗОНОЙ НЕЧУВСТВИТЕЛЬНОСТИ АМПЛИТУДНОЙ ХАРАКТЕРИСТИКИ | 2022 |

|

RU2789482C1 |

Изобретение относится к области аналоговой микроэлектроники. Технический результат: создание усилителя, обеспечивающего малые значения систематической составляющей напряжения смещения нуля, малые входные токи, а также высокое быстродействие. Для этого предложен быстродействующий двухтактный буферный усилитель на комплементарных полевых транзисторах, который содержит вход (1) и выход (2) устройства, первый (3) выходной полевой транзистор, первый (4) токовый выход устройства, первую (5) шину источника питания, второй (6) выходной полевой транзистор, второй (7) токовый выход устройства, вторую (8) шину источника питания, первый (9) и второй (10) нелинейные двухполюсники. Затворы первого (3) и второго (6) выходных полевых транзисторов соединены со входом (1) устройства, исток первого (3) выходного полевого транзистора связан с выходом (2) устройства через первый (9) нелинейный двухполюсник, а исток второго (6) выходного полевого транзистора связан с выходом (2) устройства через второй (10) нелинейный двухполюсник. 7 з.п. ф-лы, 16 ил.

1. Быстродействующий двухтактный буферный усилитель на комплементарных полевых транзисторах, содержащий вход (1) и выход (2) устройства, первый (3) выходной полевой транзистор, исток которого связан с выходом (2) устройства, а сток соединен с первым (4) токовым выходом устройства, согласованным с первой (5) шиной источника питания, второй (6) выходной полевой транзистор, исток которого связан с выходом (2) устройства, а сток соединен со вторым (7) токовым выходом устройства, согласованным со второй (8) шиной источника питания, первый (9) и второй (10) нелинейные двухполюсники, отличающийся тем, что затворы первого (3) и второго (6) выходных полевых транзисторов соединены со входом (1) устройства, исток первого (3) выходного полевого транзистора связан с выходом (2) устройства через первый (9) нелинейный двухполюсник, а исток второго (6) выходного полевого транзистора связан с выходом (2) устройства через второй (10) нелинейный двухполюсник.

2. Быстродействующий двухтактный буферный усилитель на комплементарных полевых транзисторах по п. 1, отличающийся тем, что в качестве первого (3) и второго (6) выходных полевых транзисторов используются КМОП полевые транзисторы со встроенным каналом, причем первый (9) и второй (10) нелинейные двухполюсники выполнены на первом (11) и втором (12) КМОП транзисторах с индуцированным каналом, затвор первого (11) КМОП транзистора с индуцированным каналом связан с его стоком, а затвор второго (12) КМОП транзистора с индуцированным каналом подключен к его стоку.

3. Быстродействующий двухтактный буферный усилитель на комплементарных полевых транзисторах по п. 1, отличающийся тем, что в качестве первого (9) и второго (10) нелинейных двухполюсников используются первый (14) и второй (15) биполярные транзисторы, причем база первого (14) биполярного транзистора соединена с его коллектором, а база второго (15) биполярного транзистора подключена к его коллектору.

4. Быстродействующий двухтактный буферный усилитель на комплементарных полевых транзисторах по п. 1, отличающийся тем, что в качестве первого (3) и второго (6) выходных полевых транзисторов используются полевые транзисторы с управляющим p-n-переходом.

5. Быстродействующий двухтактный буферный усилитель на комплементарных полевых транзисторах по п. 4, отличающийся тем, что первый (9) нелинейный двухполюсник выполнен в виде первого (16) прямосмещенного p-n-перехода на биполярном транзисторе, база которого соединена с коллектором, а второй (10) нелинейный двухполюсник реализован в виде второго (17) прямосмещенного p-n-перехода на биполярном транзисторе, база которого соединена с коллектором.

6. Быстродействующий двухтактный буферный усилитель на комплементарных полевых транзисторах по п. 4, отличающийся тем, что первый (9) нелинейный двухполюсник выполнен на основе первого (18) и второго (19) вспомогательных биполярных транзисторах, причем база первого (18) вспомогательного биполярного транзистора соединена с его коллектором и подключена к коллектору второго (19) вспомогательного биполярного транзистора, а эмиттер первого (18) вспомогательного биполярного транзистора соединен с базой второго (19) вспомогательного биполярного транзистора, кроме этого второй (10) нелинейный двухполюсник выполнен на третьем (20), четвертом (21) и пятом (22) вспомогательных биполярных транзисторах, причем база третьего (20) вспомогательного биполярного транзистора соединена с его коллектором и подключена к коллектору четвертого (21) вспомогательного биполярного транзистора, эмиттер третьего (20) вспомогательного биполярного транзистора подключен к базе четвертого (21) вспомогательного биполярного транзистора, а эмиттер четвертого (21) вспомогательного биполярного транзистора соединен с коллектором и базой пятого (22) вспомогательного биполярного транзистора.

7. Быстродействующий двухтактный буферный усилитель на комплементарных полевых транзисторах по п. 3, отличающийся тем, что устройство содержит вспомогательный потенциальный выход (23), который связан с эмиттерами первого (24) и второго (25) дополнительных выходных биполярных транзисторов, коллектор первого (24) дополнительного выходного биполярного транзистора подключен к первому (4) токовому выходу устройства, коллектор второго (25) дополнительного выходного биполярного транзистора соединен со вторым (7) токовым выходом устройства, база первого (24) дополнительного выходного биполярного транзистора соединена с истоком первого (3) входного полевого транзистора со встроенным каналом, база второго (25) дополнительного выходного биполярного транзистора подключена к истоку второго (6) выходного полевого транзистора со встроенным каналом, а между выходом (2) устройства и вспомогательным потенциальным выходом (23) включены два встречно-параллельно включенных вспомогательных p-n-перехода (26) и (27).

8. Быстродействующий двухтактный буферный усилитель на комплементарных полевых транзисторах по п. 3, отличающийся тем, что устройство содержит вспомогательный потенциальный выход (23), который связан с эмиттерами первого (24) и второго (25) дополнительных выходных биполярных транзисторов, коллектор первого (24) дополнительного выходного биполярного транзистора подключен к первому (4) токовому выходу устройства, коллектор второго (25) дополнительного выходного биполярного транзистора соединен со вторым (7) токовым выходом устройства, база первого (24) дополнительного выходного биполярного транзистора соединена с истоком первого (3) входного полевого транзистора со встроенным каналом, база второго (25) дополнительного выходного биполярного транзистора подключена к истоку второго (6) выходного полевого транзистора со встроенным каналом, а между выходом (2) устройства и вспомогательным потенциальным выходом (23) включен согласующий резистор (32).

| US 5497124 A1, 05.03.1996 | |||

| КОМПЛЕМЕНТАРНЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ | 2011 |

|

RU2444115C1 |

| БУФЕРНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2409889C1 |

| БУФЕРНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2401509C1 |

Авторы

Даты

2022-11-23—Публикация

2022-08-13—Подача