Изобретение относится к области микроэлектроники и может быть использовано в качестве выходного каскада различных аналоговых устройств, в т.ч. операцонных усилителей (ОУ), допускающих работу в условиях воздействия проникающей радиации, низких и высоких температур.

Известно значительное количество схем неинвертирующих выходных каскадов (НВК) и буферных усилителей (БУ) аналоговых микроэлектронных изделий, которые реализуются на биполярных (BJT) и полевых (JFet, КМОП, КНИ, КНС и др.) транзисторах, а также при их совместном включении [1-24].

Во многих применениях схема выходного каскада адаптируется под конкретные технологические процессы и внешние воздействующие факторы, т.к. только в этом случае обеспечивается реализация предельных параметров микроэлектронного устройства.

В настоящее время в российской и зарубежной микроэлектронике уделяется повышенное внимание арсенид-галлиевым микросхемам. Данное направление создания электронной компонентной базы относится к числу наиболее перспективных в задачах космического приборостроения. Однако, особенности арсенид-галлиевых технологических процессов накладывают существенные ограничения на типы реализуемых транзисторов и их характеристики. Так, например, арсенид-галлиевые технологические процессы, разработанные фирмами США [25-28], а также исследуемые Минским научно-исследовательским институтом радиоматериалов (https://mniirm.by/), ориентированы на изготовление аналоговых схем, содержащих только полевые GaAs транзисторы с управляющим pn-переходом и гетеропереходные биполярные GaAs p-n-p транзисторы. Применение других полупроводниковых приборов не допускается. Это накладывает существенные ограничения на схемотехнику аналоговых устройств, ориентированных на данный технологический процесс.

Ближайшим прототипом (фиг. 1) заявляемого устройства является GaAs инвертирующий выходной каскад, представленный в статье «Itakura K. et al. A GaAs Bi-FET technology for large scale integration //International Technical Digest on Electron Devices Meeting. – IEEE, 1989. – С. 389-392. (фиг. 7)». Он содержит (фиг. 1) вход 1 и выход 2 устройства, входной 3 полевой транзистор с управляющим pn-переходом, затвор которого соединен со входом 1 устройства, а сток подключен к затвору вспомогательного 4 полевого транзистора с управляющим pn-переходом и связан с его истоком, причем сток вспомогательного 4 полевого транзистора с управляющим pn-переходом соединен с первой 5 шиной источника питания, первый 6 выходной биполярный транзистор, база которого соединена с истоком вспомогательного 4 полевого транзистора с управляющим pn-переходом, второй 7 выходной биполярный транзистор, база которого связана со входом 1 устройства, согласующий резистор 8, вторую 9 шину источника питания.

Существенный недостаток выходного каскада – прототипа состоит в том, что он не работает в режиме неинвертирующего повторителя напряжения. Это значительно сужает области его практического использования, т.к. для многих архитектур операционных усилителей необходимы выходные каскады с коэффициентом передачи по напряжению, близким к единице.

Основная задача предполагаемого изобретения состоит в создании неинвертирующего выходного каскада арсенид-галлиевого операционного усилителя, реализуемого только на JFET арсенид-галлиевых полевых транзисторах с управляющим pn-переходом и биполярных GaAs p-n-p транзисторах, который имеет коэффициент передачи по напряжению, близкий к единице, малый статический ток потребления, а также обеспечивает в относительно низкоомной нагрузке токи двух направлений.

Поставленная задача достигается тем, что в выходном каскаде фиг. 1, содержащем вход 1 и выход 2 устройства, входной 3 полевой транзистор с управляющим pn-переходом, затвор которого соединен со входом 1 устройства, а сток подключен к затвору вспомогательного 4 полевого транзистора с управляющим pn-переходом и связан с его истоком, причем сток вспомогательного 4 полевого транзистора с управляющим pn-переходом соединен с первой 5 шиной источника питания, первый 6 выходной биполярный транзистор, база которого соединена с истоком вспомогательного 4 полевого транзистора с управляющим pn-переходом, второй 7 выходной биполярный транзистор, база которого связана со входом 1 устройства, согласующий резистор 8, вторую 9 шину источника питания, предусмотрены новые связи - сток входного 3 полевого транзистора связан с истоком вспомогательного 4 полевого транзистора с управляющим pn-переходом и базой первого 6 выходного биполярного транзистора через согласующий резистор 8, а исток подключен к выходу 2 устройства, эмиттер первого 6 выходного биполярного транзистора соединен с первой 5 шиной источника питания, а его коллектор подключен к выходу 2 устройства, причем эмиттер второго 7 выходного биполярного транзистора связан с выходом 2 устройства, а его коллектор подключен ко второй 9 шине источника питания.

На чертеже фиг. 1 показана схема выходного каскада – прототипа.

На чертеже фиг. 2 представлена схема заявляемого НВК в соответствии с формулой изобретения.

На чертеже фиг. 3 приведена схема для моделирования GaAs НВК фиг. 2 в среде LTspice при t=27 oC, +Vcc=-Vee=10 В, R1=10кОм, Rload=1 МОм на моделях JFET транзисторов со следующей шириной и длиной канала: 10u/0.2u.

На чертеже фиг. 4 показана амплитудная характеристика GaAs НВК фиг. 3.

На чертеже фиг.5 представлена схема для моделирования GaAs НВК фиг. 2 в среде LTspice при t=27 oC, +Vcc=-Vee=10 В, R1=10кОм, Rload=1 МОм на JFET транзисторах с параметрами 100u/0.2u и биполярных транзисторах VT3, VT5, включенных по схеме Дарлингтона.

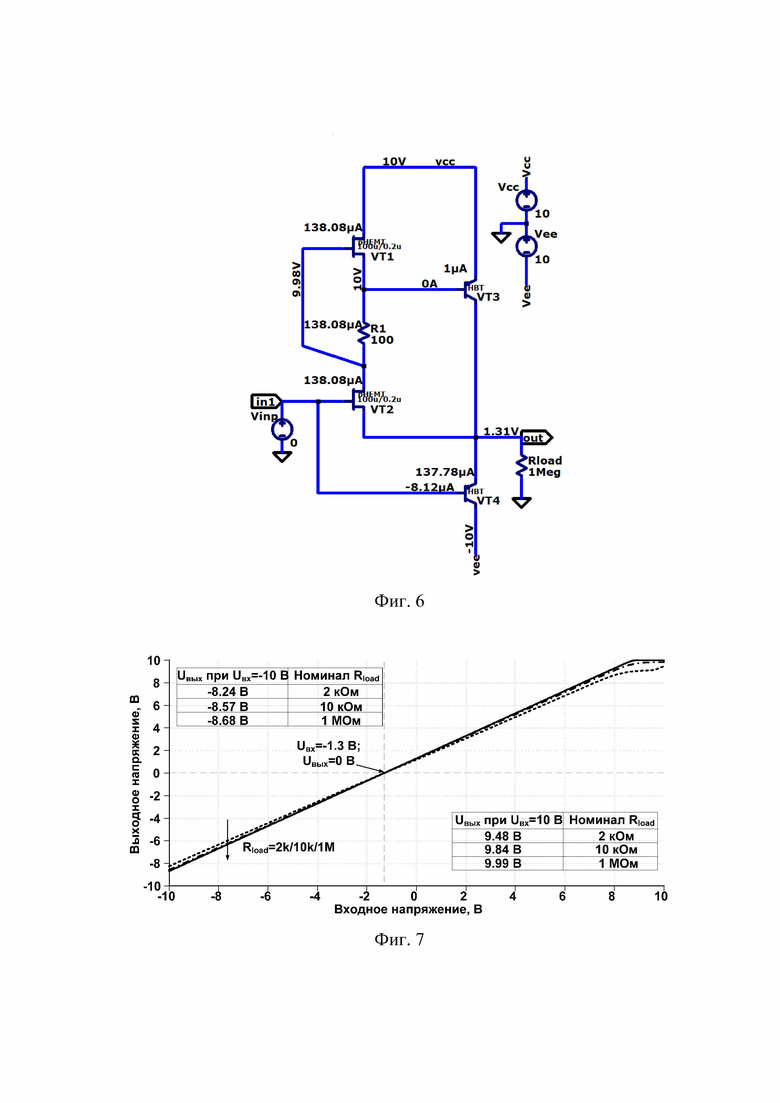

На чертеже фиг. 6 приведена схема для моделирования GaAs НВК фиг. 2 в среде LTspice при t=27 oC, +Vcc=-Vee=10 В, Rload=1 МОм на JFET транзисторах с параметрами 100u/0.2u при низкоомном резисторе R1=100 Ом.

На чертеже фиг. 7 показана амплитудная характеристика GaAs НВК фиг. 6 при разных сопротивлениях нагрузки (Rload=2 КОм ÷ 1 МОм).

На чертеже фиг. 8 представлена логарифмическая амплитудно-частотная характеристика НВК фиг. 6, которая показывает, что коэффициент передачи по напряжению предлагаемой схемы незначительно отличается от единицы в диапазоне частот до единиц-десятков гигагерц.

Неинвертирующий выходной каскад арсенид-галлиевого операционного усилителя фиг. 2 содержит вход 1 и выход 2 устройства, входной 3 полевой транзистор с управляющим pn-переходом, затвор которого соединен со входом 1 устройства, а сток подключен к затвору вспомогательного 4 полевого транзистора с управляющим pn-переходом и связан с его истоком, причем сток вспомогательного 4 полевого транзистора с управляющим pn-переходом соединен с первой 5 шиной источника питания, первый 6 выходной биполярный транзистор, база которого соединена с истоком вспомогательного 4 полевого транзистора с управляющим pn-переходом, второй 7 выходной биполярный транзистор, база которого связана со входом 1 устройства, согласующий резистор 8, вторую 9 шину источника питания. Сток входного 3 полевого транзистора связан с истоком вспомогательного 4 полевого транзистора с управляющим pn-переходом и базой первого 6 выходного биполярного транзистора через согласующий резистор 8, а исток подключен к выходу 2 устройства, эмиттер первого 6 выходного биполярного транзистора соединен с первой 5 шиной источника питания, а его коллектор подключен к выходу 2 устройства, причем эмиттер второго 7 выходного биполярного транзистора связан с выходом 2 устройства, а его коллектор подключен ко второй 9 шине источника питания. На чертеже фиг. 2 двухполюсник 10 моделирует свойства нагрузки Rн.

Рассмотрим работу предлагаемого неинвертирующего выходного каскада фиг. 2.

Особенность схемы фиг. 2 состоит в том, что благодаря отрицательной обратной связи по цепи «выход 2 устройства - исток входного 3 полевого транзистораа с управляющим pn-переходом – сток входного 3 полевого транзистораа с управляющим pn-переходом – затвор вспомогательного 4 полевого транзистора с управляющим pn-переходом – база первого 6 выходного биполярного транзистора – коллектор первого 6 выходного биполярного транзистора» здесь устанавливается ток стока входного 3 полевого транзистора с управляющим pn-переходом, который определяется сопротивлением согласующего резистора 8:

где  – напряжение затвор-исток вспомогательного 4 полевого транзистора с управляющим pn-переходом при токе стока, равном I0.

– напряжение затвор-исток вспомогательного 4 полевого транзистора с управляющим pn-переходом при токе стока, равном I0.

При высокоомной нагрузке Rн ток эмиттера второго 7 выходного биполярного транзистора имеет две составляющие

Iэ7 = Is3 + Iк6,

где Iк6 – ток коллектора первого 6 выходного биполярного транзистора.

За счет рационального выбора ширины канала входного 3 полевого транзистора с управляющим pn-переходом и геометрических параметров гетеропереходного арсенид-галлиевого выходного биполярного транзистора 7 можно обеспечить малые (микроамперные) значения Iк6. В этом случае ток потребления схемы фиг. 2 будет определяться сопротивлением согласующего резистора 8 и может измеряться десятками микроампер (см. фиг. 3).

Результаты компьютерного моделирования схем фиг. 3, фиг. 5 и фиг. 6, представленные на чертежах фиг. 4 и фиг. 7, показывают, что рассматриваемая схема НВК обеспечивает двуполярное изменение тока в нагрузке при относительно малых статических токах ее активных элементов и характеризуется коэффициентом передачи по напряжению, близким к единице. При этом величина сопротивления согласующего резистора 8 влияет на максимальные значения выходного напряжения НВК при положительных и отрицательных входных напряжениях и может выбираться по усмотрению разработчика.

Таким образом, заявляемое устройство имеет существенные преимущества в сравнении с выходном каскадом - прототипом.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент RU № 2523947 fig. 4, 2014 г.

2. Патент WO 2007135139, 2007 г.

3. Патент US 4743862, 1988 г.

4. Патент US 6433638, fig. 1a-2, 2002 г.

5. Патентная заявка US 20050253653, 2005 г.

6. Патент US 4825174, fig. 3, fig. 6, 1989 г.

7. Патент RU 2099856, fig. 3, 1997 г.

8. Патент US 4904953, fig. 2, 1990 г.

9. Патент US 7896339, fig. 4, 2011 г.

10. Патент US 6342814, 2002 г.

11. Патентная заявка US 2010/0182086, 2010 г.

12. Патент US 5387880, fig. 1, 1995 г.

13. Патент US 4598253, 1986 г.

14. Патент US 4667165, fig. 2, 1987 г.

15. Патент US 4596958, 1986 г.

16. Патент US 7116172, fig. 4, fig. 5, 2006 г.

17. Патент US 5648743, 1997 г.

18. Патент US 5367271, fig. 2, 1994 г.

19. Патентная заявка US 2000/0112075, fig. 3, 2000 г.

20. Патент US 5065043, fig. 1f, 1991 г.

21. Патентная заявка US 2007/0115056, fig. 2, 2007 г.

22. Патент US 7548117, fig. 5, 2009 г.

23. Патент EP 0 293486 B1, fig. 5, 1991 г.

24. Патент US 4420726, fig. 1 – fig. 3, 1983 г.

25. M. Fresina, "Trends in GaAs HBTs for wireless and RF," 2011 IEEE Bipolar/BiCMOS Circuits and Technology Meeting, Atlanta, GA, USA, 2011, pp. 150-153. doi: 10.1109/BCTM.2011.6082769.

26. P. J. Zampardi, M. Sun, C. Cismaru and J. Li, "Prospects for a BiCFET III-V HBT Process," 2012 IEEE Compound Semiconductor Integrated Circuit Symposium (CSICS), La Jolla, CA, USA, 2012, pp. 1-3. doi: 10.1109/CSICS.2012.6340116.

27. W. Liu, D. Hill, D. Costa and J. S. Harris, "High-performance microwave AlGaAs-InGaAs Pnp HBT with high-DC current gain," in IEEE Microwave and Guided Wave Letters, vol. 2, no. 8, pp. 331-333, Aug. 1992. doi: 10.1109/75.153604.

28. Peatman W. et al. InGaP-Plus™: advanced GaAs BiFET technology and applications // CS MANTECH Conference, May 14-17, 2007, Austin, Texas, USA. pp. 243-246.

| название | год | авторы | номер документа |

|---|---|---|---|

| АРСЕНИД-ГАЛЛИЕВЫЙ ВЫХОДНОЙ КАСКАД УСИЛИТЕЛЯ МОЩНОСТИ | 2021 |

|

RU2767976C1 |

| АРСЕНИД-ГАЛЛИЕВЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ | 2021 |

|

RU2766868C1 |

| ДВУХТАКТНЫЙ АРСЕНИД-ГАЛЛИЕВЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ С МАЛОЙ ЗОНОЙ НЕЧУВСТВИТЕЛЬНОСТИ АМПЛИТУДНОЙ ХАРАКТЕРИСТИКИ | 2022 |

|

RU2789482C1 |

| Арсенид-галлиевый операционный усилитель для работы в широком диапазоне температур | 2023 |

|

RU2814685C1 |

| АРСЕНИД-ГАЛЛИЕВЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ n-КАНАЛЬНЫХ ПОЛЕВЫХ И p-n-p БИПОЛЯРНЫХ ТРАНЗИСТОРОВ | 2022 |

|

RU2784376C1 |

| АРСЕНИД-ГАЛЛИЕВЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ | 2021 |

|

RU2771316C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ НА АРСЕНИД-ГАЛЛИЕВЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ | 2021 |

|

RU2770912C1 |

| АРСЕНИД-ГАЛЛИЕВЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ НА ПОЛЕВЫХ И БИПОЛЯРНЫХ P-N-P ТРАНЗИСТОРАХ | 2022 |

|

RU2788498C1 |

| АРСЕНИД-ГАЛЛИЕВЫЙ ВХОДНОЙ ДИФФЕРЕНЦИАЛЬНЫЙ КАСКАД КЛАССА АВ БЫСТРОДЕЙСТВУЮЩЕГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ | 2022 |

|

RU2786943C1 |

| БИПОЛЯРНО-ПОЛЕВОЙ АРСЕНИД-ГАЛЛИЕВЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ | 2023 |

|

RU2796638C1 |

Изобретение может быть использовано в качестве выходного каскада операционных усилителей. Технический результат: обеспечение коэффициента передачи по напряжению, близкого к единице, малого статического тока потребления, а также обеспечение в относительно низкоомной нагрузке токов двух направлений. Для этого предложен неинвертирующий выходной каскад арсенид-галлиевого операционного усилителя, который содержит вход (1) и выход (2), входной (3) полевой транзистор, вспомогательный (4) полевой транзистор, первую (5) шину, первый (6) выходной биполярный транзистор, второй (7) выходной биполярный транзистор, согласующий резистор (8), вторую (9) шину. Сток входного (3) полевого транзистора связан с истоком вспомогательного (4) полевого транзистора и базой первого (6) выходного биполярного транзистора через согласующий резистор (8), а исток подключен к выходу (2), эмиттер первого 6 выходного биполярного транзистора соединен с первой (5) шиной, а его коллектор подключен к выходу (2) устройства, причем эмиттер второго (7) выходного биполярного транзистора связан с выходом (2) устройства, а его коллектор подключен ко второй (9) шине. 8 ил.

Неинвертирующий выходной каскад арсенид-галлиевого операционного усилителя, содержащий вход (1) и выход (2) устройства, входной (3) полевой транзистор с управляющим pn-переходом, затвор которого соединен со входом (1) устройства, а сток подключен к затвору вспомогательного (4) полевого транзистора с управляющим pn-переходом и связан с его истоком, причем сток вспомогательного (4) полевого транзистора с управляющим pn-переходом соединен с первой (5) шиной источника питания, первый (6) выходной биполярный транзистор, база которого соединена с истоком вспомогательного (4) полевого транзистора с управляющим pn-переходом, второй (7) выходной биполярный транзистор, база которого связана со входом (1) устройства, согласующий резистор (8), вторую (9) шину источника питания, отличающийся тем, что сток входного (3) полевого транзистора связан с истоком вспомогательного (4) полевого транзистора с управляющим pn-переходом и базой первого (6) выходного биполярного транзистора через согласующий резистор (8), а исток подключен к выходу (2) устройства, эмиттер первого 6 выходного биполярного транзистора соединен с первой (5) шиной источника питания, а его коллектор подключен к выходу (2) устройства, причем эмиттер второго (7) выходного биполярного транзистора связан с выходом (2) устройства, а его коллектор подключен ко второй (9) шине источника питания.

| ITAKURA K | |||

| et al | |||

| "A GaAs Bi-FET technology for large scale integration", International Technical Digest on Electron Devices Meeting IEEE, 1989, стр | |||

| Гидравлический подъемник | 1922 |

|

SU389A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Двухтактный усилитель | 1983 |

|

SU1092701A1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ "ПЕРЕГНУТОГО" КАСКОДА | 2008 |

|

RU2391768C2 |

| US 5455535 A1, 03.10.1995. | |||

Авторы

Даты

2022-11-23—Публикация

2022-08-13—Подача