Изобретение относится к области вычислительной техники, к структуре вычислительных блоков микропроцессоров, а именно к векторным мультиформатным умножителям, и может быть использовано для вычисления произведений чисел с фиксированной и плавающей точкой разных типов, произведений с накоплением, комплексных произведений и сумм произведений в одном микропроцессоре.

Для решения задач цифровой обработки информации одной из ключевых операций является операция умножения, а также основанные на ней операции комплексного умножения, умножения с накоплением и различные суммы произведений. Эти операции необходимы для вычисления преобразований Фурье, фильтров и произведений матриц, что, в свою очередь, является основой решения задач коммуникации, обработки изображений и видео, а также сверточных нейронных сетей. Таким образом, производительность операций умножения является основой быстрого решения важнейших задач цифровой обработки информации.

При традиционном подходе к разработке вычислительных блоков микропроцессора, для вычисления произведений разных типов используют отдельные аппаратные блоки. Так, отдельные блоки используют для вычисления произведений чисел с фиксированной точкой разрядностью 32 бита, чисел с фиксированной точкой разрядностью 64 бита, чисел с плавающей точкой одинарной точности и чисел с плавающей точкой двойной точности. Учитывая то, что операции вычисления произведений разных типов редко выполняют одновременно, а также то, что блоки умножения являются весьма затратными аппаратными ресурсами микропроцессора, подобный подход ведет к увеличению площади устройства (микропроцессора) и низкому коэффициенту повторного использования, то есть простою аппаратуры.

В патенте CN 106951211 (А) описан мультиформатный умножитель принцип действия которого заключается в вычислении произведений большей разрядности на основе умножителей меньшей разрядности.

Недостатком данного мультиформатного умножителя является то, что его функциональность ограничена вычислением произведений чисел с фиксированной точкой (12 бит и 24 бита) и произведением чисел с плавающей точкой одинарной точности, при этом отсутствует возможность вычисления произведений чисел с плавающей точкой половинной и двойной точности, а также возможности осуществления умножений с накоплением и сумм произведений.

Известен из патента CN 105607889 (А) мультиформатный умножитель, в котором реализован принцип вычисления произведений большей разрядности на основе умножителей меньшей разрядности, а также решены задачи вычисления произведений чисел с фиксированной точкой (32 бита и 64 бита) и плавающей точкой (одинарной и двойной точности), осуществления умножения с накоплением, комплексного умножения и вычисления сумм произведений. Кроме того, данный умножитель позволяет одновременного выполнять две независимые операции для 32-разрядных операндов.

Недостатком данного мультиформатного умножителя является его ограниченная функциональность, вследствие отсутствия возможности вычисления произведений чисел с фиксированной точкой размерами 8 бит и 16 бит, а также вычисления произведений чисел с плавающей точкой половинной точности.

Наиболее близким к заявленному изобретению является векторный мультиформатный умножитель, описанный в заявке US 2013138711 (А1), в котором реализован принцип вычисления произведений большей разрядности на основе умножителей меньшей разрядности, осуществлена задача вычисления произведений чисел с фиксированной точкой разных типов (8 бит, 16 бит и 32 бита) в одном устройстве. Данный векторный мультиформатный умножитель выбран в качестве прототипа заявленного изобретения.

Недостатком векторного мультиформатного умножителя прототипа является его ограниченная функциональность, вследствие отсутствия возможности вычисления произведений 64-разрядных чисел с фиксированной точкой, чисел с плавающей точкой двойной точности, а также вычисления сумм произведений чисел с плавающей точкой половинной и одинарной точности.

Техническим результатом заявленного изобретения является создание векторного мультиформатного умножителя с увеличенной функциональностью и с уменьшенной занимаемой площадью, за счет использования вычислительных блоков малой разрядности с меньшей суммарной занимаемой площадью, чем площадь вычислительных блоков высокой разрядности, а именно за счет использования массива из шестнадцати 16-разрядных целочисленных умножителей и дерева сумматоров, которые позволяют вычислять произведения чисел с фиксированной точкой размером 8, 16, 32 и 64 бита, а также различные суммы этих произведений, а также за счет использования блоков формирования произведений чисел с плавающей точкой и сумматоров чисел с плавающей точкой половинной, одинарной и двойной точности, которые позволяют вычислять произведения чисел с плавающей точкой половинной, одинарной и двойной точности и различные суммы этих произведений чисел, что позволяет принимать на вход векторного мультиформатного умножителя до четырех 64-разрядных операндов и выполнять над ними одновременно до двух команд, при этом записывать результат в регистровый файл или в регистры-аккумуляторы.

Поставленный технический результат достигнут путем создания векторного мультиформатного умножителя, содержащего массив размерности 4×4 из 16-разрядных целочисленных умножителей 11, входящих в состав 64-разрядного блока 30 целочисленного умножения, два декодера команд 50, 51 и мультиплексор 52, входы которых являются входами векторного мультиформатного умножителя, а выходы которых соединены с входами 64-разрядного блока 53 целочисленного умножения, выходы которого соединены с входами двух блоков 54, 56 преобразования результата с фиксированной точкой и двух блоков 55, 57, преобразования результата с плавающей точкой, выходы которых соединены с входами мультиплексоров результата 58, 59, причем выход первого мультиплексора результата 59 является выходом векторного мультиформатного умножителя, а выход второго мультиплексора результата 58 является выходом векторного мультиформатного умножителя, а также соединен с первым входом блока 60 накопления результата в регистрах-аккумуляторах, второй вход которого является входом векторного мультиформатного умножителя, а выход которого является выходом векторного мультиформатного умножителя, при этом

- 16-разрядный целочисленный умножитель 11 выполнен с возможностью получения на входы двух 16-разрядных операндов и формирования на выходе целочисленного произведения этих операндов;

- 64-разрядный блок 53 целочисленного умножения выполнен с возможностью получения на вход двух массивов размерности 4×4 из 16-разрядных операндов и формирования на выходе двух 128-разрядных упакованных результатов целочисленных умножений и двух 64-разрядных упакованных результатов умножений с плавающей точкой;

- декодеры команд 51, 52 выполнены с возможностью декодирования команд и настройки 64-разрядного блока 53 целочисленного умножения с целью корректного выполнения этих комманд;

- мультиплексор 52 выполнен с возможностью приема на вход четырех 64-разрядных операндов, преобразования их в соответствии с текущей командой в два массива размерности 4×4 из 16-разрядных операндов и передачи их в 64-разрядный блок 53 целочисленного умножения;

- блоки 54, 56 преобразования результата с фиксированной точкой и блоки 55, 57 преобразования результата с плавающей точкой выполнены с возможностью формирования окончательных результатов команд, и передачи их через мультиплексоры результата 59, 60 на выходы векторного мультиформатного умножителя;

- блок 61 накопления результата в регистрах-аккумуляторах выполнен с возможностью сложения результата команды с содержимым регистров-аккумуляторов и передачи результата сложения на выход векторного мультиформатного умножителя.

В предпочтительном варианте осуществления векторного мультиформатного умножителя 64-разрядный блок 30 целочисленного умножения содержит демультиплексор 31 входных данных, входы которого являются входами векторного мультиформатного умножителя, а выходы которого соединены с входами четырех 32-разрядных блоков 32-35 целочисленного умножения, выходы которых соединены с входами 64-разрядного сумматора 36 чисел с фиксированной точкой, с входами двух 32-разрядных сумматоров 37, 38 чисел с плавающей точкой одинарной точности и с входами четырех 16-разрядных сумматоров 39-42 чисел с плавающей точкой половинной точности, причем выход 64-разрядного сумматора чисел с фиксированной точкой является первым выходом 64-разрядного блока 30 целочисленного умножения, а также соединен с одним входом 64-разрядного блока 43 формирования произведения с плавающей точкой двойной точности, выход которого соединен с одним входом блока 44 упаковки произведений с плавающей точкой, остальные входы которого соединены с выходами двух 32-разрядных сумматоров 37, 38 чисел с плавающей точкой одинарной точности и с входами четырех 16-разрядных сумматоров 39-42 чисел с плавающей точкой половинной точности, а выход блока 44 упаковки произведений с плавающей точкой является вторым выходом 64-разрядного блока 30 целочисленного умножения, при этом

- демультиплексор 31 входных данных выполнен с возможностью распределения входных данных на 32-разрядные блоки 32-35 целочисленного умножения;

- сумматор 36 чисел с фиксированной точкой выполнен с возможностью получения на вход целочисленных произведений 32-разрядных чисел и вычисления на их основе произведений 64-разрядных чисел, сумм произведений 32-разрядных чисел, сумм произведений 16-разрядных чисел, а также пропускания на выход целочисленных произведений 32-разрядных чисел;

- сумматоры 39-42 чисел с плавающей точкой половинной точности, выполнены с возможностью получения на вход попарно произведений с плавающей точкой половинной точности и вычисления на их основе сумм произведений, а также пропускания дальше одного из операндов;

- блок 43 формирования произведений чисел с плавающей точкой выполнен с возможностью вычисления произведения чисел с плавающей точкой на основе целочисленного произведения мантисс, которое вычисляется на общем массиве 16-разрядных целочисленных умножителей 11.

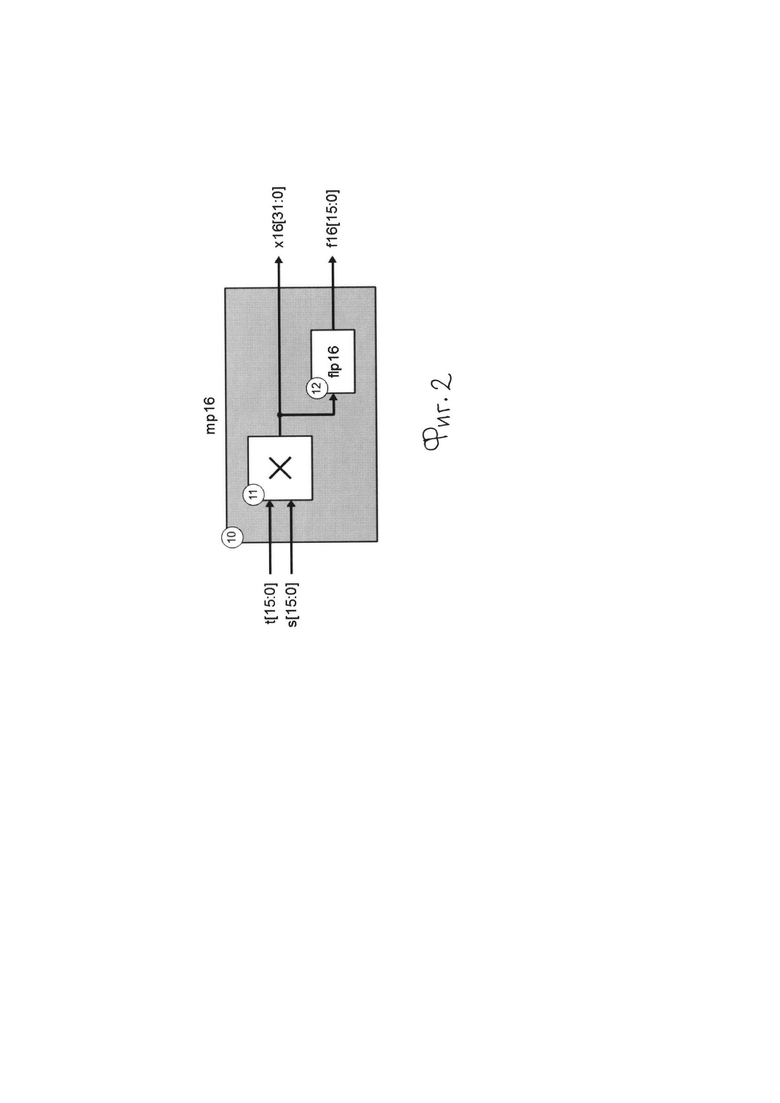

В предпочтительном варианте осуществления векторного мультиформатного умножителя 32-разрядный блок 20 целочисленного умножения содержит демультиплексор 21 входных данных, входы которого являются входами векторного мультиформатного умножителя, а выходы которого соединены с входами четырех 16-разрядных блоков 22 -25 целочисленного умножения, выходы которых соединены с входами 32-разрядного сумматора 26 чисел с фиксированной точкой, с входами двух 16-разрядных сумматоров 27,28 чисел с плавающей точкой половинной точности, причем выход 32-разрядного сумматора 26 чисел с фиксированной точкой является первым выходом 32-разрядного блока 20 целочисленного умножения, а также соединен с одним входом 32-разрядного блока 29 формирования произведения с плавающей точкой одинарной точности, выход которого является вторым выходом 32-разрядного блока 20 целочисленного умножения, а выходы двух 16-разрядных сумматоров 27,28 чисел с плавающей точкой половинной точности являются третьим и четвертым выходами 32-разрядного блока 20 целочисленного умножения, при этом

- демультиплексор 21 входных данных выполнен с возможностью распределения входных данных на 16-разрядные блоки 22-25 целочисленного умножения;

- сумматор 26 чисел с фиксированной точкой выполнен с возможностью получения на вход целочисленных произведений 16-разрядных чисел и вычисления на их основе произведений 32-разрядных чисел, сумм произведений 16-разрядных чисел, пропускания на выход целочисленных произведений 16-разрядных чисел, а также упаковки и пропускания на выход двух произведений 16-разрядных чисел;

- сумматоры 27, 28 чисел с плавающей точкой половинной точности, выполнены с возможностью получения на вход попарно произведений с плавающей точкой половинной точности и вычисления на их основе сумм произведений, а также пропускания дальше одного из операндов;

- блок 29 формирования произведений чисел с плавающей точкой выполнен с возможностью вычисления произведения чисел с плавающей точкой на основе целочисленного произведения мантисс, которое вычисляется на общем массиве 16-разрядных целочисленных умножителей 11.

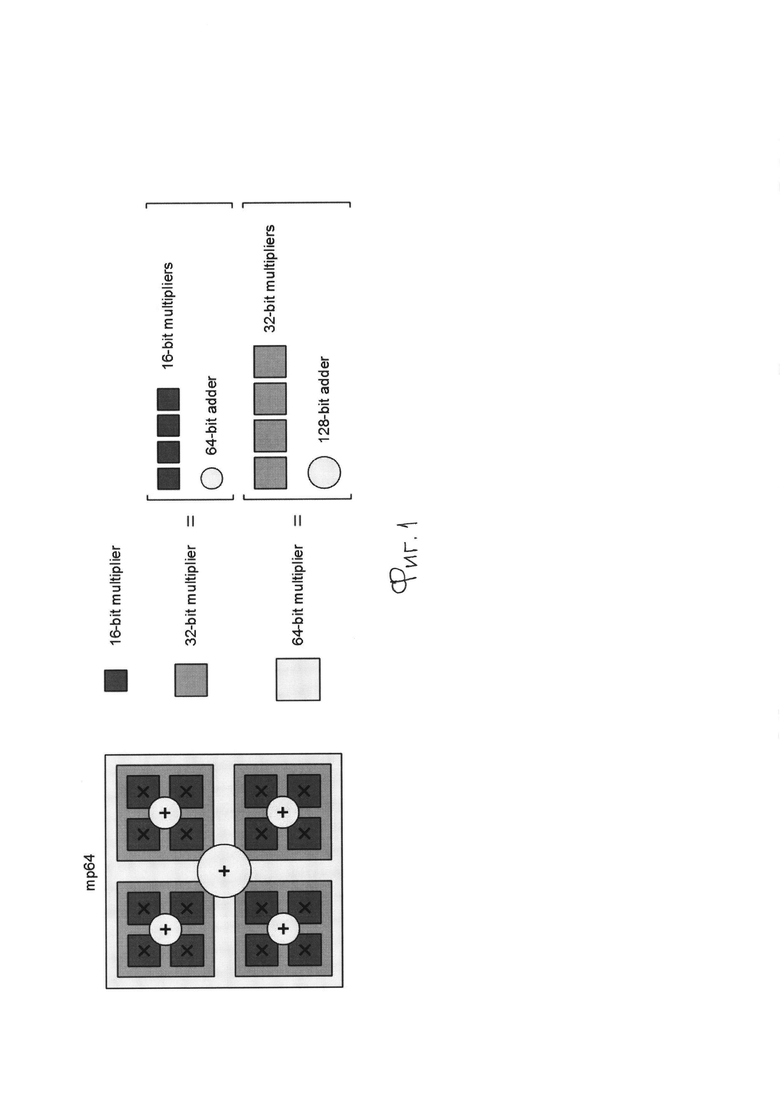

В предпочтительном варианте осуществления векторного мультиформатного умножителя 16-разрядный блок 10 целочисленного умножения содержит 16-разрядный целочисленный умножитель 11, оба входа которого являются входами 16-разрядного блока 10 целочисленного умножения, а выход которого является первым выходом 16-разрядного блока 10 целочисленного умножения, а также соединен со входом 16-разрядного блока 12 формирования произведения с плавающей точкой половинной точности, выход которого является вторым выходом 16-разрядного блока 10 целочисленного умножения, при этом

- 16-разрядный целочисленный умножитель 11 выполнен с возможностью получения на входы двух 16-разрядных операндов и формирования на выходе целочисленного произведения этих операндов;

- 16-разрядный блок 12 формирования произведений чисел с плавающей точкой выполнен с возможностью вычисления произведения чисел с плавающей точкой на основе целочисленного произведения мантисс, которое вычисляется на общем массиве 16-разрядных целочисленных умножителей 11.

В основе заявленного изобретения лежит принцип вычисления произведения чисел с фиксированной точкой большей разрядности на основе произведений чисел с фиксированной точкой меньшей разрядности. Для двоичной системы счисления он описывается следующим образом:

А=2na1+а2

В=2mb1+b2

X=АВ=2mna1b1+2na1b2+2ma2b1+a2b2,

где A - первый множитель, В - второй множитель, X - произведение.

Это означает, что каждый из множителей в двоичной системе счисления разбивают на две части, старшую и младшую, каждую из которых перемножают с каждой из частей другого множителя, после чего полученные произведения складывают со сдвигом, при этом формируют итоговое произведение. Таким образом, для вычисления произведения большей разрядности требуются четыре умножителя меньшей разрядности и сумматор, что экономичнее по площади, чем один умножитель полной разрядности.

Также в основе заявленного изобретения лежит принцип вычисления произведения чисел с плавающей точкой на основе целочисленного произведения мантисс. Это означает, что целочисленное произведение мантисс вычисляют на тех же умножителях, что и произведения чисел с фиксированной точкой, после чего с помощью аппаратного блока анализируют знаки и экспоненты множителей с плавающей точкой и формируют итоговое произведение. Данный подход существенно сокращает площадь заявленного устройства.

Основой аппаратной реализации заявленного изобретения является массив из шестнадцати 16-разрядных целочисленных умножителей и дерева сумматоров, которые позволяют вычислять произведения чисел с фиксированной точкой размером 8, 16, 32 и 64 бита, а также различные суммы произведений. Также в состав устройства входят блоки формирования произведений чисел с плавающей точкой и сумматоры чисел с плавающей точкой половинной, одинарной и двойной отчности. Устройство способно принимать на вход до четырех 64-разрядных операндов и выполнять над ними одновременно до двух команд, записывая результат в регистровый файл или в регистры-аккумуляторы.

Для лучшего понимания заявленного изобретения далее приводится его подробное описание с соответствующими графическими материалами.

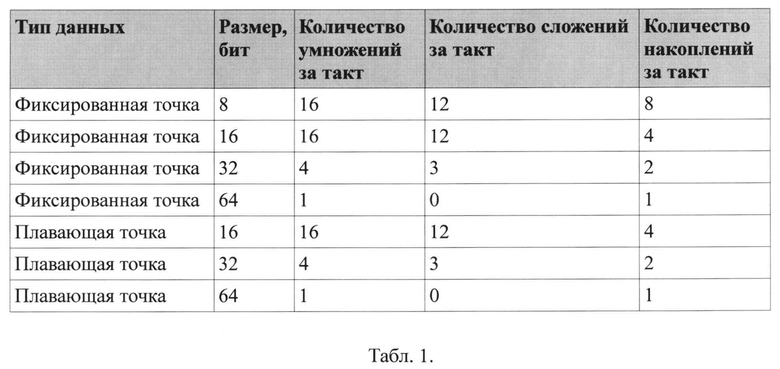

Фиг. 1. Общая схема массива умножителей, выполненная согласно изобретению.

Фиг. 2. Структурная схема 16-разрядного блока целочисленного умножения, выполненная согласно изобретению.

Фиг. 3. Структурная схема 32-разрядного блока целочисленного умножения, выполненная согласно изобретению.

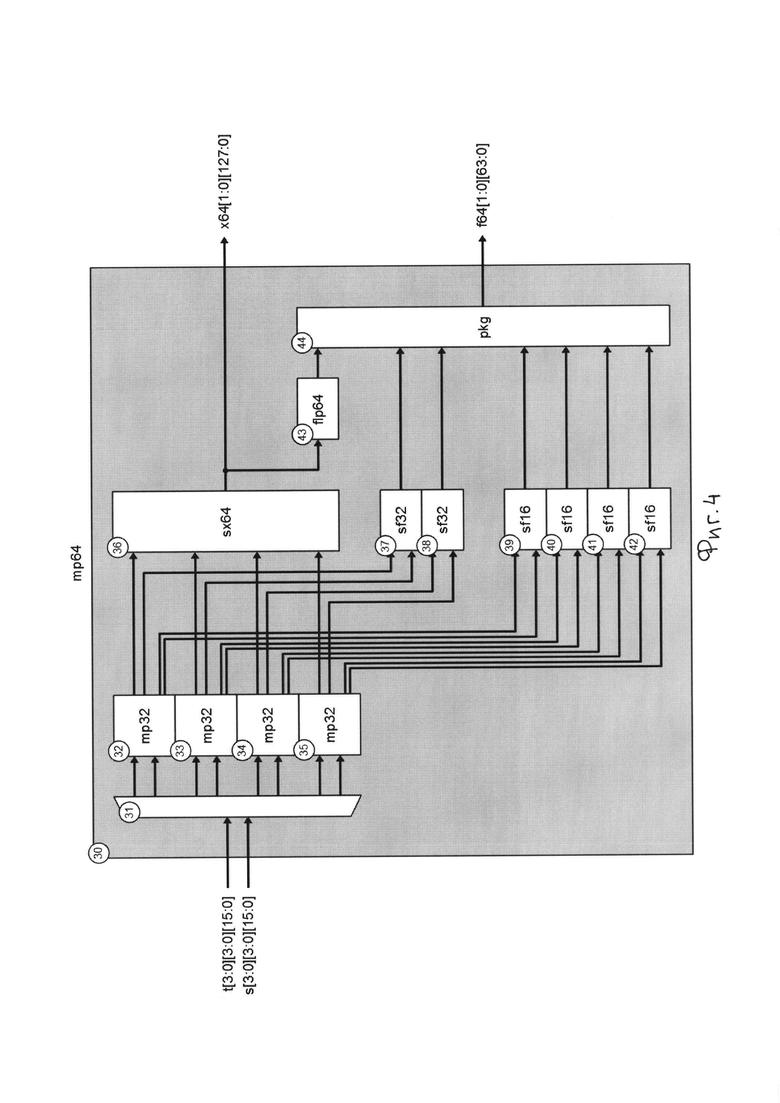

Фиг. 4. Структурная схема 64-разрядного блока целочисленного умножения, выполненная согласно изобретению.

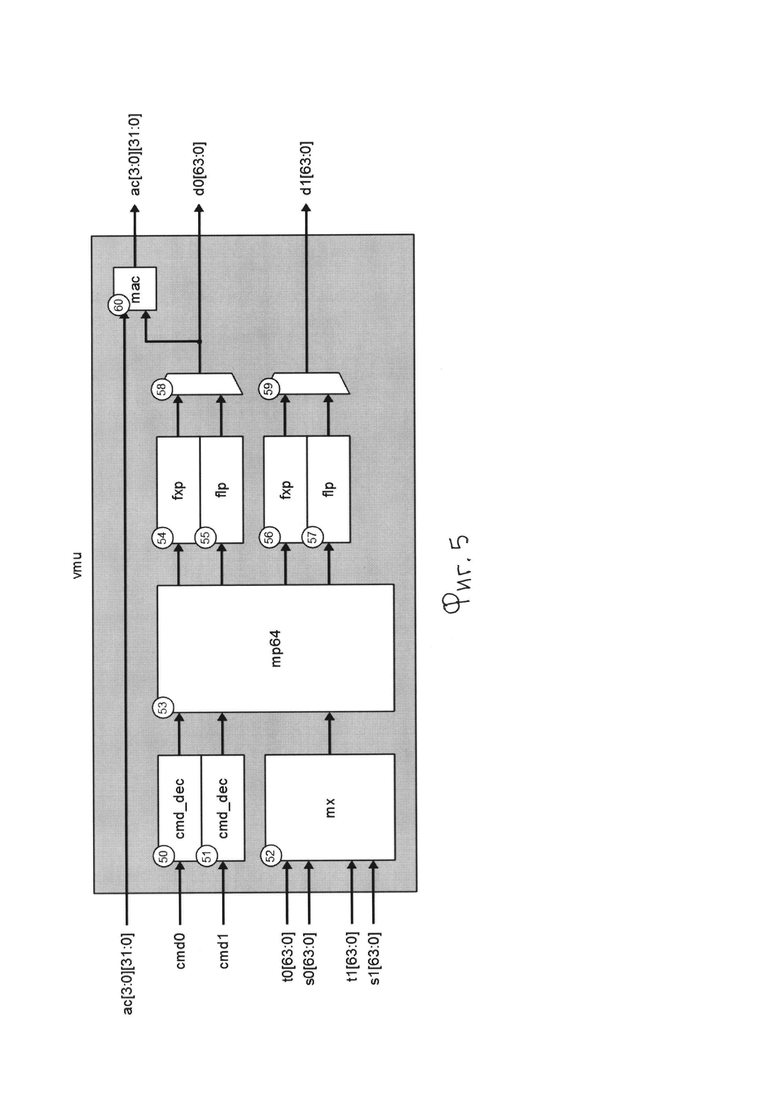

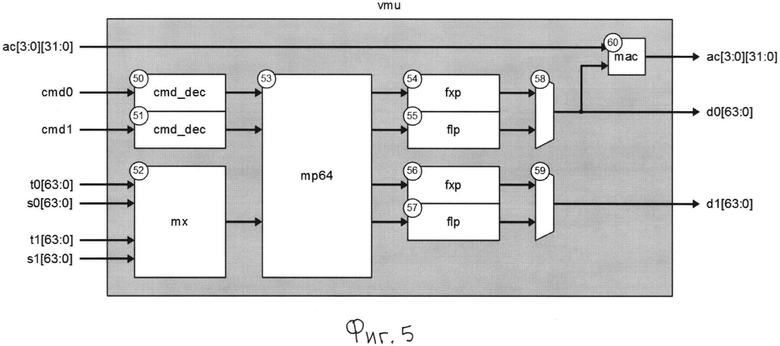

Фиг. 5. Структурная схема векторного мультиформатного умножителя, выполненная согласно изобретению.

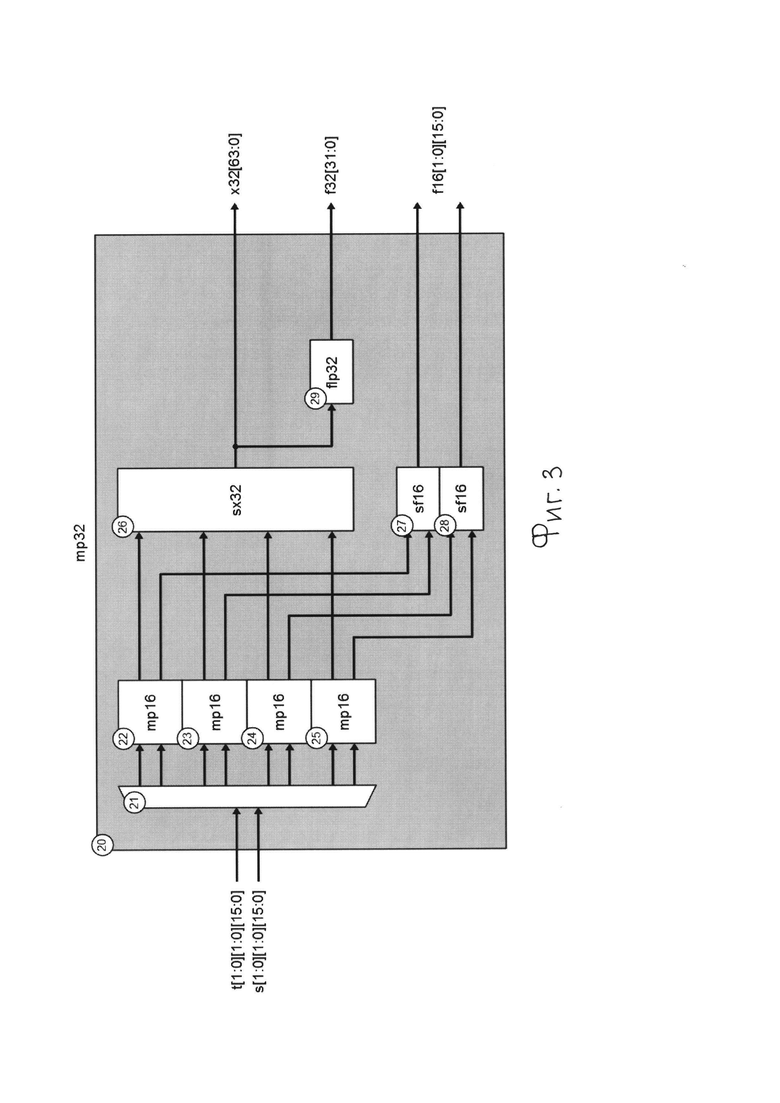

Таблица 1. Производительность векторного мультиформатного умножителя, выполненная согласно изобретению.

Элементы:

10, 22, 23, 24, 25 - 16-разрядный блок целочисленного умножения mp16;

11 - 16-разрядный целочисленный умножитель;

12 - 16-разрядный блок формирования произведений чисел с плавающей точкой flp16;

20, 32, 33, 34, 35 - 32-разрядный блок целочисленного умножения mp32;

21, 31 - демультиплексор входных данных;

26 - сумматор чисел с фиксированной точкой sx32;

27, 28, 39, 40, 41, 42 - 16-разрядные сумматоры чисел с плавающей точкой половинной точности sf16;

29 - 32-разрядный блок формирования произведения с плавающей точкой одинарной точности flp32;

30, 53 - 64-разрядный блок целочисленного умножения mp64;

36 - сумматор чисел с фиксированной точкой sx64;

37, 38 - 32-разрядные сумматоры чисел с плавающей точкой половинной точности sf32;

43 - 64-разрядный блок формирования произведения с плавающей точкой одинарной точности flp64;

44 - блок упаковки произведений с плавающей точкой pkg;

50, 51 - декодер команд cmd_dec;

52 - мультиплексор mx;

54, 56 - блок преобразования результата с фиксированной точкой fxp;

55, 57 - блок преобразования результата с плавающей точкой flp;

58, 59 - мультиплексор результата;

60 - блок накопления результата в регистрах-аккумуляторах mac.

Рассмотрим более подробно вариант выполнения заявленного изобретения (Фиг. 1-5).

Заявленный векторный мультиформатный умножитель способен принимать на вход до четырех 64-разрядных операндов и выполнять над ними одновременно до двух команд, записывая результат в регистровый файл или в регистры-аккумуляторы.

Основой заявленного векторного мультиформатного умножителя является массив размерности 4×4, состоящий из 16-разрядных целочисленных умножителей 11, связанных между собой двухуровневым деревом сумматоров, общая схема которого приведена на Фиг. 1. На каждом уровне суммирования используют сумматоры с четырьмя входами. Данная конструкция позволяет вычислять произведения 8-, 16-, 32- и 64-разрядных чисел с фиксированной точкой, а также различные суммы произведений этих чисел.

Также основой векторного мультиформатного умножителя являются блоки 12, 29, 43 формирования произведений чисел с плавающей точкой. Данные блоки позволяют вычислять произведения чисел с плавающей точкой на основе целочисленного произведения мантисс, которое вычисляют на общем массиве умножителей. Такое решение позволяет отказаться от отдельных умножителей чисел с плавающей точкой и значительно сократить площадь устройства (векторного мультиформатного умножителя). Произведения чисел с плавающей точкой связаны деревом сумматоров, позволяющим вычислять различные суммы произведений.

На Фиг. 2 приведена структурная схема 16-разрядного блока 10 целочисленного умножения, который является элементарной единицей массива умножителей. Кроме 16-разрядного целочисленного умножителя 11, в его состав входит блок 12 формирования произведения с плавающей точкой половинной точности Ар 16. 16-разрядный блок 10 целочисленного умножения получает на вход два 16-разрядных операнда и выдает на выходе два произведения этих операндов: целочисленное и с плавающей точкой.

На Фиг. 3 приведена структурная схема 32-разрядного блока 20 целочисленного умножения. Основой данного блока является массив размерности 2×2, состоящий из 16-разрядных целочисленных умножителей 22-25. Входные данные распределяются на 16-разрядные целочисленные умножители 22-25 с помощью демультиплексора 21. Целочисленные произведения с 16-разрядных целочисленных умножителей 22-25 поступают на 32-разрядный сумматор 26 чисел с фиксированной точкой, который может на их основе вычислить как произведения 32-разрядных чисел, так и различные суммы произведений 16-разрядных чисел. Также он может просто упаковать и пропустить дальше два произведения 16-разрядных чисел. Произведения с плавающей точкой половинной точности с 16-разрядных целочисленных умножителей 22-25 попарно поступают на два 16-разрядных сумматора 27, 28 чисел с плавающей точкой половинной точности, каждый из которых либо вычисляет сумму произведений, либо просто пропускает дальше один из операндов. Блок 29 формирования произведения с плавающей точкой одинарной точности используют для формирования произведения чисел с плавающей точкой одинарной точности. Блок 20 целочисленного умножения получает на вход два массива 2×2 16-разрядных операндов и выдает на выходе 64-разрядный упакованный результат целочисленных умножений, 32-разрядный упакованный результат умножений с плавающей точкой половинной точности и произведение с плавающей точкой одинарной точности.

На Фиг. 4 приведена структурная схема 64-разрядного блока 30 целочисленного умножения. Основой данного блока является массив размерности 2×2, состоящий из 32-разрядных блоков 32-35 целочисленного умножения. Входные данные распределяются на 32-разрядные блоки 32-35 целочисленного умножения с помощью демультиплексора 31. Целочисленные произведения из 32-разрядных блоков 32-35 целочисленного умножения поступают на 64-разрядный сумматор 36 чисел с фиксированной точкой, который может на их основе вычислить как произведение 64-разрядных чисел, так и различные суммы произведений 32- и 16-разрядных чисел. Также он может просто упаковать и пропустить дальше данные с выходов 32-разрядных блоков 32-35 целочисленного умножения. Произведения с плавающей точкой половинной точности с блоков 32-35 целочисленного умножения попарно поступают на четыре 16-разрядных сумматора 39-42 чисел с плавающей точкой половинной точности, каждый из которых либо вычисляет сумму произведений, либо просто пропускает дальше один из операндов. Произведения с плавающей точкой одинарной точности с блоков 32-35 целочисленного умножения попарно поступают на два 32-разрядных сумматора 37, 38 чисел с плавающей точкой одинарной точности, каждый из которых либо вычисляет сумму произведений, либо просто пропускает дальше один из операндов. 64-разрядный блок 43 формирования произведения с плавающей точкой двойной точности используют для формирования произведения чисел с плавающей точкой двойной точности. 64-разрядный блок 30 целочисленного умножения получает на вход два массива размерности 4×4 16-разрядных операндов и выдает на выходе два 128-разрядных упакованных результата целочисленных умножений и два 64-разрядных упакованных результата умножений с плавающей точкой.

На Фиг. 5 приведена структурная схема заявленного векторного мультиформатного умножителя. Основой векторного мультиформатного умножителя является 64-разрядный блок 53 целочисленного умножения, который выполняет вычисления. Два декодера команд 50, 51 осуществляют декодирование команд и настройку 64-разрядный блока 53 целочисленного умножения для их корректного выполнения. Мультиплексор 52 принимает на вход четыре 64-разрядных операнда и в соответствии с текущей командой преобразует их в два массива размерности 4×4 16-разрядных операндов, которые далее поступают на 64-разрядный блок 53 целочисленного умножения. Блоки 54, 56 преобразования результата с фиксированной точкой и блоки 55, 57 преобразования результата с плавающей точкой формируют окончательные результаты команд, которые через мультиплексоры результата 58, 59 поступают на выходы векторного мультиформатного умножителя. Блок 60 накопления результата в регистрах-аккумуляторах осуществляет сложение результата команды с содержимым регистров-аккумуляторов.

Данные по производительности векторного мультиформатного умножителя приведены в Таблице 1. За один такт выполняют или указанное количество умножений для одного типа данных, или половина умножений для одного типа данных и половина для другого, если возможно.

Векторный мультиформатный умножитель имеет следующий набор команд: умножение, умножение с накоплением, комплексное умножение, сумма произведений, вычисление КИХ-фильтра, умножение матриц.

Команды векторного мультиформатного умножителя являются векторными, то есть работают с векторами данных (SIMD - single instruction, multiple data - одиночный поток команд, множественный поток данных).

Векторный мультиформатный умножитель имеет два вычислительных слота, что дает возможность одновременно выполнять две независимые команды. В случае выполнения одной команды, требующей всей вычислительной мощности векторного мультиформатного умножителя, два вычислительных слота объединяют в один.

Векторный мультиформатный умножитель предназначен для установки в DSP-ядро или систему на кристалле в качестве высокопроизводительного вычислительного устройства.

Основными преимуществами заявленного изобретения являются:

- вычисление произведений чисел с фиксированной точкой большей разрядности на основе произведений чисел с фиксированной точкой меньшей разрядности, что позволяет значительно уменьшить площадь устройства;

- вычисление произведений чисел с плавающей точкой на основе произведений чисел с фиксированной точкой, что позволяет значительно уменьшить площадь устройства;

- поддержка большого количества различных типов входных данных (целые числа с фиксированной точкой размером 8, 16, 32 и 64 бита, дробные числа с фиксированной точкой размером 8, 16 и 32 бита, числа с плавающей точкой половинной, одинарной и двойной точности);

- поддержка векторных операций (SIMD - single instruction, multiple data);

- поддержка большого количества различных вычислительных операций (умножения, комплексного умножения, умножения с накоплением, суммирования произведений, фильтрации, умножения матриц);

- поддержка двух вычислительных слотов, то есть возможность одновременного независимого выполнения двух разных операций умножения;

- количество умножений и сложений для разных типов данных:

фиксированная точка, 8 бит - 16 умножений, 12 сложений и 8 накоплений

фиксированная точка, 16 бит - 16 умножений, 12 сложений и 4 накопления

фиксированная точка, 32 бита - 4 умножения, 3 сложения и 2 накопления

фиксированная точка, 64 бита - 1 умножение, 1 накопление

плавающая точка, 16 бит - 16 умножений, 12 сложений и 4 накопления

плавающая точка, 32 бита - 4 умножения, 3 сложения и 2 накопления

плавающая точка, 64 бита - 1 умножение, 1 накопление

Хотя описанный выше вариант выполнения изобретения был изложен с целью иллюстрации настоящего изобретения, специалистам ясно, что возможны разные модификации, добавления и замены, не выходящие из объема и смысла настоящего изобретения, раскрытого в прилагаемой формуле изобретения.

| название | год | авторы | номер документа |

|---|---|---|---|

| СКАЛЯРНО-ВЕКТОРНЫЙ ПРОЦЕССОР | 2021 |

|

RU2781355C1 |

| ИНСТРУКЦИЯ И ЛОГИЧЕСКАЯ СХЕМА ДЛЯ ВЫПОЛНЕНИЯ ОПЕРАЦИИ СКАЛЯРНОГО ПРОИЗВЕДЕНИЯ | 2007 |

|

RU2421796C2 |

| УСТРОЙСТВО ДЕЛЕНИЯ И ИЗВЛЕЧЕНИЯ КВАДРАТНОГО КОРНЯ | 2012 |

|

RU2510072C1 |

| ЦЕЛОЧИСЛЕННОЕ УМНОЖЕНИЕ ВЫСОКОГО ПОРЯДКА С ОКРУГЛЕНИЕМ И СДВИГОМ В АРХИТЕКТУРЕ С ОДНИМ ПОТОКОМ КОМАНД И МНОЖЕСТВОМ ПОТОКОВ ДАННЫХ | 2003 |

|

RU2263947C2 |

| МИКРОПРОЦЕССОР ГИБРИДНЫЙ | 2007 |

|

RU2359315C2 |

| УСТРОЙСТВО ПРЕДСКАЗАНИЯ ИСКЛЮЧИТЕЛЬНОЙ СИТУАЦИИ "ПОТЕРЯ ТОЧНОСТИ" БЛОКА ОПЕРАЦИИ "УМНОЖЕНИЕ С НАКОПЛЕНИЕМ" | 2012 |

|

RU2498392C1 |

| УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ОПЕРАЦИЙ УМНОЖЕНИЯ-СЛОЖЕНИЯ С УПАКОВАННЫМИ ДАННЫМИ | 1996 |

|

RU2139564C1 |

| ПРОЦЕССОР С ПЛАВАЮЩЕЙ ЗАПЯТОЙ С ПОНИЖЕННОЙ ПОТРЕБЛЯЕМОЙ МОЩНОСТЬЮ ДЛЯ ВЫБИРАЕМОЙ СУБТОЧНОСТИ | 2007 |

|

RU2412462C2 |

| Устройство для умножения чисел в модулярной системе счисления | 1986 |

|

SU1352483A1 |

| ОПТИЧЕСКИЙ ЦИФРОВОЙ СТРАНИЧНЫЙ УМНОЖИТЕЛЬ С ПЛАВАЮЩЕЙ ТОЧКОЙ | 1998 |

|

RU2137179C1 |

Изобретение относится к области вычислительной техники. Техническим результатом является обеспечение вычисления произведений чисел с фиксированной точкой, чисел с плавающей точкой двойной точности, вычисления сумм произведений чисел с плавающей точкой половинной и одинарной точности, а также уменьшение занимаемой площади устройства. Устройство содержит два декодера команд, мультиплексор, 64-разрядный блок целочисленного умножения, два блока преобразования результата с фиксированной точкой, два блока преобразования результата с плавающей точкой, два мультиплексора результата, блок накопления результата. 3 з.п. ф-лы, 5 ил., 1 табл.

1. Векторный мультиформатный умножитель, содержащий массив размерности 4×4 из 16-разрядных целочисленных умножителей 11, входящих в состав 64-разрядного блока 30 целочисленного умножения, два декодера команд 50, 51 и мультиплексор 52, входы которых являются входами векторного мультиформатного умножителя, а выходы которых соединены с входами 64-разрядного блока 53 целочисленного умножения, выходы которого соединены с входами двух блоков 54, 56 преобразования результата с фиксированной точкой и двух блоков 55, 57 преобразования результата с плавающей точкой, выходы которых соединены с входами мультиплексоров результата 58, 59, причем выход первого мультиплексора результата 59 является выходом векторного мультиформатного умножителя, а выход второго мультиплексора результата 58 является выходом векторного мультиформатного умножителя, а также соединен с первым входом блока 60 накопления результата в регистрах-аккумуляторах, второй вход которого является входом векторного мультиформатного умножителя, а выход которого является выходом векторного мультиформатного умножителя, при этом:

- 16-разрядный целочисленный умножитель 11 выполнен с возможностью получения на входы двух 16-разрядных операндов и формирования на выходе целочисленного произведения этих операндов;

- 64-разрядный блок 53 целочисленного умножения выполнен с возможностью получения на вход двух массивов размерности 4×4 из 16-разрядных операндов и формирования на выходе двух 128-разрядных упакованных результатов целочисленных умножений и двух 64-разрядных упакованных результатов умножений с плавающей точкой;

- декодеры команд 51, 52 выполнены с возможностью декодирования команд и настройки 64-разрядного блока 53 целочисленного умножения с целью корректного выполнения этих комманд;

- мультиплексор 52 выполнен с возможностью приема на вход четырех 64-разрядных операндов, преобразования их в соответствии с текущей командой в два массива размерности 4×4 из 16-разрядных операндов и передачи их в 64-разрядный блок 53 целочисленного умножения;

- блоки 54, 56 преобразования результата с фиксированной точкой и блоки 55, 57 преобразования результата с плавающей точкой выполнены с возможностью формирования окончательных результатов команд, и передачи их через мультиплексоры результата 59, 60 на выходы векторного мультиформатного умножителя;

- блок 61 накопления результата в регистрах-аккумуляторах выполнен с возможностью сложения результата команды с содержимым регистров-аккумуляторов и передачи результата сложения на выход векторного мультиформатного умножителя.

2. Векторный мультиформатный умножитель по п. 1, отличающийся тем, что 64-разрядный блок 30 целочисленного умножения содержит демультиплексор 31 входных данных, входы которого являются входами векторного мультиформатного умножителя, а выходы которого соединены с входами четырех 32-разрядных блоков 32 - 35 целочисленного умножения, выходы которых соединены с входами 64-разрядного сумматора 36 чисел с фиксированной точкой, с входами двух 32-разрядных сумматоров 37, 38 чисел с плавающей точкой одинарной точности и с входами четырех 16-разрядных сумматоров 39 - 42 чисел с плавающей точкой половинной точности, причем выход 64-разрядного сумматора чисел с фиксированной точкой является первым выходом 64-разрядного блока 30 целочисленного умножения, а также соединен с одним входом 64-разрядного блока 43 формирования произведения с плавающей точкой двойной точности, выход которого соединен с одним входом блока 44 упаковки произведений с плавающей точкой, остальные входы которого соединены с выходами двух 32-разрядных сумматоров 37, 38 чисел с плавающей точкой одинарной точности и с входами четырех 16-разрядных сумматоров 39-42 чисел с плавающей точкой половинной точности, а выход блока 44 упаковки произведений с плавающей точкой является вторым выходом 64-разрядного блока 30 целочисленного умножения, при этом

- демультиплексор 31 входных данных выполнен с возможностью распределения входных данных на 32-разрядные блоки 32 - 35 целочисленного умножения;

- сумматор 36 чисел с фиксированной точкой выполнен с возможностью получения на вход целочисленных произведений 32-разрядных чисел и вычисления на их основе произведений 64-разрядных чисел, сумм произведений 32-разрядных чисел, сумм произведений 16-разрядных чисел, а также пропускания на выход целочисленных произведений 32-разрядных чисел;

- сумматоры 39-42 чисел с плавающей точкой половинной точности, выполнены с возможностью получения на вход попарно произведений с плавающей точкой половинной точности и вычисления на их основе сумм произведений, а также пропускания дальше одного из операндов;

- блок 43 формирования произведений чисел с плавающей точкой выполнен с возможностью вычисления произведения чисел с плавающей точкой на основе целочисленного произведения мантисс, которое вычисляется на общем массиве 16-разрядных целочисленных умножителей 11.

3. Векторный мультиформатный умножитель по п. 1, отличающийся тем, что 32-разрядный блок 20 целочисленного умножения содержит демультиплексор 21 входных данных, входы которого являются входами векторного мультиформатного умножителя, а выходы которого соединены с входами четырех 16-разрядных блоков 22-25 целочисленного умножения, выходы которых соединены с входами 32-разрядного сумматора 26 чисел с фиксированной точкой, с входами двух 16-разрядных сумматоров 27, 28 чисел с плавающей точкой половинной точности, причем выход 32-разрядного сумматора 26 чисел с фиксированной точкой является первым выходом 32-разрядного блока 20 целочисленного умножения, а также соединен с одним входом 32-разрядного блока 29 формирования произведения с плавающей точкой одинарной точности, выход которого является вторым выходом 32-разрядного блока 20 целочисленного умножения, а выходы двух 16-разрядных сумматоров 27, 28 чисел с плавающей точкой половинной точности являются третьим и четвертым выходами 32-разрядного блока 20 целочисленного умножения, при этом

- демультиплексор 21 входных данных выполнен с возможностью распределения входных данных на 16-разрядные блоки 22-25 целочисленного умножения;

- сумматор 26 чисел с фиксированной точкой выполнен с возможностью получения на вход целочисленных произведений 16-разрядных чисел и вычисления на их основе произведений 32-разрядных чисел, сумм произведений 16-разрядных чисел, пропускания на выход целочисленных произведений 16-разрядных чисел, а также упаковки и пропускания на выход двух произведений 16-разрядных чисел;

- сумматоры 27, 28 чисел с плавающей точкой половинной точности, выполнены с возможностью получения на вход попарно произведений с плавающей точкой половинной точности и вычисления на их основе сумм произведений, а также пропускания дальше одного из операндов;

- блок 29 формирования произведений чисел с плавающей точкой выполнен с возможностью вычисления произведения чисел с плавающей точкой на основе целочисленного произведения мантисс, которое вычисляется на общем массиве 16-разрядных целочисленных умножителей 11.

4. Векторный мультиформатный умножитель по п. 1, отличающийся тем, что 16-разрядный блок 10 целочисленного умножения содержит 16-разрядный целочисленный умножитель 11, оба входа которого являются входами 16-разрядного блока 10 целочисленного умножения, а выход которого является первым выходом 16-разрядного блока 10 целочисленного умножения, а также соединен с входом 16-разрядного блока 12 формирования произведения с плавающей точкой половинной точности, выход которого является вторым выходом 16-разрядного блока 10 целочисленного умножения, при этом

- 16-разрядный целочисленный умножитель 11 выполнен с возможностью получения на входы двух 16-разрядных операндов и формирования на выходе целочисленного произведения этих операндов;

- 16-разрядный блок 12 формирования произведений чисел с плавающей точкой выполнен с возможностью вычисления произведения чисел с плавающей точкой на основе целочисленного произведения мантисс, которое вычисляется на общем массиве 16-разрядных целочисленных умножителей 11.

| Многоступенчатая активно-реактивная турбина | 1924 |

|

SU2013A1 |

| CN 106951211 A, 14.07.2017 | |||

| CN 105607889 A, 25.05.2016 | |||

| US 4953119 A, 28.08.1990 | |||

| ЦЕЛОЧИСЛЕННОЕ УМНОЖЕНИЕ ВЫСОКОГО ПОРЯДКА С ОКРУГЛЕНИЕМ И СДВИГОМ В АРХИТЕКТУРЕ С ОДНИМ ПОТОКОМ КОМАНД И МНОЖЕСТВОМ ПОТОКОВ ДАННЫХ | 2003 |

|

RU2263947C2 |

Авторы

Даты

2019-05-29—Публикация

2018-08-21—Подача