Настоящее изобретение относится к вычислительной технике и предназначено для автоматического выявления неисправностей в программно-аппаратных комплексах, для имитации неисправностей и сбоев в программно-аппаратных комплексах на базе группы микроконтроллеров с поддержкой интерфейса JTAG и стандарта IEEE 1149.1 - «совместимый интерфейс граничного сканирования JTAG».

Наиболее близким к предлагаемому устройству является устройство для имитации отказов и сбоев ЭВМ, содержащее блоки памяти, регистры, триггеры, блоки шинных формирователей, дешифратор адресов, формирователь импульсов, мультиплексор, генератор тактовых импульсов, шифратор управляющих сигналов, шифратор искажений информации.

Недостатком устройства-прототипа является невозможность программной настройки на разные типы интерфейсов, что делает его неприменимым в современных устройствах для различных архитектур, малая скорость имитации неисправностей, отсутствие режима машинного обучения, позволяющего применять алгоритмы искусственного интеллекта для обработки результатов эксперимента. Применение настоящего изобретения возможно для микроконтроллерных систем. Большинство современных интерфейсов поддерживают стандарт JTAG, обеспечивающий доступ к памяти и регистрам микропроцессоров системы в режиме отладки, что позволяет осуществлять постоянный контроль состояния одного или нескольких микроконтроллеров при имитации неисправностей.

Задача изобретения - расширение функциональных возможностей путем внедрения новых режимов работы.

Достигаемым техническим результатом является внедрение новых режимов работы, а именно режимов экспертного алгоритма и алгоритма машинного обучения, в котором для тестирования системы на отказы и сбои вводится блок рабочей станции для имитации неисправностей, определяющий сигнатуры реакции системы средств контроля имитируемых неисправностей, что позволяет увеличить скорость тестов для проведения испытаний на надежность системы, унифицировать проводимые тесты имитации для микроконтроллерных систем.

Поставленная задача достигается с помощью использования экспертного алгоритма, который предназначен для поиска наиболее уязвимых мест программы и корректировки зоны применения алгоритма машинного обучения, и алгоритма машинного обучения для генерации данных для микроконтроллерной системы, за счет которого устанавливаются сигнатурные признаки отказа микроконтроллерной системы, предназначенные для генерации последовательности по JTAG-интерфейсу вызывающий вероятный сбой или отказ системы. Для машинного алгоритма фиксируется состояния системы на блоке рабочей станции баз данных, которые генерируются устройством отладки по интерфейсу JTAG, за счет чего повышается эффективность испытания по сравнению с аналогами, где новый процесс имитации занимает длительное время.

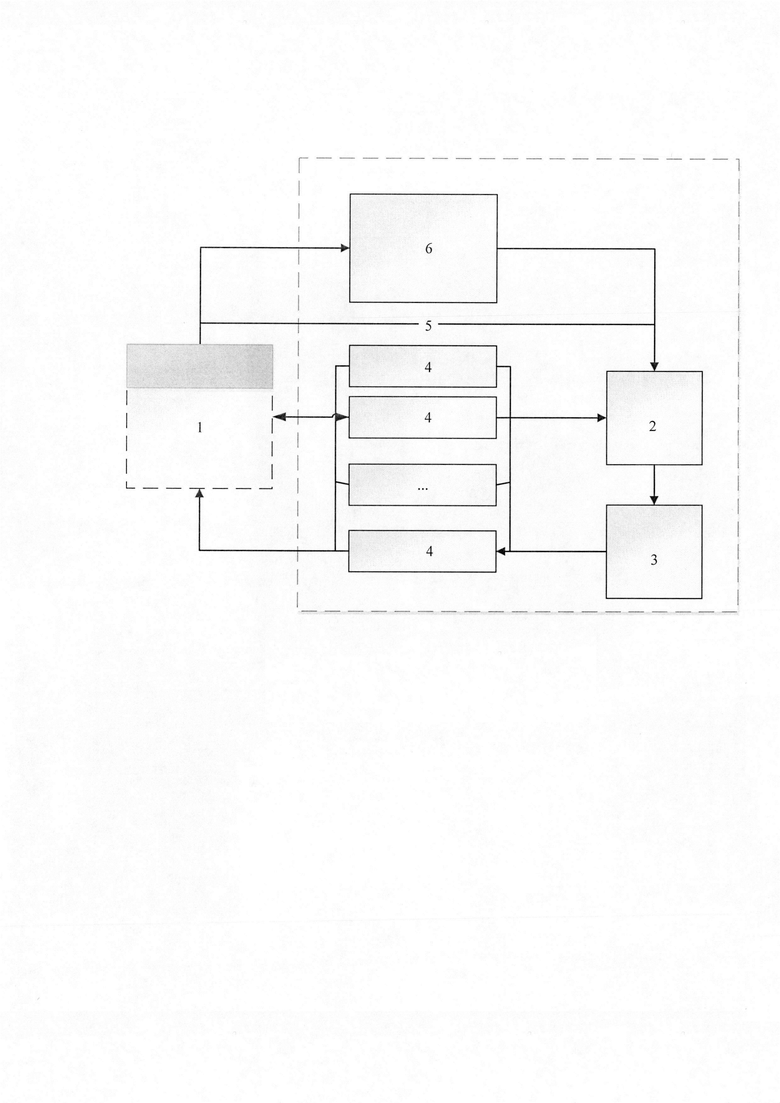

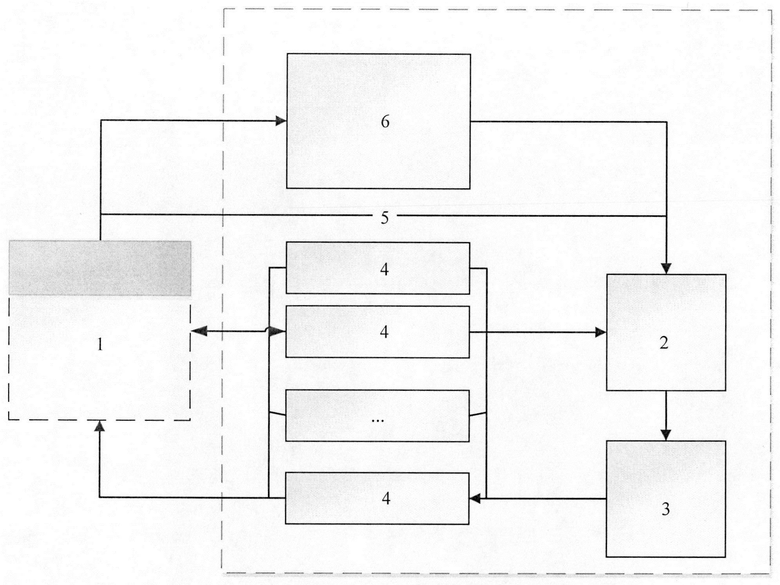

Сущность изобретения поясняется схемой. На фигуре изображена структурная схема устройства для имитации отказов и сбоев в микроконтроллерной системе. Устройство содержит 1 - набор тестируемых микроконтроллеров; 2 - блок рабочей станции баз данных; 3 - блок рабочей станции для имитации неисправностей; 4 - устройство отладки по интерфейсу JTAG; 5 - блок обратной связи микроконтроллерной системы и баз данных; 6 - внешнее устройство для имитации неисправностей, типа приведенных в описании прототипа[1].

Набор тестируемых микроконтроллеров 1 представляет собой несколько устройств, обладающих JTAG-интерфейсами стандарта IEEE 1149.1 (или аналогами), объединенных в JTAG-цепочку посредством последовательного подключения данных устройств. На наборе микроконтроллеров исполняется тестовая программа, результат выполнения которой известен на любой стадии выполнения. При возникновении неисправности система считывает данные с блока с отказного микроконтроллера при отсутствии стандартного сигнала о выполнении операций, выдаваемого на выход микроконтроллера и фиксируемого другими блоками системы.

Блок рабочей станции баз данных 2 представляет собой устройство с развернутым сервисом баз данных, накапливающим информацию по выбранным полям регистров процессора, периферии, памяти для анализа алгоритму машинного обучения.

Блок рабочей станции для имитации неисправностей 3 представляет собой устройство с запушенным алгоритмом машинного обучения и JTAG-программу, которая на основе переданных команд алгоритма модифицирует содержимое памяти микроконтроллера на основе сигнатурного анализа. Также на рабочей станции запущен экспертный алгоритм, который корректирует зоны применения алгоритма машинного обучения для увеличения скорости моделирования отказов и сбоев.

Устройство отладки по интерфейсу JTAG 4 представляет собой набор JTAG-контроллеров, объединенных в общую JTAG-цепочку, подключенную вводом-выводом к блоку 1, который также подключается к блоку 2.

Внешняя связь 5 предоставляет интерфейс, по которому управляющая подсистема корректирует управляемую.

Устройство внешнего контроля 6 представляет собой блок для контроля микроконтроллеров без встроенного JTAG-интерфейса.

Устройство работает следующим образом. С помощью блока 3 генерируется набор данных, который с помощью блоков 4 управляет вводами-выводами и состоянием регистров блока 1 и с помощью блоков 5, 6 в установленный интервал времени передает информацию своем состоянии на блок 2, где информация ранжируется и разбивается на составляющие сигнатурных признаков. Блок 2 генерирует признаки для алгоритма обучения и передает на блок 3, который содержит обучающий экспертный алгоритм и алгоритм машинного обучения, который по этим признакам вновь генерирует входную последовательность для 1 блока через блок 4.

Использование заявляемого изобретения в сравнении с известными устройствами обеспечивает высокоточное обнаружение сбоев и неисправностей на микроконтроллере и может использоваться для проведения операций по восстановлению и коррекции техники при разработке и эксплуатации.

Источники информации.

1. А. св. №1564628, G06F 11/26, опубликованное 15.05.1990 Б. №18.

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОГОФУНКЦИОНАЛЬНЫЙ ДИАГНОСТИЧЕСКИЙ КОМПЛЕКС | 2023 |

|

RU2815706C1 |

| СТЕНД ДЛЯ ИЗУЧЕНИЯ МИКРОКОНТРОЛЛЕРНЫХ СИСТЕМ УПРАВЛЕНИЯ | 2008 |

|

RU2402822C2 |

| СПОСОБ ДИАГНОСТИРОВАНИЯ ИНФОРМАЦИОННО-ПРЕОБРАЗУЮЩИХ ЭЛЕМЕНТОВ БОРТОВОГО ОБОРУДОВАНИЯ ВОЗДУШНОГО СУДНА НА ОСНОВЕ МАШИННОГО ОБУЧЕНИЯ | 2022 |

|

RU2802976C1 |

| ЦИФРОВОЙ ОТЛАДОЧНЫЙ КОМПЛЕКС | 2021 |

|

RU2773696C1 |

| УСТРОЙСТВО ТЕХНИЧЕСКОГО ДИАГНОСТИРОВАНИЯ КОМПЛЕКСА БОРТОВОГО ОБОРУДОВАНИЯ ВОЗДУШНЫХ СУДОВ НА ОСНОВЕ МАШИННОГО ОБУЧЕНИЯ | 2024 |

|

RU2831917C1 |

| ПЕРЕНОСНОЙ ДИАГНОСТИЧЕСКИЙ КОМПЛЕКС | 2015 |

|

RU2612072C1 |

| Стенд микроконтроллерный для изучения, исследования и отладки алгоритмов встраиваемых систем управления и цифровой обработки сигналов | 2021 |

|

RU2765610C1 |

| СПОСОБ ДИАГНОСТИРОВАНИЯ КОМПЛЕКСА БОРТОВОГО ОБОРУДОВАНИЯ ВОЗДУШНЫХ СУДОВ НА ОСНОВЕ МАШИННОГО ОБУЧЕНИЯ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2023 |

|

RU2816667C1 |

| СПОСОБ ДИАГНОСТИРОВАНИЯ КОМПЛЕКСА БОРТОВОГО ОБОРУДОВАНИЯ ВОЗДУШНЫХ СУДОВ НА ОСНОВЕ МАШИННОГО ОБУЧЕНИЯ БЕЗ УЧИТЕЛЯ С АВТОМАТИЧЕСКИМ ОПРЕДЕЛЕНИЕМ ПАРАМЕТРОВ ОБУЧЕНИЯ МОДЕЛЕЙ | 2023 |

|

RU2818858C1 |

| ПЕРЕНОСНОЙ ДИАГНОСТИЧЕСКИЙ КОМПЛЕКС | 2015 |

|

RU2612069C1 |

Изобретение относится к вычислительной технике. Технический результат - расширение функциональных возможностей имитации неисправностей в программно-аппаратных системах. Устройство для имитации неисправностей в программно-аппаратных системах содержит внешнее устройство для имитации неисправностей, при этом в устройство дополнительно введены набор тестируемых микроконтроллеров, блок рабочей станции баз данных, которая хранит сигнатуры реакций системы, блок рабочей станции для имитации неисправностей, которая содержит экспертный алгоритм, предназначенный для поиска наиболее уязвимых мест программы и корректировки зоны применения алгоритма машинного обучения, и алгоритм машинного обучения для генерации данных для микроконтроллерной системы, устройство отладки по интерфейсу JTAG, блок обратной связи микроконтроллерной системы и блока рабочей станции баз данных. 1 ил.

Устройство для имитации неисправностей в программно-аппаратных системах, содержащее внешнее устройство для имитации неисправностей, отличающееся тем, что в устройство дополнительно введены набор тестируемых микроконтроллеров, блок рабочей станции баз данных, которая хранит сигнатуры реакций системы, блок рабочей станции для имитации неисправностей, которая содержит экспертный алгоритм, предназначенный для поиска наиболее уязвимых мест программы и корректировки зоны применения алгоритма машинного обучения, и алгоритм машинного обучения для генерации данных для микроконтроллерной системы, устройство отладки по интерфейсу JTAG, блок обратной связи микроконтроллерной системы и блока рабочей станции баз данных, причем выход набора тестируемых микроконтроллеров соединен с первым входом-выходом внешнего устройства для имитации неисправностей и со входом блока обратной связи набора тестируемых микроконтроллеров и блока баз данных, а первый вход-выход соединен с первым входом-выходом устройства отладки по интерфейсу, второй вход-выход которого соединен с входом-выходом блока баз данных, вход которого соединен с выходом внешнего устройства имитации неисправностей и выходом блока обратной связи набора тестируемых микроконтроллеров и рабочей станции баз данных, а выход соединен со входом блока рабочей станции для имитации неисправностей, выход которого соединен со входом отладки по интерфейсу.

| CN 104657247 A, 27.05.2015 | |||

| Электрическое устройство для решения системы уравнений | 1944 |

|

SU75070A1 |

| АВТОМАТИЗИРОВАННОЕ УСТРОЙСТВО ДЛЯ ТЕСТИРОВАНИЯ МИКРОПРОЦЕССОРНЫХ СИСТЕМ | 2008 |

|

RU2392657C2 |

| Устройство для имитации отказов и сбоев ЭВМ | 1987 |

|

SU1564628A1 |

Авторы

Даты

2019-08-15—Публикация

2018-02-13—Подача