Изобретение относится к вычисли™ тельной технике и предназначено для имитации неисправностей при экспери - ментальном исследовании надежности я устойчивости функционирования структурно-избыточных вычислительных систем, построенных с использованием различных асинхронных магистральных интерфейсов„

Цель изобретения расширение функциональных возможностей устройства путем имитации неисправностей в циклах Адрес и Данные магистрали ЭВМ.

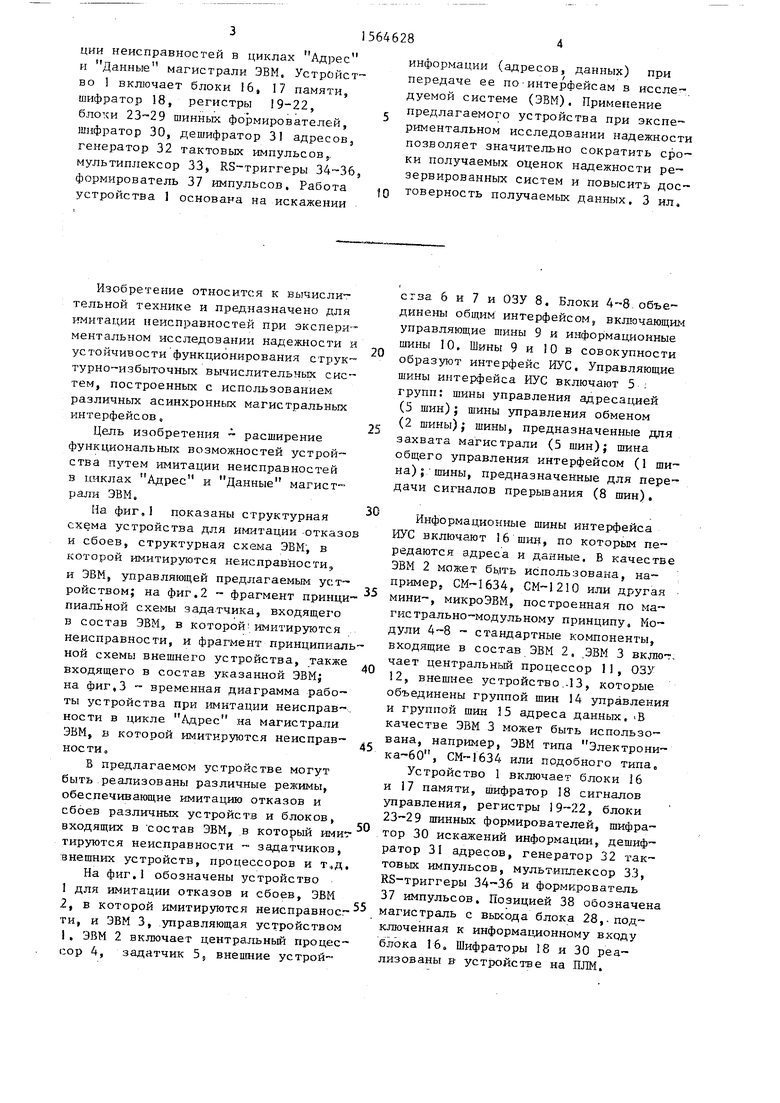

На фиг,1 показаны структурная схема устройства для имитации отказов и сбоев, структурная схема ЭВМ, в которой имитируются неисправности,, и ЭВМ, управляющей предлагаемым устройством; на фиг.2 фрагмент принципиальной схемы задатчика, входящего в состав ЭВМ, в которой1 имитируются неисправности, и фрагмент принципиальной схемы внешнего устройства, также входящего в состав указанной ЭВМ; на фиг,3 ™ временная диаграмма рабо ты устройства при имитации неисправности в цикле Адрес на магистрали ЭВМ, в которой имитируются неисправ- ности„

В предлагаемом устройстве могут быть реализованы различные режимы, обеспечивающие имитацию отказов и сбоев различных устройств и блоков, входящих в состав ЭВМ, в который ими тируются неисправности - задатчиков, внешних устройств, процессоров и т„д.

На фиг.1 обозначены устройство 1 для имитации отказов и сбоев, ЭВМ 2, в которой имитируются неисправности, и ЭВМ 3, управляющая устройством I. ЭВМ 2 включает центральный процессор 4, задатчик 5, внешние устрой,

,20

30

25

. ,,

.

50

55

сгза 6 и 7 и ОЗУ 8. Блоки 4-8 объединены общим интерфейсом, включающим управляющие шины 9 и информационные шины 10, Шины 9 и 10 в совокупности образуют интерфейс ИУС. Управляющие шины интерфейса ИУС включают 5 групп: шины управления адресацией (5 шин); шины управления обменом (2 шины); шины, предназначенные для захвата магистрали (5 шин); шина общего управления интерфейсом (1 шина); шины, предназначенные для передачи сигналов прерывания (8 шин),

Информационные шины интерфейса ИУС включают 16 шин, по которым передаются адреса и данные. В качестве ЭВМ 2 может быть использована, например, CM-I634, СМ-1210 или другая мини-, микроЭВМ, построенная по ма- гистрально-модульному принципу. Модули 4-8 стандартные компоненты, входящие в состав ЭВМ 2. ЭВМ 3 вклю. чает центральный процессор 1, ОЗУ 12, внешнее устройство -13, которые объединены группой шин 14 управления и группой шин 35 адреса данных. В качестве ЭВМ 3 может быть использована, например, ЭВМ типа Электрони- ка-60, или подобного типа,

Устройство 1 включает блоки 16 и 17 памяти, шифратор 18 сигналов управления, регистры 19-22, блоки 23-29 шинных формирователей, шифратор 30 искажений информации, дешифратор 31 адресов, генератор 32 тактовых импульсов, мультиплексор 33, RS-триггеры 34-36 и формирователь 37 импульсов. Позицией 38 обозначена магистраль с выхода блока 28,-подключенная к информационному входу блока 16. Шифраторы 18 и 30 реализованы в устройстве на ПЛМ.

515

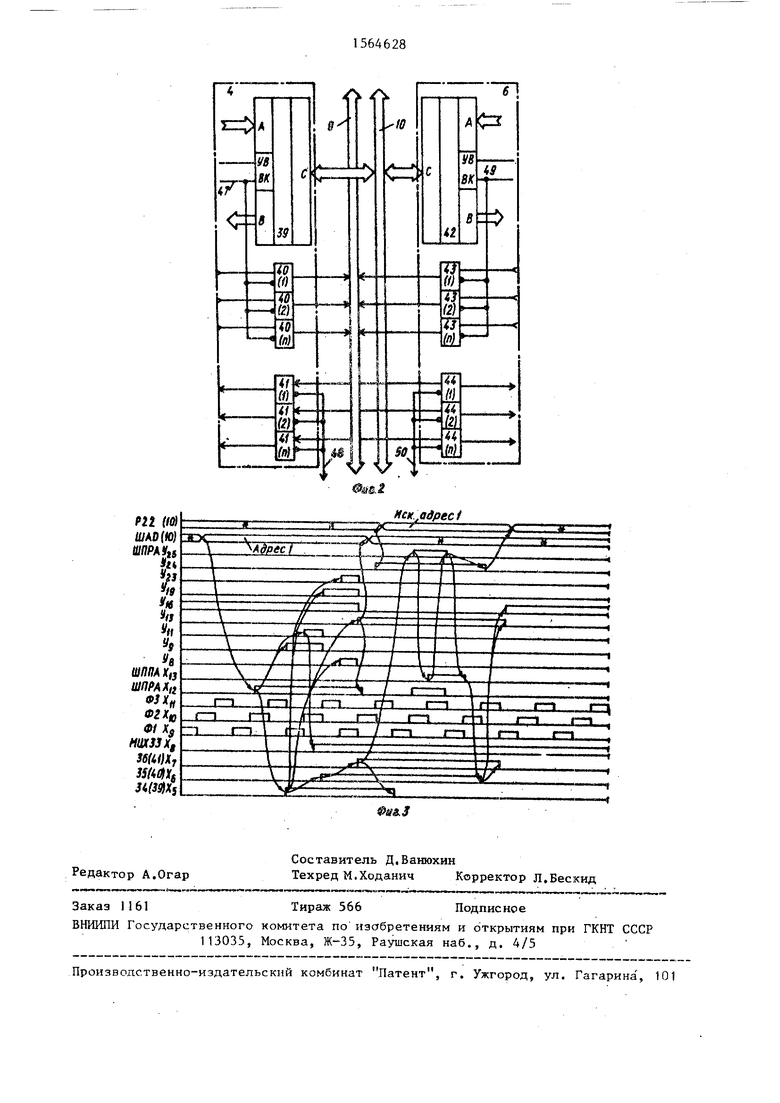

На фиг.2 представлены фрагмент принципиальной схемы задатчика 5 и фрагмент принципиальной схемы внешнего устройства 7, входящих в состав ЭВМ 2. Задатчик 5 включает блок 39 шинных формирователей, содержащий 4 микросхемы К589АП26, подключенных к информационным шинам 10, буферные усилители 40(1)- 40(п) с открытым коллектором и магистральные приемники 41(1) - 41(п), подключенные к управляющим шинам 9.

В состав внешнего устройства 7 входят блок 42 тинных формирователей, буферные усилители 43(1) - 43(п) и магистральные приемники 44(1) - 44(п

Работа устройства 1 основана на искажении информации (адресов, дан™ ных) при передаче ее от одного моду- ля к другому по информационным шинам 10.

Блок 16 памяти служит для синхронизации момента имитации неисправностей с появлением определенного (заранее заданного и записанного в блок 16) адреса или данного, передаваемого по магистрали 0, В момент появления определенного адреса на выходе блока 16 появляется следующая информация:

адрес кода искажения в блоке 17 (3 разряда);

номер задатчика, формирующего адрес на магистрали 10 (3 разряда);

код типа неисправности (4 разряда) ;отказ или сбой, в адресной или информационной части цикла магистрали.

Блок 17 необходим для хранения кода искажения для каждой имитируемой неисправности. Для каждой из 16 информационных шин магистрали 10 в блоке 17 двумя разрядами задается

тип искажениям(константа 1, константа 0й, инверсия передаваемого разряда, нет искажений)

Шифратор 18 служит для управления работой устройства 1 - для выработки сигналов управления блоками 16 и 17, регистрами , триггерами 34-36, блоками 23, 29 и формирователем 37. Входы шифратора 18 X 1 X., имеют следующее назначение:

Х, Х код типа неисправности, поступающий с блока 16;

Ху- Х-, - значения триггеров 34-36; Xg сигнал, подтверждения

того, что адрес формиру-

0

5

0

X,

Х,Г

ется задатчиком, для которого требуется проимити- ровать неисправностьj Xf1 - тактовые частоты (см. временные диаграммы на

фиг.З);

управляющие сигналы

интерфейса ИУС; X - шина признака адресации

(ШПРА);

шина подтверждения приема

адреса (ШГША) ;

шина блокировки сброса

выборки (ШБСВ);

шина признака внешнего

устройства (ШПВУ);

шина4признака приемника

(ШППР);

шина запроса данных (ШЗД); наличия данных (ШНД);

шина занято (ШЗАН);

Х,э

х,Xf5

Х,

Xf7

X,f - шина

х„

Х1в- шина сброса (ШСБР);

5

Х1

0

5

сигнал разрешения работы устройства;

сигнал управления записью регистра 19;

сигнал управления записью регистра 20;

Xt4 сигнал управления записью блока 16;

сигнал управления записью блока 17;

сигнал управления чтением регистра 21. Выходы шифратора 18 следующее назначение:

х17х13Х15

Х1Г

Yr

Y31имеют

V -

0

Y Y i,i

4

5

41

0

5

YT

Y Y1o

YnYn

сигналы установки в 1 триггеров 34-36 соответственно; сигналы установки в О триггеров 34-36 соответственно; сигнал запуска формирователя 37; соответственно сигналы записи и считывания блока 16;

сигналы записи и отключения (перевода в третье состояние) регистра 21 ;

сигнал подключения на передачу блока 29 шинных формировател-ей; сигнал отключения шинных формирователей за- датчиков (блокировка выдачи информационных

Y., 15

YU

17

Y -

Y -

Yz,v121

Y23

15

и управляющих сигналов в задатчиках); сигнал блокировки приема управляющих сигналов в задатчиках; сигнал отключения шин- ных формирователей внешних устройств (6ло кировка приема и выда- д чи информационных и выдачи управляющих сигналов во внешних устройствах); сигнал блокировки приема управляющих сигналов во внешних устройствах; сигнал записи регистра 19;20 сигнал записи регистра 20;

сигнал считывания блока 17;

сигнал отключения ( ревода выходов в третье состояние) регистра 20 ;

сигнал отключения бпока 23;

сигнал отключения ре гистра 19, блока 28 сигнал записи регистра 22;

15646288

В регистр 22 записывается искаженное информационное сОтово,, поступающее через блок 24 и шифратор 30 с магистрали 10.

Блоки 23-29 шинных формирователей служат для подключения устройства к магистралям 9 и 10 ЭВМ 2 и шинам 14 и 15 t3BM 3. Каждый блок может включать несколько микросхем типа К589АП16, К559ИП2, К559ИП1, К589АП26 и т.п.

30

Блоки 24, 27, 25 и 26 постоянно работают на передачу информации, блоки 23, 28 и 29 включаются на передачу сигналами от шифратора 18.

Шифратор 30 необходим для внесения искажений в информационное слово считьюаемое с шины 10 (9), На каждый разряд слова, считываемого с интерфейса, приходится два разряда, считываемых с йлока 17, которыми кодируется искажение: 00 - константа 11 - константа 01 - инверсия; 10 - нет искажений.

Дешифратор 31 адресов служит для организации записи регистров 19 и 20 и блоков 16 и 17, Генератор 32 тактовых импульсов вырабатывает три серии неперекрывающихся тактовых импульсов (фиг.З). Мультиплексор 33 служит для передачи на шифратор 18 сигнала о том, что задатчик, для которого должна имитироваться неисправность, действительно подключен к магистрали (управляет в данный момент времени передачей адресов и данных по магистрали). На вход блока 25 поступают сигналы с шины Занято, которая есть в каждом задатчике, Активный сигнал на этой- шине свидетельствует о том, что данный задатчик управляет магистралью (9, 10) и формирует адреса внешних устройств. Триггеры 34-36 применяются для создания последовательностей действий при имитации неисправностей. Формирователь 37 служит для сообщения в ЭВМ 3- о том, что заданная неисправность введена. Выход формирователя 37 подключен к шине прерывания ЭВМ 3, и после окончания имитации неисправности он формирует импульс заданной длительности, который и сообщает ЭВМ 3 об окончании имитации.неисправности.

Y, сигнал чтения регистYWYn YISY« YaT

Yl Y«

Y3opa 22;

управляющие сигналы

интерфейса ИУС;

ШПРА;

ШППА;

ШБСВ ;

ШПВУ;

ШППР;

ШЗД; Y3 ШНД; Yn ШСБР.

Регистры 19 и 20 используются для записи блоков 16 и 17 соответственно. Выходы регистра 19 и блока 23 имеют три состояния (аналогично выходам регистров 20 и 21), так что на передачу в один момент времени рботает только один из них, другой отключен,

На регистре 21 фиксируется (запи сывается) информация с выхода блока 16, Три группы информационных выходов регистра соответствуют трем группам информации с выхода блока 1

5

д 0

5

30

35

40

45

50

55

Блоки 24, 27, 25 и 26 постоянно работают на передачу информации, блоки 23, 28 и 29 включаются на передачу сигналами от шифратора 18.

Шифратор 30 необходим для внесения искажений в информационное слово считьюаемое с шины 10 (9), На каждый разряд слова, считываемого с интерфейса, приходится два разряда, считываемых с йлока 17, которыми кодируется искажение: 00 - константа 11 - константа 01 - инверсия; 10 - нет искажений.

Дешифратор 31 адресов служит для организации записи регистров 19 и 20 и блоков 16 и 17, Генератор 32 тактовых импульсов вырабатывает три серии неперекрывающихся тактовых импульсов (фиг.З). Мультиплексор 33 служит для передачи на шифратор 18 сигнала о том, что задатчик, для которого должна имитироваться неисправность, действительно подключен к магистрали (управляет в данный момент времени передачей адресов и данных по магистрали). На вход блока 25 поступают сигналы с шины Занято, которая есть в каждом задатчике, Активный сигнал на этой- шине свидетельствует о том, что данный задатчик управляет магистралью (9, 10) и формирует адреса внешних устройств. Триггеры 34-36 применяются для создания последовательностей действий при имитации неисправностей. Формирователь 37 служит для сообщения в ЭВМ 3- о том, что заданная неисправность введена. Выход формирователя 37 подключен к шине прерывания ЭВМ 3, и после окончания имитации неисправности он формирует импульс заданной длительности, который и сообщает ЭВМ 3 об окончании имитации.неисправности.

Работа устройства описана для од ного режима - имитации сбоя в адресной части цикла для интерфейса ИУС

(ОСТ 24.908-80). Предлагаемое устройство может быть применено и в других интерфейсах, при этом изменяется логика работы шифратора 18.

Временные диаграммы режима показаны на фиг.З.

Имитации любой неисправности устройством 1 предшествует настройка этого устройства, заключающаяся в следующем,

1.Определяется, при появлении (или после появления) какого адреса на магистрали 10 будет имитироваться неисправность. Этот адрес из ЭВМ 3 записывается на регистр 19 (блок 23 при этом в третьем состоянии выключен) .

2.Определяется тип неисправности (отказ, сбой), номер задатчика1 на магистрали 10, который должен сформировать заданный в п,1 адрес, после чего данной неисправности присваивается определенный номер; который одновременно служит адресом в блок 17. По этому адресу (номеру неисправности) в блоке 17 хранится код искажения. Код искажения содержит 32 разряда .(для . 16-разрядного слова на магистрали 10) и задает отдельно для каждого из 16 разрядов тип искажения - константы О, 1, инверсия, нет искажения.

По адресу, определенному в п.1, и записанному в регистр 19, записыва- ется через блок 28 в блок 16 из ЭВМ 3 информация, определенная в п.2.

Затем на регистр 20 из ЭВМ 3 записывается номер неисправности (адрес для блока 17), после чего через блок 28 из ЭВМ 3 в блок 17 в два этапа записываются два 16-разрядных слова кода искажения. Блок 17 имеет два сигнала записи (59 и 60) которые и обеспечивают возможность такой последовательной записи с, помощью дешифратора 31 адресов, Сигнал . считывания в блок 17 один, поэтому счи тывается 32-разрядное слово, В момент времени, когда регистр 20 работает на передачу адресаа на вход блока 17, регистр 21 находится в третьем состоянии. Это обеспечивается логикой функционирования шифратора 18, В начальный момент времени после включения питания в ЭВМ 3 формируется сигнал сброса Xio, по которому сбрасываются триггеры 34-36: Y2, Y, - Х10.

Работа устройства 1 при имитации неисправности типа сбой, заданной в пп.1 и 2, начинается после записи в регистр 20 1 в разряд, который подключен к входу Xt,шифратора 18.

1)Yj0 X - сигнал отключения

регистра 20$

-Г ц сигнал отключения регистра 19, блока 28. Выход, подключенный к входу Х41, в регистре 20 имеет только два состояния, все остальные - три. Регистр 20 может быть реализован, например, на микросхемах К589ИР12 и 155ТМ2.

2)Y21 X2,- блок 23 работает на передачу информации с магистрали 10 на адресный вход блока 16.

3)На магистрали.10 (шины адреса данных - ШАДОО-ШАД15) появляется адрес, определенный в п.1 (фиг.З).

4)На шине ШПРА (X 2) появляется сигнал признака адреса X 17 1. .Этот сигнал не проходит в устройство (одно из 6-8), подключенное к магистрали 10 так как включен сигнал

Y 1, блокировка ШПРА в устройствах . Таким образом, операция адресации выбранного (одного из 6-8) устройства не состоится

5) Y, (XMX,-Xq+ XMX

ЬП 11

9 ЛПЛ г1х 10) Х6

считывание блока 16;

Yt Х1гХг,Х9 установка в триггера 34 (Xs)t

6)Y ,., , X 10 Xfi - запись регистра 21 - по переднему фронту Y f1 , После записи регистра 21 на входах X .,- Х4 появляется код 0101, в котором задано, что имитируется неисправность Х1 0, сбой X г I,

в адресной части цикля магистрали X+ lj на адресном входе блока 17 появляется адрес, по которому в нем хранится информация о типах искажений в адресе для каждого из 16 разрядов; на адресном входе мультиплексора 33 будет номер задатчнка, который должен сформировать данный адрес.

7)На входе Xg появляется 1 в том с.пучае, если адрес сформировал заранее определенный в п.2 задатчик.

8)Yig XrX7-Xg-X X5( XJ - считывание блока 17;

Y3 X -Xj-X - установка в

Т

1 1

триггера 35 (Х6)

9) Y2 .Xg -запись в регистр 22 искаженного адреса - по переднему фронту сигнала Y7,,

Ю)

г

X i X с, X 1

запись

блока 16 (так как имитируется одно кратный сбой).

11)Y5 )0- установка триггера 36.

12)Y13 X7 - блокировка выдачи адреса и сигнала ШПРА в задатчиках (фиг. 2) ;

Y ,( -, сброс сигнала блоки ровки ШПРА в устройствах-приемниках (6-8).

13)Yt4 X7

считывание регисл-ра 2.2 (или искажен ного адреса в магистраль 10).

14)YT XyXj- сброс триггера

Х11+ X7 XS + Y1SH,34,

15) Y45 Х7 Х дача сигнала ШПРА,

5-Х,э(Х

Ю

+ X ,„ ) - ви

(,

Х7 X1}-X5-Y сброс триг сброс триггера

16)Y, гера 35.

17)Y 36.

Таким образом, заканчивается имитация неисправности типа сбой в ад-ч ресной части цикла магистрали ЭВМ.

В зависимости от того, какое значение принял сигнал Х8 после установки в 1 триггера 34 (см. п.7), а также в зависимости от кода, записанного на регистре 21 после установки -в 1 триггера 34, далее может производиться три типа операций:

1)имитация отказа (если на регистре 21 записан соответствующий код X г 0);

2)имитация сбоя, которая отличается от имитации отказа тем, что происходит стирание информации в блоке 16 по адресу, заданному в. п.1 таким образом,обеспечивается одно- . кратность его действия;

3)разрешение нормальной работы ЭВМ 2 - следует снятие блокировки сигнала ШПРА (Y) на время, необходимое для фиксации адреса в одном из адресуемых устройств (6-8).

Имитация отката отличается от имитации сбоя только тем, что отсутствует сигнал Ys (фиг.З), т.е. в блоке 16 не стираемся информация о неисправное ти.

Разрешение нормальной работы ЭВМ 2 происходит следующим образом.

Если адрес на магистрали 10 не совпал с заданным в п„1 или совпал, но был сформирован не тем задатчиком (заданным в п.2), т„е. сигнал Х. 0, то происходит снятие блокиров

0

5

0

0

5

.5

0

5

0

5

ки сигнала ШПРА: Y

Xi Xj Х

х5х,

+ х, х.

1Ј 5 8 5

+ Xj-X, . При снятии сигнала ШПРА, которое автоматически последует после адресации выбранного (одного из 6-8) устройства, блокировка сигнала ШПРА устанавливается снова. Это происходит путем сброса триггера 34 установкой в

+ х, Хг.хэ-х4+ x,.x

Х3-Х4 ).

Таким образом обеспечивается разрешение нормальной работы ЭВМ 2.

В предлагаемом устройстве могут быть реализованы и другие режимы работы, типа сбой в информационной части, отказ в адресной части и другие.

Применение предлагаемого устройства при экспериментальном исследовании надежности позволяет значительно сократить сроки получения оценок н4&$Жйости резервированных вычислительных систем и повысить достоверность получаемых данных. Формула изобретения

Устройство для имитации отказов и сбоев ЭВМ, содержащее первый и второй блоки памяти, первый и второй регистры, триггер, первый, второй и третий блоки шинных формирователей, причем первые информационные входы первого и второго блоков шинных формирователей подключены к входу устройства для подключения к шине адреса данных исследуемой ЭВМ, вторые информационные входы первого и второго блоков шинных формирователей подключены к входу устройства для подключения к шине управления исследуемой ЭВМ, выход первого блока шинных формирователей соединен с входом адреса первого блока памяти, о т л и - ч ающееся тем, что, с целью расширения функциональных возможностей за счет имитации отказов и сбоев в циклах Адрес и Данные магистрали ЭВМ, оно содержит третий и.четвертый регистры, с четвертого по седьмой блоки шинных формирователей, дешифратор адресов, второй и третий триггеры, формирователь импульсов, мультиплексор, генератор тактовых импульсов, шифратор управляющих сигналов, шифратор искажений информации, причем выход третьего блока шинных формирователей соединен, с информационными входами первого и второго блоков памяти, выход первого

13

блока памяти соединен с информационным входом первого регистра, первый выход разрядов которого соединен с информационным входом четвертого блока шинных формирователей и адресным входом второго блока памяти, второй выход разрядов первого регистра соединен с адресным входом мультиплексора, информационный вход которого сое- динен с выходом пятого блока шинных формирователей, третий выход разрядов первого регистра подключен к первому - четвертому входам шифратора управляющих сигналов, первый и второй выходы которого соединены соответственно с S- и R-входами первого триггера, третий и четвертый выходы шифратора управляющих сигналов

156

соединены соответственно с S- и R-BXO-дами второго триггера, пятый и шестой выходы шифратора управляющих сигналов соединены соответственно с S- и R-входами третьего триггера, пя-

. О

462814

вторым входами записи второго блока памяти, с тринадцатого по шестнадцатый выходы шифратора управляющих сигналов образуют выход блокировки устройства, выходы с семнадцатого по двадцать второй шифратора управляющих сигналов соединены соответственно с входами записи третьего и второго регистров считывания второго блока памяти, управления переводом выходов в третье состояние второго и третьего регистров и управления первого и третьего блоков шинных формирователей, двадцать третий и двад- четвертый выходы шифратора управляющих сигналов соединены соответственно с входами записи и чтения четвертого регистра, информационный вход которого соединен с выходом шифратора искажений информации, первый вход которого соединен с выходом второго блока памяти, второй вход шифратора искажений информации соединен с выхо15

20

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для имитации неисправностей | 1987 |

|

SU1444775A1 |

| Устройство для контроля неисправностей | 1991 |

|

SU1798787A1 |

| Устройство для имитации неисправностей | 1988 |

|

SU1661766A1 |

| Устройство для имитации сбоев | 1990 |

|

SU1836684A3 |

| Устройство для контроля за ходом вычислительного процесса | 1987 |

|

SU1539780A1 |

| Устройство для контроля неисправностей | 1987 |

|

SU1564626A1 |

| Устройство для контроля и перезапуска ЭВМ | 1987 |

|

SU1464162A1 |

| Устройство для сопряжения двух вычислительных машин | 1987 |

|

SU1474665A1 |

| Устройство для имитации неисправностей | 1988 |

|

SU1536388A1 |

| Имитатор абонентов | 1986 |

|

SU1325490A2 |

Изобретение относится к вычислительной технике и предназначено для имитации неисправностей при экспериментальном исследовании надежности и устойчивости функционирования структурно-избыточных вычислительных систем, построенных с использованием различных асинхронных магистральных интерфейсов. Цель изобретения - расширение функциональных возможностей устройства путем имитации неисправностей в циклах "адрес" и "данные" магистрали ЭВМ. Устройство 1 включает блоки памяти 16,17, шифратор 18, регистры 19-22, блоки шинных формирователей 23-29, шифратор 30, дешифратор адресов 31, генератор тактовых импульсов 32, мультиплексор 33, R+S-триггеры 34-36, формирователь импульсов 37. Работа устройства 1 основана на искажении информации (адресов, данных) при передаче ее по интерфейсам в исследуемой системе (ЭВМ). Применение предлагаемого устройства при экспериментальном исследовании надежности позволяет значительно сократить сроки получаемых оценок надежности резервированных систем и повысить достоверность получаемых данных. 3 ил.

тый, шестой и седьмой входы шифрато- 25 дом второго блока шинных формирова-

ра управляющих сигналов соединены с выходами соответственно первого, второго и третьего триггеров, седьмо выход шифратора управляющих сигналов соединен с входом формирователя импульсов, с восьмого по двенадцатый выходы шифратора управляющих сигналов соединены соответственно с входами записи и считывания первого блока памяти, записи и перевода выходов в третье состояние первого регистра и управления четвертого блока шинных формирователей, выход мультиплексора соединен с восьмым входом шифратора управляющих сигналов, с девятого по одиннадцатый входы которого соединены соответственно с первым, вторым и третьим выходами генератора тактовых импульсов, информационный вход шестого блока шинных формирователей соединен с входом устройства для подключения к шине управления исследуемой ЭВМ, с двенадцатого по двадцатый входы шифратора управляющих сигналов соединены с выходом шестого блока шинных формирователей, выход первого разряда второго регистра соединен с двадцать первым входом шифратора управляющих сигналов, с двадцать второго по двадцать шестой входы которого соединены соответственно с первого по пятый выходами дешифратора адресов, шестой и седьмой выходы которого соединены с первым и

0

5

0

5

0

5

телей, информационные входы второго и третьего регистров и дешифратора адресов и вход третьего блока шинных формирователей подключены к входу устройства для подключения к информационной шине управляющей ЭВМ, выходы третьего и второго регистров соединены с адресными входами соответственно первого и второго блоков памяти, выход четвертого блока шинных формирователей подключен к выходу устройства для подключения к информационной шине управляющей ЭВМ, вход управления дешифратора адресов соединен с входом устройства для подключения к шине управления управляющей ЭВМ, выход формирователя импульсов является выходом устройства для подключения к шине управления управляющей ЭВМ, выход четвертого регистра соединен с выходом устройства для подключения к шине адреса данных исследуемой ЭВМ, выходы с двадцать пятого по тридцать второй шифратора управляющих сигналов соединены с информационным входом седьмого блока шинных формирователей, выход которого соединен с выходом устройства для подключения к шине управления исследуемой ЭЕМ, информационный вход пятого блока шинных формирователей образован входами устройства для подключении к выходам занятости устройств исследуемой ЭВМ.

| Устройство для имитации сбоев | 1983 |

|

SU1107126A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для имитации сбоев | 1985 |

|

SU1298925A2 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-05-15—Публикация

1987-11-09—Подача