Изобретение относится к цифровой технике в области контрольно-измерительной и вычислительной аппаратуры, и может быть использовано в космической, авиационной, кораблестроительной и др. отраслях в качестве контрольно-отладочного комплекса и устройства внутрисхемного программирования программируемого постоянно запоминающего устройства (ППЗУ).

Известен встроенный модуль диагностирования (RU 130105 от 10.07.2013), управляемый по последовательной шине от компьютера (блока диагностики), содержащий контроллер последовательной шины, предназначенной для приема из блока диагностики управляющих тест-команд, сохраняемых в оперативном запоминающем устройстве (ОЗУ) модуля диагностирования, считываемых микроконтроллером, предназначенным для расшифровки управляющих тест-команд в последовательность микрокоманд путем обращения к постоянному запоминающему устройству (ПЗУ) микрокоманд, пересылки их через буферы как элементарных стимулирующих воздействий в объект диагностирования и считывания ответных реакций модуля диагностирования, выполненный в виде цифрового автомата, встроенного в объект диагностики и подключенного к шине объекта через разъем, при этом применен микроконтроллер с микропрограммным управлением, а в качестве управляющей памяти - постоянное запоминающее устройство микрокоманд с возможностью ее перепрограммирования.

Недостатком данного устройства является малая глубина тестирования системы и изменение содержимого управляющей памяти для каждой новой цифровой системы при проведении самой процедуры тестирования объекта диагностики. Кроме того, сам принцип формирования и передачи тестовых воздействий на объект диагностики для каждого объекта индивидуален, не систематизирован.

Наиболее близким устройством по сущности и достигаемому эффекту является программируемый JTAG-модуль диагностирования (RU 170434 от 25.04.2017), с управлением по линиям JTAG-интерфейса, который состоит из граничных регистров с мультиплексором, микроконтроллера, управляющей памяти, арбитра, ОЗУ, регистра инструкций и регистра данных. Модуль диагностирования управляется по линиям JTAG-интерфейса от ЭВМ и является встроенным в объект диагностики цифровым автоматом - подключается к системной шине.

Недостатком данного устройства является недостаточная глубина тестирования системы, пропорциональная количеству граничных регистров, усложнение изготовления печатной платы и самого объекта диагностики, обусловленное необходимостью внедрения микроконтроллера, граничных регистров, мультиплексора, арбитра, ОЗУ, регистра инструкций и регистра данных.

Задачей изобретения является возможность перепрограммирования, отладки аппаратных и программных средств ЭВМ, уменьшение количества внешней аппаратуры и уменьшение количества электро-радио элементов, устанавливаемых в ЭВМ для стыковки с внешними устройствами диагностики.

Поставленная задача достигается за счет внедрения отладочных средств в микросхему большой интегральной схемы (БИС), а также использования дополнительных регистров отладки, значительно расширяющих возможности диагностики системы в целом.

На фиг.1 представлена структурная схема цифрового отладочного комплекса (ЦОК), включающая в себя следующие элементы (средства отладки):

1.1- контроллер,

1.2 -дешифратор (Д);

2 - регистр инструкций (РИ);

3 - первый регистр данных (РД1);

4 - второй регистр данных (РД2);

5 - третий регистр данных (РД3);

6 - первый регистр сдвига (РС1);

7 - второй регистр сдвига (РС2);

8 - регистр адреса (РА);

9 - регистр останова (РО);

10 - компаратор (К);

11 - однобитный регистр (ОР);

12 - первый блок мультиплексоров (БМ1);

13 - второй блок мультиплексоров (БМ2);

14 - мультиплексор (М).

На схему ЦОК поступают четыре входных сигнала интерфейса JTAG - входной порт управления контроллером-дешифратором TMS, входной порт тестовых данных TDI, сигнал сброса TRST и входной тактовый сигнал ТСK. Сигналы ТСK, TMS, TRST поступают на контроллер-дешифратор, в котором вырабатываются сигналы управления поступающие на РС1 (6), РИ (2), РС2 (7), РД1 (3), РД2 (4) и РД3 (5), РО (9), РА (8), БМ1 (12), БМ2 (13) и Μ (14). Сигнал TDI поступает на БР (11), РС1 (6) и РС2 (7). К шине данных ЭВМ подключены К (10) и PC1 (6). PC1 (6) и РС2 (7) связаны информационными выходами с первым и вторым входами Μ (14). РС2 связан шиной данных с РИ (2), РД1 (3), РД2 (4), РД3 (5), РО (9) и БМ2 (13).

Выходы регистров РИ (2), РД1 (3), РД2 (4), РД3 (5) и вход БМ1 (12) посредством своих соответствующих шин подключены к шине управления ЭВМ, при этом выход РИ посредством своей шины дополнительно связан с входом инструкций Д.

БМ1 (12) подключен к шине управления ЭВМ и связан первой шиной мультиплексоров (ШМ1) с РС2 (7). БМ2 (13) связан второй шиной мультиплексоров (ШМ2) с РА (8), который шиной регистра адреса, связан с К (10) и БМ1 (12). РО (9) шиной регистра останова связан с К (10) и БМ1 (12). Шина адреса ЭВМ подключена к входу БМ2 (13) и входу К (10), в котором вырабатывается сигнал ОСТАНОВ для ЭВМ. Выход ОР (11) связан с третьим входом Μ (14), в котором вырабатывается сигнал TDO. Сигналы шины прерываний ЭВМ поступают на вход прерываний РД2 (4), на выходе сигнала прерываний которого формируется сигнал прерывания для внешнего диагностического устройства.

ЦОК входит в состав ЭВМ и предназначен для отладки аппаратуры ЭВМ и программного обеспечения. Выполняет следующие функции:

частичный контроль целостности печатного монтажа платы методом граничного сканирования (контроль шины данных и шины адреса);

внутрисхемное программирование НИЗУ ЭВМ;

доступ в память ЭВМ;

задание режимов работы ЭВМ;

связь ЭВМ с внешними устройствами диагностики через последовательный интерфейс JTAG (стандарт IEEE 1149.1).

Сигналы интерфейса JTAG поступают с внешних устройств диагностики на контроллер (1.1)-дешифратор (1.2) и регистры РС1 (6), РС2 (7), ОР (11). Контроллер JTAG является конечным автоматом, работа которого определена стандартом IEEE 1149.1. Контроллер-дешифратор формирует циклограмму выполнения операций загрузки и чтения регистров РИ (2), РД1 (3), РД2 (4), РД3 (5), РС1 (6), РС2 (7), РО (8), РА (9), а также по шине управления блока мультиплексоров, управляет мультиплексорами, входящими в состав блоков мультиплексоров БМ1 (12), БМ2 (13), и мультиплексором Μ (14).

На фиг.2 представлена диаграмма работы контроллера-дешифратора, которая определена стандартом IEEE 1149.1. Переходы между состояниями выполняются по положительному фронту сигнала ТСK и определяются значениями сигнала TMS в этот момент.

Контроллер-дешифратор выполняет следующие основные функции:

- в состоянии ЧТЕНИЕ_IR содержимое РИ выдается на шину РИ, затем на шину управления ЭВМ, по которой информация поступает на БМ1 из которого по шине ШМ1 загружается в РС2;

- в состоянии СДВИГ_IR выполняется последовательная выдача информации через порт TDO с одновременной загрузкой РС2 через порт TDI новой информации;

- в состоянии ЗАГРУЗКА_IR выполняется запись содержимого РС2 по шине данных РС2 в РИ;

- в состоянии ЧТЕНИЕ_RD информация одного из регистров РИ, РД1, РД2 и РД3, ранее указанного в РИ, по шине управления ЭВМ поступает на БМ1 из которого по шине ШМ1 загружается в РС2.

- в состоянии СДВИГ_RD выполняется последовательная выдача информации через порт TDO с одновременной загрузкой в РС1 или РС2 новой информации;

- в состоянии ЗАГРУЗКА_RD выполняется запись содержимого РС1 или РС2 в один из регистров: РИ, РД1, РД2, РД3, РО и РА, указанный в РИ.

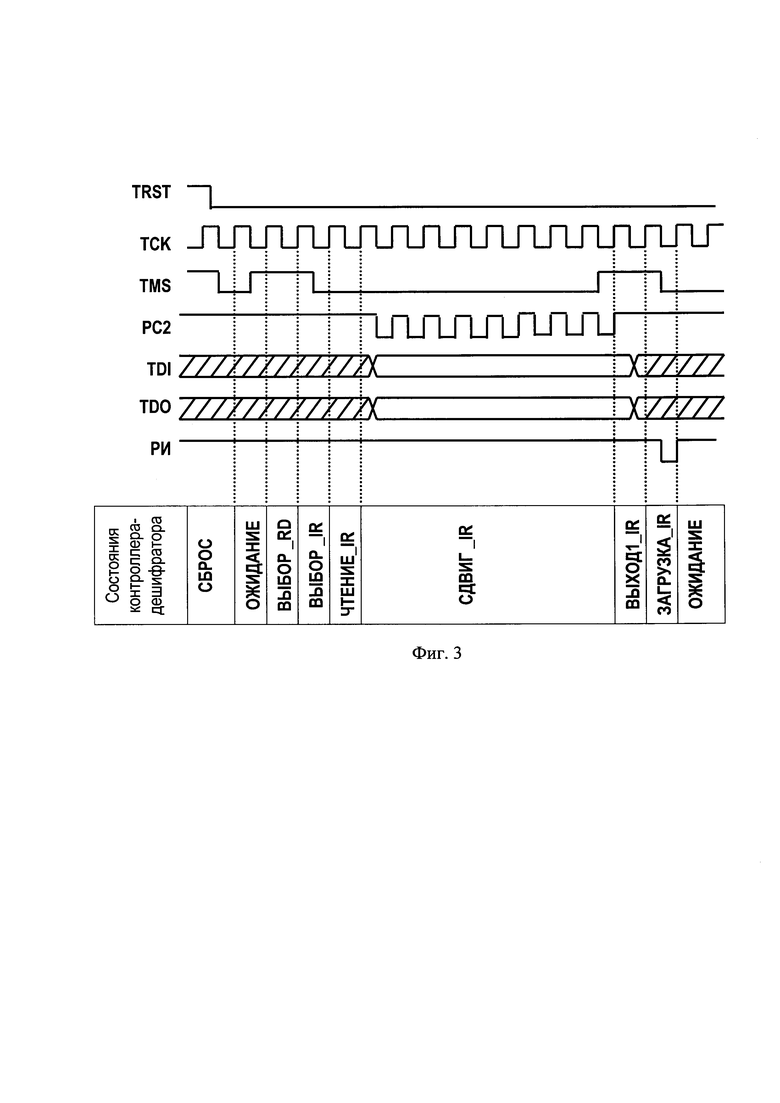

На фиг.3 и фиг.4 приведены циклограммы работы контроллера-дешифратора при начальной загрузке регистра РИ и выполнении загрузки в РД1.

Информация в РИ записывается из РС2 при состоянии ЗАГРУЗКА_IR контроллера-дешифратора. РИ в зависимости от загруженного в него кода вырабатывает сигналы управления, которые поступают на дешифратор, и управляют выбором регистра данных, в который будет производится загрузка/чтение. Также в РИ вырабатываются сигналы управления ЭВМ, которые поступают в шину управления ЭВМ, управляют технологическими сигналами записи/чтения ЗУ (запоминающего устройства, ПЗУ, ОЗУ) ЭВМ, обращения ЗУ и другие.

РД1, РД2, РД3, РА, РО, записываются параллельным кодом по сигналам управления которые вырабатывает дешифратор и выполняют следующие функции передачи и обработки информации:

- РД1 задание условий работы ЦОК РД1;

- РД2 получение информации о прерываниях ЭВМ;

- РД3 задание режимов работы ЦОК и ЭВМ;

- РА формирование адреса при обращении ЦОК к ЗУ;

- РО формирование данных для заданных условий работы ЦОК.

Запись в РС1 может производиться:

- параллельно во все разряды одновременно с шины данных при чтении из памяти по заявке ЦОК;

- последовательно побитно младшими разрядами вперед через порт TDI, когда контроллер-дешифратор находится в состоянии СДВИГ_RD, а в РИ загружен соответствующий код, при этом прежнее значение РС1 выдается через порт TDO.

Содержимое РС1 выдается параллельным кодом на шину данных при выполнении операции записи в память по заявке ЦОК.

Запись в РС2 может производиться параллельным кодом:

- при состоянии ЧТЕНИЕ_IR контроллера-дешифратора,

- при состоянии ЧТЕНИЕ_RD контроллера-дешифратора.

Запись в РС2 может производиться последовательным кодом через порт TDI:

- при состоянии СДВИГ_IR контроллера-дешифратора,

- при состоянии СДВИГ_RD контроллера-дешифратора, при этом прежнее значение РС2 выдается через порт TDO.

Для быстрой передачи информации из порта TDI в порт TDO используется ОР. Информация в него записывается из порта TDI по положительному фронту сигнала ТСK.

Информация ОР поступает на выход порта TDO, если контроллер-дешифратор находится в состоянии СБРОС, а также если в РИ загружен соответствующий код.

БМ1, БМ2 и Μ, управляются контроллером-дешифратором. В зависимости от кода, загруженного в РИ и состояния контроллера-дешифратора на выход БМ1, БМ2 и Μ поступает необходимая информация.

Компаратор сравнивает поступающие на него данные и в случае совпадения данных выдает сигнал ОСТАНОВ, который используется ЭВМ для остановки процессора.

Регистр инструкций РИ.

Информация в РИ записывается из РС2 при состоянии ЗАГРУЗКА_IR контроллера JTAG. Информация записываемая в РИ задает режим работы ЭВМ, а также определяет какой из двух регистров (РС1 или РС2) будет участвовать в операциях обмена по интерфейсу JTAG.

При записи "1" в 0-й разряд формируется заявка на обращение в память ЭВМ, после реализации заявка снимается.

"1" в 1-м разряде задает режим записи в память ЭВМ при обращении в память со стороны ЦОК.

При записи "1" во 2-й разряд выполняется безусловный останов ЭВМ.

При записи "1" в 3-й разряд РИ выполняется пуск ЭВМ из состояния останова или технологического сброса.

Если ЭВМ не находится в состоянии останова или сброса, значение 3-го разряда РИ игнорируется.

Если ЭВМ находится в состоянии останова, то при записи "1" одновременно во 2-й и 3-й разряды РИ ЭВМ выполняет следующую команду программы и останавливается (пошаговый режим работы).

4-й разряд РИ разрешает запись в регистры РД1, РД2, РД3 при состоянии ЗАГРУЗКА_RD контроллера JTAG.

5-й разряд определяет, какой из двух сдвиговых регистров будет участвовать в операциях обмена по интерфейсу JTAG.

С 5 по 7 разряды определяют регистр, в который будет записана информация из РС1 или РС2 при состоянии ЗАГРУЗКА_RD контроллера JTAG (таблица 1), а также определяют информацию, записываемую в РС1 или РС2 при состоянии ЧТЕНИЕ_RD контроллера JTAG.

Если 4-7 разряды равны нулю, информация с TDI выдается через ОР на выход TDO с задержкой на один такт TCK независимо от состояния контроллера JTAG.

Регистр РД1 (регистр управления режимами останова)

Информация в РД1 записывается из регистра РС2 параллельным кодом при состоянии ЗАГРУЗКА_RD контроллера JTAG и коде "1001" в (4-7) разрядах РИ.

0-й и 1-й разряды регистра РД1 задают условие останова ЭВМ:

- код 01 - после выполнения команды с заданным адресом;

- код 10 - по заданному времени в машинном цикле;

- код 11 - по обращению по заданному адресу;

- код 00 - условие останова не задано.

При задании останова по обращению по заданному адресу в (2-7) разрядах конкретизируется условие останова.

Когда контроллер JTAG находится в состоянии СБРОС, 0 и 1 разряды РД1 устанавливаются в ноль.

Регистр РД2 (регистр управления прерываниями)

Разряды 4-7 РД2 устанавливаются ЭВМ аппаратно. При наличии "1" хотя бы в одном из этих разрядов ЭВМ формирует сигнал запроса прерывания встроенного ЦОК для обработки определенных ситуаций, возникающих в ЭВМ.

Информация 4-7 разрядов РД2 записывается в (4-7) разряды РС2 при состояниях ЧТЕНИЕ_RD и ЧТЕНИЕ_IR контроллера JTAG и последовательным кодом через порт TDO выдается в тестирующее устройство.

Запрос на прерывание снимается программно при состоянии ЗАГРУЗКА_RD контроллера JTAG, коде "1010" в (4-7) разрядах РИ и "1" в соответствующем разряде РС2. При этом информация в (0-3) разрядах РС2 может быть произвольной.

Когда контроллер JTAG находится в состоянии СБРОС, (4-7) разряды РД2 устанавливаются в ноль.

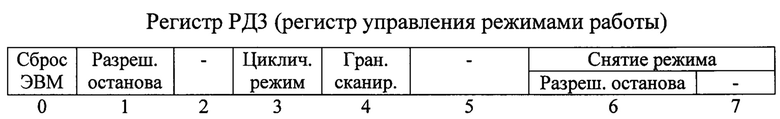

При установке "1" в 0-м разряде РД3 ЭВМ выдает сигнал СБРОС.Сигнал СБРОС снимается при записи "1" в 3-й разряд РИ.

1-й разряд РД3 опрашивается циклично и "1" в этом разряде разрешает останов ЭВМ в заданном цикле при выполнении условия останова. Разрешение останова снимается при записи "1" в 6-й разряд РД3.

Безусловный останов, инициируемый записью "1" во 2-й разряд РИ, выполняется независимо от наличия или отсутствия разрешения останова.

Запись "1" в 3-й разряд РД3 задает циклический режим работы ЭВМ, при котором при выполнении условия останова формируется сигнал СБРОС по окончании сигнала сброса ЭВМ начинает выполнять текущую программу с начала. Режим снимается при записи "0" в 3-й разряд РД3.

Запись "1" в 4-й разряд РД3 задает режим граничного сканирования, который снимается при записи "0" в 4-й разряд РД3.

Когда контроллер JTAG находится в состоянии СБРОС, снимаются все режимы, устанавливаемые РД3.

Регистр PA.

23-х разрядный РА задает разряды адреса при обращении со стороны ЦОК в память ЭВМ.

В РА переписываются разряды РС1 при состоянии ЗАГРУЗКА_RD контроллера JTAG и коде "1101" в 4-7 разрядах РИ.

Для упрощения обмена массивами информации между ЦОК и памятью ЭВМ после каждого обращения в память со стороны ЦОК значение адреса в РА увеличивается.

Организация доступа в память ЭВМ.

При загрузке регистра инструкций с "1" в 0-м разряде формируется запрос в ЭВМ в схему приоритетов по обращению в память. Этот запрос имеет самый низкий приоритет и выполняется в паузах при отсутствии обращений в память других устройств ЭВМ. При штатной работе ЭВМ объем читаемой из памяти информации ограничен и зависит от загруженности цикла работы ЭВМ.

Когда заявка на обращение в память принята, схема управления интерфейсом памяти формирует стандартную циклограмму обращения в память, при этом:

- при чтении информации из памяти ЭВМ прочитанное слово с шины данных записывается в РС1, затем выдается во внешнее тестирующее устройство через интерфейс JTAG;

- при записи в память ЭВМ на шину данных выдается слово данных из РС1.

Одновременно с выполнением обращения в память 4-й разряд РД2 устанавливается в "1" и формируется запрос на прерывание в ЭВМ.

Регистр РО.

РО загружается с PC1 и задает значения адреса команды, адреса памяти или счетчика относительного времени для соответствующих условных остановов.

Таким образом, заявлен цифровой отладочный комплекс интегрированный в объект диагностирования, подключенный к шинам данных, адреса и управления ЭВМ, с JTAG-интерфейсом с проводными линиями связи TCK, TMS, TDO, TDI и TRST, и содержащий мультиплексор (М), регистр инструкций (РИ) и регистр данных (РД1). Отличительная особенность комплекса заключается в том, что введены контроллер, дешифратор (Д), два блока мультиплексоров (БМ1 и БМ2), два регистра сдвига (РС1 и РС2), компаратор (К), регистр останова (РО), регистр адреса (РА), однобитный регистр (ОР) и два регистра данных (РД2 и РД3), при этом, входы сигналов TCK, TMS и TRST контроллера и вход сигнала TDI регистров PC1, РС2 и БР, являются входами комплекса, выход контроллера связан с входом Д, который первым выходом управления связан посредством шины управления блоков мультиплексоров с управляющими входами БМ1, БМ2 и М, Д выходами управления загрузки связан с соответствующими входами управления загрузки РИ, РД1, РД2, РД3, РС1, РС2, РО и PA, РС1 вход-выходом посредством шины данных ЭВМ связан с входом данных ЭВМ и первым входом К, РС2 выходом данных посредством шины данных регистра сдвига связан с входами данных РО, РИ, РД1, РД2, РД3 и первым входом БМ2, РС1 и РС2 информационными выходами связаны с первым и вторым входами М, выходы РИ, РД1, РД3 и первый выход РД2 связаны посредством шины управления с входом управления ЭВМ и первым входом БМ1, вход инструкций Д связан с выходом РИ, РД2 входом прерываний подключен к шине прерываний ЭВМ, второй выход РД2 является выходом сигнала прерываний для внешнего устройства, второй вход БМ2 и второй вход К подключены посредством шины адреса с портом адреса ЭВМ, вход загрузки РА связан с выходом БМ2, выход РО связан с третьим входом К и вторым входом БМ1, выход РА связан с вторым входом К и с третьим входом БМ1, выход К связан с входом сигнала останова ЭВМ, выход БР связан с третьим входом М, выход которого связан с входом сигнала TDO ЭВМ.

Техническим результатом изобретения является возможность проводить перепрограммирование, отладку аппаратных и программных средств ЭВМ, уменьшение количества внешней аппаратуры и уменьшение количества электро-радио элементов, устанавливаемых в ЭВМ для стыковки с внешними устройствами диагностики.

| название | год | авторы | номер документа |

|---|---|---|---|

| МУЛЬТИПЛЕКСОР ПЕРЕДАЧИ ДАННЫХ | 2005 |

|

RU2295148C1 |

| ТЕСТИРОВАНИЕ JTAG ТРАКТОВ ПЕРЕДАЧИ ДИСКРЕТНЫХ ДАННЫХ ПРИ ИСПОЛЬЗОВАНИИ СМЕННЫХ ПЕЧАТНЫХ ПЛАТ С УСТАНОВЛЕННЫМИ НА НИХ ЛОГИЧЕСКИМИ СХЕМАМИ JTAG | 1996 |

|

RU2182711C2 |

| Устройство для отладки программ микроЭВМ | 1989 |

|

SU1815643A1 |

| МИКРОКОМПЬЮТЕР И СПОСОБ ЕГО ТЕСТИРОВАНИЯ | 2006 |

|

RU2374679C2 |

| Устройство для отладки микроЭВМ | 1985 |

|

SU1410708A1 |

| Устройство для определения среднеквадратического значения переменного сигнала | 1989 |

|

SU1781686A1 |

| Устройство для сопряжения электронно-вычислительной машины с группой внешних устройств | 1985 |

|

SU1278866A1 |

| Устройство для контроля памяти | 1983 |

|

SU1280459A1 |

| ИМИТАТОР СИГНАЛОВ УПРАВЛЕНИЯ ПОЗИЦИОНИРОВАНИЕМ МАГНИТНЫХ ГОЛОВОК ОТНОСИТЕЛЬНО МАГНИТНЫХ ДИСКОВ | 1991 |

|

RU2017239C1 |

| МУЛЬТИПЛЕКСОР ТЕЛЕКОММУНИКАЦИОННЫЙ МНОГОФУНКЦИОНАЛЬНЫЙ | 2004 |

|

RU2269154C1 |

Изобретение относится к вычислительной технике. Технический результат заключается в обеспечении возможности проведения перепрограммирования, отладки аппаратных и программных средств ЭВМ. Цифровой отладочный комплекс, интегрированный в объект диагностирования, подключенный к шинам данных, адреса и управления ЭВМ, с JTAG-интерфейсом с проводными линиями связи TCK, TMS, TDO, TDI и TRST, и содержит мультиплексор (М), регистр инструкций (РИ) и регистр данных (РД1), при этом введены контроллер, дешифратор (Д), два блока мультиплексоров (БМ1 и БМ2), два регистра сдвига (РС1 и РС2), компаратор (К), регистр останова (РО), регистр адреса (РА), однобитный регистр (ОР) и два регистра данных (РД2 и РД3). 5 ил., 4 табл.

Цифровой отладочный комплекс, интегрированный в объект диагностирования, подключенный к шинам данных, адреса и управления ЭВМ, с JTAG-интерфейсом с проводными линиями связи TCK, TMS, TDO, TDI и TRST и содержащий мультиплексор (М), регистр инструкций (РИ) и регистр данных (РД1), отличающийся тем, что введены контроллер, дешифратор (Д), два блока мультиплексоров (БМ1 и БМ2), два регистра сдвига (РС1 и РС2), компаратор (К), регистр останова (РО), регистр адреса (РА), однобитный регистр (ОР) и два регистра данных (РД2 и РД3), при этом, входы сигналов TCK, TMS и TRST контроллера и вход сигнала TDI регистров PC1, РС2 и БР являются входами комплекса, выход контроллера связан с входом Д, который первым выходом управления связан посредством шины управления блоков мультиплексоров с управляющими входами БМ1, БМ2 и М, Д выходами управления загрузки связан с соответствующими входами управления загрузки РИ, РД1, РД2, РД3, РС1, РС2, РО и PA, РС1 вход-выходом посредством шины данных ЭВМ связан с входом данных ЭВМ и первым входом К, РС2 выходом данных посредством шины данных регистра сдвига связан с входами данных РО, РИ, РД1, РД2, РД3 и первым входом БМ2, РС1 и РС2 информационными выходами связаны с первым и вторым входами М, выходы РИ, РД1, РД3 и первый выход РД2 связаны посредством шины управления с входом управления ЭВМ и первым входом БМ1, вход инструкций Д связан с выходом РИ, РД2 входом прерываний подключен к шине прерываний ЭВМ, второй выход РД2 является выходом сигнала прерываний для внешнего устройства, второй вход БМ2 и второй вход К подключены посредством шины адреса с портом адреса ЭВМ, вход загрузки РА связан с выходом БМ2, выход РО связан с третьим входом К и вторым входом БМ1, выход РА связан с вторым входом К и с третьим входом БМ1, выход К связан с входом сигнала останова ЭВМ, выход БР связан с третьим входом М, выход которого связан с входом сигнала TDO ЭВМ.

| КЛАПАН ДЛЯ РАЗГРУЗКИ СГУЩЕННОГО ПРОДУКТА | 0 |

|

SU170434A1 |

| Трехфазная выпрямительная установка | 1959 |

|

SU130105A1 |

| US 6918057 B1, 12.07.2005 | |||

| US 6243842 B1, 05.06.2001 | |||

| US 5708773 A, 13.01.1998. | |||

Авторы

Даты

2022-06-07—Публикация

2021-01-11—Подача