Предлагаемое изобретение относится к цифровой вычислительной технике и может быть использовано при согласовании схем, имеющих различные уровни напряжений источников питания и(или) внутренних сигналов.

Известна Цифровая КМОП схема сдвига [1]. Это устройство предназначено для преобразования уровня напряжения входного сигнала с низкой амплитудой в выходной сигнал с уровнем напряжения высокой амплитуды (например, при сопряжении ТТЛ- и КМДП логических элементов).

Недостатком указанной выше схемы является низкое быстродействие. Низкое быстродействие схемы вызвано задержкой появления напряжения низкого уровня на затворах транзисторов защелки Р-типа, образующих обратную связь. Эта задержка вызвана разрядом узловых емкостей стоков и истоков транзисторов N- и Р-типа последовательно включенных между источником напряжения низкого уровня VSS и затворами транзисторов защелки Р-типа.

Задачей предлагаемого изобретения является повышение быстродействия Цифровой КМОП схемы сдвига.

Поставленная задача достигается тем, что в Цифровой КМОП схеме сдвига, содержащей полевые транзисторы Р-типа с первого по седьмой и N-типа с восьмого по четырнадцатый, вход сигнала IN, соединенный с затворами первого, восьмого и четырнадцатого транзисторов, вывод питания высокого уровня напряжения VCC, соединенный с истокам и подложкой первого транзистора, вывод питания высокого уровня напряжения VDD, соединенный, с истоками и подложками второго и третьего транзисторов, вывод питания низкого уровня напряжения VSS, соединенный с истоками восьмого, тринадцатого и четырнадцатого транзисторов и подложками транзисторов с восьмого по четырнадцатый, инверсный выход OUT, соединенный со стоками седьмого и десятого транзисторов, вход источника опорного напряжения  VDD, соединенный с затворами четвертого, пятого, девятого и десятого транзисторов, вход источника опорного напряжения

VDD, соединенный с затворами четвертого, пятого, девятого и десятого транзисторов, вход источника опорного напряжения  VDD, соединенный с затворами шестого, седьмого, одиннадцатого и двенадцатого транзисторов, причем стоки первого и восьмого транзисторов соединены с затвором тринадцатого, сток второго транзистора соединен с истоком и подложкой четвертого, сток которого соединен с истоком и подложкой шестого, сток шестого транзистора - со стоком девятого, а сток третьего транзистора соединен с истоком и подложкой пятого, сток которого соединен с истоком и подложкой седьмого, исток девятого транзистора соединен со стоком одиннадцатого, исток которого соединен со стоком тринадцатого, а исток десятого - со стоком двенадцатого, исток которого соединен со стоком четырнадцатого, затвор второго транзистора соединен со стоками седьмого и десятого транзисторов, а затвор третьего транзистора - со стоками шестого и девятого транзисторов.

VDD, соединенный с затворами шестого, седьмого, одиннадцатого и двенадцатого транзисторов, причем стоки первого и восьмого транзисторов соединены с затвором тринадцатого, сток второго транзистора соединен с истоком и подложкой четвертого, сток которого соединен с истоком и подложкой шестого, сток шестого транзистора - со стоком девятого, а сток третьего транзистора соединен с истоком и подложкой пятого, сток которого соединен с истоком и подложкой седьмого, исток девятого транзистора соединен со стоком одиннадцатого, исток которого соединен со стоком тринадцатого, а исток десятого - со стоком двенадцатого, исток которого соединен со стоком четырнадцатого, затвор второго транзистора соединен со стоками седьмого и десятого транзисторов, а затвор третьего транзистора - со стоками шестого и девятого транзисторов.

Таким образом, в предлагаемой схеме Высоковольтного преобразователя уровня напряжения, вследствие отличий от известного устройства, описанных выше, из цепочек последовательно соединенных транзисторов N- и Р-типа, включенных между источником напряжения низкого уровня VSS и затворами второго и третьего транзисторов Р-типа защелки, транзисторы Р-типа с четвертого по седьмой - исключены. Поэтому последовательные цепочки узловых емкостей по сравнению с Цифровой КМОП схемой сдвига, количественно укорочены, и, следовательно, суммарное время разряда этих узловых емкостей уменьшено. Таким образом, напряжение низкого уровня поступает на затворы второго и третьего транзисторов быстрее, вследствие чего быстродействие всей схемы Высоковольтного преобразователя уровня напряжения увеличивается.

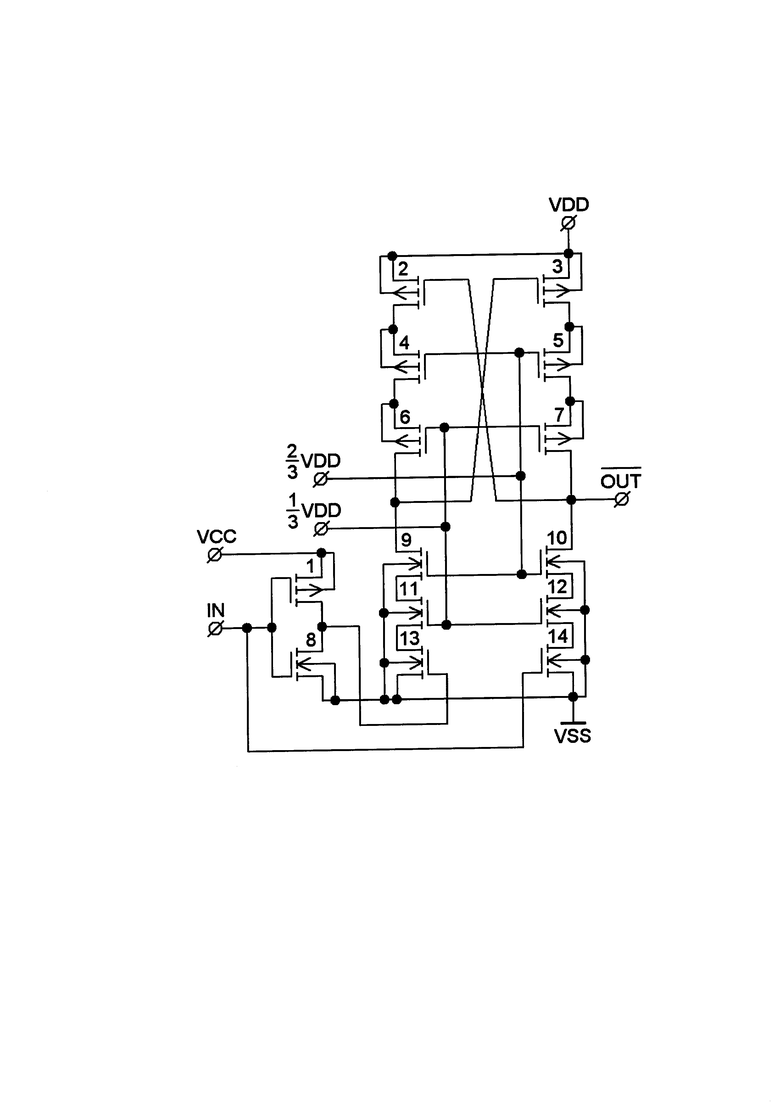

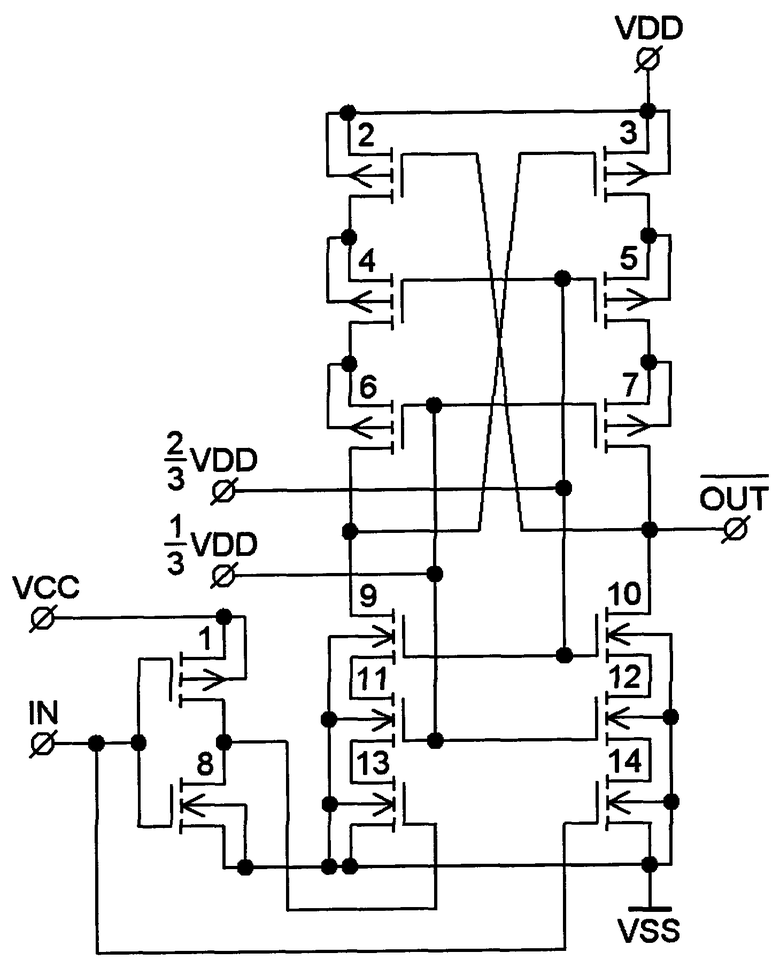

На чертеже приведена схема предлагаемого Высоковольтного преобразователя уровня напряжения.

Предлагаемый Высоковольтный преобразователь уровня напряжения, содержит полевые транзисторы Р-типа с первого по седьмой (1-7) и N-типа - с восьмого по четырнадцатый (8-14), вход сигнала IN, соединенный с затворами транзисторов первого (1), восьмого (8) и четырнадцатого (14), вывод питания высокого уровня напряжения VCC, соединенный с истокам и подложкой первого транзистора (1), вывод питания высокого уровня напряжения VDD, соединенный, с истоками и подложками транзисторов второго (2) и третьего (3), вывод питания низкого уровня напряжения VSS, соединенный с истоками транзисторов восьмого (8), тринадцатого (13) и четырнадцатого (14) и подложками транзисторов с восьмого по четырнадцатый (8-14), инверсный выход  , соединенный со стоками транзисторов седьмого (7) и десятого (10), вход источника опорного напряжения

, соединенный со стоками транзисторов седьмого (7) и десятого (10), вход источника опорного напряжения  VDD, соединенный с затворами транзисторов четвертого (4), пятого (5), девятого (9) и десятого (10), вход источника опорного напряжения

VDD, соединенный с затворами транзисторов четвертого (4), пятого (5), девятого (9) и десятого (10), вход источника опорного напряжения  VDD, соединенный с затворами транзисторов шестого (6), седьмого (7), одиннадцатого (11) и двенадцатого (12). Причем стоки транзисторов первого (1) и восьмого (8) соединены с затвором тринадцатого (13), сток второго (2) транзистора соединен с истоком и подложкой четвертого (4), сток которого соединен с истоком и подложкой шестого (6), сток шестого (6) транзистора - со стоком девятого (9), а сток третьего транзистора (3) соединен с истоком и подложкой пятого (5), сток которого соединен с истоком и подложкой седьмого (7), исток девятого (9) транзистора соединен со стоком одиннадцатого (11), исток которого соединен со стоком тринадцатого (13), а исток десятого (10) - со стоком двенадцатого (12), исток которого соединен со стоком четырнадцатого (14), затвор второго (2) транзистора соединен со стоками седьмого (7) и десятого (10) транзисторов, а затвор третьего (3) транзистора - со стоками шестого (6) и девятого (9) транзисторов.

VDD, соединенный с затворами транзисторов шестого (6), седьмого (7), одиннадцатого (11) и двенадцатого (12). Причем стоки транзисторов первого (1) и восьмого (8) соединены с затвором тринадцатого (13), сток второго (2) транзистора соединен с истоком и подложкой четвертого (4), сток которого соединен с истоком и подложкой шестого (6), сток шестого (6) транзистора - со стоком девятого (9), а сток третьего транзистора (3) соединен с истоком и подложкой пятого (5), сток которого соединен с истоком и подложкой седьмого (7), исток девятого (9) транзистора соединен со стоком одиннадцатого (11), исток которого соединен со стоком тринадцатого (13), а исток десятого (10) - со стоком двенадцатого (12), исток которого соединен со стоком четырнадцатого (14), затвор второго (2) транзистора соединен со стоками седьмого (7) и десятого (10) транзисторов, а затвор третьего (3) транзистора - со стоками шестого (6) и девятого (9) транзисторов.

Предлагаемый Высоковольтный преобразователь уровня напряжения представляет собой цифровое логическое устройство, предназначенное для преобразования входного сигнала с амплитудой от напряжения низкого уровня VSS («О») до напряжения логической единицы «1*» (VCC), в выходной сигнал с амплитудой от напряжения низкого уровня VSS («0») до напряжения логической «1», соответствующее напряжению питания высокого уровня напряжения VDD и работает следующим образом.

Исходное состояние. На вывод питания VSS и на вход EST подано напряжение низкого уровня, соответствующее напряжению логического «0», на вывод первого источника питания высокого уровня напряжения VCC - высокое напряжение, соответствующее для входного инвертора, выполненного на полевых транзисторах 1 и 8, напряжению логической «1*» и на вывод второго источника питания высокого уровня напряжения VDD - высокое напряжение, соответствующее выходному напряжению логической «1» Высоковольтного преобразователя уровня напряжения. Кроме того, на входе источника опорного напряжения  VDD установлено напряжение, соответствующее двум третям напряжения высокого уровня VDD, а на входе

VDD установлено напряжение, соответствующее двум третям напряжения высокого уровня VDD, а на входе  VDD - напряжение, соответствующее одной трети напряжения высокого уровня VDD, вследствие чего транзисторы и N- и Р-типа, на затворы которых поступают эти опорные напряжения - всегда открыты. Так как вход IN соединен с затворами транзисторов Р-типа 1 и N-типа 8 и 14, а на нем установлено напряжение низкого уровня VSS («0»), то транзистор Р-типа 1 открыт, а транзисторы N-типа 8 и 14 - закрыты. Поэтому, через открытый транзистор 1 на затвор транзистора 13 поступает напряжение высокого уровня VCC («1*»), вследствие чего транзистор N-типа 13 - открыт.Так как на затворы транзисторов N-типа 11 и 12 и Р-типа 6 и 7 поступает напряжение высокого уровня

VDD - напряжение, соответствующее одной трети напряжения высокого уровня VDD, вследствие чего транзисторы и N- и Р-типа, на затворы которых поступают эти опорные напряжения - всегда открыты. Так как вход IN соединен с затворами транзисторов Р-типа 1 и N-типа 8 и 14, а на нем установлено напряжение низкого уровня VSS («0»), то транзистор Р-типа 1 открыт, а транзисторы N-типа 8 и 14 - закрыты. Поэтому, через открытый транзистор 1 на затвор транзистора 13 поступает напряжение высокого уровня VCC («1*»), вследствие чего транзистор N-типа 13 - открыт.Так как на затворы транзисторов N-типа 11 и 12 и Р-типа 6 и 7 поступает напряжение высокого уровня  VDD, а на затворы транзисторов N-типа 9 и 10 и Р-типа 4 и 5 - напряжение высокого уровня

VDD, а на затворы транзисторов N-типа 9 и 10 и Р-типа 4 и 5 - напряжение высокого уровня  VDD, то транзисторы 4-7 и 9-12 - открыты. Кроме того, в результате действия предыдущего регенеративного цикла транзистор Р-типа 2 закрыт, а транзистор Р-типа 3 - открыт.Поэтому через открытые транзисторы 3, 5 и 7 на инверсном выходе

VDD, то транзисторы 4-7 и 9-12 - открыты. Кроме того, в результате действия предыдущего регенеративного цикла транзистор Р-типа 2 закрыт, а транзистор Р-типа 3 - открыт.Поэтому через открытые транзисторы 3, 5 и 7 на инверсном выходе  Высоковольтного преобразователя уровня напряжения установлено напряжение высокого уровня VDD («1»).

Высоковольтного преобразователя уровня напряжения установлено напряжение высокого уровня VDD («1»).

В режиме преобразования высокого напряжения логической единицы «1*» (VCC) в напряжение низкого уровня VSS («0»), на вход IN, и следовательно, на затворы транзисторов Р-типа 1 и N-типа 8 и 14, поступает напряжение логической единицы «1*» (VCC). Поэтому транзистор 1 закрывается, а транзисторы 8 и 14 открываются и через них на затвор транзистора 13 и на исток транзистора N-типа 12 поступает напряжение низкого уровня VSS («0»), в результате чего транзистор N-типа 13 закрывается, а через открытые транзисторы N-типа 12 и 10 напряжение низкого уровня VSS («0») поступает на затвор транзистора 2 и инверсный выход  Высоковольтного преобразователя уровня напряжения. Поэтому транзистор 2 открывается и через открытые транзисторы Р-типа 2,4 и 6 на затвор транзистора Р-типа 3 поступает напряжение высокого уровня VDD («1»), в результате чего транзистор 3 закрывается, защелка устанавливается в режим хранения, а на инверсном выходе OUT установлено напряжение низкого уровня VSS («0»).

Высоковольтного преобразователя уровня напряжения. Поэтому транзистор 2 открывается и через открытые транзисторы Р-типа 2,4 и 6 на затвор транзистора Р-типа 3 поступает напряжение высокого уровня VDD («1»), в результате чего транзистор 3 закрывается, защелка устанавливается в режим хранения, а на инверсном выходе OUT установлено напряжение низкого уровня VSS («0»).

При переходе Высоковольтного преобразователя уровня напряжения в исходное состояние и режим формирования на инверсном выходе  напряжения высокого уровня VDD («1»), на вход IN, и, следовательно, на затворы транзисторов Р-типа 1 и N-типа 8 и 14, поступает напряжение низкого уровня VSS («0»). Поэтому транзистор 1 открывается, а транзисторы 8 и 14 закрываются. Через открытый транзистор 1 на затвор транзистора 13 поступает напряжение высокого уровня VCC («1*»), вследствие чего он открывается и через него на исток транзистора 11 поступает напряжение низкого уровня VSS («0»). Так как транзисторы N-типа 9 и 11 открыты, то напряжение низкого уровня VSS («0»), поступает на затвор транзистора Р-Типа 3 и транзистор 3 открывается. Поэтому через открытые транзисторы Р-типа 3, 5 и 7 напряжение высокого уровня VDD («1») поступает на инверсный выход

напряжения высокого уровня VDD («1»), на вход IN, и, следовательно, на затворы транзисторов Р-типа 1 и N-типа 8 и 14, поступает напряжение низкого уровня VSS («0»). Поэтому транзистор 1 открывается, а транзисторы 8 и 14 закрываются. Через открытый транзистор 1 на затвор транзистора 13 поступает напряжение высокого уровня VCC («1*»), вследствие чего он открывается и через него на исток транзистора 11 поступает напряжение низкого уровня VSS («0»). Так как транзисторы N-типа 9 и 11 открыты, то напряжение низкого уровня VSS («0»), поступает на затвор транзистора Р-Типа 3 и транзистор 3 открывается. Поэтому через открытые транзисторы Р-типа 3, 5 и 7 напряжение высокого уровня VDD («1») поступает на инверсный выход  и на затвор транзистора Р-типа 2, в результате чего транзистор 2 закрывается, защелка устанавливается в режим хранения и схема Высоковольтного преобразователя уровня напряжения переходит в исходное состояние.

и на затвор транзистора Р-типа 2, в результате чего транзистор 2 закрывается, защелка устанавливается в режим хранения и схема Высоковольтного преобразователя уровня напряжения переходит в исходное состояние.

Таким образом, в предлагаемой схеме Высоковольтного преобразователя уровня напряжения, в отличие от Цифровой КМОП схемы сдвига в цепочках последовательно соединенных транзисторов N- и Р-типа, включенных между источником напряжения низкого уровня VSS и затворами транзисторов защелки Р-типа 2 и 3, транзисторы Р-типа с четвертого по седьмой - исключены. Поэтому последовательные цепочки узловых емкостей по сравнению с Цифровой КМОП схемой сдвига, укорочены количественно, и, следовательно, суммарное время разряда этих узловых емкостей уменьшено. Так как, напряжение низкого уровня поступает на затворы транзисторов 2 и 3 быстрее, то быстродействие всей схемы Высоковольтного преобразователя уровня напряжения увеличивается.

Литература

1. CMOS Digital Level Shift Circuit: Patent № US 6099100A / Won Kee Lee; assignee LG Semicon Co Ltd. - 8.08.2008.

| название | год | авторы | номер документа |

|---|---|---|---|

| ВЫСОКОВОЛЬТНЫЙ ПРЕОБРАЗОВАТЕЛЬ УРОВНЯ НАПРЯЖЕНИЯ | 2019 |

|

RU2712422C1 |

| ПРЕОБРАЗОВАТЕЛЬ УРОВНЯ НАПРЯЖЕНИЯ | 2018 |

|

RU2679186C1 |

| ПРЕОБРАЗОВАТЕЛЬ УРОВНЯ НАПРЯЖЕНИЯ | 2017 |

|

RU2667798C1 |

| ПРЕОБРАЗОВАТЕЛЬ УРОВНЯ НАПРЯЖЕНИЯ | 2016 |

|

RU2604054C1 |

| ПРЕОБРАЗОВАТЕЛЬ ЛОГИЧЕСКОГО УРОВНЯ НАПРЯЖЕНИЯ | 2016 |

|

RU2642416C1 |

| ТРЁХВХОДОВОЙ КМОП ЛОГИЧЕСКИЙ ВЕНТИЛЬ ИСКЛЮЧАЮЩЕЕ ИЛИ/ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ | 2020 |

|

RU2761172C1 |

| ЧЕТЫРЁХВХОДОВОЙ КМОП ЛОГИЧЕСКИЙ ВЕНТИЛЬ ИСКЛЮЧАЮЩЕЕ-ИЛИ/ИСКЛЮЧАЮЩЕЕ-ИЛИ-НЕ | 2022 |

|

RU2784457C1 |

| ПРЕОБРАЗОВАТЕЛЬ УРОВНЯ НАПРЯЖЕНИЯ | 2016 |

|

RU2632567C1 |

| ПРЕОБРАЗОВАТЕЛЬ УРОВНЯ НАПРЯЖЕНИЯ | 2021 |

|

RU2756445C1 |

| ПРЕОБРАЗОВАТЕЛЬ УРОВНЯ НАПРЯЖЕНИЯ | 2020 |

|

RU2739487C1 |

Изобретение относится к вычислительной технике и может быть использовано для построения быстродействующих высоковольтных преобразователей уровня напряжения, в том числе при сопряжении элементов электронных систем с несколькими источниками питания. Технический результат – повышение быстродействия Цифровой КМОП схемы сдвига. Для этого в схеме высоковольтного преобразователя уровня напряжения содержится семь полевых транзисторов Р-типа (1-7) и семь транзисторов N-типа (8-14), вход сигнала IN, входы источников опорного напряжения  VDD и

VDD и  VDD, инверсный выход

VDD, инверсный выход  , выводы питания высокого уровня напряжения VCC и VDD и низкого уровня напряжения VSS. 1 ил.

, выводы питания высокого уровня напряжения VCC и VDD и низкого уровня напряжения VSS. 1 ил.

Высоковольтный преобразователь уровня напряжения, содержащий полевые транзисторы Р-типа с первого по седьмой и N-типа - с восьмого по четырнадцатый, вход сигнала IN, соединенный с затворами первого, восьмого и четырнадцатого транзисторов, вывод питания высокого уровня напряжения VCC, соединенный с истокам и подложкой первого транзистора, вывод питания высокого уровня напряжения VDD, соединенный, с истоками и подложками второго и третьего транзисторов, вывод питания низкого уровня напряжения VSS, соединенный с истоками восьмого, тринадцатого и четырнадцатого транзисторов и подложками транзисторов с восьмого по четырнадцатый, инверсный выход  , соединенный со стоками седьмого и десятого транзисторов, вход источника опорного напряжения

, соединенный со стоками седьмого и десятого транзисторов, вход источника опорного напряжения  VDD, соединенный с затворами четвертого, пятого, девятого и десятого транзисторов, вход источника опорного напряжения

VDD, соединенный с затворами четвертого, пятого, девятого и десятого транзисторов, вход источника опорного напряжения  VDD, соединенный с затворами шестого, седьмого, одиннадцатого и двенадцатого транзисторов, причем стоки первого и восьмого транзисторов соединены с затвором тринадцатого, сток второго транзистора соединен с истоком и подложкой четвертого, сток которого соединен с истоком и подложкой шестого, сток шестого транзистора - со стоком девятого, а сток третьего транзистора соединен с истоком и подложкой пятого, сток которого соединен с истоком и подложкой седьмого, исток девятого транзистора соединен со стоком одиннадцатого, исток которого, соединен со стоком тринадцатого, а исток десятого - со стоком двенадцатого, исток которого соединен со стоком четырнадцатого, отличающийся тем, что затвор второго транзистора соединен со стоками седьмого и десятого транзисторов, а затвор третьего транзистора - со стоками шестого и девятого транзисторов.

VDD, соединенный с затворами шестого, седьмого, одиннадцатого и двенадцатого транзисторов, причем стоки первого и восьмого транзисторов соединены с затвором тринадцатого, сток второго транзистора соединен с истоком и подложкой четвертого, сток которого соединен с истоком и подложкой шестого, сток шестого транзистора - со стоком девятого, а сток третьего транзистора соединен с истоком и подложкой пятого, сток которого соединен с истоком и подложкой седьмого, исток девятого транзистора соединен со стоком одиннадцатого, исток которого, соединен со стоком тринадцатого, а исток десятого - со стоком двенадцатого, исток которого соединен со стоком четырнадцатого, отличающийся тем, что затвор второго транзистора соединен со стоками седьмого и десятого транзисторов, а затвор третьего транзистора - со стоками шестого и девятого транзисторов.

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| ПРЕОБРАЗОВАТЕЛЬ УРОВНЯ НАПРЯЖЕНИЯ | 2016 |

|

RU2604054C1 |

| ВЫСОКОВОЛЬТНЫЙ ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ | 2002 |

|

RU2231903C2 |

| ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ | 2011 |

|

RU2457601C1 |

Авторы

Даты

2019-10-14—Публикация

2019-03-14—Подача