Предлагаемое изобретение предназначено для локализации дефектов короткого замыкания между выводами микросхем с JTAG (Joint Test Action Group) интерфейсом, параллельно подключенных к информационной шине при производстве высоко интегрированных электронных модулей в авиации и космонавтике.

Электронные модули в авиации и космонавтике для повышения надежности функционирования выполняются в виде нескольких параллельно работающих однотипных каналов преобразования и обработки информации, обеспечивая «горячее резервирование». Функционал таких каналов реализован на сверхбольших интегральных микросхемах (СБИС), выполненных чаще всего в корпусах BGA (Ball Grid Array). Программное кон Фигурирование СБИС после изготовления модуля, как правило, выполняется через JTAG интерфейс, описанный в стандарте IEEE 1149.1 (IEEE Std 1149.1-2001 IEEE Standard Test Access Port and Boundary-Scan Atchitecture).

Пример электронного модуля с горячим резервированием в виде параллельной трехканальной структуры на трех интегральных микросхемах (ИМС1-ИМС3) с информационной шиной показан на Фиг. 1.

В процессе автоматизированной пайки микросхем в корпусах BGA могут возникать дефекты в виде короткого замыкания (КЗ) между их выводами, находящимися в подкорпусном пространстве микросхем (Фиг. 1), то есть в зоне физической недоступности. Для устранения данных дефектов вследствие неизвестности нахождения дефектов КЗ под конкретными корпусами микросхем удаляют все микросхем с платы, что существенно повышает процент брака, стоимость и время ремонта электронных модулей.

JTAG интерфейс кроме выполнения функции программирования микросхем может быть использован для поиска различных дефектов в линиях связи информационных шин, например, методом граничного (периферийного) сканирования (ГС) (Тестирование и тестопригодное проектирование. А. Городецкий. Компоненты и технологии. №2, 2009 г. стр. 6-7.).

Результат поиска дефектов методом ГС в виде обнаружения пар линий связи (ЛС): ЛС2-ЛС3, ЛС3-ЛС4 и ЛС2-ЛС4 в информационной шине, между которыми выявлен дефект короткого замыкания, показан на Фиг. 1 -Трехканальная структура электронного модуля с информационной шиной.

Однако применение метода ГС не позволяет определить, между выводами какой конкретно микросхемы, параллельно подключенной к линиям связи информационной шины с другими микросхемами, имеется дефект КЗ. Это приводит к неоправданным затратам средств и времени при устранении дефектов пайки, так как демонтажу с платы подвергаются все микросхемы, в том числе и не имеющие дефектов КЗ.

В технике известны различные способы локализации дефектов типа КЗ в линиях связи. Например, в приборах для обнаружения мест короткого замыкания в электрических схемах Toneohm 950 (Polar Toneohm Model 950. http://www.sovtest.ru/sites/default/files/Polar950.pdf) и Toneohm 970 (Toneohm 970. http: //www, polarinstruments. com/products/toneohm/toneohm970. html) фирмы Polar Instrument (Великобритания) используется высокочувствительный миллиомметр с векторным сопровождением поиска места локализации дефекта. В область предполагаемого расположения дефекта КЗ на плате подается питание и отслеживается зависимость изменений тока при перемещении пробника на плате. Поиск обеспечивают три указателя: цифровой, звуковой и векторный. Цифровой индикатор показывает значение тока, звуковой изменяет тональность по мере приближения к дефекту, а векторный - указывает направление движения тестового пробника.

Недостатками данного способа определения местоположения дефекта КЗ являются:

- необходимость физического контактирования элементов прибора с проводниками платы, имеющими защитное покрытие, при подключении внешнего тестового источника или щупов микровольтметра. Подключение к элементам схемы может оказаться невозможным на платах с высокой плотностью монтажа и минимальными размерами проводников;

- использование человека - оператора в процессе поиска дефекта, увеличивающее время и стоимость диагностики.

В способе определения места положения дефекта короткого замыкания (Авторское свидетельство №941910, кл. G01R 31/02, 1982 г.) основным информационным источником является датчик напряжения, определяющий падение напряжения на участках линии связи при последовательной коммутации вдоль линии связи источника тока с датчиком тока.

Недостатком данного метода определения местоположения дефекта КЗ является необходимость использования датчика напряжения микровольтового уровня для определения падения напряжения на проводниках печатной платы длиной 5-10 мм и необходимость его подключения к участкам печатных проводников, имеющих поверхностное защитное покрытие. Кроме того, для выявления местоположения нескольких дефектов КЗ в линии связи необходимо предварительно обнаруженный дефект устранять, что замедляет и усложняет процесс диагностики.

В методе локализации дефекта КЗ (Авторское свидетельство №1041963 А, кл. G01R 31/02, 1983 г. ) используются два датчика тока, жестко связанных между собой механически и четыре генератора напряжения, подключаемые к проводникам печатной платы. Наличие двух связанных датчиков тока и подключение 4-х генераторов импульсного напряжения к проводникам печатной платы требует достаточного пространства на печатной плате, которого может не быть при монтаже высокой плотности. Кроме того, в данном методе невозможно локализовать несколько дефектов КЗ, так как при этом будет возникать зона с отсутствием в проводниках линии связи токов между двумя дефектами короткого замыкания, что приведет к нарушению работы алгоритма.

Наиболее близким техническим решением (прототипом) является устройство и способ, описанные в (Патент №US 20080215942 A1, United States, 2008 г.). Сущность излагаемого в патенте способа локализации дефектов КЗ между выводами микросхем заключается в использовании метода граничного (периферийного) сканирования. Встроенный в микросхемы производителем JTAG интерфейс позволяет использовать выводы микросхем в качестве источников и приемников тестовых сигналов.

Диагностический комплекс устройства (прототипа), состоит из тестируемой платы, подключенной через контроллер USB (Universal Serial Bus)/JTAG интерфейса к управляющему компьютеру с программным обеспечением, содержащим: диагностические модели компонент (Boundary Scan Description Language (BSDL) файлы); файл межкомпонентных связей (net-list); программу формирования и анализа тестовых наборов, встроенные скрипты пользователя (script) и драйвер контроллера JTAG интерфейса.

В описании прототипа - патента (таблицы 1 и 2) приводятся алгоритмы определения короткого замыкания между выводами микросхем без использования дополнительного измерительного оборудования на основе анализа тестовых откликов тестируемой схемы.

Недостатком предлагаемого в прототипе - патенте способа определения дефектов короткого замыкания является невозможность точной локализации дефекта КЗ между выводами нескольких конкретных микросхем, параллельно подключенных к линиям связи. Это приводит к неоправданным потерям средств и времени при выполнении операций по устранению выявленных дефектов КЗ.

Целью предлагаемого способа является локализации дефектов короткого замыкания выводов интегральных микросхем с JTAG интерфейсом, подключенных параллельно к линиям связи информационных шин высокоинтегрированных электронных модулей.

Цель достигается за счет того, что: используется метод граничного сканирования для выявления пар линий связи в информационной шине с параллельно подключенными микросхемами, в которых имеется дефект короткого замыкания (на Фиг. 1 пары линий связи ЛС2-ЛС3, ЛС3-ЛС4 и ЛС2-ЛС4).

Кроме того для тестирования произвольно выбирают две линии связи - первая и вторая линия связи, в которой выявлен дефект КЗ, например, линии связи ЛС2 и ЛС3 на Фиг. 1.

Суть технического решения поясняется следующим чертежом:

На фиг. 1 изображена трехканальная структура электронного модуля с информационной шиной;

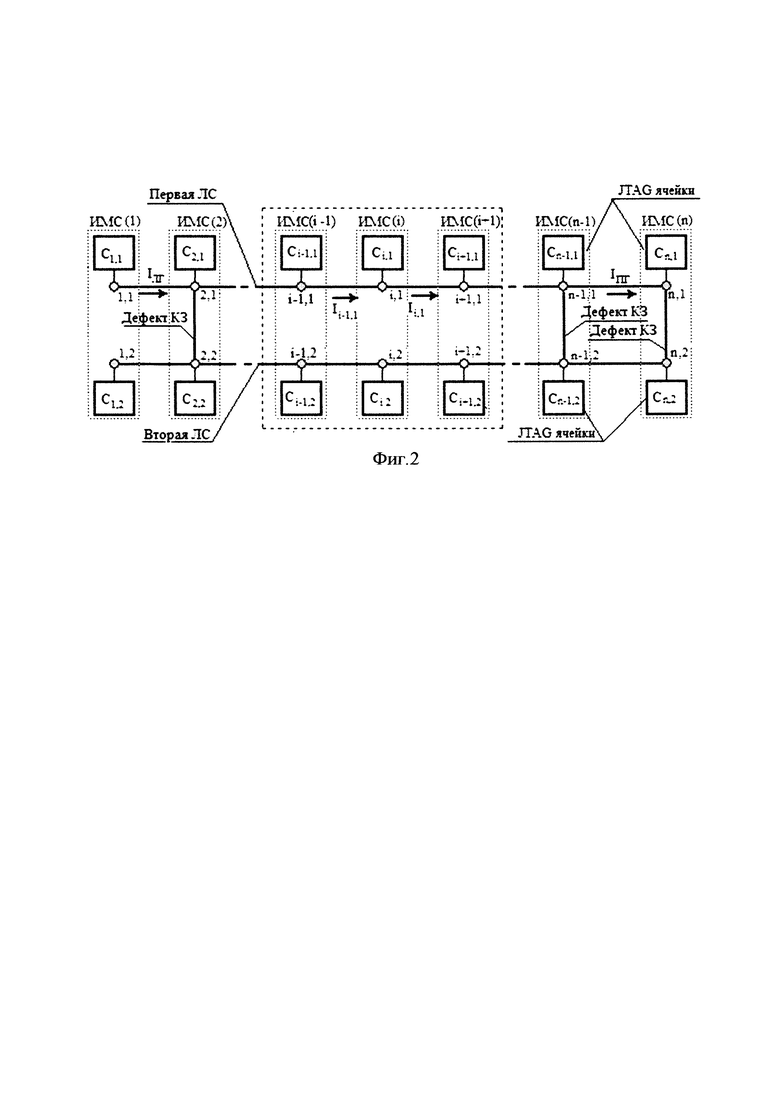

на фиг. 2 показаны первая и вторая линии связи с подключенными JTAG ячейками «n» микросхем;

на фиг. 3 представлена эквивалентная схема для расчета токов в проводниках первой ЛС;

на фиг. 4 изображены эквивалентные схемы расчета токов в проводниках левой границы (А) и правой границы (Б) первой линии связи;

на фиг. 5 показан структурная схема устройство для реализации способа локализации дефектов КЗ выводов JTAG микросхем;

на фиг. 6 представлена функциональная схема бесконтактного датчика тока.

На Фиг. 2 отдельно показаны первая и вторая линии связи информационной шины, к которым через JTAG ячейки параллельно подсоединены выводы «n» микросхем ИМС(1) -ИМС(n). Микросхемы подключены к первой и второй ЛС через встроенные в них JTAG ячейки регистра граничного сканирования: C11/C1,2 - ИМС(1)… Cn,1/Cn,2 - ИМС(n). Первый индекс JTAG ячейки указывает номер ИМС, подключенной к ЛС, второй индекс JTAG ячейки указывает номер ЛС (первая или вторая ЛС). Для примера, на Фиг. 2 показано наличие дефектов КЗ между выводами 2,1/2,2 - ИМС(2); между выводами n-1,1/n-1,2 - ИМС(n-1); между выводами n,1/n,2-ИМС(n).

Все JTAG ячейки выводов микросхем, подключенных к линиям связи с выявленными дефектами короткого замыкания, отключают, переводом их в высокоимпендансное состояние (Z).

Произвольно выбирают три рядом расположенные микросхемы с JTAG интерфейсом, выводы которых подключены к первой и второй линиям связи информационной шины. На Фиг. 2 показаны произвольно выбранные три рядом расположенные микросхемы: ИМС(i-1); ИМС(i) и ИМС(i+1).

JTAG ячейку Ci,2 средней из трех выбранных микросхем, подключенную к второй ЛС устанавливают в состояние логического нуля, JTAG ячейки выбранных трех микросхем, подключенные к первой линии связи - Ci-1,1; Ci,1; Ci+1,1 стимулируют тестовыми наборами вида: ZZ1; Z1Z; Z11; 1ZZ; 11Z; 111. В тестовом наборе выключенному состоянию JTAG ячейки соответствует символ Z, состояние логической единицы JTAG ячейки соответствует символ 1. Всего формируют шесть тестовых наборов, исключая тестовый набор ZZZ. В результате стимуляции тест наборами трех JTAG ячеек выбранных трех микросхем на участках первой ЛС, между микросхемами ИМС(i-1)/ ИМС(i) и ИМС(i) ИМС(i+1) будут протекать токи Ii-1,1; Ii,1 (Фиг. 2) для определенных тест наборов.

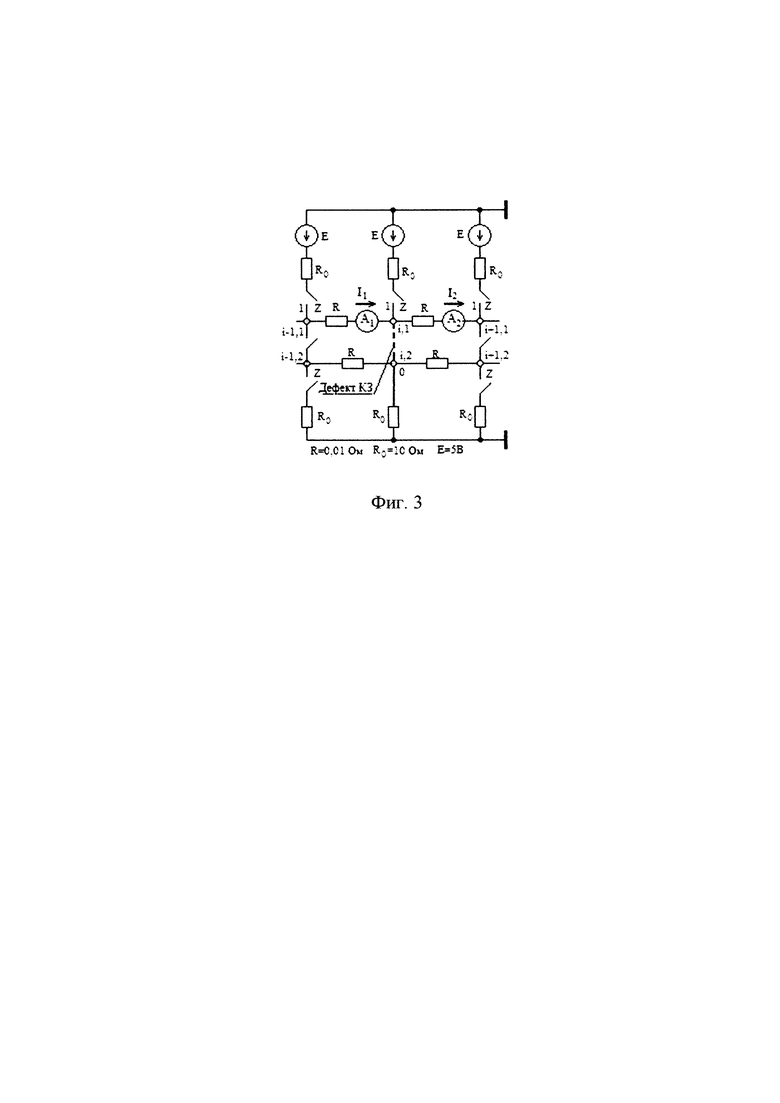

Эквивалентная схема для расчета токов в проводниках первой ЛС показана на Фиг. 3

JTAG ячейка в состоянии логической «1» представлена на эквивалентной схеме источником напряжения Е, внутренним сопротивлением драйверов R0 и положением замкнутого ключа «1» (Фиг. 3). JTAG ячейка в состоянии логического «0» представлена внутренним сопротивлением драйверов R0 и положением ключа «0». JTAG ячейки, отключенные от ЛС в высокоимпендансном состоянии Z представлены разомкнутыми ключами в положении «Z» (Фиг. 3).

В эквивалентной схеме (Фиг. 3) для упрощения принято равенство токов: I1=Ii-1,1; ток I2=Ii,1.

Амперметры А1 и А2 измеряют токи I1 и I2 соответственно и имеют нулевое внутреннее сопротивление, моделируя работу бесконтактного измерителя тока.

В таблице №1 приведены значения нормированных токов I1/IMAX и I2/IMAX в проводниках первой линии связи при условии отсутствия дефекта КЗ между выводами ИМС(i) (JTAG ячейка Ci,2 установлена в состояние логического 0). Максимальный ток IMAX, определяется из условия протекания тока между соседними ячейками первой ЛС, находящимися в состоянии логической «1» и логического «0» соответственно (например между Ci-1,1 и Ci,1):

В таблице №2 приведены нормированные значения токов I1/IMAX и IMAX в проводниках первой линии связи при условии наличия дефекта КЗ между выводами ИМС(i) (JTAG ячейка Ci,2=0).

По полученным значениям токов выполняют расчет контрольного числа К для всех сочетаний состояния выводов трех выбранных микросхем (таблицы №1 и №2):

N=1…7 - номер тестового набора (таблицы №1, №2);

Х1, Х2 - логические переменные для нормированных токов I1/IMAX и

I2/IMAX соответственно;

Значения контрольных чисел K, приведенные в таблицах №1 и №2, рассчитывают по формуле (2) с учетом условий (3).

Определяют наличие дефекта короткого замыкания между выводами «i,1»и «i,2» (Фиг. 2, 3) центральной ИМС(i) из равенства контрольного числа K=945.

Эквивалентные схемы расчета токов в проводниках левой IЛГ и правой IПГ границ первой ЛС (Фиг. 2) приведены на Фиг. 4А и 4Б соответственно.

В таблице №3 приведены нормированные значения токов IЛГ/IMAX в левом граничном проводе первой линии связи для всех вариантов наличия дефектов КЗ между выводами ИМС(1) и ИМС(2); JTAG ячейка C1,2 установлена в состояние логического «0».

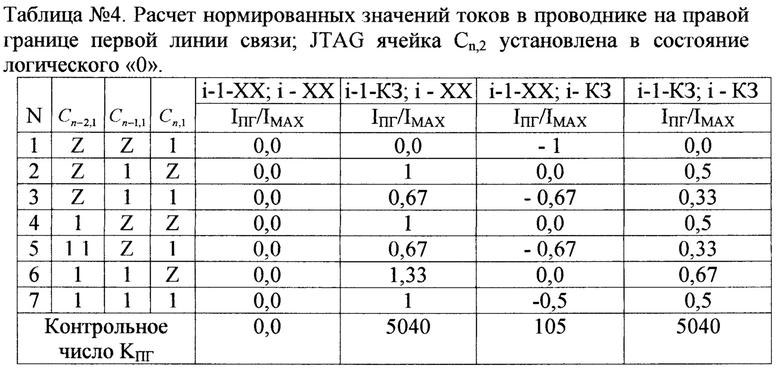

В таблице №4 приведены нормированные значения токов IПГ/IMAX в правом граничном проводе первой линии связи для всех вариантов наличия дефектов КЗ между выводами ИМС(n-1) и ИМС(n); JTAG ячейка Cn,2 установлена в состояние логического «0».

Контрольное число КЛГ для токов левой границы первой ЛС рассчитываются из выражения:

Контрольное число КПГ для токов правой границы первой ЛС рассчитываются из выражения:

N=1…7 - номер тестового набора (таблица №3, №4);

ХЛГ, ХПГ - логические переменные для нормированных токов IЛГ/ IMAX и IПГ/ IMAX соответственно;

Определяют наличие дефекта короткого замыкания между выводами ИМС(1), установленной на левой границе ЛС из равенства контрольного числа KЛГ=1260.

Определяют наличие дефекта короткого замыкания между выводами ИМС(n), установленной на правой границе ЛС из равенства контрольного числа KПГ=5040.

Наличие или отсутствие токов в проводниках первой ЛС определяют бесконтактным способом с использованием преобразователей напряженность магнитного поля Н, возбуждаемого протекающим в проводнике током в электрический сигнал.

С целью увеличения достоверности локализации дефектов КЗ осуществляют: предварительную идентификацию места определения тока на первой линии связи на участках первой ЛС и выбор порогового уровня то, соответствующего протеканию тока в проводнике.

Идентификацию места определения тока на первой линии связи выполняют последовательным формированием уровней логической «1» и логического «0» в двух JTAG ячейках рядом расположенных микросхем, подключенных к первой ЛС. Формирование начинают с JTAG ячеек C1,1 и С2,1 (Фиг. 2), устанавливая ячейку C1,1 состояние логической «1», ячейку С2,1 - в состояние логического «0». Все остальные JTAG ячейки находятся в отключенном высокоимпендансном состоянии (Z). В результате этого на участке первой ЛС между ИМС(1) и ИМС(2) будет протекать ток амплитудой IMAX, значение которой определяется из выражения (1). Сканирование следующих участков первой ЛС током IMAX осуществляется последовательным выбором вдоль первой ЛС стимулируемых JTAG ячеек: С2,1(«1»)/С3,1(«0»), остальные ячейки находятся в отключенном состоянии «Z». Последние стимулируемые ячейки в первой ЛС: Cn-1,1(«1») и Cn,1(«0») (Фиг. 2). В процессе последовательного сканирования первой ЛС выходной сигнал в виде логической «1» будет появляться в момент времени, когда стимулируются JTAG ячейки двух рядом расположенных микросхем, между которыми осуществляется бесконтактный способ определения наличия тока в проводнике.

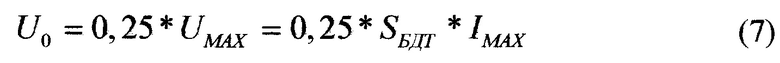

Определение порогового уровня, соответствующего протеканию тока в проводнике первой ЛС выполняют запоминанием напряжения UMAX, пропорционального максимальному току IMAX, протекающему в проводнике на участке первой ЛС, на котором в данный момент времени осуществляется определение его наличия. Пороговое значение напряжения U0 в соответствие с условиями (3) и (6) формируют путем четырехкратного деления напряжения UMAX:

SБДТ - коэффициент связи между током в проводнике IMAX и напряжением UMAX в бесконтактном способе определения наличия тока.

Определение порогового уровня наличия тока в ЛС позволяет уменьшить влияние дестабилизирующих факторов на результат определения тока в проводнике в виде нестабильности взаимного положения проводников и преобразователей напряженность магнитного поля в электрический сигнал.

Последовательным применением алгоритма, состоящего из определения местоположения бесконтактного способа индикации тока, калибровки порогового уровня, соответствующего наличию тока в проводнике и определения наличия токов в проводниках между стимулируемыми JTAG ячейками трех рядом расположенных микросхем с последующим расчетом контрольных чисел и их сравнении с эталонными значениями к каждой микросхеме, подключенной к первой и второй ЛС, определяют наличие или отсутствие дефектов короткого замыкания выводов для каждой тестируемой микросхемы первой и второй ЛС.

Последовательным применением алгоритма локализации дефектов короткого замыкания выводов всех микросхем, подключенных к первой и второй линиям связи информационной шины, определяют наличие или отсутствие дефекта короткого замыкания между выводами всех микросхем, подключенных ко всем линиям связи информационной шины, между которыми предварительно были выявлены дефекты короткого замыкания.

Для реализации предлагаемого способа локализации дефектов короткого замыкания выводов микросхем с JTAG интерфейсом в известное устройство (Патент № US 20080215942 A1, United States, 2008 г.) содержащее (Фиг. 5): персональный компьютер 1 (ПК), с установленным программным обеспечением 2, включающим: диагностические модели компонент (BSDL файлы); файл межкомпонентных связей (net-list), программу формирования и анализа тестовых наборов (Test software), встроенные скрипты пользователя (scripts), подключенный через JTAG контроллер 3 к JTAG интерфейсу 4 тестируемого электронного модуля 5 с информационной шиной 6, с целью определения наличия токов в проводниках линий связи информационной шины 6, введен бесконтактный датчик тока 7 (Фиг. 5). Бесконтактный датчик тока (БДТ) 7 связан посредством магнитного поля Н с током I, протекающим в проводниках линий связи информационной шины 6. Для синхронизации всех операций выполнения алгоритма локализации дефектов КЗ бесконтактный датчик тока 7 связан с персональным компьютером 1 интерфейсом JTAG 4 через контроллер JTAG интерфейса 3.

Бесконтактный датчик тока 7 устройства локализации дефектов КЗ между выводами JTAG микросхем (Фиг. 5) выполнен в виде (Фиг. 6): преобразователя магнитного поля в электрический сигнал 8, неинвертирующего 9 и инвертирующего 10 усилителей напряжения; первого 11 и второго 12 диодов, электронного ключа 13, нагрузочного сопротивления R3, схемы выборки и хранения (СВХ) 14, делителя напряжения 15 на резисторах R1 и R2, компаратора напряжения 16, микросхемы с JTAG интерфейсом 17 и кнопки активации работы устройства 18.

Преобразователь магнитного поля в электрический сигнал 8 выполнен на основе одного из физических эффектов: индукционного, эффекта Холла, магниторезистивного или гигантского магниторезистивного эффекта Giant Magneto-Resistive (GMR) (Бараночников М.Л. Микромагнитоэлектроника. Т. 1. - М: ДМК Пресс, 2001. - 544 с. ил.).

Выход преобразователя 8 подключен к входам неинвертирующего 9 и инвертирующего 10 усилителей. Выходы неинвертирующего усилителя 9 через первый диод 11 и выход инвертирующего усилителя 10 через второй диод 12 подключены к нагрузочному сопротивлению R3, к входу электронного ключа 13 и второму входу (вх2) компаратора напряжений 16. Выход электронного ключа 13 соединен с входом аналоговой памяти - схемой выборки и хранения (СВХ) 14, выход которой подключен к резистивному делителю напряжения 15 на сопротивлениях R1 и R2. Средняя точка делителя напряжений 15 подключена к первому входу (вх1) компаратора напряжений 16. Кнопка активации работы устройства 18 подключена одним выводом к шине земля, другим выводом через резистор R4 к источнику положительного напряжения и к JTAG ячейке «е» микросхемы 17. Входы управления электронного ключа 13, схемы выборки и хранения 14 и выход компаратора напряжения 16 подключены к соответствующим JTAG ячейкам «d», «с», «b» и «а» микросхемы 17. JTAG интерфейс микросхемы 17 соединен с JTAG интерфейсом 4 всего устройства (Фиг 5).

Использование инвертирующего усилителя 10, первого 11 и второго 12 диодов позволяет сделать схему БДТ нечувствительной к направлению тока в проводе ЛС, то есть не учитывать знаки токов (таблицы №№1-4) в формулах (2), (4), (5) для расчета соответствующих контрольных чисел.

Номинал нагрузочного сопротивления R3 выбран равным номиналу сопротивления R2. В этом случае, при отсутствии тока в проводе ЛС напряжения на резисторах R2 и R3 равны нулю и выходное напряжение компаратора 16 принимает значений логического нуля, соответствующего отсутствию тока в проводнике первой ЛС.

Циклами работ БДТ 7 через JTAG интерфейс 4 устройства управляет программа пользователя «script» (Фиг. 3), интегрированная в программный пакет 2 управляющего компьютера 1. Это позволяет синхронизировать процессы стимуляции JTAG ячеек тестируемых микросхем электронного модуля 5 и работу бесконтактного датчика тока 7 (Фиг. 5).

Бесконтактный датчик тока 7 (Фиг. 6) работает следующим образом.

В исходном состоянии кнопка активации работы устройства 18 разомкнута и JTAG ячейкой «е» микросхемы 17 считывается логическая «1», которая переводит ПК 1 устройства в режим ожидания. В этом режиме БДТ 7 устанавливается на выбранный участок первой ЛС между двух ИМС. Выходное напряжение компаратора напряжений 16 вследствие отсутствия стимуляции JTAG ячеек и токов в проводниках первой ЛС соответствует логическому «0».

При замыкании кнопки 18 JTAG ячейка «е» микросхемы 17 считывает значение логического «0» в ПК 1, и активирует работу программы локализации дефекта КЗ «script».

В режиме «Идентификация местоположения и калибровка порогового уровня БДТ» сигналами JTAG ячеек «d» и «с» микросхемы 17 (Фиг. 6) выполняется размыкание электронного ключа 13 и обнуление выходного напряжения СВХ 14. При этом выполняется программа «script», которая последовательно формирует пары логических сигналов «1» и «0» для всех JTAG ячеек, подключенных к первой ЛС (Фиг. 2).

При стимуляции очередной пары JTAG ячеек, между микросхемами которых установлен БДТ (например, между ИМС(i) и ИМС(i+1) - Фиг. 2), на выходе преобразователя магнитного поля в электрический сигнал 8, на выходе неинвертирующего усилителя 9 и на входе 2 компаратора напряжений 16 появится напряжение положительной полярности, соответствующее положительному направлению тока от JTAG ячейки Ci,1 к ячейке Ci+1,1 (Фиг. 2). Так как напряжение на входе 1 компаратора 16 равно нулю, его выходное напряжение примет значение логической «1», которое будет считано через JTAG ячейку «а» микросхемы 17 в ПК 1.

Таким образом, по совпадению моментов времени появления логической «1» на выходе компаратора 16 и номерам стимулируемых в данный момент времени JTAG ячеек определяется точное местоположение БДТ 7 между микросхемами, подключенными к первой ЛС.

При считывании сигнала логической «1» на выходе компаратора 16 программой «script» в JTAG ячейке «d» микросхемы 17 формируется сигнал замыкания ключа 13, а в ячейке «b» - сигнал записи напряжения с выхода неинвертирующего усилителя 9 в аналоговую память - СВХ 14. Напряжение UCBX на выходе СВХ 14 (Фиг. 6) при этом пропорционально максимальному току IMAX в проводнике первой ЛС в соответствие с (7). Делитель напряжения 15 формирует на резисторе R2 пороговое напряжение U1=0,25*UCBX в соответствие с условиями (3) и (6). Пороговое напряжение U1, будет удерживаться СВХ 14 в течение всего цикла формирования тестовых наборов для определения наличия или отсутствия токов в проводнике первой ЛС в режиме локализации дефектов КЗ. Таким образом, осуществляется калибровка порогового уровня U1 БДТ 7.

В режиме «Локализация дефектов КЗ» сигналом с JTAG ячейки «d» размыкается электронный ключ 13 и программой «script» на ПК 1 выполняется последовательная генерация тестовых наборов для JTAG ячеек (согласно таблицам №№1-4) в выбранных трех рядом находящихся ИМС, подключенных к первой ЛС (Фиг. 2). Для положительного направления тока от ИМС(i) к ИМС(i+1) положительное напряжение формируется на выходе неинвертирующего усилителя 9. Для обратного направления тока положительное напряжение формируется на выходе инвертирующего усилителя 10. Отрицательные напряжения на выходах усилителей 9 и 10 отсекаются соответствующими диодами 11 и 12. Таким образом, в режиме локализации дефектов КЗ на второй вход (вх2) компаратора напряжения 16 подается только положительное напряжение, независимо от направления тока в проводнике первой ЛС. Если напряжение на втором входе (вх.2) компаратора напряжений 16 будет больше опорного напряжения U1 на его первом входе (вх.1), то на выходе компаратора 16 формируется напряжение логической «1», соответствующее наличию тока в контролируемом проводнике, если меньше, на выходе компаратора 16 формируется напряжение логического «0», соответствующее отсутствию тока в контролируемом проводнике. Выходные напряжения компаратора 16 считываются через JTAG ячейку «а» микросхемы 17 в ПК 1 и используются программой «script» для расчета контрольных чисел K, KЛГ и KПГ (таблицы №№1-4) по формулам (2), (4) и (5).

Для микросхемы ИМС(1) (Фиг. 2) электронного модуля 4 (Фиг. 5), расположенной на левой границе ЛС расчет контрольного числа KЛГ выполняется только для положения БДТ 7 между ИМС(1) и ИМС(2). Равенство контрольного числа KЛГ эталонному значению 1260 указывает на наличие дефекта КЗ меду выводами ИМС(1).

Для микросхемы ИМС(n) (Фиг. 2) электронного модуля 4 (Фиг. 5), расположенной на правой границе ЛС расчет контрольного числа KПГ выполняется только для положения БДТ 7 между ИМС(n-1) и ИМС(n) по формуле (4). Равенство контрольного числа KПГ эталонному значению 5040 указывает на наличие дефекта КЗ меду выводами ИМС(n).

Для микросхем ИМС(2) -ИМС(n-1) (Фиг. 2) электронного модуля 4 (Фиг. 5) расчет контрольного числа K выполняется для двух положений БДТ 7: между ИМС(i-1)/ИМС(i) и между ИМС(i)ИМС(i+1) по формуле (2). Равенство контрольного числа K эталонному значению 945 указывает на наличие дефекта КЗ меду выводами ИМС(i).

При последующих изменениях положения БДТ 7 между микросхемами ЛС кнопка 18 размыкается и выполнение программы «script» останавливается.

После диагностики всех микросхем, подключенных к выбранной паре ЛС, тестируют все микросхемы, подключенные к остальным парам ЛС информационной шины, между которыми предварительно методом ГС выявлены дефекты короткого замыкания.

1. Использование предлагаемого способа контроля дефектов короткого замыкания между выводами JTAG микросхем и устройства для его реализации в виде совокупности отличительных признаков относительно известного способа (Патент №US 20080215942 A1, United States, 2008 г.) позволяет: осуществить локализацию дефектов короткого замыкания между физически недоступными выводами любого количества микросхем, подключенных к линиям связи информационных шин, полностью автоматизировать процесс локализации дефектов КЗ и обеспечить его высокую достоверность, что позволит существенно снизить затраты при производстве дорогостоящих высокоинтегрированных модулей современной электроники.

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ тестирования микросхем энергонезависимой памяти и устройство для его осуществления | 2023 |

|

RU2821349C1 |

| Устройство для бесконтактного измерения амплитуды импульсов тока в электронных цифровых блоках | 1981 |

|

SU1628021A1 |

| Оптоэлектронный цифровой преобразователь угла | 2018 |

|

RU2694759C1 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ДАННЫХ С МИКРОСХЕМ | 2017 |

|

RU2656582C1 |

| МНОГОФУНКЦИОНАЛЬНЫЙ ДИАГНОСТИЧЕСКИЙ КОМПЛЕКС | 2023 |

|

RU2815706C1 |

| АВТОМАТИЗИРОВАННЫЙ КОМПЛЕКС ДЛЯ ИСПЫТАНИЙ ИНТЕГРАЛЬНЫХ МИКРОСХЕМ НА РАДИАЦИОННУЮ СТОЙКОСТЬ | 2010 |

|

RU2435169C1 |

| ИНТЕГРАЛЬНАЯ ТЕСТОВАЯ СТРУКТУРА ДЛЯ ОЦЕНКИ НАДЕЖНОСТИ МЕТАЛЛИЗАЦИИ | 2011 |

|

RU2460169C1 |

| СИСТЕМА ФУНКЦИОНАЛЬНОГО ТЕСТИРОВАНИЯ КОРПУСИРОВАННЫХ МИКРОСХЕМ ОПЕРАТИВНО ЗАПОМИНАЮЩИХ УСТРОЙСТВ | 2009 |

|

RU2438164C2 |

| Устройство для обнаружения и локализации коротких замыканий в электронных блоках | 1984 |

|

SU1193609A1 |

| УСТРОЙСТВО ДЛЯ ЗАЩИТЫ ОТ ПЕРЕГРУЗКИ ПО ТОКУ ПРЕОБРАЗОВАТЕЛЯ ПОСТОЯННОГО НАПРЯЖЕНИЯ В ПОСТОЯННОЕ | 2008 |

|

RU2370884C1 |

Изобретение относится к области производства и диагностики высокоинтегрированных электронных модулей в авиационной и космической промышленности. Сущность: устройство содержит персональный компьютер с программным обеспечением, подключенный через JTAG контроллер к JTAG интерфейсу тестируемого электронного модуля и бесконтактный датчик тока в виде преобразователя магнитного поля в электрический сигнал, подключенный ко входам неинвертирующего и инвертирующего усилителей. Выход неинвертирующего усилителя через первый диод и выход инвертирующего усилителя через второй диод присоединены к нагрузочному сопротивлению, к входу электронного ключа и к второму входу компаратора напряжений. Выход электронного ключа соединен с входом аналоговой памяти, выход которой подключен к резистивному делителю напряжения средней точкой присоединенный к первому входу компаратора напряжений. Входы управления электронного ключа, схемы выборки и хранения, выход компаратора напряжения и кнопка активации устройства подключены к соответствующим JTAG ячейкам микросхемы. JTAG интерфейс микросхемы соединен с JTAG интерфейсом всего устройства. Технический результат: локализация дефектов короткого замыкания между выводами параллельно подключенных к информационной шине JTAG микросхем, увеличение достоверности результатов процесса локализации и его полная автоматизация. 2 н. и 3 з.п. ф-лы, 6 ил., 4 табл.

1. Способ локализации дефектов короткого замыкания выводов микросхем с JTAG интерфейсом, подключенных к информационной шине, заключающийся в формировании тестовых сигналов на выходе одной JTAG ячейки, подключенной через вывод микросхемы к линии связи, приеме тестовых сигналов другой JTAG ячейкой, подключенной через вывод микросхемы к другой линии связи и по отличию принятого тестового сигнала от переданного определяют наличие дефекта короткого замыкания между выводами микросхем, отличающийся тем, что все JTAG ячейки микросхем, подключенные к линиям связи информационный шины, между которыми предварительно выявлены дефекты короткого замыкания, отключают, переводом в высокоимпендансное состояние (Z), произвольно выбирают первую и вторую линию связи информационной шины с предварительно выявленным дефектом короткого замыкания, произвольно выбирают три рядом расположенные микросхемы, выводы которых подключены к первой и второй линиям связи, JTAG ячейку средней из трех микросхем, подключенную ко второй линии связи устанавливают в состояние логического нуля; JTAG ячейки выбранных трех микросхем, подключенных к первой линии связи стимулируют тест-наборами (логической единицей) следующего вида: ZZ1; Z1Z; Z11; 1ZZ; 1Z1; 11Z; 111, далее определяют наличие или отсутствие токов в двух проводниках первой линии связи между тремя выбранными микросхемами; рассчитывают контрольное число в виде суммы произведений номеров тестовых наборов (от 1 до 7) для ненулевых значений токов двух проводников первой линии связи и определяют наличие дефекта короткого замыкания между выводами средней из трех выбранных микросхем при условии равенства полученного контрольного числа одному их трех эталонных значений.

2. Способ по п. 1, отличающийся тем, что осуществляют предварительную идентификацию места определения тока на первой линии связи, выбор порогового уровня тока, соответствующего наличию тока в проводнике, путем последовательного попарного формирования сигналов высокого и низкого уровней JTAG ячеек в каждой из двух соседних микросхем, подключенных к первой линии связи при отключенных всех других, переведенных в высокоимпендансное состояние (Z), JTAG ячеек микросхем, присоединенных к первой и второй линиям связи.

3. Способ по п. 1, отличающийся тем, что последовательным применением указанного алгоритма локализации дефекта короткого замыкания между выводами одной микросхемы определяют наличие или отсутствие дефекта короткого замыкания между выводами всех микросхем, подключенных к первой и второй линиям связи информационной шины.

4. Способ по п. 1, отличающийся тем, что последовательным применением указанного алгоритма локализации дефекта короткого замыкания между выводами всех микросхем первой и второй линий связи определяют наличие или отсутствие дефекта короткого замыкания между выводами всех микросхем, подключенных ко всем линиям связи информационной шины, между которыми предварительно были выявлены дефекты короткого замыкания.

5. Устройство, реализующее способ, содержащее персональный компьютер с установленным программным обеспечением, включающим: диагностические модели компонент (BSDL файлы); файл межкомпонентных связей (net-list), программу формирования и анализа тестовых наборов, встроенные скрипты пользователя (scripts), подключенный через JTAG контроллер к JTAG интерфейсу тестируемого электронного модуля, отличающееся тем, что в него введен бесконтактный датчик тока, связанный посредством магнитного поля с проводниками линий связи и содержащий преобразователь магнитного поля в электрический сигнал, неинвертирующий и инвертирующий усилители, первый и второй диоды, сопротивление нагрузки, электронный ключ, схему выборки и хранения, резистивный делитель напряжения, компаратор напряжений, микросхему с JTAG интерфейсом и кнопку активации работы устройства при этом выход преобразователя магнитного поля в электрический сигнал параллельно подключен к входам усилителей, выход неинвертирующего усилителя через первый диод и выход инвертирующего усилителя через второй диод подключены к нагрузочному сопротивлению R3, к входу электронного ключа и к второму входу (вх2) компаратора напряжений, выход электронного ключа соединен с входом схемы выборки и хранения, выход которой подключен к резистивному делителю напряжения на сопротивлениях R1 и R2, средняя точка делителя напряжений соединена с первым входом (вх1) компаратора напряжений; управляющие входы электронного ключа, схемы выборки и хранения, кнопка активации устройства и выход компаратора напряжений присоединены к соответствующим JTAG ячейкам микросхемы, подключенной к JTAG интерфейсу устройства.

| US 20080215942 A1, 04.09.2008 | |||

| WO 2002042949 A1, 30.05.2002 | |||

| US 20170115346 A1, 27.04.2017 | |||

| ТЕСТИРОВАНИЕ JTAG ТРАКТОВ ПЕРЕДАЧИ ДИСКРЕТНЫХ ДАННЫХ ПРИ ИСПОЛЬЗОВАНИИ СМЕННЫХ ПЕЧАТНЫХ ПЛАТ С УСТАНОВЛЕННЫМИ НА НИХ ЛОГИЧЕСКИМИ СХЕМАМИ JTAG | 1996 |

|

RU2182711C2 |

| ТЕСТОВЫЙ РЕЖИМ ВЫСОКОГО ИМПЕДАНСА ДЛЯ JTAG | 1996 |

|

RU2191396C2 |

Авторы

Даты

2019-10-17—Публикация

2018-12-28—Подача