Изобретение относится к областям радиотехники, измерительной и вычислительной техники и может быть использовано в устройствах интегрирования в системах цифровой обработки сигналов, системах управления и специализированных вычислительных устройствах.

Известны цифровые интеграторы [1-3] на базе накапливающих сумматоров со сбросом, в которых отсутствует возможность непрерывного (текущего) интегрирования по выборке заданного объема, что снижает их быстродействие.

Известны цифровые интеграторы на базе цифровых усредняющих фильтров, например, с окном Дирихле [4] или с конечной импульсной характеристикой [5]. Их недостатком является сложность аппаратной реализации при большой выборке отсчетов сигнала.

Наиболее близким по технической сущности к предлагаемому устройству является цифровой интегратор, содержащий аналого-цифровой преобразователь (АЦП), генератор тактовых импульсов, сумматоры, многоразрядные регистры сдвига и регистр результата [6]. Его недостатком является сравнительно низкая точность, обусловленная использованием для численного интегрирования метода прямоугольников.

Задачей предлагаемого технического решения является повышение точности цифрового интегрирования сигнала по выборке отсчетов заданного объема. Для повышения точности интегрирования целесообразно использовать метод парабол (Симпсона) [7].

Поставленная задача решается тем, что цифровой интегратор, содержащий аналого-цифровой преобразователь (АЦП), генератор тактовых импульсов (ГТИ) и регистр результата (РР), дополнительно содержит многоразрядный регистр сдвига на пять отсчетов (МР5), вход которого соединен с выходом АЦП, первый сумматор, входы которого подключены ко второму и четвертому выходам МР5 и второй сумматор, входы которого подключены к третьему и пятому выходам МР5, первый и второй идентичные каналы накопления отсчетов (КНО), каждый из которых содержит m каскадно соединённых блоков накопления отсчетов (БНО). При этом k-й блок накопления отсчетов (БНО-k) состоит из многоразрядного регистра сдвига МР-k на

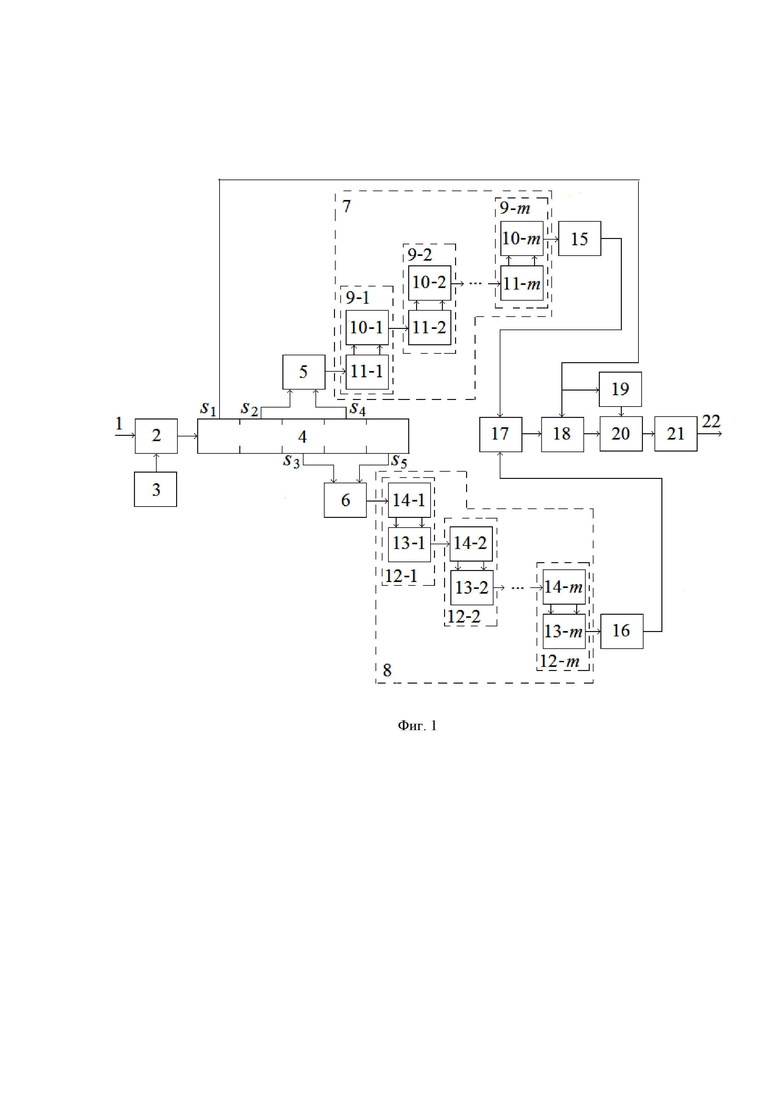

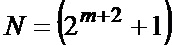

Предлагаемое техническое решение поясняется чертежами.

На фиг. 1 представлена структурная схема предлагаемого устройства.

1- Интегрируемый сигнал;

2- аналого-цифровой преобразователь АЦП;

3- генератор тактовых импульсов (ГТИ);

4- многоразрядный регистр сдвига на пять отсчетов (МР5);

5- первый сумматор;

6- второй сумматор;

7- канал накопления отсчетов КНО;

8- канал, идентичный каналу 7;

9- блоки накопления отсчетов канала 7 БНО-1 … БНО-m;

10- сумматор (СУМ-k);

11- МР-k, многоразрядный регистр сдвига на

12- блоки накопления канала 8;

13- сумматор канала 8;

14- многоразрядный регистр сдвига канала 8;

15- умножитель на 4;

16- умножитель на 2;

17- третий сумматор;

18- четвертый сумматор;

19- МР-N, многоразрядный регистр сдвига на

20- вычитатель;

21- регистр результата РР;

22- выход интегратора.

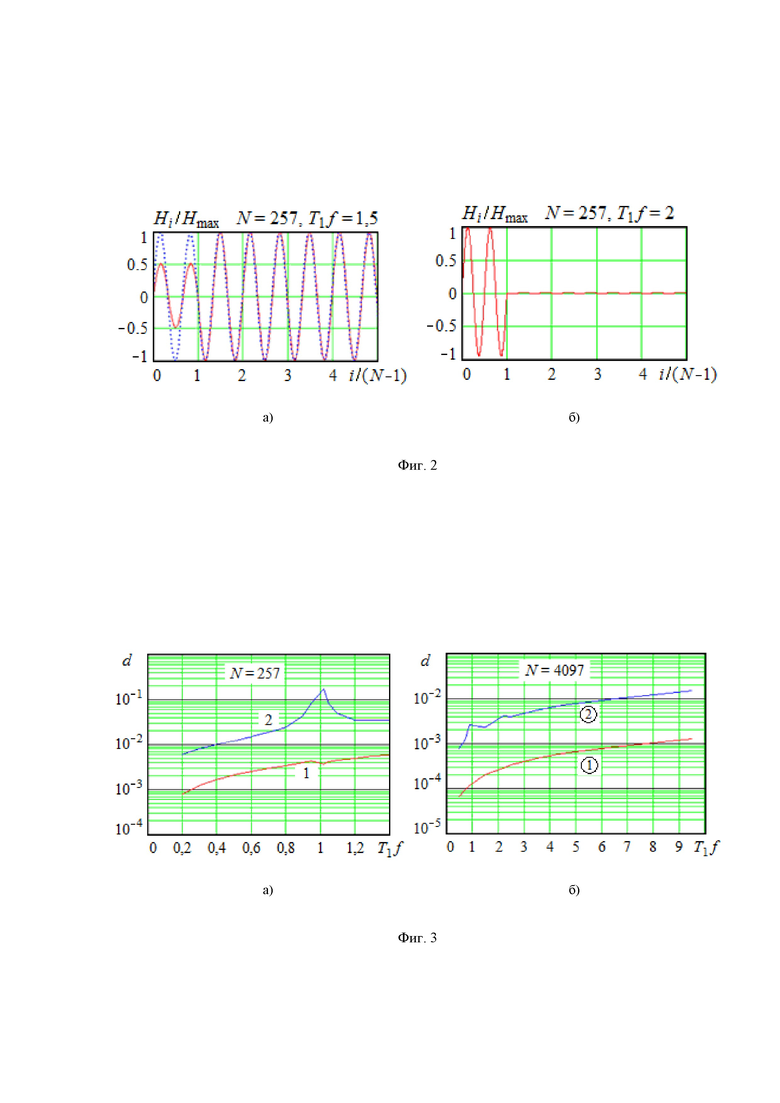

На фиг. 2 представлены временные диаграммы работы интегратора при гармоническом входном сигнале.

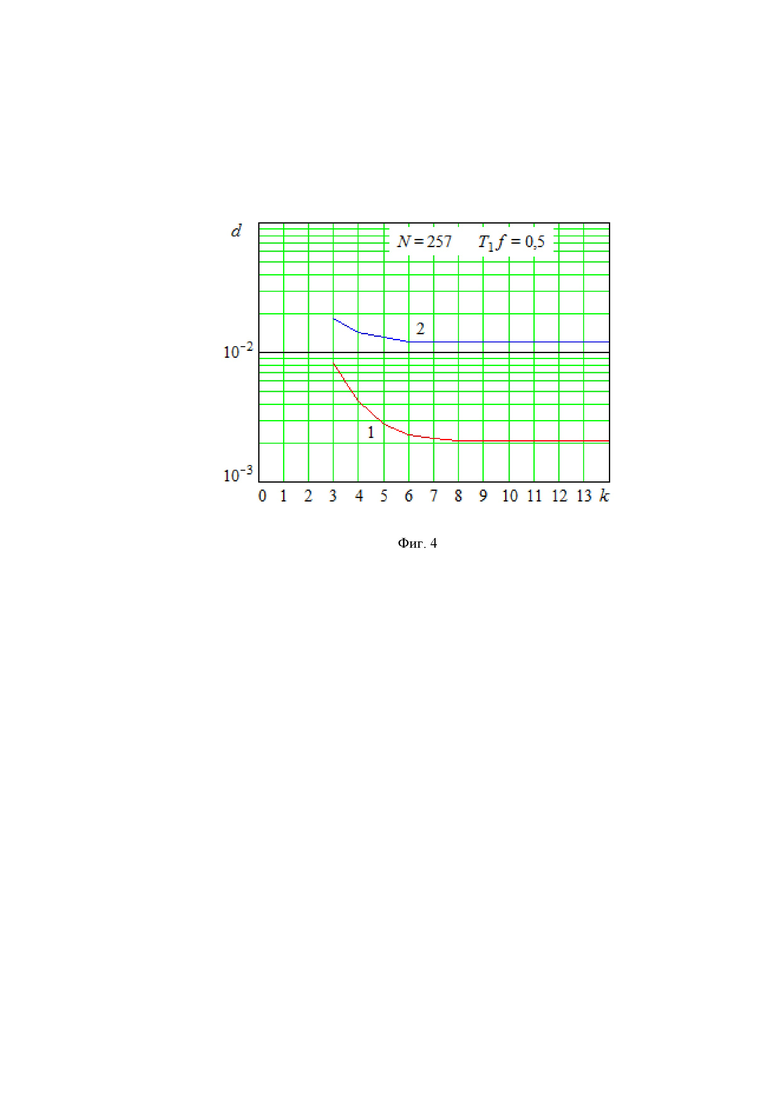

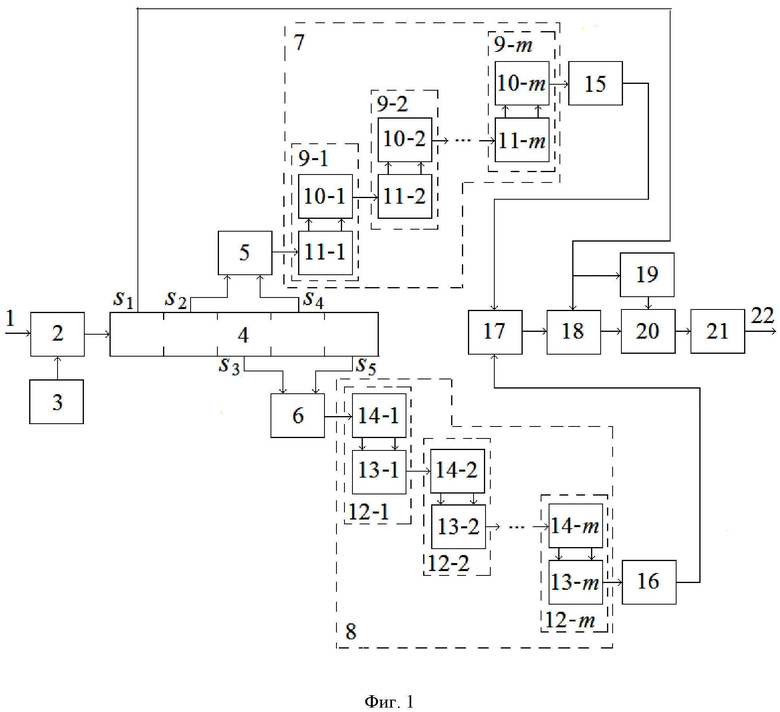

На фиг. 3-4 – представлены оценки относительной погрешности интегрирования.

Интегрируемый сигнал 1 поступает на вход АЦП 2, который по тактовым импульсам ГТИ 3, выход которого соединен с тактовым входом АЦП 2, формирует отсчеты, которые записываются в МР5 4, при этом ранее записанные данные сдвигаются вправо. Второй

Устройство работает следующим образом.

Входной сигнал

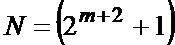

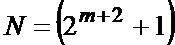

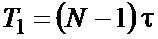

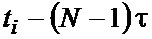

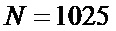

где m – целое число. Выбор N согласно выражению (1) обусловлен необходимостью организации быстрой вычислительной процедуры в КНО 7 и КНО 8. Интервал интегрирования равен

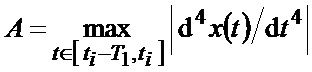

с абсолютной погрешностью R [7], равной

где

При заданном интервале интегрирования

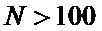

Для снижения погрешности необходимо использовать выборки отсчетов большого объема

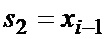

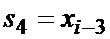

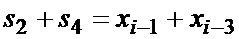

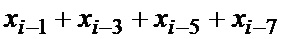

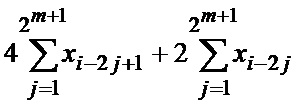

Отсчеты

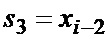

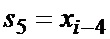

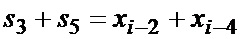

а во втором КНО 8 – соответственно

На вход первого БНО-1 первого КНО 7 с выхода сумматора 5 поступает величина

При этом для вычисления сумм (3) и (4) при условии (1) требуются минимальные вычислительные затраты. Например, при

На выходе третьего сумматора 17 формируется величина

к которой в четвертом сумматоре 18 добавляется значение

Эта величина записывается в регистр 21, и на его выходе появляется результат интегрирования 22.

Для вычисления полной суммы (6) требуется

Технически устройство наиболее целесообразно реализовать на базе программируемых логических интегральных схем (ПЛИС). Современные недорогие ПЛИС позволяют реализовать предлагаемое устройство при

Интервал интегрирования, равный

В случае гармонического входного сигнала

В результате имитационного моделирования работы интегратора согласно (2) формируется величина

Нормированная зависимость

На фиг. 2б показана зависимость

Для оценки относительной погрешности введем величину

где

На фиг. 3 приведены оценки погрешности интегратора (8), полученные с помощью имитационного моделирования. Нижние кривые 1 соответствуют предлагаемому устройству (методу парабол), а верхние кривые 2 – прототипу (методу прямоугольников). Величина

Всплески оценок (8) при целочисленных значениях

При ограниченной разрядности АЦП погрешность интегрирования увеличивается. На фиг. 4 приведены полученные в результате моделирования зависимости относительной погрешности d (4) от числа k разрядов АЦП для гармонического сигнала при

Величина погрешности зависит от формы сигнала и его параметров, однако предлагаемое устройство и в этих случаях обеспечивает существенное повышение точности интегрирования.

С уменьшением амплитуды сигнала относительно раствора АЦП погрешность повышается, то есть целесообразно проводить масштабирование преобразования сигнала в последовательность отсчетов. Увеличение числа разрядов АЦП позволяет расширить динамический диапазон интегратора.

Частота квантования АЦП от ГТИ должна выбираться не менее чем в 30-50 раз выше граничной частоты спектра входного сигнала.

Библиография.

1. Новиков Ю.В. Введение в цифровую схемотехнику. – М.: Интуит, 2016. – 393 с.

2. Дрозд А.В., Полин Е.Л., Нестеренко С.А., Николенко А.А., Ногина Е.Н. Устройство цифрового интегрирования // Авторское свидетельство SU 1532922А1, МПК G06F7/64 от 30.12.89 (Бюлл. № 48).

3. Полян Л.Е., Угер В.Г. Цифровой интегратор // Патент № 2029357, МПК G06F7/64 от 20.02.1995; заявка № 5043408/24 от 26.05.1992.

4. Гутников В.С. Фильтрация измерительных сигналов. – Л.: Энергоатомиздат, 1990. – 122 с.

5. Солонина А.И., Улахович Д.А., Арбузов С.М., Соловьева Е.Б. Основы цифровой обработки сигналов. – СПб.: БХВ Петербург, 2005. – 768 с.

6. Чернояров О.В., Сальникова А.В., Литвиненко В.П., Литвиненко Ю.В., Матвеев Б.В., Пчелинцев Е.А. Цифровой интегратор // Патент № 2670389, МПК G06F7/00 от 22.10.2018; заявка № 2018110562 от 26.03.2018.

7. Гусак А.А., Гусак Г.М., Бричикова Е.А. Справочник по высшей математике. – Мн.: ТетраСистеис, 1999. – 640 с.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЙ ИНТЕГРАТОР | 2018 |

|

RU2670389C1 |

| Цифровой измеритель действующего значения сигнала | 2018 |

|

RU2685062C1 |

| Цифровой измеритель отношения сигнал/шум сигналов с фазовой манипуляцией | 2023 |

|

RU2799234C1 |

| Цифровой измеритель отношения сигнал/шум сигналов с фазовой манипуляцией | 2024 |

|

RU2827313C1 |

| Цифровой некогерентный демодулятор сигналов с амплитудно-фазовой манипуляцией | 2021 |

|

RU2766429C1 |

| ЦИФРОВОЙ ИЗМЕРИТЕЛЬ СДВИГА ФАЗ ГАРМОНИЧЕСКИХ СИГНАЛОВ | 2020 |

|

RU2751020C1 |

| ЦИФРОВОЙ ДЕМОДУЛЯТОР ДВОИЧНЫХ СИГНАЛОВ С ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ МАНИПУЛЯЦИЕЙ ВТОРОГО ПОРЯДКА | 2018 |

|

RU2690959C1 |

| НЕКОГЕРЕНТНЫЙ ЦИФРОВОЙ ДЕМОДУЛЯТОР "В ЦЕЛОМ" КОДИРОВАННЫХ СИГНАЛОВ С ФАЗОВОЙ МАНИПУЛЯЦИЕЙ | 2014 |

|

RU2556429C1 |

| ЦИФРОВОЙ ДЕМОДУЛЯТОР СИГНАЛОВ С МНОГОПОЗИЦИОННОЙ ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ МАНИПУЛЯЦИЕЙ | 2021 |

|

RU2776968C1 |

| Цифровой демодулятор сигналов с квадратурной амплитудной манипуляцией | 2015 |

|

RU2628427C2 |

Изобретение относится к областям радиотехники. Технический результат направлен на повышение точности цифрового интегрирования сигнала по выборке отсчетов заданного объема. Цифровой интегратор, содержащий аналого-цифровой преобразователь (АЦП), вход которого является входом интегратора, генератор тактовых импульсов (ГТИ) и регистр результата (РР), при этом цифровой интегратор дополнительно содержит многоразрядный регистр сдвига на пять отсчетов (МР5), вход которого соединен с выходом АЦП, первый сумматор, входы которого подключены ко второму и четвертому выходам МР5, и второй сумматор, входы которого подключены к третьему и пятому выходам МР5, первый и второй идентичные каналы накопления отсчетов (КНО), каждый из которых содержит m каскадно соединённых блоков накопления отсчетов (БНО), при этом каждый k-й блок накопления отсчетов (БНО-k) состоит из многоразрядного регистра сдвига (МР-k) на

Цифровой интегратор, содержащий аналого-цифровой преобразователь (АЦП), вход которого является входом интегратора, генератор тактовых импульсов (ГТИ) и регистр результата (РР), отличающийся тем, что он дополнительно содержит многоразрядный регистр сдвига на пять отсчетов (МР5), вход которого соединен с выходом АЦП, первый сумматор, входы которого подключены ко второму и четвертому выходам МР5, и второй сумматор, входы которого подключены к третьему и пятому выходам МР5, первый и второй идентичные каналы накопления отсчетов (КНО), каждый из которых содержит m каскадно соединённых блоков накопления отсчетов (БНО), при этом каждый k-й блок накопления отсчетов (БНО-k) состоит из многоразрядного регистра сдвига (МР-k) на

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ | 2007 |

|

RU2344541C1 |

| US 7917560 B2, 29.03.2011 | |||

| US 4701871, 20.10.1987 | |||

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ | 1991 |

|

RU2030092C1 |

Авторы

Даты

2020-01-14—Публикация

2019-09-23—Подача