Изобретение относится к области радиотехники и микроэлектроники и может быть использовано в аналоговых микросхемах (АМ) и аналого-цифровых интерфейсах датчиков, работающих в тяжелых условиях эксплуатации (низкие температуры, проникающая радиация).

Одним из базовых функциональных узлов современных аналоговых микросхем является источник опорного тока (ИОТ), который обеспечивает стабилизацию статического режима транзисторов.

Современные ИОТ, в зависимости от применяемого технологического процесса, выполняются как на полевых [1-8], так и на биполярных [9-18] транзисторах. При этом достаточно перспективным для тяжелых условий эксплуатации является ИОТ на полевых транзисторах с управляющим p-n переходом (JFet). В работах [19-29] показано, что на основе JFet возможно построение аналоговых микросхем, работающих в диапазоне криогенных температур и воздействии потока нейтронов. Предлагаемое устройство относится к данному классу микроэлектронных изделий. На его основе возможно построение низкотемпературных АМ с экстремально малым уровнем шумов ( при частоте 1 кГц).

при частоте 1 кГц).

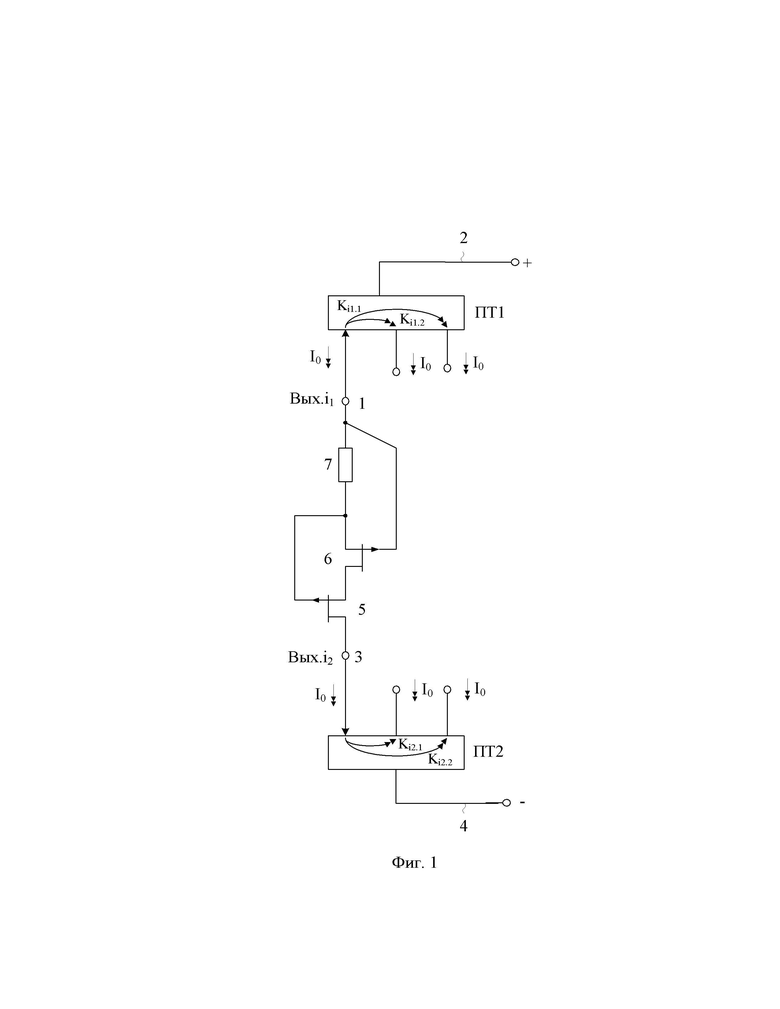

Ближайшим прототипом (фиг. 1) заявляемого устройства является ИОТ по патенту фирмы Analog Device (US 4.639.683, 1987 г.). Он содержит (фиг. 1) первый 1 токовый выход устройства, согласованный с первой 2 шиной источника питания, второй 3 токовый выход устройства, согласованный со второй 4 шиной источника питания, первый 5 выходной транзистор, сток которого подключен ко второму 3 токовому выходу устройства, исток соединен со стоком первого 6 вспомогательного транзистора, а затвор связан с истоком первого 6 вспомогательного транзистора, вспомогательный резистор 7.

Существенный недостаток известного ИОТ состоит в том, что он не обеспечивает высокую стабильность выходных токов в диапазоне криогенных температур, а также не позволяет управлять допустимым диапазоном изменения напряжений на первом 1 и втором 3 токовых выходах. В данной схеме ИОТ потенциал первого 1 входа должен быть зафиксирован (привязан) ко второй 2 шине источника питания. Это недостаток оказывает существенное влияние на области использования известного ИОТ, так как первый 1 и второй 3 токовые выходы обладают существенно разными свойствами – напряжение на втором 3 токовом выходе может изменяться, а напряжение на первом 1 токовом выходе должно быть зафиксировано (привязано) к первой 2 шине источника питания. В ином случае ИОТ фиг.1 неработоспособен.

Первая задача предполагаемого изобретения состоит в повышении стабильности выходного тока ИОТ в широком диапазоне температур, в том числе криогенных. Вторая задача – это создание условий, которые позволяют управлять численными значениями допустимого диапазона изменений напряжений на первом 1 и втором 3 токовых выходах. Третья задача - обеспечение одинаковых свойств первого 1 и второго 3 токовых выходов, при которых напряжения на этих выходах могут существенно и независимо друг от друга изменяться. Это позволяет подключать к предлагаемому ИОТ две разные нагрузки - первая из них может быть связана с первым 1 высокоомным токовым выходом, а вторая - со вторым 3 высокоомным токовым выходом.

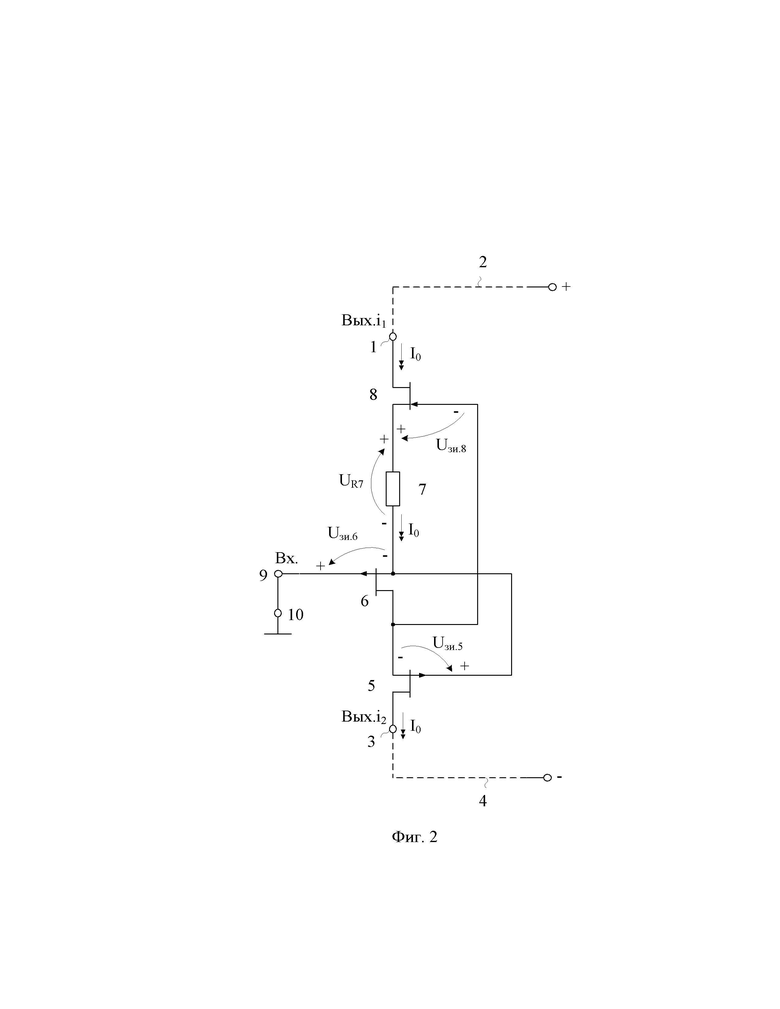

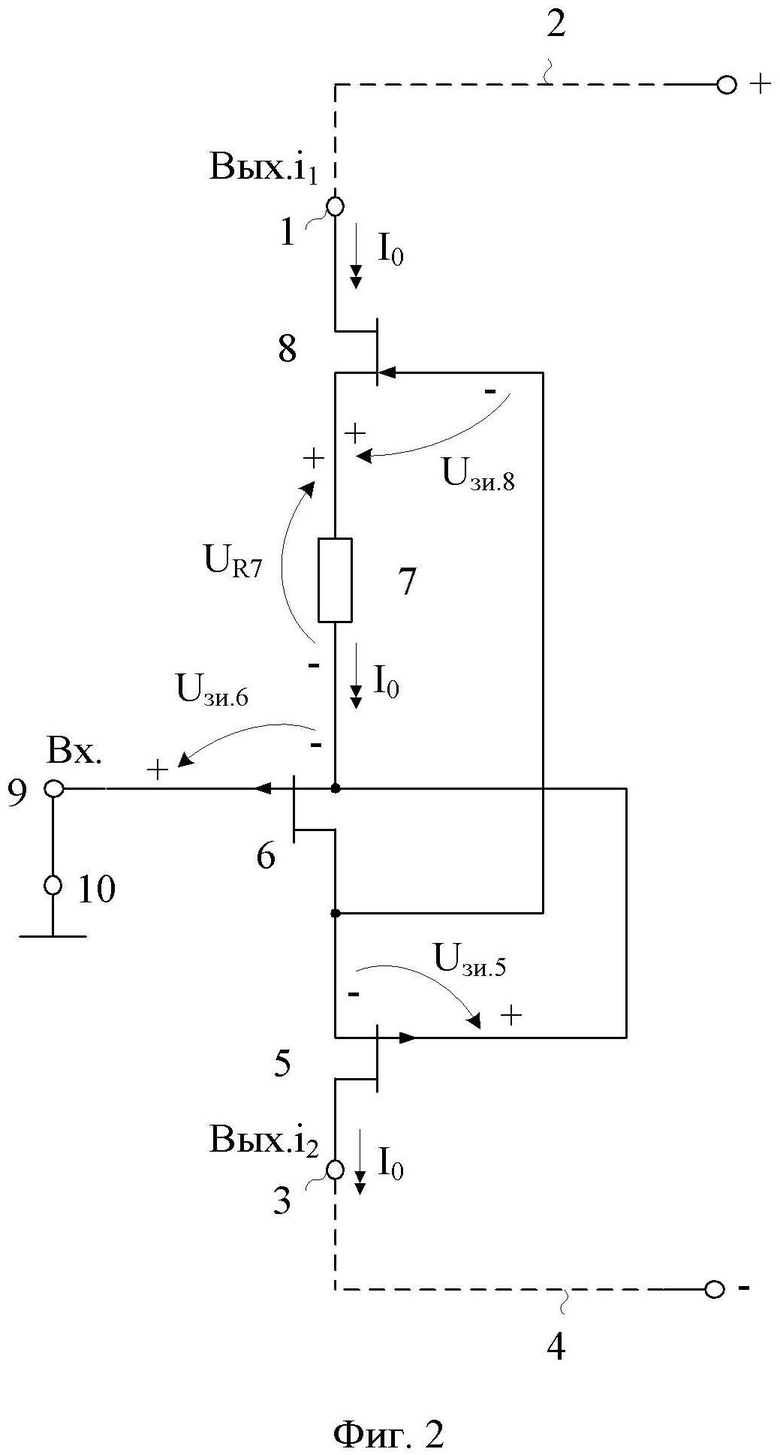

Решение поставленных задач достигается тем, что в ИОТ фиг.1, содержащем первый 1 токовый выход устройства, согласованный с первой 2 шиной источника питания, второй 3 токовый выход устройства, согласованный со второй 4 шиной источника питания, первый 5 выходной транзистор, сток которого подключен ко второму 3 токовому выходу устройства, исток соединен со стоком первого 6 вспомогательного транзистора, а затвор соединен с истоком первого 6 вспомогательного транзистора, вспомогательный резистор 7, предусмотрены новые элементы и связи - в схему введен второй 8 вспомогательный полевой транзистор, сток которого связан с первым 1 токовым выходом устройства, затвор подключен к истоку первого 5 выходного транзистора, а исток связан с истоком первого 6 вспомогательного транзистора через вспомогательный резистор 7, причем затвор первого 6 вспомогательного транзистора подключен к управляющему входу 9 устройства.

На фиг. 1 показана схема ИОТ-прототипа. На фиг. 2 представлена схема заявляемого устройства в соответствии с п. 1 и п. 2 формулы изобретения.

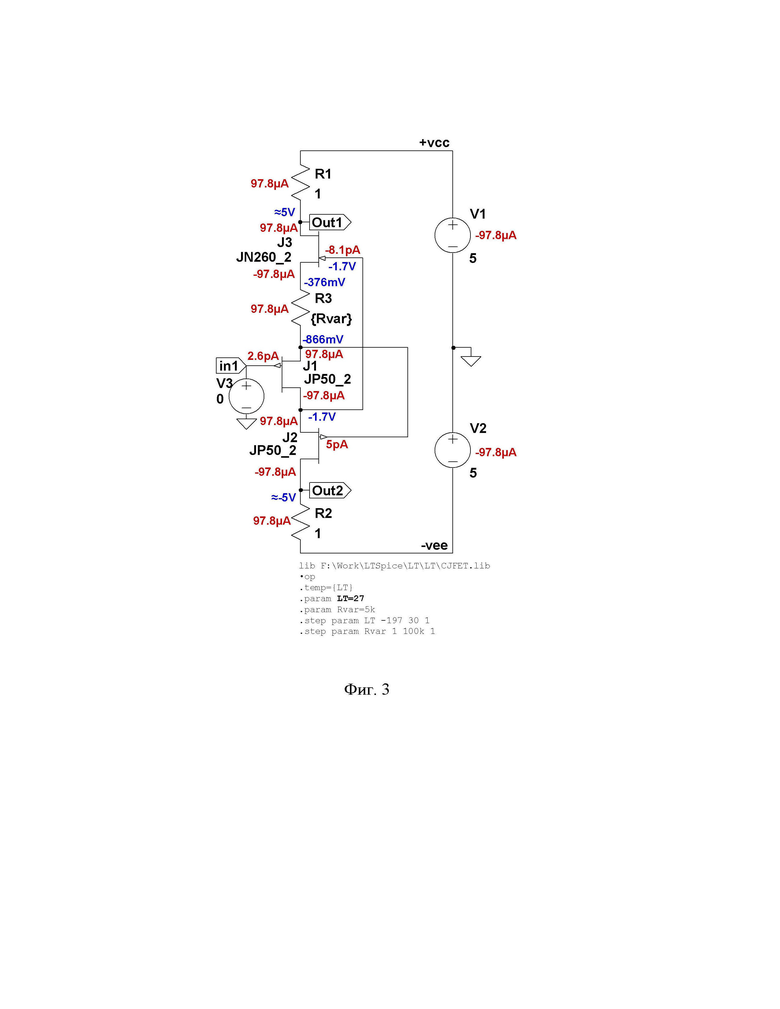

На фиг. 3 представлен статический режим ИОТ фиг. 2 в среде LTspice XVII на моделях JFET транзисторов АО «Интеграл» (г. Минск, Беларусь) при температуре 27°С и сопротивлении R3=5 кОм.

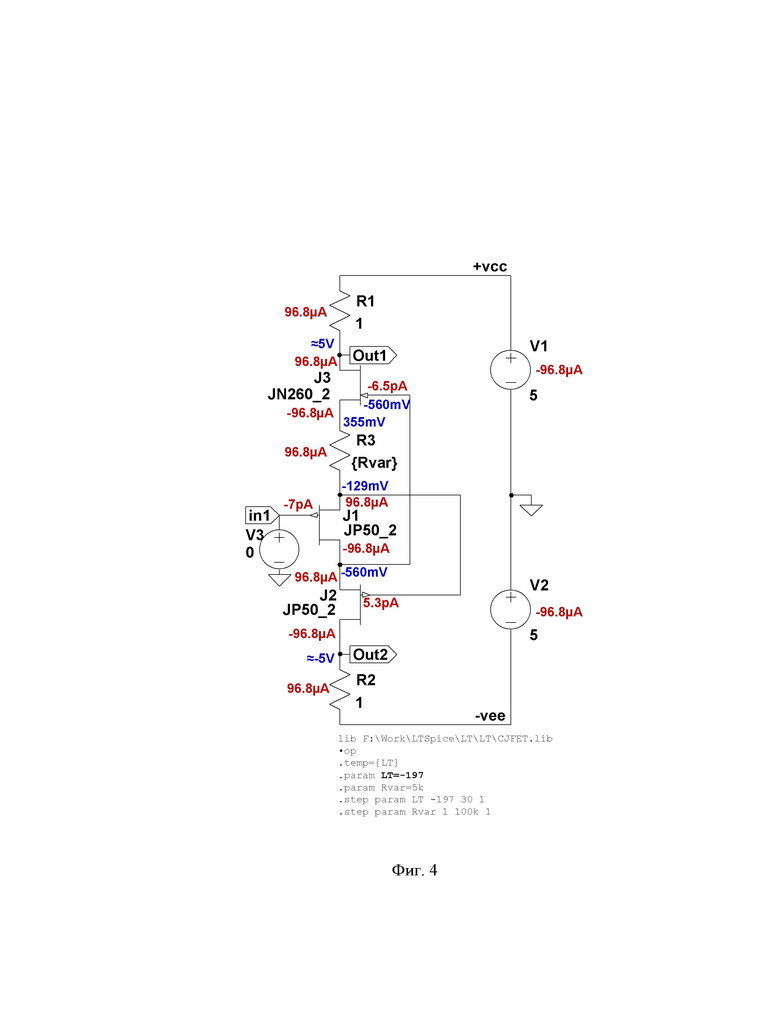

На фиг. 4 приведен статический режим ИОТ фиг. 2 в среде LTspice XVII на моделях JFET транзисторов АО «Интеграл» (г. Минск, Беларусь) при температуре -197°С и сопротивлении R3=5 кОм.

Источник опорного тока фиг. 2 содержит первый 1 токовый выход устройства, согласованный с первой 2 шиной источника питания, второй 3 токовый выход устройства, согласованный со второй 4 шиной источника питания, первый 5 выходной транзистор, сток которого подключен ко второму 3 токовому выходу устройства, исток соединен со стоком первого 6 вспомогательного транзистора, а затвор соединен с истоком первого 6 вспомогательного транзистора, вспомогательный резистор 7. В схему введен второй 8 вспомогательный полевой транзистор, сток которого связан с первым 1 токовым выходом устройства, затвор подключен к истоку первого 5 выходного транзистора, а исток связан с истоком первого 6 вспомогательного транзистора через вспомогательный резистор 7, причем затвор первого 6 вспомогательного транзистора подключен к управляющему входу 9 устройства.

На фиг. 2, в соответствии с п. 2 формулы изобретения, управляющий вход 9 устройства связан с общей шиной 10 первого 2 и второго 4 источников питания.

Эффективность предлагаемого ИОТ (фиг. 2) подтверждают результаты компьютерного моделирования его схемы, представленные на чертежах фиг. 3 (для комнатной температуры) и фиг. 4 (для температуры -197°С). Их анализ показывает, что при t=27°C выходные токи ИОТ по первому 1 и второму 3 токовым выходам идентичны и равны, например, 97,8 мкА. Заданные численные значения Iвых. устанавливаются сопротивлением резистора R3. При изменении температуры окружающей среды до 197°C выходной ток ИОТ (фиг. 4) уменьшается на 1 мкА и принимает значение 96,8 мкА. Таким образом, относительная погрешность выходных токов заявляемого ИОТ по первому 1 и второму 3 токовым выходам имеет значение около 1%, что достаточно для многих низкотемпературных применений.

Изменение опорного напряжения U9 на управляющем входе 9 в ИОТ фиг. 2 позволяет управлять допустимым диапазоном изменения напряжений на первом 1 и втором 3 токовых выходах, при котором ИОТ работает в линейном режиме (с высоким выходным сопротивлением). Если выбрать положительное значение U9 относительно общей шины, то допустимый диапазон напряжений на первом 1 токовом выходе уменьшится, а на втором 3 токовом выходе - увеличится. Во многих случаях управляющий вход 9 может быть связан с общей шиной первого 2 и второго 4 источников питания.

Таким образом, заявляемое устройство имеет существенные преимущества в сравнении с ИОТ-прототипом и может быть рекомендовано для применения в низкотемпературных малошумящих аналоговых микросхемах для обработки сигналов датчиков, в том числе работающих при воздействии проникающей радиации.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент US 7.869.285, fig. 1, 2011 г.

2. Патент WO 2004/042782, fig. 1, 2004 г.

3. Заявка на патент US 2010/0295528, fig. 4, 1986 г.

4. Патент US 7.612.606, 2009 г.

5. Патент US 7.902.912, 2011 г.

6. Патент US 6.323.725, fig. 1, 2001 г.

7. Патент US 6.737.849, 2004 г.

8. Патент US 5.684.394, 1997 г.

9. Патент US 4.563.632, 1986 г.

10. Патент DE 3238880, fig. 1, 1983 г.

11. Патент US 6.556.082, fig. 1, fig. 2, fig. 3, fig. 5, 2003 г.

12. Патент US 4.507.573, fig. 3, 1985 г.

13. Патент US 4.308.496, 1981 г.

14. Патент US 5.440.277, 1995 г.

15. Патент US 4.574.233, 1986 г.

16. Патент US 4.837.496, 1989 г.

17. Патент EP 0107028, 1984 г.

18. Патент US 7.075.358, 2006 г.

19. Дворников О.В., Прокопенко Н.Н., Пахомов И.В., Игнашин А.А., and Бугакова А.В. "Прецизионный радиационно-стойкий BiJFet операционный усилитель для низкотемпературных аналоговых интерфейсов датчиков" Глобальная ядерная безопасность, № 1 (22), 2017, С. 36-45.

20. O. V. Dvornikov, N. N. Prokopenko, A. V. Bugakova, V. A. Tchekhovski and I. V. Maliy, "Cryogenic Operational Amplifier on Complementary JFETs," 2018 IEEE East-West Design & Test Symposium (EWDTS), Kazan, 2018, pp. 1-5. doi: 10.1109/EWDTS.2018.8524640.

21. K. O. Petrosyants, M. R. Ismail-zade, L. M. Sambursky, O. V. Dvornikov, B. G. Lvov and I. A. Kharitonov, "Automation of parameter extraction procedure for Si JFET SPICE model in the −200…+110°C temperature range," 2018 Moscow Workshop on Electronic and Networking Technologies (MWENT), Moscow, 2018, pp. 1-5. doi: 10.1109/MWENT.2018.8337212M.

22. O. V. Dvornikov, N. N. Prokopenko, I. V. Pakhomov and A. V. Bugakova, "The analog array chip AC-1.3 for the tasks of tool engineering in conditions of cryogenic temperature, neutron flux and cumulative radiation dose effects," 2016 IEEE East-West Design & Test Symposium (EWDTS), Yerevan, 2016, pp. 1-4. doi: 10.1109/EWDTS.2016.7807724.

23. Citterio, S. Rescia and V. Radeka, "Radiation effects at cryogenic temperatures in Si-JFET, GaAs MESFET, and MOSFET devices," in IEEE Transactions on Nuclear Science, vol. 42, no. 6, pp. 2266-2270, Dec. 1995. doi: 10.1109/23.489425.

24. M. Citterio, S. Rescia and V. Radeka, "A study of low noise JFETs exposed to large doses of gamma-rays and neutrons," IEEE Conference on Nuclear Science Symposium and Medical Imaging, Orlando, FL, USA, 1992, pp. 794-796 vol.2. doi: 10.1109/NSSMIC.1992.301428.

25. W. Buttler, B. J. Hosticka, G. Lutz and P. F. Manfredi, "A JFET-CMOS radiation-tolerant charge-sensitive preamplifier," in IEEE Journal of Solid-State Circuits, vol. 25, no. 4, pp. 1022-1024, Aug. 1990. doi: 10.1109/4.58299.

26. A. Pullia, F. Zocca, S. Riboldi, D. Budjas, A. D'Andragora and C. Cattadori, "Cryogenic Performance of a Low-Noise JFET-CMOS Preamplifier for HPGe Detectors," in IEEE Transactions on Nuclear Science, vol. 57, no. 2, pp. 737-742, April 2010. doi: 10.1109/TNS.2009.2038697.

27. T. S. Jung, H. Guckel, J. Seefeldt, G. Ott and Y. C. Ahn, "A fully integrated, monolithic, cryogenic charge sensitive preamplifier using N-channel JFETs and polysilicon resistors," in IEEE Transactions on Nuclear Science, vol. 41, no. 4, pp. 1240-1245, Aug. 1994. doi: 10.1109/23.322892.

28. A. D'Andragora et al., "Spectroscopic performances of the GERDA cryogenic Charge Sensitive Amplifier based on JFET-CMOS ASIC, coupled to germanium detectors," 2009 IEEE Nuclear Science Symposium Conference Record (NSS/MIC), Orlando, FL, 2009, pp. 396-400. doi: 10.1109/NSSMIC.2009.5401678.

29. D. M. Long, "Transient radiation response of jfets and misfets at cryogenic temperatures," in IEEE Transactions on Nuclear Science, vol. 21, no. 6, pp. 119-123, Dec. 1974. doi: 10.1109/TNS.1974.6498915.

Изобретение относится к области радиотехники и микроэлектроники и может быть использовано в аналоговых микросхемах и аналого-цифровых интерфейсах датчиков, работающих в тяжелых условиях эксплуатации (низкие температуры, проникающая радиация). Технический результат: повышение стабильности выходного тока устройства, в том числе при криогенных температурах; создание условий, которые позволяют управлять численными значениями допустимого диапазона изменений напряжений на первом и втором токовых выходах; обеспечение одинаковых свойств первого и второго токовых выходов, при которых напряжения на этих выходах могут изменяться независимо друг от друга. Источник опорного тока для задач стабилизации статического режима операционных усилителей при низких температурах, содержащий первый (1) токовый выход устройства, согласованный с первой (2) шиной источника питания, второй (3) токовый выход устройства, согласованный со второй (4) шиной источника питания, первый (5) выходной транзистор, сток которого подключен ко второму (3) токовому выходу устройства, исток соединен со стоком первого (6) вспомогательного транзистора, а затвор соединен с истоком первого (6) вспомогательного транзистора, вспомогательный резистор (7). В схему введен второй (8) вспомогательный полевой транзистор, сток которого связан с первым (1) токовым выходом устройства, затвор подключен к истоку первого (5) выходного транзистора, а исток связан с истоком первого (6) вспомогательного транзистора через вспомогательный резистор (7), причем затвор первого (6) вспомогательного транзистора подключен к управляющему входу (9) устройства. Управляющий вход (9) устройства связан с общей шиной (10) первого (2) и второго (4) источников питания. 1 з.п. ф-лы, 4 ил.

1. Источник опорного тока для задач стабилизации статического режима операционных усилителей при низких температурах, содержащий первый (1) токовый выход устройства, согласованный с первой (2) шиной источника питания, второй (3) токовый выход устройства, согласованный со второй (4) шиной источника питания, первый (5) выходной транзистор, сток которого подключен ко второму (3) токовому выходу устройства, исток соединен со стоком первого (6) вспомогательного транзистора, а затвор соединен с истоком первого (6) вспомогательного транзистора, вспомогательный резистор (7), отличающийся тем, что в схему введен второй (8) вспомогательный полевой транзистор, сток которого связан с первым (1) токовым выходом устройства, затвор подключен к истоку первого (5) выходного транзистора, а исток связан с истоком первого (6) вспомогательного транзистора через вспомогательный резистор (7), причем затвор первого (6) вспомогательного транзистора подключен к управляющему входу (9) устройства.

2. Источник опорного тока для задач стабилизации статического режима операционных усилителей при низких температурах по п. 1, отличающийся тем, что управляющий вход (9) устройства связан с общей шиной (10) первого (2) и второго (4) источников питания.

| US 4639683 A1, 27.01.1987 | |||

| Источник опорного напряжения | 1990 |

|

SU1793434A1 |

| Стабилизатор постоянного напряжения | 1985 |

|

SU1275404A1 |

Авторы

Даты

2020-01-16—Публикация

2019-10-11—Подача