Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения, например, операционных усилителях (ОУ), компараторах, мостовых усилителях мощности и т.п., в т.ч. работающих при низких температурах и воздействии радиации [1].

Известны схемы классических дифференциальных каскадов на комплементарных транзисторах [2-28], в т.ч. на комплементарных КМОП полевых транзисторах [3-28] и комплементарных полевых транзисторах с управляющим p-n переходом (JFet) [2], которые стали основой многих серийных аналоговых микросхем. В литературе по аналоговой микроэлектронике этот класс ДК имеет специальное обозначение – dual-input-stage [29].

Для работы при низких температурах и жестких ограничениях на уровень шумов перспективно использование JFet полевых транзисторов [30-32]. ДК данного класса активно применяются в структуре малошумящих аналоговых интерфейсов для обработки сигналов датчиков [33-35].

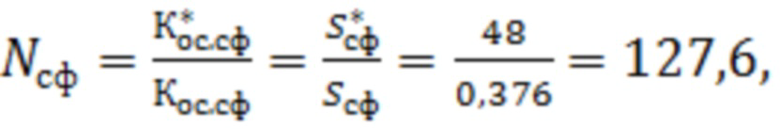

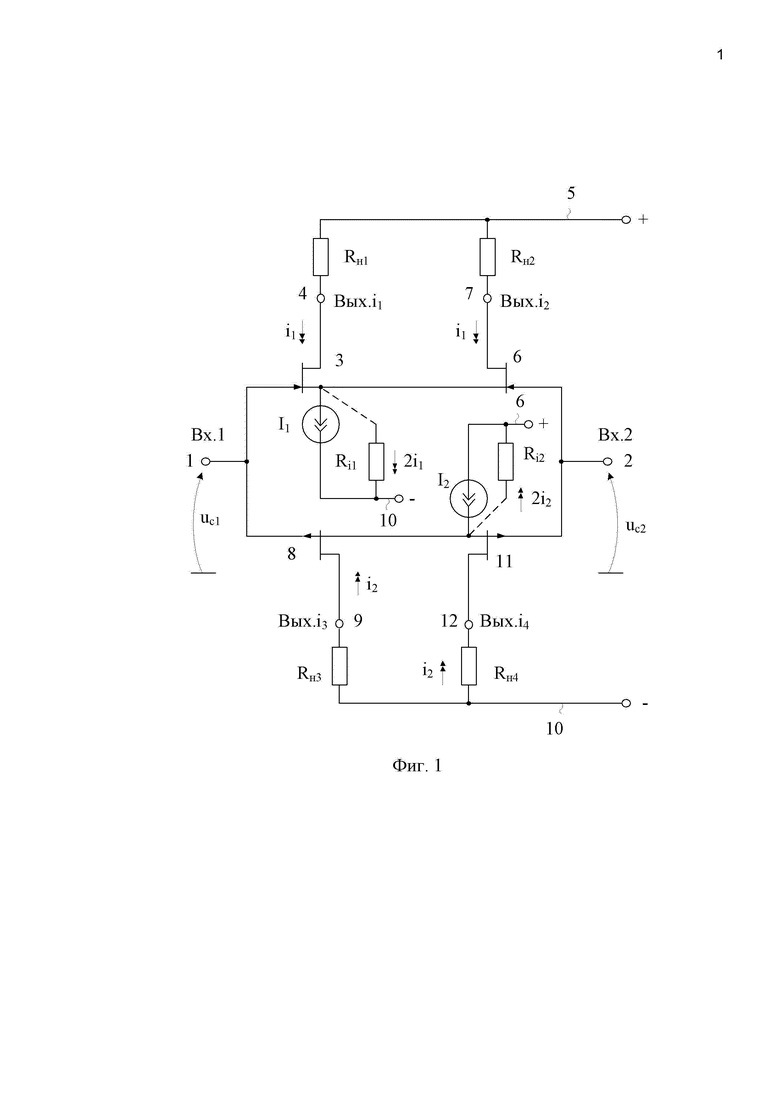

Ближайшим прототипом (фиг. 1) заявляемого устройства является дифференциальный каскад, описанный в патенте US 5.291.149, fig.4, 1994г., который содержит первый 1 и второй 2 входы устройства, первый 3 входной полевой транзистор, затвор которого соединен с первым 1 входом устройства, сток соединен с первым 4 токовым выходом устройства, согласованным с первой 5 шиной источника питания, второй 6 входной полевой транзистор, затвор которого соединен со вторым 2 входом устройства, а сток соединен со вторым 7 токовым выходом устройства, согласованным с первой 5 шиной источника питания, причем истоки первого 3 и второго 6 входных полевых транзисторов связаны друг с другом, третий 8 входной полевой транзистор, затвор которого соединен с первым 1 входом устройства, сток соединен с третьим 9 токовым выходом устройства, согласованным со второй 10 шиной источника питания, четвертый 11 входной полевой транзистор, затвор которого соединен со вторым 2 входом устройства, а сток соединен с четвертым 12 токовым выходом устройства, согласованным со второй 10 шиной источника питания, причем истоки третьего 8 и четвертого 11 входных полевых транзисторов связаны друг с другом.

Существенный недостаток известного ДК фиг. 1 состоит в том, что статический режим его входных полевых транзисторов (ПТ) определяется двумя независимыми источниками опорного тока I1 (I2), которые, как правило, неидентичны из-за разных напряжений отсечки ПТ c p- и n-каналами. Это становится источником дополнительных погрешностей при усилении сигналов, ухудшает коэффициент ослабления входных синфазных сигналов ДК (Кос.сф), а также коэффициент подавления помех по шинам питания (Кпп). В прецизионных устройствах требования к этим параметрам иногда доминируют.

Основная задача предполагаемого изобретения состоит в создании условий, при которых в ДК фиг. 1 обеспечиваются более высокие значения Кос.сф и Кпп, в т.ч. при отрицательных температурах (до -197̊С).

Поставленная задача решается тем, что в дифференциальном каскаде фиг. 1, содержащем первый 1 и второй 2 входы устройства, первый 3 входной полевой транзистор, затвор которого соединен с первым 1 входом устройства, сток соединен с первым 4 токовым выходом устройства, согласованным с первой 5 шиной источника питания, второй 6 входной полевой транзистор, затвор которого соединен со вторым 2 входом устройства, а сток соединен со вторым 7 токовым выходом устройства, согласованным с первой 5 шиной источника питания, причем истоки первого 3 и второго 6 входных полевых транзисторов связаны друг с другом, третий 8 входной полевой транзистор, затвор которого соединен с первым 1 входом устройства, сток соединен с третьим 9 токовым выходом устройства, согласованным со второй 10 шиной источника питания, четвертый 11 входной полевой транзистор, затвор которого соединен со вторым 2 входом устройства, а сток соединен с четвертым 12 токовым выходом устройства, согласованным со второй 10 шиной источника питания, причем истоки третьего 8 и четвертого 11 входных полевых транзисторов связаны друг с другом, предусмотрены новые элементы и связи – в схему введен первый 13 дополнительный полевой транзистор, затвор которого соединен с объединенными истоками первого 3 и второго 6 входных полевых транзисторов, сток подключен к объединенным истокам третьего 8 и четвертого 11 входных полевых транзисторов, а исток связан с объединенными истоками первого 3 и второго 6 входных полевых транзисторов через первый 14 вспомогательный двухполюсник.

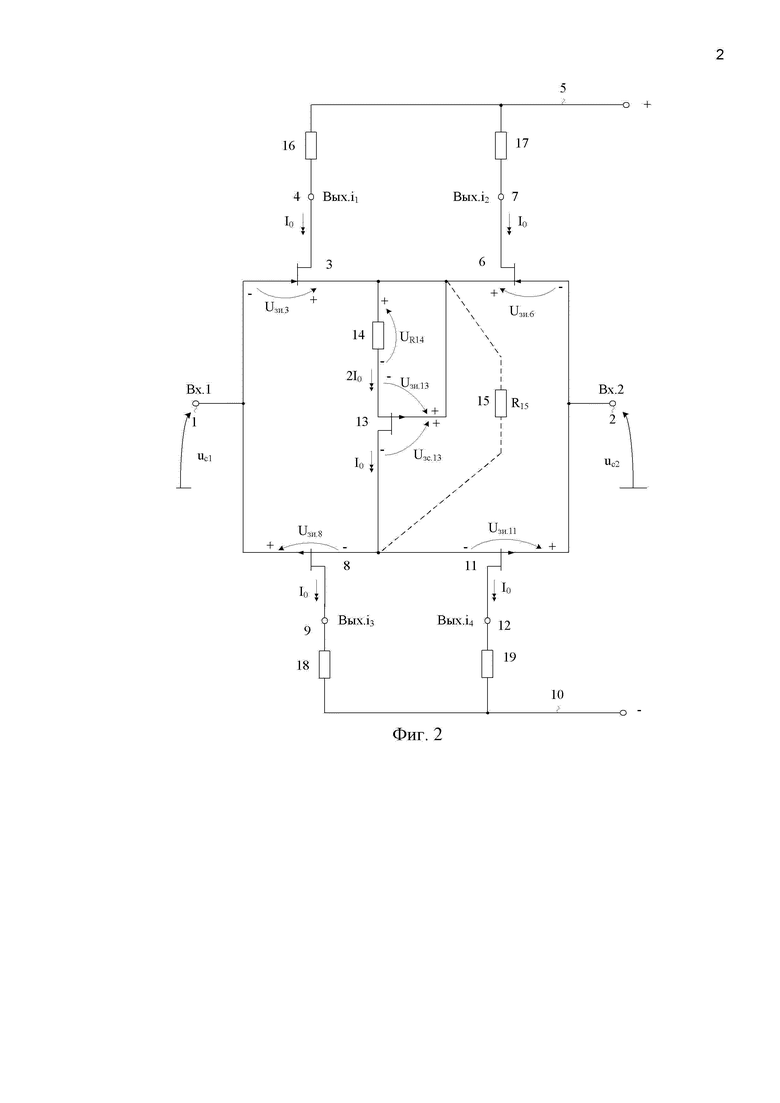

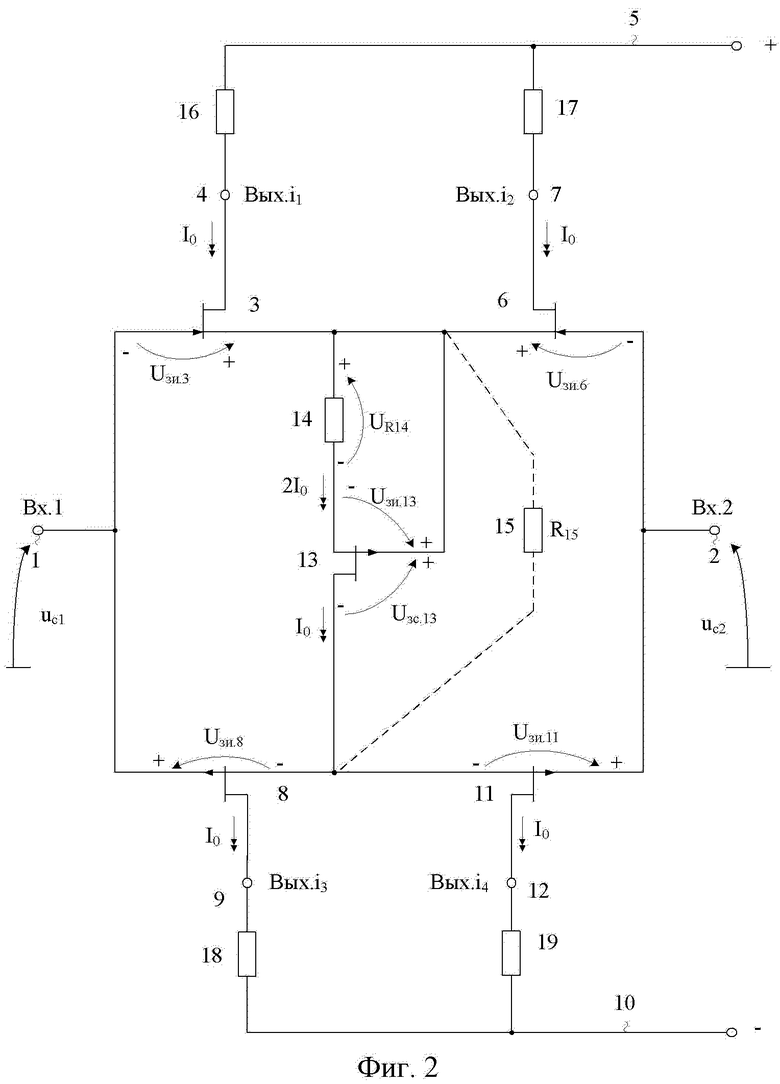

На чертеже фиг. 1 представлена схема ДК-прототипа по патенту US 5.291.149, fig.4, 1994г., а на чертеже фиг. 2 - схема заявляемого дифференциального каскада на комплементарных полевых транзисторах с управляющим p-n переходом в соответствии с п.1 формулы изобретения.

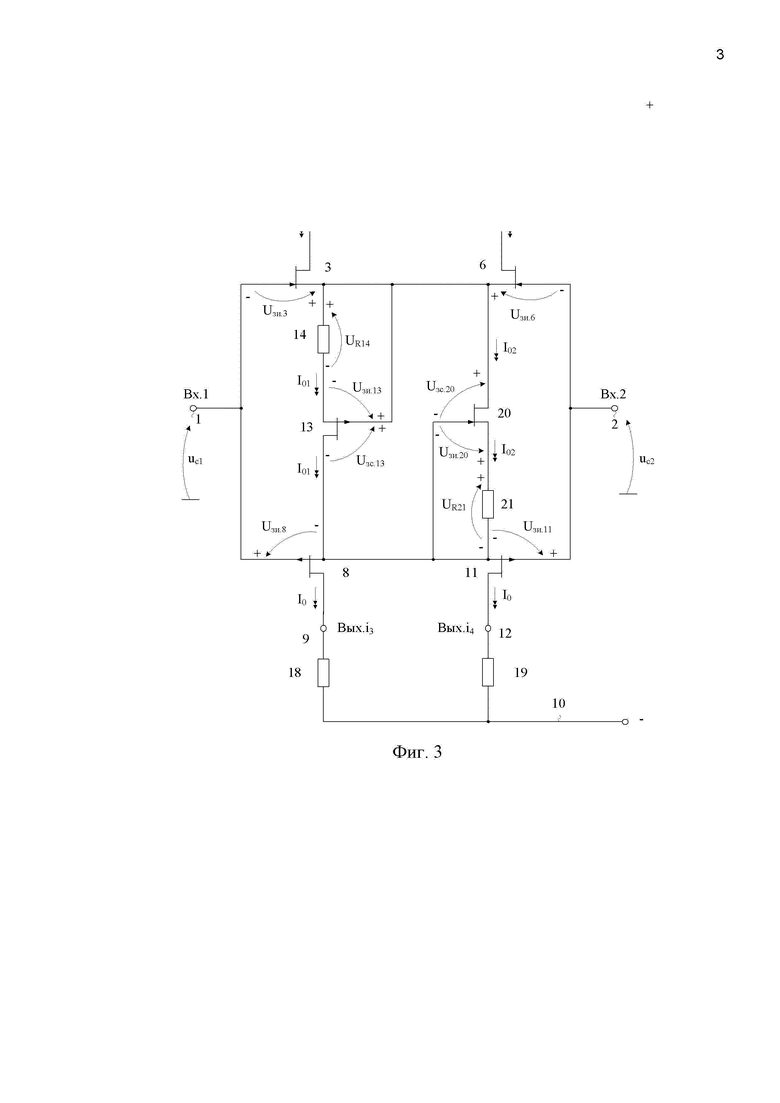

На чертеже фиг. 3 показана схема заявляемого дифференциального каскада в соответствии с п.2 формулы изобретения.

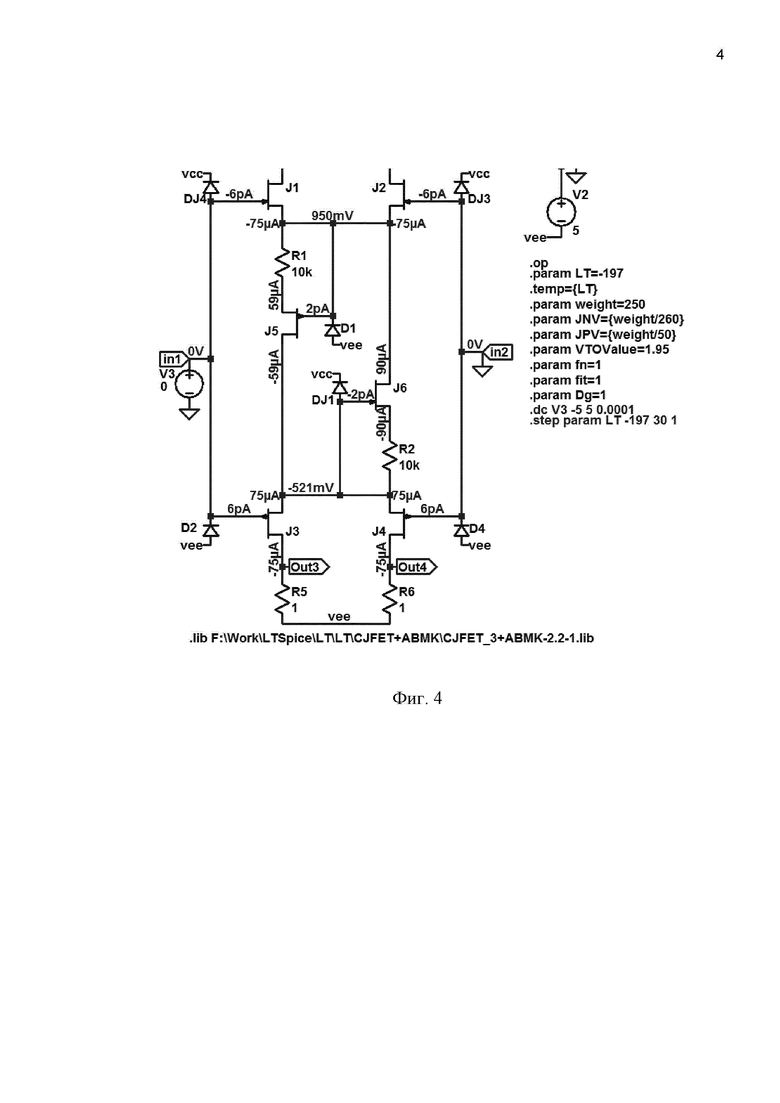

На чертеже фиг. 4 приведен статический режим ДК фиг. 3 при t=-197ᵒC в среде LTSpice на моделях CJFet транзисторов ОАО «Интеграл» (г. Минск).

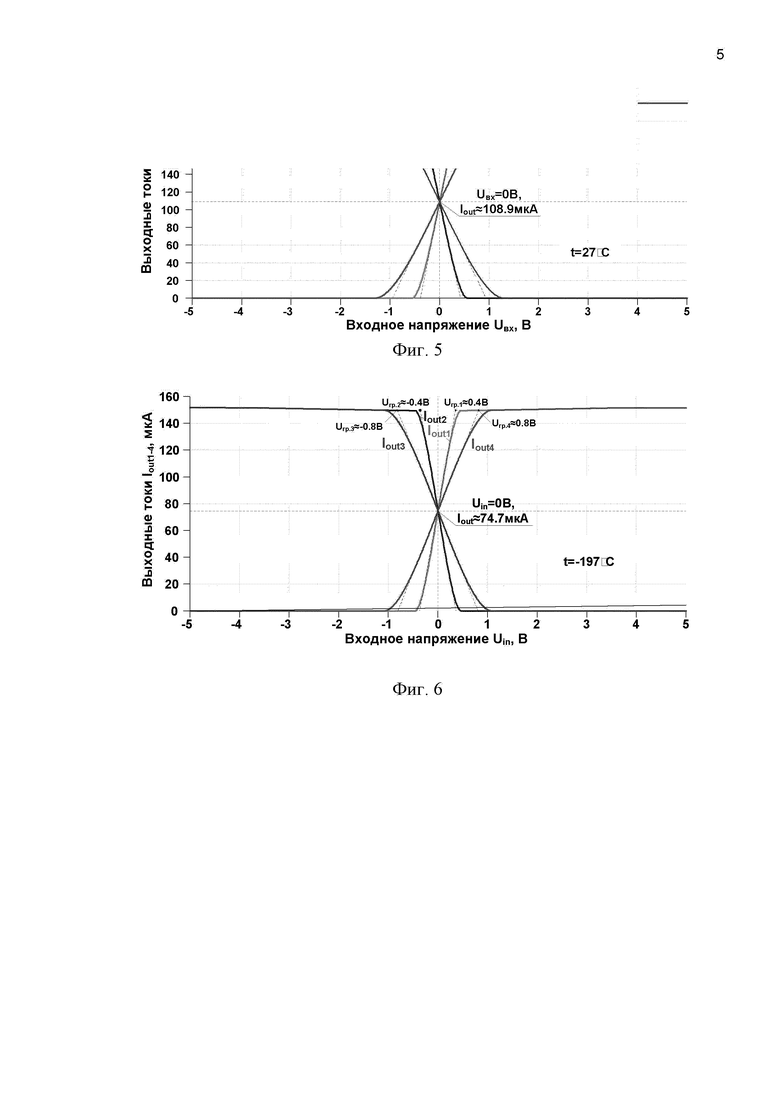

На чертеже фиг. 5 представлены проходные характеристики ДК фиг. 4 при температуре 27ᵒС, сопротивлениях резисторов R1=R2=10 кОм, напряжениях питания V1=V2=±5В для токовых выходов Out.1, Out.2, Out.3, Out.4 при входном напряжении V3=Uвх, изменяющимся в пределах -5÷5В.

На чертеже фиг. 6 показаны проходные характеристики ДК фиг. 4 при температуре -197ᵒС, сопротивлениях резисторов R1=R2=10 кОм, напряжениях питания V1=V2=±5В для токовых выходов Out.1, Out.2, Out.3, Out.4 при входном напряжении V3=Uвх, изменяющимся в пределах -5÷5В.

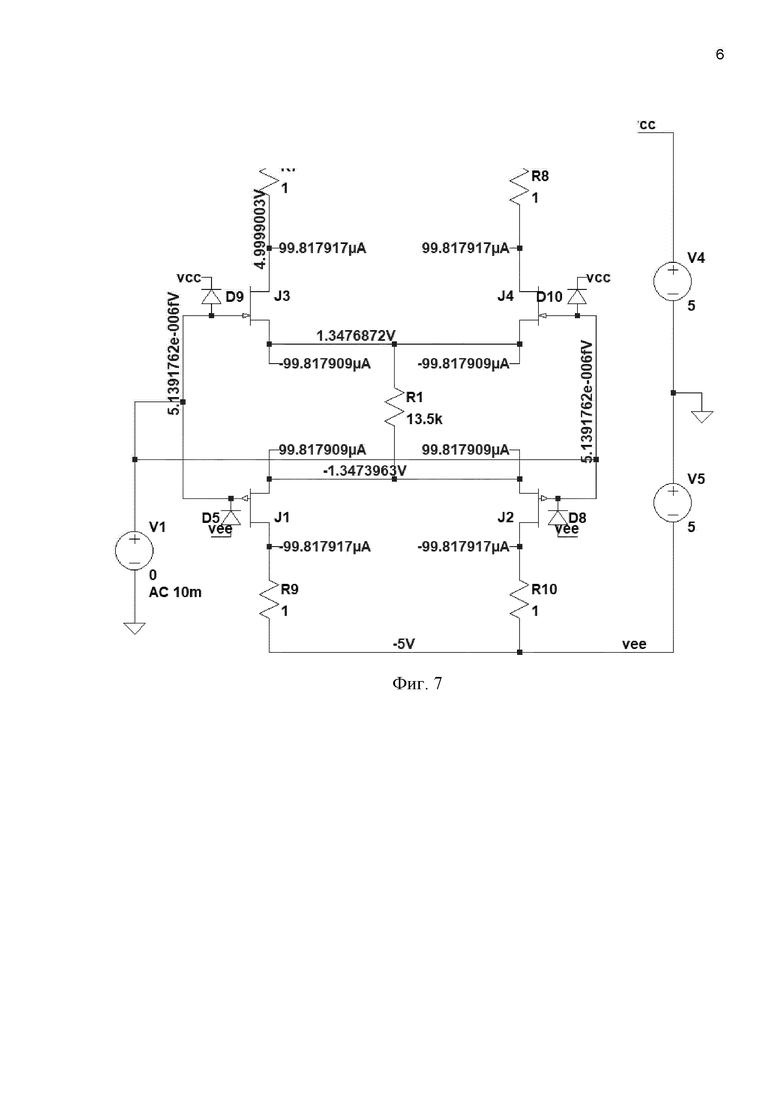

На чертеже фиг. 7 представлен статический режим ДК фиг. 2 в режиме измерения проводимости передачи входного синфазного сигнала uc при эквивалентном сопротивлении резистора R15(R1)=13,5 кОм, обеспечивающего идентичные статические токи стоков входных полевых транзисторов J1-J4 по 100 мкА при температуре 25ᵒС.

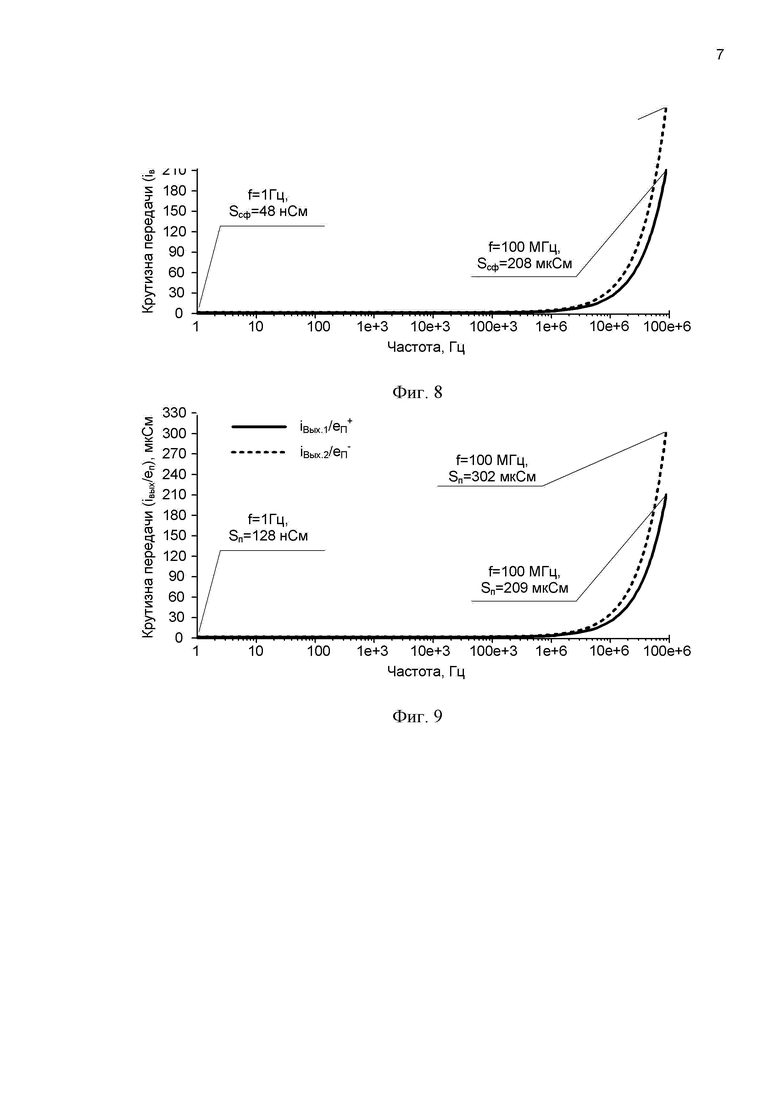

На чертеже фиг. 8 приведена частотная зависимость крутизны передачи входного синфазного сигнала (Sсф) дифференцильного каскада фиг. 7 со входов 1, 2 до первого 4 (Вых.i1) и второго 7 (Вых.i2) токовых выходов.

На чертеже фиг. 9 показана частотная зависимость крутизны передачи помех на шинах питания Sп(+), Sп(-) (синусоидальное напряжение с амплитудой 100 мВ на положительной и отрицательной шинах) в ДК фиг. 7 по первому 4 (Вых.i1) и второму 7 (Вых.i2) токовым выходам.

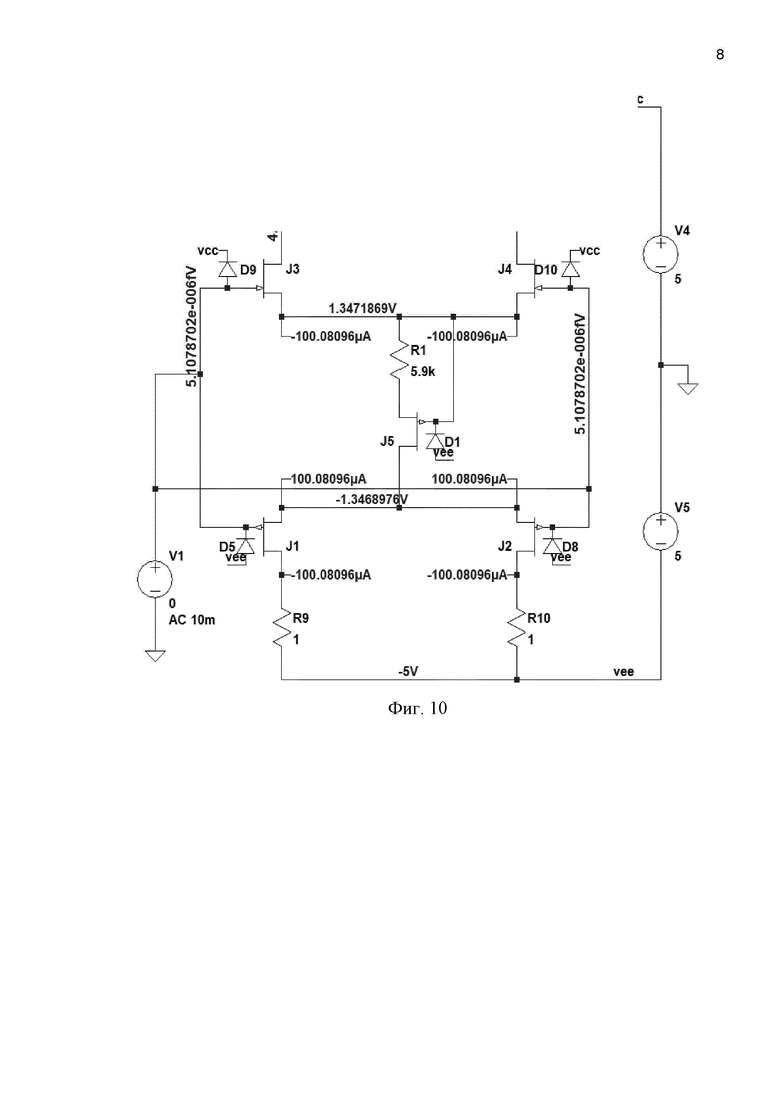

На чертеже фиг. 10 представлены статические токи в заявляемом ДК фиг. 2 в режиме измерения проводимостей передачи входного синфазного сигнала при температуре 25ᵒС.

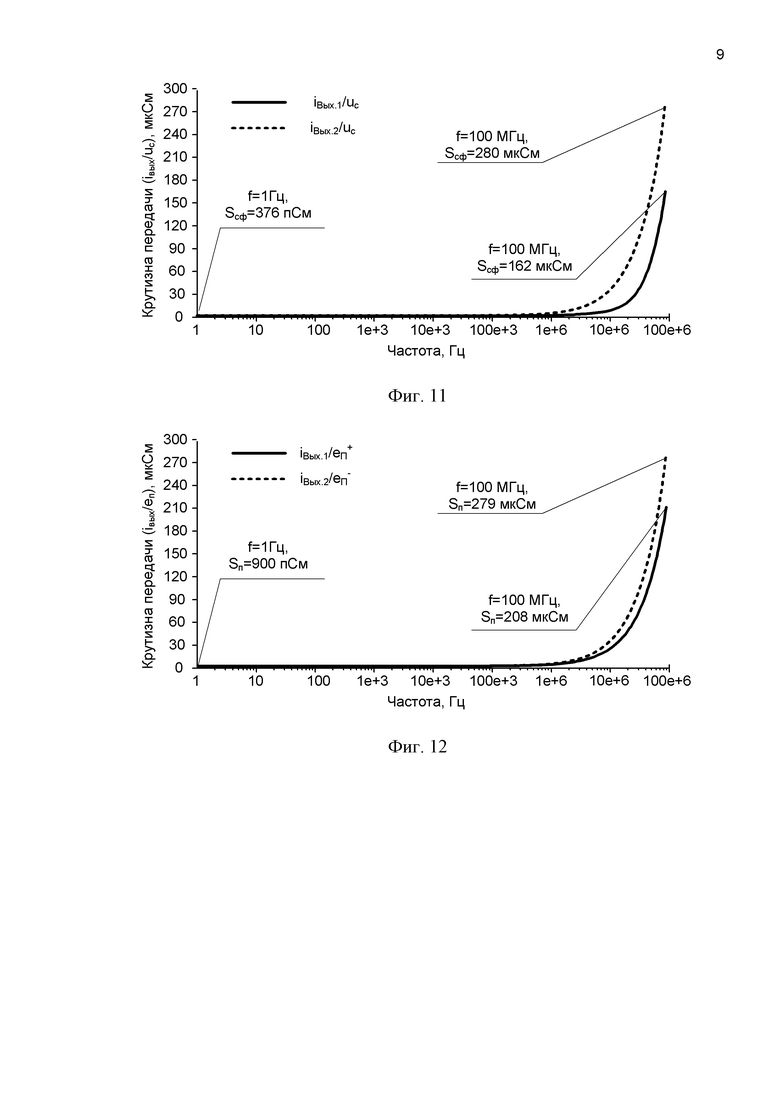

На чертеже фиг. 11 приведена частотная зависимость крутизны передачи Sсф входного синфазного сигнала ДК фиг. 10 для первого 4 (Вых.i1) и второго 7 (Вых.i2) токовых выходов при статических токах входных полевых транзисторов по 100 мкА, идентичных токам ПТ в схеме фиг. 7.

На чертеже фиг. 12 показана частотная зависимость крутизны передачи помех по шинам питания Sп(+), Sп(-) с амплитудой 100 мВ в ДК фиг. 10 для первого 4 (Вых.i1) и второго 7 (Вых.i2) токовых выходов.

Дифференциальный каскад на комплементарных JFET полевых транзисторах с повышенным ослаблением входного синфазного сигнала фиг. 2 содержит первый 1 и второй 2 входы устройства, первый 3 входной полевой транзистор, затвор которого соединен с первым 1 входом устройства, сток соединен с первым 4 токовым выходом устройства, согласованным с первой 5 шиной источника питания, второй 6 входной полевой транзистор, затвор которого соединен со вторым 2 входом устройства, а сток соединен со вторым 7 токовым выходом устройства, согласованным с первой 5 шиной источника питания, причем истоки первого 3 и второго 6 входных полевых транзисторов связаны друг с другом, третий 8 входной полевой транзистор, затвор которого соединен с первым 1 входом устройства, сток соединен с третьим 9 токовым выходом устройства, согласованным со второй 10 шиной источника питания, четвертый 11 входной полевой транзистор, затвор которого соединен со вторым 2 входом устройства, а сток соединен с четвертым 12 токовым выходом устройства, согласованным со второй 10 шиной источника питания, причем истоки третьего 8 и четвертого 11 входных полевых транзисторов связаны друг с другом. В схему введен первый 13 дополнительный полевой транзистор, затвор которого соединен с объединенными истоками первого 3 и второго 6 входных полевых транзисторов, сток подключен к объединенным истокам третьего 8 и четвертого 11 входных полевых транзисторов, а исток связан с объединенными истоками первого 3 и второго 6 входных полевых транзисторов через первый 14 вспомогательный двухполюсник.

Резистор 15 в схеме фиг. 2 соответствует эквивалентному сопротивлению между истоками транзисторов 3 и (6) и 8 (11). Его введение необходимо для оценки эффективности предлагаемого схемотехнического решения по величине реализуемых Кос.сф и Кпп.

Кроме этого, на чертеже фиг. 2 двухполюсники 16, 17, 18 и 19 моделируют свойства нагрузки ДК. В практических аналоговых микросхемах в качестве таких нагрузок используются входы токовых зеркал, обеспечивающих дальнейшее преобразование токовых сигналов по выходам 4, 7, 9, 12.

На чертеже фиг. 3, в соответствии с п. 2 формулы изобретения, в схему введен второй 20 дополнительный полевой транзистор, затвор которого соединен с объединенными истоками третьего 8 и четвертого 11 входных полевых транзисторов, сток подключен к объединенным истокам первого 3 и второго 6 входных полевых транзисторов, а исток связан с объединенными истоками третьего 8 и четвертого 11 входных полевых транзисторов через второй 21 вспомогательный двухполюсник.

Рассмотрим работу ДУ фиг. 2 с учетом результатов сравнительного компьютерного моделирования, представленных на чертежах фиг. 8, фиг. 9, фиг. 11 и фиг. 12.

Компьютерное моделирование проходной характеристики ДК фиг. 4 в среде LTspice при комнатной (фиг. 5) и криогенной (фиг. 8) температурах показывает, что рассматриваемое схемотехнические решение обеспечивает преобразование входного синфазного напряжения ДК uc в токи выходов ДК (Out.1, Out.2, Out.3, Out.4) в диапазоне Vin=±1В. Это достаточно для многих применений.

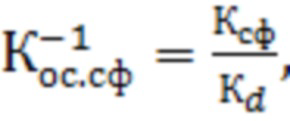

Коэффициент ослабления входного синфазного сигнала ДК фиг.2 для первого 4 выхода (Вых.i1) определяется по формуле

(1)

(1)

где Ксф=R16Sсф – коэффициент преобразования входного синфазного сигнала ДК (uc=uc1=uc2) в напряжение на эквивалентном двухполюснике нагрузки 16;

Scф=iвых.1/uc – проводимость передачи входного синфазного сигнала uc по первому 4 токовому выходу;

Kd=R16(S3+S6) – дифференциальный коэффициент усиления по напряжению от дифференциального входа ДК (входы 1, 2) к первому 4 токовому выходу;

S3≈S6 – крутизна стоко-затворной характеристики первого 3 и второго 6 входных полевых транзисторов.

Из уравнения (1) можно получить

(2)

(2)

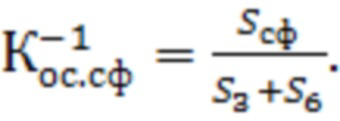

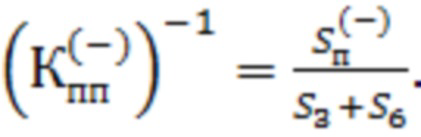

Похожие формулы можно получить и для коэффициентов подавления помех по шинам питания

(3)

(3)

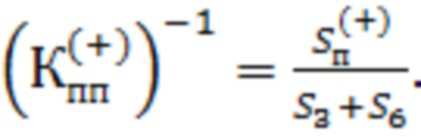

(4)

(4)

Таким образом, для повышения помехоустойчивости ДК необходимо минимизировать схемотехническим путем проводимости передачи по входному синфазному сигналу (Sсф=0) и проводимости передачи помех по шинам питания (Sп(+)=0, Sп(-)=0).

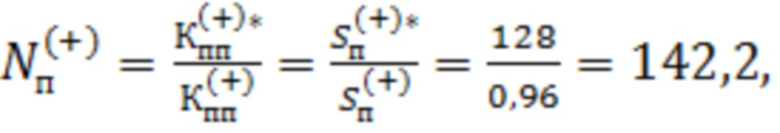

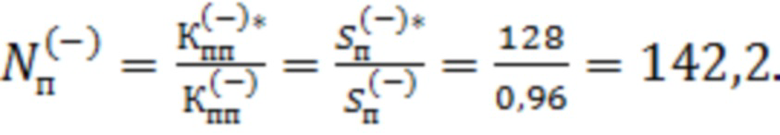

Результаты сравнительного компьютерного моделирования схемы фиг. 2 с дополнительными элементами 13 и 14, которые введены в соответствии с п.1 формулы изобретения, а также без элементов 13 и 14 (только с резистором 15, обеспечивающим идентичный статический режим входных полевых транзисторов ДК по 100 мкА), представлены на чертежах фиг. 8 и фиг. 11. Их анализ показывает, что предлагаемое схемотехническое решение обеспечивает на низких частотах следующие проводимости передачи Sсф=376 пСм и Sп(+)=Sп(-)=900 пСм.

В то же время схема ДК-аналога дает Sсф*=48 нСм, Sп(+)*=Sп(-)*=128 нСм.

Таким образом, в заявляемом устройстве коэффициенты Кос.сф и Кпп улучшаются не менее чем на два порядка:

(5)

(5)

(6)

(6)

(7)

(7)

Следовательно, заявляемое устройство имеет существенные преимущества в сравнении с известными схемотехническими решениями ДК класса dual-input-stage [2-28] по величине коэффициента ослабления входного синфазного сигнала и уровню подавления помех по шинам питания. Это позволяет рекомендовать рассмотренные схемы ДК для практического использования в прецизионных ОУ и построения малошумящих, низкотемпературных и радиационно-стойких аналоговых микросхем по техпроцессу CJFet ОАО «Интеграл» (г. Минск), а также комплементарному биполярно-полевому технологическому процессу АО «НПП «Пульсар» (г. Москва).

Библиографический список

1. Dvornikov O. V., Dziatlau V. L., Prokopenko N. N., Petrosiants K. O., Kozhukhov N. V. and Tchekhovski V. A. The accounting of the simultaneous exposure of the low temperatures and the penetrating radiation at the circuit simulation of the BiJFET analog interfaces of the sensors // 2017 International Siberian Conference on Control and Communications (SIBCON), Astana, 2017, pp. 1-6. DOI: 10.1109/SIBCON.2017.7998507

2. Патент US 5.291.149 fig. 4, 1994 г.

1. Патент US 4.377.789, fig. 1, 1983 г.

2. Патентная заявка US 2006/0125522, 2006 г.

3. Патент US 7.907.011, 2011

4. US 2008/0024217, fig. 1, 2008 г.

5. Патент EP 0318263,1989 г.

6. Патент US 5.907.259, fig. 1, 1999 г.

7. Патент US 7.408.410, 2008 г.

8. Патент US 6.628.168, fig.2, 2003 г.

9. Патентная заявка US 2009/0302895, 2009 г.

10. Патент US 5.714.906, fig. 4, 1998 г.

11. Патент US 2005/0285677, 2005 г.

12. Патент US 5.070.306, fig. 3, 1991 г.

13. Патент US 2010/001797, 2010 г.

14. Патент US 6.972.623, fig. 4, fig. 6, 2005 г.

15. Патент US 2008/0252374, 2008 г.

16. Патент US 7.586.373, 2009 г.

17. Патент US 2006/0215787, 2006 г.

18. Патент US 7.453.319, 2008 г.

19. Патент US 2004/0174216, fig. 2, 2004 г.

20. Патент US 7.215.200, fig. 6, 2007 г.

21. Патент US № 6.433.637, fig. 2, 2002 г.

22. Патент US № 6.392.485, 2002 г.

23. Патент US 5.963.085, fig. 3, 1999 г.

24. Патент US 6.788.143, 2004 г.

25. Патент US 4.390.850, 1983 г.

26. Патент US 6.696.894, fig. 1, 2004 г.

29. Prokopenko N. N., Butyrlagin N. V., Bugakova A. V. and Ignashin A. A. Method for speeding the micropower CMOS operational amplifiers with dual-input-stages // 2017 24th IEEE International Conference on Electronics, Circuits and Systems (ICECS), Batumi, 2017, pp. 78-81.

30. Petrosyants K.O., Ismail-zade M.R., Sambursky L. M., Dvornikov O.V., Lvov B. G. and Kharitonov I. A. Automation of parameter extraction procedure for Si JFET SPICE model in the −200…+110°C temperature range // 2018 Moscow Workshop on Electronic and Networking Technologies (MWENT), Moscow, 2018, pp. 1-5. DOI: 10.1109/MWENT.2018.8337212

31. Создание низкотемпературных аналоговых ИС для обработки импульсных сигналов датчиков. Часть 2 / О. Дворников, В. Чеховский, В. Дятлов, Н. Прокопенко // Современная электроника, 2015, № 5. С. 24-28

32. Dvornikov O.V., Prokopenko N.N., Butyrlagin N.V. and Pakhomov I.V. The differential and differential difference operational amplifiers of sensor systems based on bipolar-field technological process AGAMC // 2016 International Siberian Conference on Control and Communications (SIBCON), Moscow, 2016, pp. 1-6. DOI: 10.1109/SIBCON.2016.7491792

33. Дворников О.В., Чеховский В.А., Дятлов В.Л., Прокопенко Н.Н. Малошумящий электронный модуль обработки сигналов лавинных фотодиодов // Приборы и методы измерений, № 2 (7), 2013, pp. 42-46.

34. Дворников О. Чеховский В., Дятлов В., Прокопенко Н. Применение структурных кристаллов для создания интерфейсов датчиков // Современная электроника. – 2014. – №. 1. – С. 32-37.

35. Dvornikov O. V., Bugakova A. V., Prokopenko N. N., Dziatlau V. L. and Pakhomov I. V. The microcircuits MH2XA010-02/03 for signal processing of optoelectronic sensors // 2017 18th International Conference of Young Specialists on Micro/Nanotechnologies and Electron Devices (EDM), Erlagol, 2017, pp. 396-402. DOI: 10.1109/EDM.2017.7981781

| название | год | авторы | номер документа |

|---|---|---|---|

| Дифференциальный каскад класса АВ с токовыми выходами, согласованными с разными шинами источников питания | 2024 |

|

RU2822991C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ КАСКАД НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ | 2022 |

|

RU2786941C1 |

| ВХОДНОЙ ДИФФЕРЕНЦИАЛЬНЫЙ КАСКАД НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ ДЛЯ РАБОТЫ ПРИ НИЗКИХ ТЕМПЕРАТУРАХ | 2019 |

|

RU2712416C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ КАСКАД КЛАССА АВ НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ С УПРАВЛЯЮЩИМ P-N ПЕРЕХОДОМ ДЛЯ РАБОТЫ В УСЛОВИЯХ НИЗКИХ ТЕМПЕРАТУР | 2019 |

|

RU2710847C1 |

| Дифференциальный каскад на комплементарных полевых транзисторах | 2018 |

|

RU2684473C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ КАСКАД КЛАССА АВ С НЕЛИНЕЙНЫМ ПАРАЛЛЕЛЬНЫМ КАНАЛОМ | 2020 |

|

RU2740306C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ КАСКАД НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ С ПОВЫШЕННОЙ ТЕМПЕРАТУРНОЙ СТАБИЛЬНОСТЬЮ СТАТИЧЕСКОГО РЕЖИМА | 2020 |

|

RU2746888C1 |

| Дифференциальный усилитель на комплементарных полевых транзисторах с управляемым напряжением ограничения проходной характеристики | 2018 |

|

RU2679970C1 |

| Дифференциальный усилитель на комплементарных полевых транзисторах с управляющим p-n переходом | 2018 |

|

RU2688225C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ КАСКАД НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ С УПРАВЛЯЮЩИМ P-N ПЕРЕХОДОМ КЛАССА АВ С ИЗМЕНЯЕМЫМ НАПРЯЖЕНИЕМ ОГРАНИЧЕНИЯ ПРОХОДНОЙ ХАРАКТЕРИСТИКИ | 2019 |

|

RU2712414C1 |

Изобретение относится к области радиотехники. Технический результат: создание условий, при которых обеспечиваются более высокие значения коэффициента ослабления входных синфазных сигналов и коэффициента подавления помех по шинам питания. Для этого предложен дифференциальный каскад на комплементарных JFET полевых транзисторах с повышенным ослаблением входного синфазного сигнала, который содержит первый (1) и второй (2) входы устройства, первый (3) входной полевой транзистор, первый (4) токовый выход устройства, первую (5) шину источника питания, второй (6) входной полевой транзистор, второй (7) токовый выход устройства, третий (8) входной полевой транзистор, третий (9) токовый выход устройства, вторую (10) шину источника питания, четвертый (11) входной полевой транзистор, четвертый (12) токовый выход устройства, первый (13) дополнительный полевой транзистор, первый (14) вспомогательный двухполюсник. 1 з.п. ф-лы, 12 ил.

1. Дифференциальный каскад на комплементарных JFET полевых транзисторах с повышенным ослаблением входного синфазного сигнала, содержащий первый (1) и второй (2) входы устройства, первый (3) входной полевой транзистор, затвор которого соединен с первым (1) входом устройства, сток соединен с первым (4) токовым выходом устройства, согласованным с первой (5) шиной источника питания, второй (6) входной полевой транзистор, затвор которого соединен со вторым (2) входом устройства, а сток соединен со вторым (7) токовым выходом устройства, согласованным с первой (5) шиной источника питания, причем истоки первого (3) и второго (6) входных полевых транзисторов связаны друг с другом, третий (8) входной полевой транзистор, затвор которого соединен с первым (1) входом устройства, сток соединен с третьим (9) токовым выходом устройства, согласованным со второй (10) шиной источника питания, четвертый (11) входной полевой транзистор, затвор которого соединен со вторым (2) входом устройства, а сток соединен с четвертым (12) токовым выходом устройства, согласованным со второй (10) шиной источника питания, причем истоки третьего (8) и четвертого (11) входных полевых транзисторов связаны друг с другом, отличающийся тем, что в схему введен первый (13) дополнительный полевой транзистор, затвор которого соединен с объединенными истоками первого (3) и второго (6) входных полевых транзисторов, сток подключен к объединенным истокам третьего (8) и четвертого (11) входных полевых транзисторов, а исток связан с объединенными истоками первого (3) и второго (6) входных полевых транзисторов через первый (14) вспомогательный двухполюсник.

2. Дифференциальный каскад на комплементарных JFET полевых транзисторах с повышенным ослаблением входного синфазного сигнала по п. 1, отличающийся тем, что в схему введен второй (20) дополнительный полевой транзистор, затвор которого соединен с объединенными истоками третьего (8) и четвертого (11) входных полевых транзисторов, сток подключен к объединенным истокам первого (3) и второго (6) входных полевых транзисторов, а исток связан с объединенными истоками третьего (8) и четвертого (11) входных полевых транзисторов через второй (21) вспомогательный двухполюсник.

| US 5291149 A1, 01.03.1994 | |||

| US 4079332 A1, 14.03.1978 | |||

| US 7330074 B2, 12.02.2008 | |||

| Дифференциальный усилительный каскад | 1987 |

|

SU1483601A1 |

Авторы

Даты

2019-12-25—Публикация

2019-10-03—Подача