Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения, например, операционных усилителях (ОУ), компараторах и т.п., в т.ч. работающих при низких температурах и воздействии радиации [1].

Известны схемы классических дифференциальных каскадов (ДК) на комплементарных транзисторах [2-29], в т.ч. на комплементарных КМОП полевых транзисторах [3-28] и комплементарных полевых транзисторах с управляющим p-n переходом (JFet) [2], которые стали основой многих серийных аналоговых микросхем.

Для работы ДК при низких температурах и жестких ограничениях на уровень собственных шумов перспективно использование полевых транзисторов с управляющим p-n переходом [30-32]. ДК данного класса активно применяются в структуре малошумящих аналоговых интерфейсов для обработки сигналов датчиков [33-35].

Ближайшим прототипом (фиг. 1) заявляемого устройства является дифференциальный каскад, описанный в патентной заявке US 2006/01255222, 2006г., который содержит первый 1 и второй 2 входы устройства, первый 3 и второй 4 токовые выходы устройства, согласованные с первой 5 шиной источника питания, третий 6 и четвертый 7 токовые выходы устройства, согласованные со второй 8 шиной источника питания, первый 9 входной полевой транзистор, затвор которого соединен с первым 1 входом устройства, а сток подключен к первому 3 токовому выходу устройства, второй 10 входной полевой транзистор, затвор которого соединен со вторым 2 входом устройства, а сток подключен ко второму 4 токовому выходу устройства, третий 11 входной полевой транзистор, сток которого подключен к третьему 6 токовому выходу устройства, четвертый 12 входной полевой транзистор, сток которого соединен с четверым 7 токовым выходом устройства, первый 13 и второй 14 токостабилизирующие двухполюсники.

Существенный недостаток известного ДК, архитектура которого представлена на чертеже фиг.1, состоит в том, что он не работает в режиме класса АВ и, как следствие, при микроамперных статических токах JFET имеет малые значения максимального выходного тока (Iвых.max) и напряжения ограничения проходной характеристики (Uгр). Это значительно сужает области его практического применения, не позволяет обеспечить повышенное быстродействие в режиме большого сигнала, например операционных усилителей [36,37], для которых максимальная скорость нарастания выходного напряжения (SR) в режиме большого сигнала определяется известными формулами:

SR≈2πf1Uгр, (1)

SR≈Iвых.max/Cк , (2)

где f1 – частота единичного усиления скорректированного ОУ;

Uгр – напряжение ограничения проходной характеристики входного ДК в ОУ с классической архитектурой [36, 37];

Ск – емкость корректирующего конденсатора ОУ;

Iвых.max - максимальное значение выходного тока входного ДК, перезаряжающего Ск.

Основная задача предполагаемого изобретения состоит в обеспечении работы ДК в режиме класса АВ, т.е. повышении его Iвых.max, а также в расширении диапазона активной работы ДК – увеличении его напряжения ограничения проходной характеристики (Uгр) в условиях криогенных температур и воздействии проникающей радиации.

Решение поставленной задачи достигается тем, что в дифференциальном каскаде фиг. 1, содержащем первый 1 и второй 2 входы устройства, первый 3 и второй 4 токовые выходы устройства, согласованные с первой 5 шиной источника питания, третий 6 и четвертый 7 токовые выходы устройства, согласованные со второй 8 шиной источника питания, первый 9 входной полевой транзистор, затвор которого соединен с первым 1 входом устройства, а сток подключен к первому 3 токовому выходу устройства, второй 10 входной полевой транзистор, затвор которого соединен со вторым 2 входом устройства, а сток подключен ко второму 4 токовому выходу устройства, третий 11 входной полевой транзистор, сток которого подключен к третьему 6 токовому выходу устройства, четвертый 12 входной полевой транзистор, сток которого соединен с четверым 7 токовым выходом устройства, первый 13 и второй 14 токостабилизирующие двухполюсники, предусмотрены новые элементы и связи – в схему введены первый 15 и второй 16 дополнительные полевые транзисторы, затвор первого 15 дополнительного полевого транзистора подключен к первому 1 входу устройства, затвор второго 16 дополнительного полевого транзистора подключен ко второму 2 входу устройства, между истоками первого 15 и второго 16 дополнительных полевых транзисторов включены последовательно соединенные первый 17 и второй 18 вспомогательные резисторы, общий узел которых соединен с затворами третьего 11 и четвертого 12 входных полевых транзисторов, между истоком первого 15 дополнительного полевого транзистора и второй 8 шиной источника питания включен первый 13 токостабилизирующий двухполюсник, между истоком второго 16 дополнительного полевого транзистора и второй 8 шиной источника питания включен второй 14 токостабилизирующий двухполюсник, исток третьего 11 входного полевого транзистора связан с истоком первого 9 входного полевого транзистора, а исток четвертого 12 входного полевого транзистора связан с истоком второго 10 входного полевого транзистора.

На чертеже фиг. 1 представлена схема ДК-прототипа, а на чертеже фиг. 2 – схема заявляемого дифференциального каскада класса АВ с нелинейным параллельным каналом в соответствии с п.1 и п. 2 формулы изобретения.

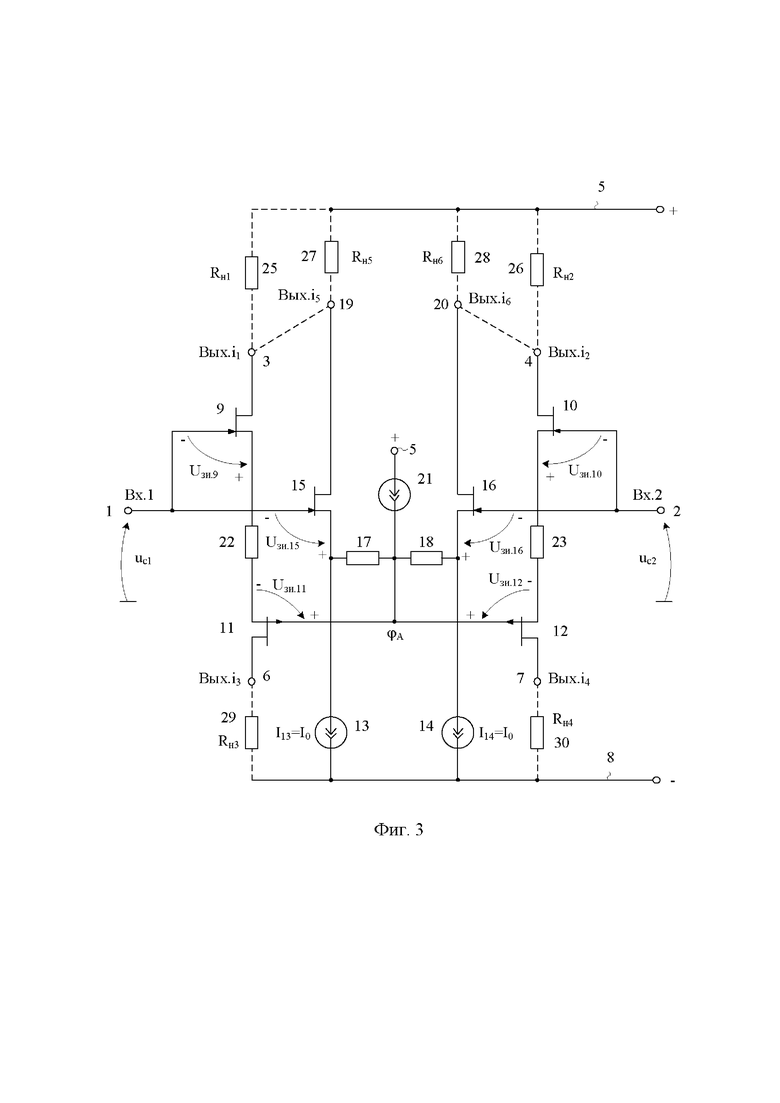

На чертеже фиг. 3 показана заявляемая схема дифференциального каскада класса АВ с нелинейным параллельным каналом по п.3 и п. 4 формулы изобретения.

На чертеже фиг. 4 приведена схема для моделирования CJFet ДК класса АВ фиг.2 (фиг.3) при t=27°C, I1=I2=50 мкА, I3=25 мкА, R5=R6=100 кОм в среде LTspice на моделях JFet транзисторов ОАО «Интеграл» (г. Минск).

На чертеже фиг. 5 представлена проходная характеристика CJFet ДК класса АВ фиг.4 при t=27°C, I1=I2=50 мкА, I3=25 мкА, R5=R6=100 кОм.

На чертеже фиг. 6 показана схема для моделирования CJFet ДК класса АВ фиг.2 (фиг.3) при t=-197°C, I1=I2=50 мкА, I3=25 мкА, R5=R6=100 кОм в среде LTspice на моделях JFet транзисторов ОАО «Интеграл» (г. Минск).

На чертеже фиг. 7 приведена проходная характеристика CJFet ДК класса АВ фиг.6 при t=-197°C, I1=I2=50 мкА, I3=25 мкА, R5=R6=100 кОм.

На чертеже фиг. 8 представлена схема для моделирования CJFet ДК класса АВ фиг.2 (фиг.3) при t=27°C, I1=I2=10 мкА, R5=R6=50 кОм, R7=R8=1 кОм в среде LTspice на моделях JFet транзисторов ОАО «Интеграл» (г. Минск).

На чертеже фиг. 9 показана проходная характеристика CJFet ДК класса АВ фиг.8 при t=27°C, I1=I2=10 мкА, R5=R6=50 кОм, R7=R8=1 кОм.

Дифференциальный каскад класса АВ с нелинейным параллельным каналом фиг. 2 содержит первый 1 и второй 2 входы устройства, первый 3 и второй 4 токовые выходы устройства, согласованные с первой 5 шиной источника питания, третий 6 и четвертый 7 токовые выходы устройства, согласованные со второй 8 шиной источника питания, первый 9 входной полевой транзистор, затвор которого соединен с первым 1 входом устройства, а сток подключен к первому 3 токовому выходу устройства, второй 10 входной полевой транзистор, затвор которого соединен со вторым 2 входом устройства, а сток подключен ко второму 4 токовому выходу устройства, третий 11 входной полевой транзистор, сток которого подключен к третьему 6 токовому выходу устройства, четвертый 12 входной полевой транзистор, сток которого соединен с четверым 7 токовым выходом устройства, первый 13 и второй 14 токостабилизирующие двухполюсники. В схему введены первый 15 и второй 16 дополнительные полевые транзисторы, затвор первого 15 дополнительного полевого транзистора подключен к первому 1 входу устройства, затвор второго 16 дополнительного полевого транзистора подключен ко второму 2 входу устройства, между истоками первого 15 и второго 16 дополнительных полевых транзисторов включены последовательно соединенные первый 17 и второй 18 вспомогательные резисторы, общий узел которых соединен с затворами третьего 11 и четвертого 12 входных полевых транзисторов, между истоком первого 15 дополнительного полевого транзистора и второй 8 шиной источника питания включен первый 13 токостабилизирующий двухполюсник, между истоком второго 16 дополнительного полевого транзистора и второй 8 шиной источника питания включен второй 14 токостабилизирующий двухполюсник, исток третьего 11 входного полевого транзистора связан с истоком первого 9 входного полевого транзистора, а исток четвертого 12 входного полевого транзистора связан с истоком второго 10 входного полевого транзистора.

На чертеже фиг. 2, в соответствии с п. 2 формулы изобретения, первый 3 токовый выход устройства связан со стоком первого 15 дополнительного полевого транзистора, а второй 4 токовый выход устройства связан со стоком второго 16 дополнительного полевого транзистора. В этом случае схема ДК имеет пятый 19 (Вых.i5) и шестой 20 (Вых.i6) дополнительные токовые выходы, к которым могут подключаться двухполюсники нагрузки Rн5 и Rн6.

На чертеже фиг. 3, в соответствии с п. 3 формулы изобретения, общий узел первого 17 и второго 18 последовательно включенных вспомогательных резисторов связан с дополнительным источником опорного тока 21.

На чертеже фиг. 3, в соответствии с п. 4 формулы изобретения, исток третьего 11 входного полевого транзистора связан с истоком первого 9 входного полевого транзистора через первый 22 согласующий резистор, а исток четвертого 12 входного полевого транзистора связан с истоком второго 10 входного полевого транзистора через второй 23 согласующий резистор.

Кроме этого, на чертеже фиг. 3 показаны двухполюсники Rн1÷Rн6, моделирующие свойства нагрузки ДК, например, входные цепи токовых зеркал ОУ, на которую работает предлагаемое устройство. На чертеже фиг.3 данные двухполюсники обозначены как элементы 25÷30.

Схема ДК фиг. 2 может рассматриваться как многоканальный дифференциальный усилитель, состоящий из линейного дифференциального канала усиления (элементы 13÷18) и нелинейного дифференциального параллельного канала (элементы 9, 11 и 10, 12), работающего при большом входном дифференциальном напряжении и обеспечивающего повышенные максимальные токи в нагрузке Rн5, Rн6. При этом проводимость передачи входного напряжения ДК к дополнительным токовым выходам 19 и 20 для линейного канала усиления определяется, в основном, сопротивлениями первого 17 и второго 18 вспомогательных резисторов. За счет рационального выбора этих сопротивлений можно в широких пределах управлять численными значениями максимальных выходных токов ДК.

Рассмотрим более подробно работу ДК фиг. 3 для случая, когда ток дополнительного источника опорного тока 21 близок к нулю (I21=0).

В статическом режиме рабочие токи стоков полевых транзисторов схемы фиг. 3 (при нулевом входном дифференциальном напряжении uвх=uc1-uc2) определяются следующими уравнениями:

Ic15=I13, Ic16=I14, (5)

где R22, R23 – сопротивления первого 22 и второго 23 согласующих резисторов;

Iвых.i – выходной статический ток i-го токового выхода ДК (i=1,2,3,4);

IR24, IR23 – токи первого 22 и второго 23 согласующих резисторов;

Uзи.i - напряжение затвор-исток i-го полевого транзистора;

I13, I14 – токи первого 13 и второго 14 токостабилизирующих двухполюсников.

Таким образом, за счет выбора сопротивлений первого 22 и второго 23 согласующих резисторов, а также токов I13, I14, влияющих на Uзи.15 (Uзи.16), в схеме фиг. 3 устанавливаются заданные значения статических выходных токов ДК. Так, например при R22=R23=1 кОм и I13=I14=10 мкА выходные токи ДК, протекающие в элементах нагрузки R1÷R4 (фиг. 8), принимают значения порядка 470 мкА при t=27°C.

Дополнительный источник опорного тока 21 позволяет обеспечить в схеме фиг. 3 заданные статические токи JFET в более широком диапазоне их численных значений.

Если напряжение на входе ДК фиг. 3 получает небольшое положительное приращение относительно напряжения на входе 2 (uвх=uc1-uc2), то это вызывает увеличение токов стока первого 9 и третьего 11 входных полевых транзисторов. При этом токи стока второго 10 и четвертого 12 входных полевых транзисторов уменьшаются, а на проходной характеристике ДК Iвых.i=f(uвх) формируются начальные участки (фиг. 5, фиг. 7), крутизна которых зависит от крутизны стокозатворных характеристик применяемых полевых транзисторов и численных значений R22 и R23.

Дальнейшее увеличение uвх приводит к полному запиранию второго 10 и четвертого 12 входных полевых транзисторов, которые теперь можно исключить из рассмотрения работы ДК. При этом выходные токи Iвых.1 и Iвых.3 ДК фиг. 3, в отличие от ДК-прототипа фиг. 1, не ограничиваются и получают дополнительное приращение относительно статического уровня:

где S9, S11 - крутизна стоко-затворной характеристики первого 9 и третьего 11 входных полевых транзисторов.

Как следствие, на проходных характеристиках ДК (фиг. 5, фиг. 7) формируется второй пропорциональный uвх участок, крутизна которого определяется, в основном, сопротивлением резистора R22 (6).

Таким образом, схема ДК фиг. 3, в отличие от ДК–прототипа фиг. 1, работает в режиме класса АВ, когда максимальные выходные токи Iвых.max значительно превышают выходные токи ДК в статическим режиме, а напряжение ограничения проходной характеристики (Uгр) близко к напряжению питания (фиг. 5, фиг. 7). Увеличение Uгр и Iвых.max, несмотря на нелинейность проходной характеристики [36,37], позволяет повысить SR операционных усилителей на основе заявляемого ДК.

Существенная особенность предлагаемого ДК состоит в том, что он фактически работает в режиме класса AB (фиг. 5). Действительно, при нулевом входном сигнале выходные статические токи ДК в 18 раз меньше, чем максимальные выходные токи ДК при большом входном сигнале. Это позволяет получить в ОУ на основе предлагаемого ДК более высокие (в 18 раз) значения максимальной скорости нарастания выходного напряжения [36,37].

Таким образом, заявляемое устройство имеет существенные преимущества в сравнении с известным схемотехническим решением ДК, что позволяет рекомендовать его для практического использования в различных ОУ и построения низкотемпературных и радиационно-стойких аналоговых микросхем по JFet техпроцессу ОАО «Интеграл» (г. Минск), а также комплементарному биполярно-полевому технологическому процессу АО «НПП «Пульсар» (г. Москва).

Библиографический список

1. O. V. Dvornikov, V. L. Dziatlau, N. N. Prokopenko, K. O. Petrosiants, N. V. Kozhukhov and V. A. Tchekhovski, "The accounting of the simultaneous exposure of the low temperatures and the penetrating radiation at the circuit simulation of the BiJFET analog interfaces of the sensors," 2017 International Siberian Conference on Control and Communications (SIBCON), Astana, 2017, pp. 1-6. DOI: 10.1109/SIBCON.2017.7998507

2. Патент US 5.291.149 fig. 4, 1994 г.

3. Патент US 4.377.789, fig. 1, 1983 г.

4. Патентная заявка US 2006/0125522, 2006 г.

5. Патент US 7.907.011, 2011

6. US 2008/0024217, fig. 1, 2008 г.

7. Патент EP 0318263,1989 г.

8. Патент US 5.907.259, fig. 1, 1999 г.

9. Патент US 7.408.410, 2008 г.

10. Патент US 6.628.168, fig.2, 2003 г.

11. Патентная заявка US 2009/0302895, 2009 г.

12. Патент US 5.714.906, fig. 4, 1998 г.

13. Патент US 2005/0285677, 2005 г.

14. Патент US 5.070.306, fig. 3, 1991 г.

15. Патент US 2010/001797, 2010 г.

16. Патент US 6.972.623, fig. 4, fig. 6, 2005 г.

17. Патент US 2008/0252374, 2008 г.

18. Патент US 7.586.373, 2009 г.

19. Патент US 2006/0215787, 2006 г.

20. Патент US 7.453.319, 2008 г.

21. Патент US 2004/0174216, fig. 2, 2004 г.

22. Патент US 7.215.200, fig. 6, 2007 г.

23. Патент US № 6.433.637, fig. 2, 2002 г.

24. Патент US № 6.392.485, 2002 г.

25. Патент US 5.963.085, fig. 3, 1999 г.

26. Патент US 6.788.143, 2004 г.

27. Патент US 4.390.850, 1983 г.

28. Патент US 6.696.894, fig. 1, 2004 г.

29. N. N. Prokopenko, N. V. Butyrlagin, A. V. Bugakova and A. A. Ignashin, "Method for speeding the micropower CMOS operational amplifiers with dual-input-stages," 2017 24th IEEE International Conference on Electronics, Circuits and Systems (ICECS), Batumi, 2017, pp. 78-81.

30. K. O. Petrosyants, M. R. Ismail-zade, L. M. Sambursky, O. V. Dvornikov, B. G. Lvov and I. A. Kharitonov, "Automation of parameter extraction procedure for Si JFET SPICE model in the −200…+110°C temperature range," 2018 Moscow Workshop on Electronic and Networking Technologies (MWENT), Moscow, 2018, pp. 1-5. DOI: 10.1109/MWENT.2018.8337212

31. Создание низкотемпературных аналоговых ИС для обработки импульсных сигналов датчиков. Часть 2 / О. Дворников, В. Чеховский, В. Дятлов, Н. Прокопенко // Современная электроника, 2015, № 5. С. 24-28

32. O. V. Dvornikov, N. N. Prokopenko, N. V. Butyrlagin and I. V. Pakhomov, "The differential and differential difference operational amplifiers of sensor systems based on bipolar-field technological process AGAMC," 2016 International Siberian Conference on Control and Communications (SIBCON), Moscow, 2016, pp. 1-6. DOI: 10.1109/SIBCON.2016.7491792

33. Дворников О.В., Чеховский В.А., Дятлов В.Л., Прокопенко Н.Н. "Малошумящий электронный модуль обработки сигналов лавинных фотодиодов" Приборы и методы измерений, no. 2 (7), 2013, pp. 42-46.

34. Дворников О. Чеховский В., Дятлов В., Прокопенко Н. Применение структурных кристаллов для создания интерфейсов датчиков //Современная электроника. – 2014. – №. 1. – С. 32-37.

35. O. V. Dvornikov, A. V. Bugakova, N. N. Prokopenko, V. L. Dziatlau and I. V. Pakhomov, "The microcircuits MH2XA010-02/03 for signal processing of optoelectronic sensors," 2017 18th International Conference of Young Specialists on Micro/Nanotechnologies and Electron Devices (EDM), Erlagol, 2017, pp. 396-402. DOI: 10.1109/EDM.2017.7981781

36. Прокопенко Н.Н. Нелинейная активная коррекция в прецизионных аналоговых микросхемах (монография) // Ростов-на-Дону: Изд-во Северо-Кавказского научного центра высшей школы, 2000. 222с.

37. Операционные усилители с непосредственной связью каскадов: монография / Анисимов В.И., Капитонов М.В., Прокопенко Н.Н., Соколов Ю.М. - Л.: «Энергия», 1979. - 148 с.

| название | год | авторы | номер документа |

|---|---|---|---|

| ВХОДНОЙ КАСКАД КЛАССА АВ БЫСТРОДЕЙСТВУЮЩЕГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ С РЕЗИСТИВНОЙ ОТРИЦАТЕЛЬНОЙ ОБРАТНОЙ СВЯЗЬЮ ПО СИНФАЗНОМУ СИГНАЛУ | 2022 |

|

RU2784382C1 |

| НЕИНВЕРТИРУЮЩИЙ УСИЛИТЕЛЬ ТОКА КЛАССА "АВ" | 2022 |

|

RU2783042C1 |

| АРСЕНИД-ГАЛЛИЕВЫЙ ВХОДНОЙ ДИФФЕРЕНЦИАЛЬНЫЙ КАСКАД КЛАССА АВ БЫСТРОДЕЙСТВУЮЩЕГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ | 2022 |

|

RU2786943C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ВХОДНОЙ КАСКАД БЫСТРОДЕЙСТВУЮЩЕГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ ДЛЯ КМОП-ТЕХПРОЦЕССОВ | 2014 |

|

RU2566963C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ КЛАССА АВ НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ С УПРАВЛЯЮЩИМ P-N ПЕРЕХОДОМ | 2020 |

|

RU2736549C1 |

| Дифференциальный каскад класса АВ с токовыми выходами, согласованными с разными шинами источников питания | 2024 |

|

RU2822991C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ КАСКАД НА КОМПЛЕМЕНТАРНЫХ JFET ПОЛЕВЫХ ТРАНЗИСТОРАХ С ПОВЫШЕННЫМ ОСЛАБЛЕНИЕМ ВХОДНОГО СИНФАЗНОГО СИГНАЛА | 2019 |

|

RU2710296C1 |

| МНОГОФУНКЦИОНАЛЬНОЕ ТОКОВОЕ ЗЕРКАЛО НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ С УПРАВЛЯЮЩИМ PN-ПЕРЕХОДОМ ДЛЯ РАБОТЫ ПРИ НИЗКИХ ТЕМПЕРАТУРАХ | 2019 |

|

RU2720557C1 |

| ПРОМЕЖУТОЧНЫЙ КАСКАД ОПЕРАЦИОННОГО УСИЛИТЕЛЯ С ПАРАФАЗНЫМ ВЫХОДОМ НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ С УПРАВЛЯЮЩИМ P-N ПЕРЕХОДОМ | 2019 |

|

RU2720555C1 |

| ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ ДЛЯ АКТИВНЫХ RC-ФИЛЬТРОВ, РАБОТАЮЩИХ В УСЛОВИЯХ ВОЗДЕЙСТВИЯ ПОТОКА НЕЙТРОНОВ И НИЗКИХ ТЕМПЕРАТУР | 2020 |

|

RU2724921C1 |

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения, например, операционных усилителях (ОУ), компараторов и т.п., в том числе работающих при низких температурах и воздействии радиации. Технический результат: обеспечение работы в режиме класса АВ, т.е. повышение его максимального выходного напряжения, а также увеличение его напряжения ограничения проходной характеристики (Uгр) в условиях криогенных температур и воздействия проникающей радиации. Дифференциальный каскад класса АВ с нелинейным параллельным каналом содержит первый (1) и второй (2) входы, первый (3) и второй (4) токовые выходы, третий (6) и четвертый (7) токовые выходы, первый (9) входной полевой транзистор, затвор которого соединен с первым (1) входом, а сток подключен к первому (3) токовому выходу, второй (10) входной полевой транзистор, затвор которого соединен со вторым (2) входом, а сток подключен ко второму (4) токовому выходу, третий (11) входной полевой транзистор, сток которого подключен к третьему (6) токовому выходу, четвертый (12) входной полевой транзистор, сток которого соединен с четвертым (7) токовым выходом, первый (13) и второй (14) токостабилизирующие двухполюсники. В схему введены первый (15) и второй (16) дополнительные полевые транзисторы, затвор первого (15) дополнительного полевого транзистора подключен к первому (1) входу, затвор второго (16) дополнительного полевого транзистора подключен ко второму (2) входу, между истоками первого (15) и второго (16) дополнительных полевых транзисторов включены последовательно соединенные первый (17) и второй (18) вспомогательные резисторы, общий узел которых соединен с затворами третьего (11) и четвертого (12) входных полевых транзисторов, между истоком первого (15) дополнительного полевого транзистора и второй (8) шиной источника питания включен первый (13) токостабилизирующий двухполюсник, между истоком второго (16) дополнительного полевого транзистора и второй (8) шиной источника питания включен второй (14) токостабилизирующий двухполюсник, исток третьего (11) входного полевого транзистора связан с истоком первого (9) входного полевого транзистора, а исток четвертого (12) входного полевого транзистора связан с истоком второго (10) входного полевого транзистора. 3 з.п. ф-лы, 9 ил.

1. Дифференциальный каскад класса АВ с нелинейным параллельным каналом, содержащий первый (1) и второй (2) входы устройства, первый (3) и второй (4) токовые выходы устройства, согласованные с первой (5) шиной источника питания, третий (6) и четвертый (7) токовые выходы устройства, согласованные со второй (8) шиной источника питания, первый (9) входной полевой транзистор, затвор которого соединен с первым (1) входом устройства, а сток подключен к первому (3) токовому выходу устройства, второй (10) входной полевой транзистор, затвор которого соединен со вторым (2) входом устройства, а сток подключен ко второму (4) токовому выходу устройства, третий (11) входной полевой транзистор, сток которого подключен к третьему (6) токовому выходу устройства, четвертый (12) входной полевой транзистор, сток которого соединен с четверым (7) токовым выходом устройства, первый (13) и второй (14) токостабилизирующие двухполюсники, отличающийся тем, что введены первый (15) и второй (16) дополнительные полевые транзисторы, затвор первого (15) дополнительного полевого транзистора подключен к первому (1) входу устройства, затвор второго (16) дополнительного полевого транзистора подключен ко второму (2) входу устройства, между истоками первого (15) и второго (16) дополнительных полевых транзисторов включены последовательно соединенные первый (17) и второй (18) вспомогательные резисторы, общий узел которых соединен с затворами третьего (11) и четвертого (12) входных полевых транзисторов, между истоком первого (15) дополнительного полевого транзистора и второй (8) шиной источника питания включен первый (13) токостабилизирующий двухполюсник, между истоком второго (16) дополнительного полевого транзистора и второй (8) шиной источника питания включен второй (14) токостабилизирующий двухполюсник, исток третьего (11) входного полевого транзистора связан с истоком первого (9) входного полевого транзистора, а исток четвертого (12) входного полевого транзистора связан с истоком второго (10) входного полевого транзистора.

2. Дифференциальный каскад класса АВ с нелинейным параллельным каналом по п.1, отличающийся тем, что первый (3) токовый выход устройства связан со стоком первого (15) дополнительного полевого транзистора, а второй (4) токовый выход устройства связан со стоком второго (16) дополнительного полевого транзистора.

3. Дифференциальный каскад класса АВ с нелинейным параллельным каналом по п.1, отличающийся тем, что общий узел первого (17) и второго (18) последовательно включенных вспомогательных резисторов связан с дополнительным источником опорного тока (21).

4. Дифференциальный каскад класса АВ с нелинейным параллельным каналом по п.1, отличающийся тем, что исток третьего (11) входного полевого транзистора связан с истоком первого (9) входного полевого транзистора через первый (22) согласующий резистор, а исток четвертого (12) входного полевого транзистора связан с истоком второго (10) входного полевого транзистора через второй (23) согласующий резистор.

| ДИФФЕРЕНЦИАЛЬНЫЙ КАСКАД КЛАССА АВ НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ С УПРАВЛЯЮЩИМ P-N ПЕРЕХОДОМ ДЛЯ РАБОТЫ В УСЛОВИЯХ НИЗКИХ ТЕМПЕРАТУР | 2019 |

|

RU2710847C1 |

| Маслоуловитель для предохранения от попадания масла из шестеренкой коробки в полость якорного подшипника электрической машины | 1930 |

|

SU25819A1 |

| US 5907262 A, 25.05.1999 | |||

| US 5049653 A, 17.09.1991. | |||

Авторы

Даты

2021-01-13—Публикация

2020-07-08—Подача