Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения, например, операционных усилителях (ОУ), компараторах, мостовых усилителях мощности и т.п., в т.ч. работающих при низких температурах и воздействии радиации.

Известны схемы дифференциальных каскадов (ДК) на комплементарных транзисторах с управляющим p-n переходом (JFet) [1-9], которые стали основой многих аналоговых устройств с малым уровнем шумов.

Для работы при низких температурах и жестких ограничениях на уровень шумов перспективно использование JFet полевых транзисторов [10-13]. ДК данного класса активно применяются в структуре малошумящих аналоговых интерфейсов для обработки сигналов датчиков [12].

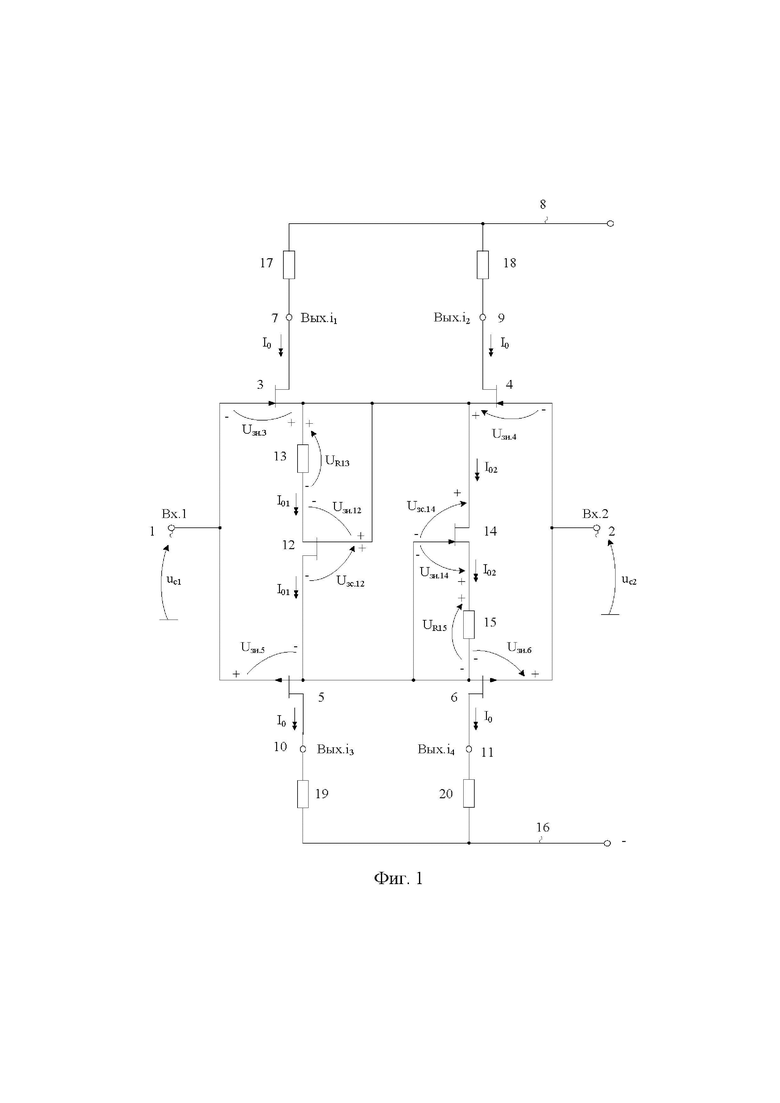

Ближайшим прототипом (фиг. 1) заявляемого устройства является дифференциальный каскад, описанный в патенте RU 2710296, fig.2, 2019г., который содержит первый 1 и второй 2 входы устройства, первый 3 и второй 4 входные полевые транзисторы с управляющим p-n переходом, истоки которых объединены, третий 5 и четвертый 6 входные полевые транзисторы с управляющим p-n переходом, истоки которых соединены друг с другом, причем затвор первого 3 и затвор третьего 5 входных полевых транзисторов с управляющим p-n переходом подключены к первому 1 входу устройства, а затвор второго 4 и затвор четвертого 6 входных полевых транзисторов с управляющим p-n переходом связаны со вторым 2 входом устройства, первый 7 токовый выход устройства, согласованный с первой 8 шиной источника питания и подключенный к стоку первого 3 входного полевого транзистора с управляющим p-n переходом, второй 9 токовый выход устройства, согласованный с первой 8 шиной источника питания и подключенный к стоку второго 4 входного полевого транзистора с управляющим p-n переходом, третий 10 токовый выход устройства, связанный со стоком третьего 5 входного полевого транзистора с управляющим p-n переходом, четвертый 11 токовый выход устройства, связанный со стоком четвертого 6 входного полевого транзистора с управляющим p-n переходом, третий 12 вспомогательный полевой транзистор с управляющим p-n переходом, исток которого соединен с объединенными истоками первого 3 и второго 4 входных полевых транзисторов с управляющим p-n переходом через первый 13 вспомогательный резистор, второй 14 вспомогательный полевой транзистор с управляющим p-n переходом и второй 15 вспомогательный резистор.

Существенный недостаток известного ДК фиг. 1 состоит в том, что статический режим его входных полевых транзисторов (ПТ) изменяется под влиянием низких и повышенных температур. Это приводит к изменению в крутизны ДК, отрицательно сказывается на основных статических и динамических параметрах ДК (систематической составляющей напряжения смещения нуля, коэффициенте ослабления входных синфазных сигналов ДК (Кос.сф), коэффициенте подавления помех по шинам питания (Кпп), коэффициенте усиления по напряжению). Эти эффекты становится источником дополнительных погрешностей ДК при усилении малых сигналов.

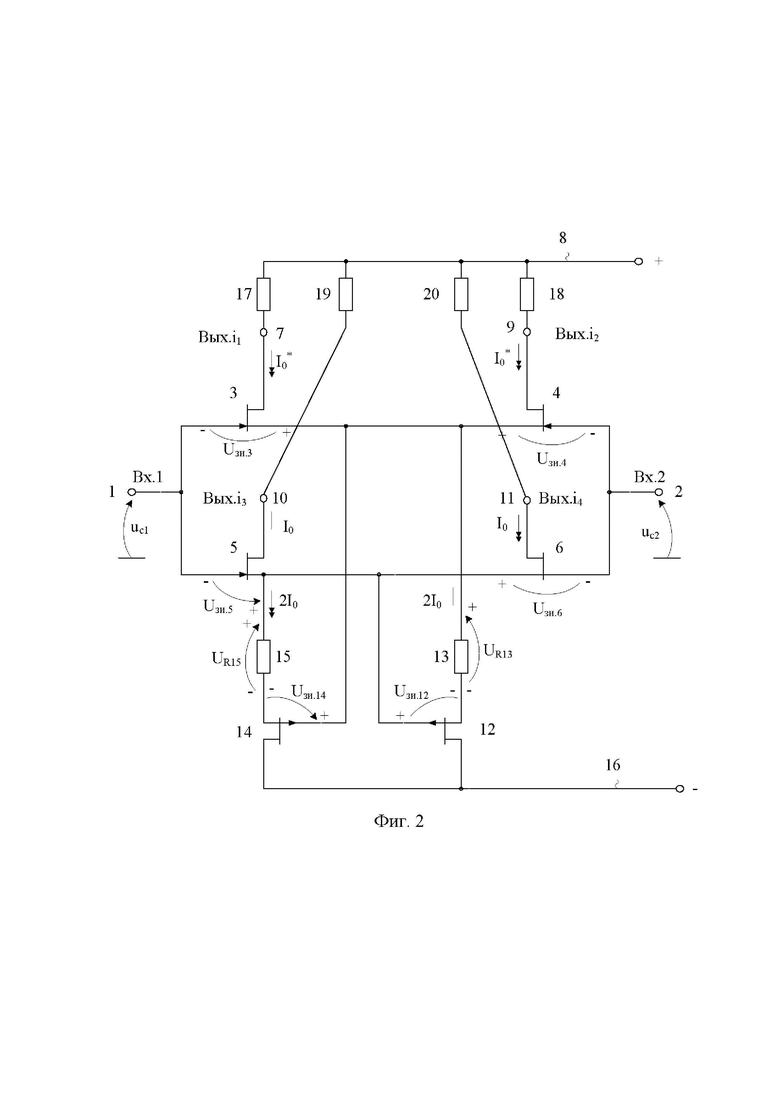

Основная задача предполагаемого изобретения состоит в создании условий, при которых в ДК фиг. 2 обеспечивается более высокая стабильность статического режима входных транзисторов при воздействии отрицательных температур.

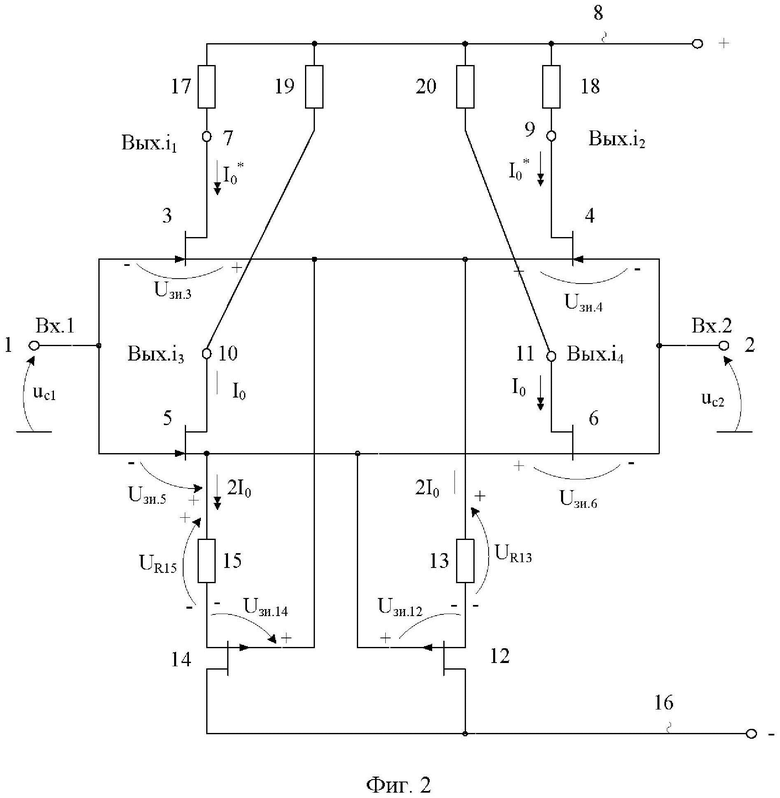

Поставленная задача решается тем, что в дифференциальном каскаде фиг. 1, содержащем первый 1 и второй 2 входы устройства, первый 3 и второй 4 входные полевые транзисторы с управляющим p-n переходом, истоки которых объединены, третий 5 и четвертый 6 входные полевые транзисторы с управляющим p-n переходом, истоки которых соединены друг с другом, причем затвор первого 3 и затвор третьего 5 входных полевых транзисторов с управляющим p-n переходом подключены к первому 1 входу устройства, а затвор второго 4 и затвор четвертого 6 входных полевых транзисторов с управляющим p-n переходом связаны со вторым 2 входом устройства, первый 7 токовый выход устройства, согласованный с первой 8 шиной источника питания и подключенный к стоку первого 3 входного полевого транзистора с управляющим p-n переходом, второй 9 токовый выход устройства, согласованный с первой 8 шиной источника питания и подключенный к стоку второго 4 входного полевого транзистора с управляющим p-n переходом, третий 10 токовый выход устройства, связанный со стоком третьего 5 входного полевого транзистора с управляющим p-n переходом, четвертый 11 токовый выход устройства, связанный со стоком четвертого 6 входного полевого транзистора с управляющим p-n переходом, третий 12 вспомогательный полевой транзистор с управляющим p-n переходом, исток которого соединен с объединенными истоками первого 3 и второго 4 входных полевых транзисторов с управляющим p-n переходом через первый 13 вспомогательный резистор, второй 14 вспомогательный полевой транзистор с управляющим p-n переходом и второй 15 вспомогательный резистор, предусмотрены новые элементы и связи - третий 10 и четвертый 11 токовые выходы устройства согласованы с первой 8 шиной источника питания, затвор третьего 12 вспомогательного полевого транзистора с управляющим p-n переходом подключен к объединенными истокам третьего 5 и четвертого 6 входных полевых транзисторов с управляющим p-n переходом, а его сток согласован со второй 16 шиной источника питания, исток второго 14 вспомогательного полевого транзистора с управляющим p-n переходом связан с объединенными истоками третьего 5 и четвертого 6 входных полевых транзисторов с управляющим p-n переходом через второй 15 вспомогательный резистор, затвор второго 14 вспомогательного полевого транзистора с управляющим p-n переходом соединен с объединенными истоками первого 3 и второго 4 входных полевых транзисторов с управляющим p-n переходом, а сток второго 14 вспомогательного полевого транзистора с управляющим p-n переходом подключен ко второй 16 шине источника питания.

На чертеже фиг. 1 представлена схема ДК-прототипа по патенту RU 2710296, fig.2, 2019 г., а на чертеже фиг. 2 - схема заявляемого дифференциального каскада в соответствии с формулой изобретения.

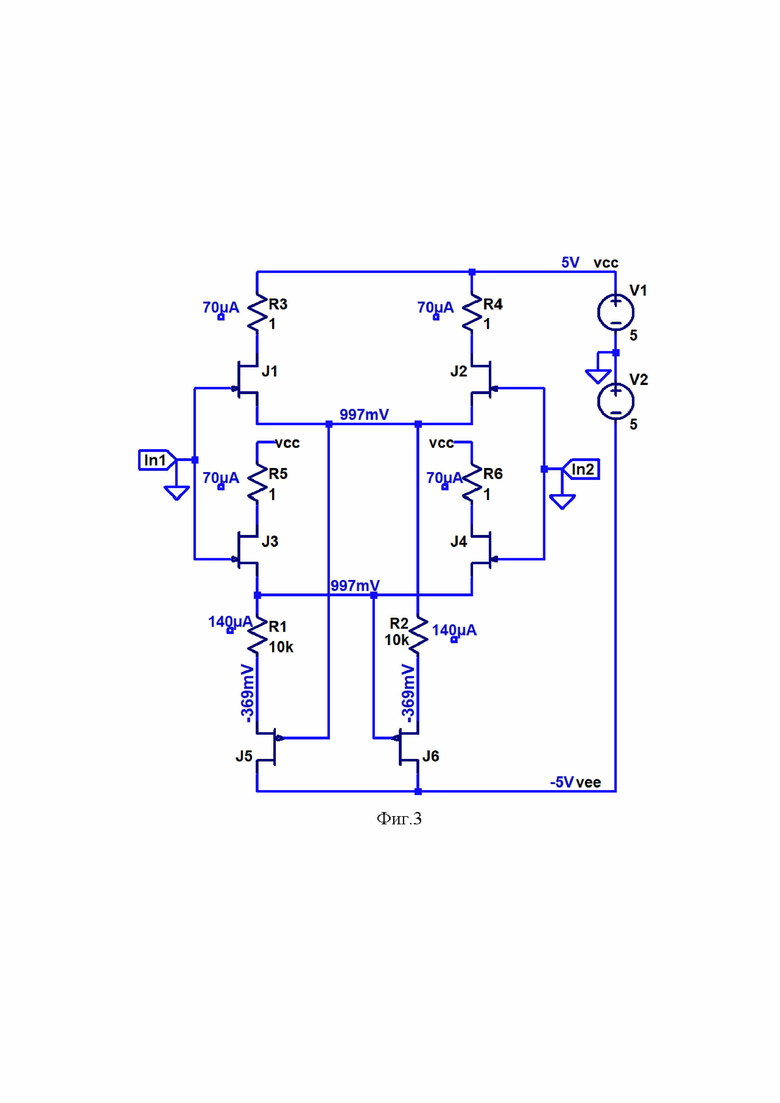

На чертеже фиг.3 приведена схема для моделирования заявляемого ДК фиг. 2 в среде LTspice на моделях JFET транзисторов АО «Интеграл» при t=27°C, R1=R2=10 кОм.

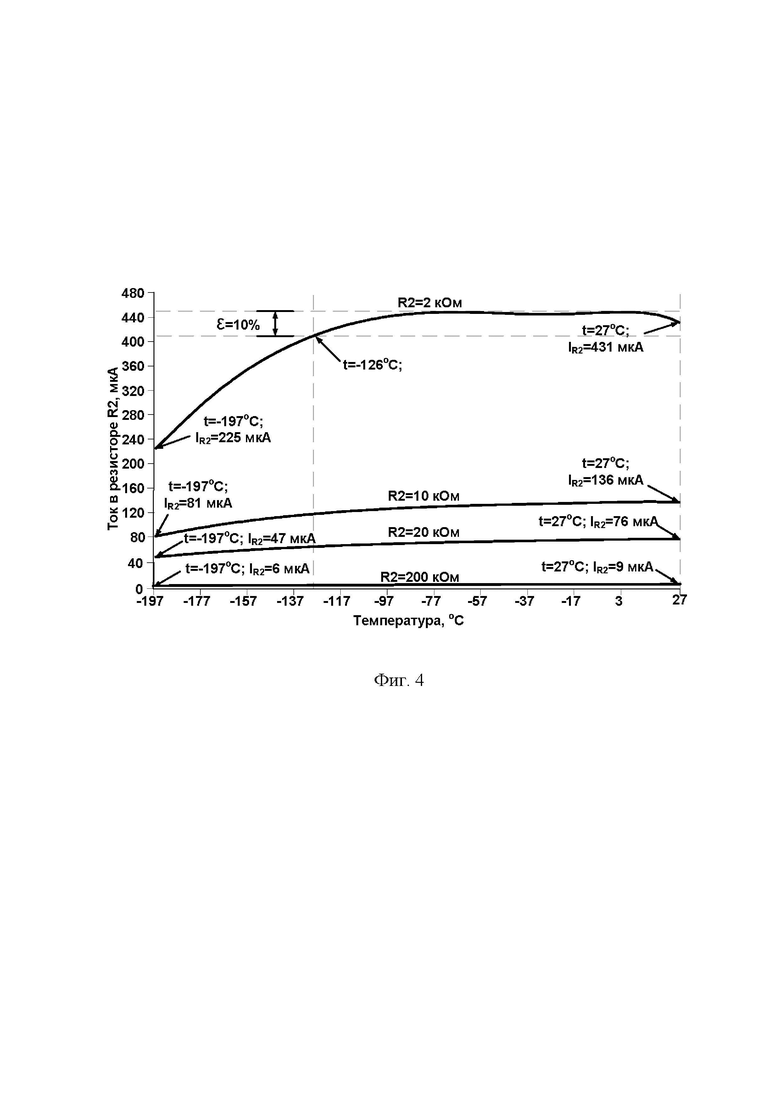

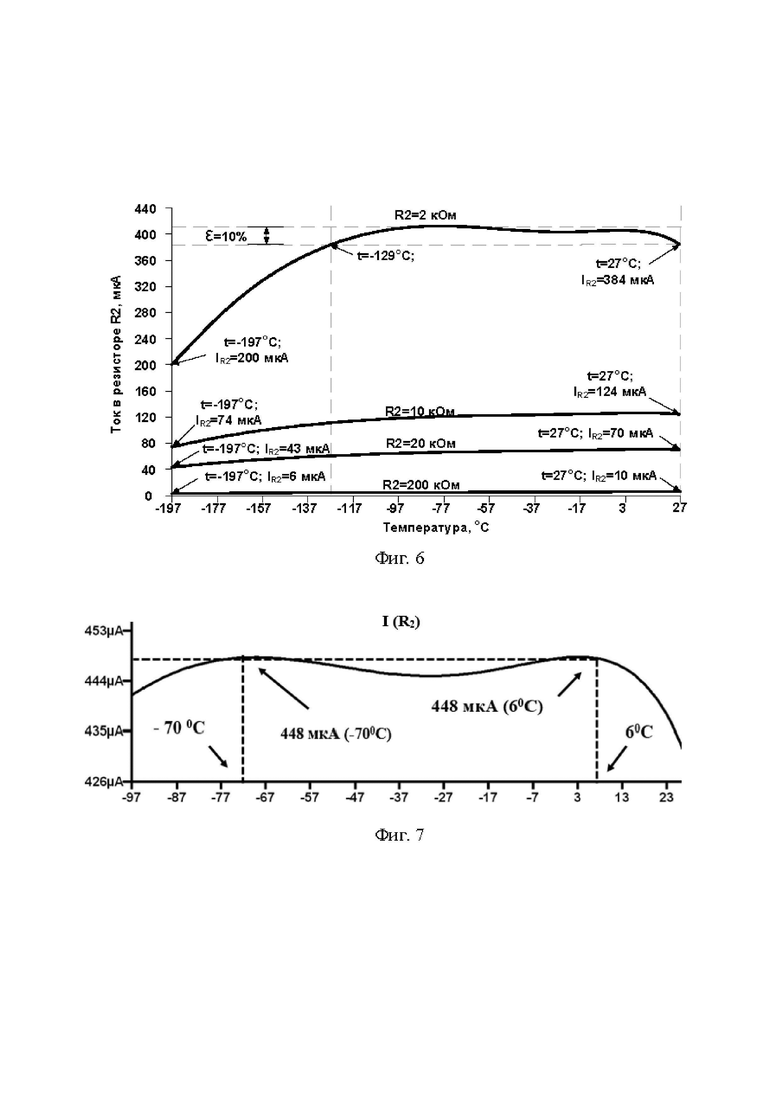

На чертеже фиг. 4 показаны результаты компьютерного моделирования температурной зависимости тока в резисторе R2 ДК фиг. 3 при R1=10 кОм, R2= 2 кОм, 10 кОм, 20 кОм, 200 кОм в среде LTspice на моделях JFET транзисторов АО «Интеграл» (г. Минск).

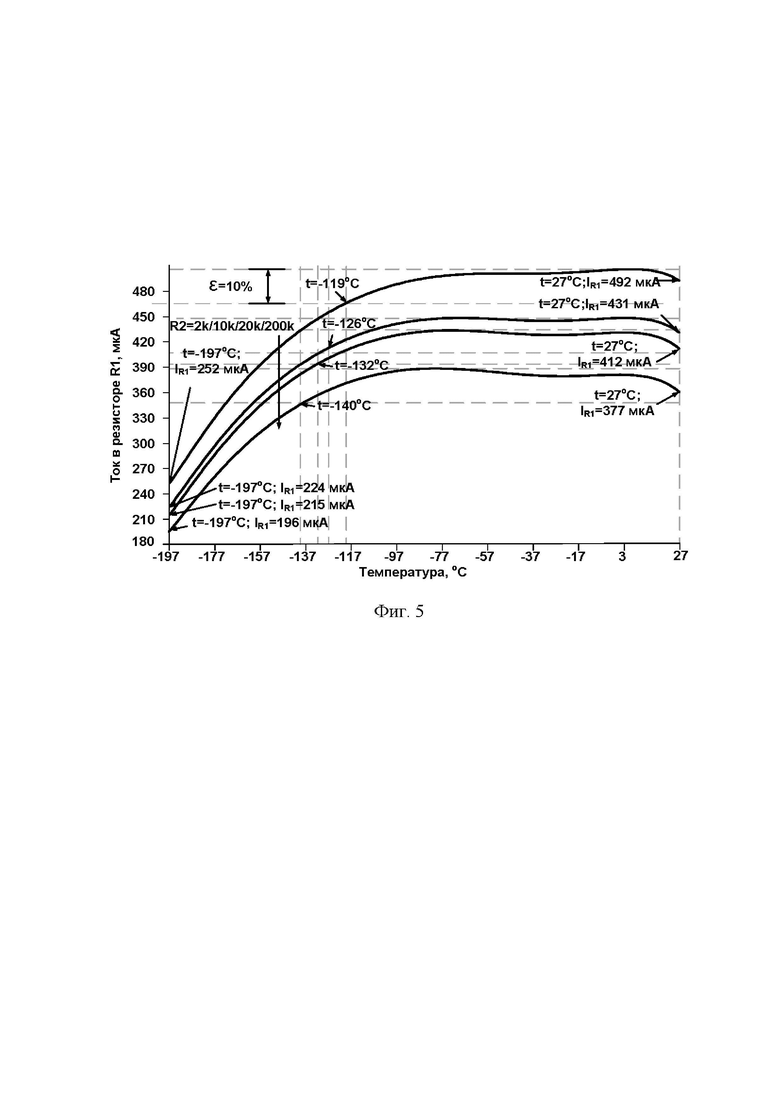

На чертеже фиг. 5 представлены результаты компьютерного моделирования температурной зависимости тока в резисторе R1 ДК фиг. 3 при R1=2 кОм=const, R2= 2 кОм, 10 кОм, 20 кОм, 200 кОм в среде LTspice на моделях JFET транзисторов АО «Интеграл» (г. Минск).

На чертеже фиг. 6 показаны результаты компьютерного моделирования температурной зависимости тока в резисторе R2 ДК фиг. 3 при R1=100 кОм=const, R2= 100 кОм, 10 кОм, 20 кОм, 200 кОм в среде LTspice на моделях JFET транзисторов АО «Интеграл» (г. Минск).

На чертеже фиг. 7 приведено компьютерное моделирование температурной зависимости тока в резисторе R1 ДК фиг. 3 при R1 = 10 кОм, R2 = 2 кОм в среде LTspice на моделях JFET транзисторов АО «Интеграл» (г. Минск).

Дифференциальный каскад на комплементарных полевых транзисторах с повышенной температурной стабильностью статического режима фиг. 2 содержит первый 1 и второй 2 входы устройства, первый 3 и второй 4 входные полевые транзисторы с управляющим p-n переходом, истоки которых объединены, третий 5 и четвертый 6 входные полевые транзисторы с управляющим p-n переходом, истоки которых соединены друг с другом, причем затвор первого 3 и затвор третьего 5 входных полевых транзисторов с управляющим p-n переходом подключены к первому 1 входу устройства, а затвор второго 4 и затвор четвертого 6 входных полевых транзисторов с управляющим p-n переходом связаны со вторым 2 входом устройства, первый 7 токовый выход устройства, согласованный с первой 8 шиной источника питания и подключенный к стоку первого 3 входного полевого транзистора с управляющим p-n переходом, второй 9 токовый выход устройства, согласованный с первой 8 шиной источника питания и подключенный к стоку второго 4 входного полевого транзистора с управляющим p-n переходом, третий 10 токовый выход устройства, связанный со стоком третьего 5 входного полевого транзистора с управляющим p-n переходом, четвертый 11 токовый выход устройства, связанный со стоком четвертого 6 входного полевого транзистора с управляющим p-n переходом, третий 12 вспомогательный полевой транзистор с управляющим p-n переходом, исток которого соединен с объединенными истоками первого 3 и второго 4 входных полевых транзисторов с управляющим p-n переходом через первый 13 вспомогательный резистор, второй 14 вспомогательный полевой транзистор с управляющим p-n переходом и второй 15 вспомогательный резистор. Третий 10 и четвертый 11 токовые выходы устройства согласованы с первой 8 шиной источника питания, затвор третьего 12 вспомогательного полевого транзистора с управляющим p-n переходом подключен к объединенными истокам третьего 5 и четвертого 6 входных полевых транзисторов с управляющим p-n переходом, а его сток согласован со второй 16 шиной источника питания, исток второго 14 вспомогательного полевого транзистора с управляющим p-n переходом связан с объединенными истоками третьего 5 и четвертого 6 входных полевых транзисторов с управляющим p-n переходом через второй 15 вспомогательный резистор, затвор второго 14 вспомогательного полевого транзистора с управляющим p-n переходом соединен с объединенными истоками первого 3 и второго 4 входных полевых транзисторов с управляющим p-n переходом, а сток второго 14 вспомогательного полевого транзистора с управляющим p-n переходом подключен ко второй 16 шине источника питания.

На чертеже фиг.2 элементы 17, 18, 19 и 20 моделируют свойства нагрузки ДК, которые подключаются к соответствующим токовым выходам устройства 7, 9, 10, 11.

Рассмотрим работу ДУ фиг. 2 с учетом результатов его компьютерного моделирования, представленных на чертежах фиг. 4, фиг.5, фиг. 6 и фиг. 7.

Графики фиг. 4 показывают, что при изменении сопротивления резистора R2 ток в этом резисторе при R2=2 кОм изменяется не более чем на 10% в диапазоне температур от -126°С до +27°С.

Результаты компьютерного моделирования (фиг. 5) температурной зависимости тока в резисторе R1 ДК фиг. 3 при R1=2 кОм=const, R2= 2 кОм, 10 кОм, 20 кОм, 200 кОм в среде LTspice на моделях JFET транзисторов АО «Интеграл» (г. Минск) также показывают, что при определенных сопротивлениях резистора R2 ток в резисторе R1 незначительно изменяется в диапазоне температур от -119°С до +27°С.

Аналогичные выводы можно сделать и по результатам анализа графиков фиг. 6.

Графики фиг. 4 - фиг. 6 позволяют сделать вывод о существовании некоторых оптимальных значений R1, R2, при которых температурные изменения статических токов в резисторе R2 (токов общей истоковой цепи ДК) незначительны.

Представленная на чертеже фиг. 7 температурная зависимость тока в резисторе R2 для оптимальных значений R1 и R2, которые получены в результате параметрической оптимизации схемы фиг. 2 с помощью рассмотренной в [14] САПР, показывает, что за счет рационального выбора численных значений R1, R2 можно обеспечить незначительные изменения токов в резисторе R2 в широком диапазоне температур. Этот эффект позволяет стабилизировать крутизну ДК фиг. 3 и обеспечить температурно стабильные значения основных статических и динамических параметров ДК.

Следовательно, заявляемое устройство имеет существенные преимущества в сравнении с ДК-прототипом. Это позволяет рекомендовать рассмотренную схему ДК для практического использования в прецизионных ОУ и построения других малошумящих, низкотемпературных и радиационно-стойких аналоговых микросхем по техпроцессу CJFet ОАО «Интеграл» (г. Минск), а также комплементарному биполярно-полевому технологическому процессу АО «НПП «Пульсар» (г. Москва).

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент RU 2710296, fig.3, 2019 г.

2. Патент RU 2684473. 2019 г.

3. Патент RU 2688225 (по з. 785), 2019 г.

4. Патент RU 2679970, 2019 г.

5. Патент RU 2712414, 2020 г.

6. Патент RU 2624585, 2017 г.

7. Патент RU 2712416, 2020 г.

8. Патент RU 2710930, 2020 г.

9. Патент US 4.004.245, 1977 г.

10. Dvornikov O. V., Dziatlau V. L., Prokopenko N. N., Petrosiants K. O., Kozhukhov N. V. and Tchekhovski V. A. The accounting of the simultaneous exposure of the low temperatures and the penetrating radiation at the circuit simulation of the BiJFET analog interfaces of the sensors // 2017 International Siberian Conference on Control and Communications (SIBCON), Astana, 2017, pp. 1-6. DOI: 10.1109/SIBCON.2017.7998507.

11. Petrosyants K.O., Ismail-zade M.R., Sambursky L. M., Dvornikov O.V., Lvov B. G. and Kharitonov I. A. Automation of parameter extraction procedure for Si JFET SPICE model in the −200…+110°C temperature range // 2018 Moscow Workshop on Electronic and Networking Technologies (MWENT), Moscow, 2018, pp. 1-5. DOI: 10.1109/MWENT.2018.8337212.

12. Создание низкотемпературных аналоговых ИС для обработки импульсных сигналов датчиков. Часть 2 / О. Дворников, В. Чеховский, В. Дятлов, Н. Прокопенко // Современная электроника, 2015, № 5. С. 24-28.

13. Dvornikov O.V., Prokopenko N.N., Butyrlagin N.V. and Pakhomov I.V. The differential and differential difference operational amplifiers of sensor systems based on bipolar-field technological process AGAMC // 2016 International Siberian Conference on Control and Communications (SIBCON), Moscow, 2016, pp. 1-6. DOI: 10.1109/SIBCON.2016.7491792.

14. Parametric Optimization Subsystem in LTspice Environment of Analog Microcircuits for Operation at Low Temperatures / M. V. Liashov, N. N. Prokopenko, A. A. Ignashin, O. V. Dvornikov and A. A. Zhuk // Proceedings of 17th IEEE East-West Design & Test Symposium (EWDTS-2019), September 13-16, 2019, Batumi, Georgia, pp. 356-359. doi: 10.1109/EWDTS.2019.8884446.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДИФФЕРЕНЦИАЛЬНЫЙ КАСКАД НА КОМПЛЕМЕНТАРНЫХ JFET ПОЛЕВЫХ ТРАНЗИСТОРАХ С ПОВЫШЕННЫМ ОСЛАБЛЕНИЕМ ВХОДНОГО СИНФАЗНОГО СИГНАЛА | 2019 |

|

RU2710296C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ КАСКАД КЛАССА АВ НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ С УПРАВЛЯЮЩИМ P-N ПЕРЕХОДОМ ДЛЯ РАБОТЫ В УСЛОВИЯХ НИЗКИХ ТЕМПЕРАТУР | 2019 |

|

RU2710847C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ КАСКАД КЛАССА АВ С НЕЛИНЕЙНЫМ ПАРАЛЛЕЛЬНЫМ КАНАЛОМ | 2020 |

|

RU2740306C1 |

| ВХОДНОЙ ДИФФЕРЕНЦИАЛЬНЫЙ КАСКАД НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ ДЛЯ РАБОТЫ ПРИ НИЗКИХ ТЕМПЕРАТУРАХ | 2019 |

|

RU2712416C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ КАСКАД НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ | 2022 |

|

RU2786941C1 |

| ПРЕОБРАЗОВАТЕЛЬ ДИФФЕРЕНЦИАЛЬНОГО ВХОДНОГО НАПРЯЖЕНИЯ С ПАРАФАЗНЫМИ ТОКОВЫМИ ВЫХОДАМИ НА ОСНОВЕ КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРОВ С УПРАВЛЯЮЩИМ P-N ПЕРЕХОДОМ | 2020 |

|

RU2724975C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ КАСКАД НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ С УПРАВЛЯЮЩИМ P-N ПЕРЕХОДОМ КЛАССА АВ С ИЗМЕНЯЕМЫМ НАПРЯЖЕНИЕМ ОГРАНИЧЕНИЯ ПРОХОДНОЙ ХАРАКТЕРИСТИКИ | 2019 |

|

RU2712414C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ КЛАССА АВ НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ С УПРАВЛЯЮЩИМ P-N ПЕРЕХОДОМ | 2020 |

|

RU2736549C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРОВ С УПРАВЛЯЮЩИМ P-N ПЕРЕХОДОМ | 2020 |

|

RU2736412C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ С ПОВЫШЕННОЙ СТАБИЛЬНОСТЬЮ СТАТИЧЕСКОГО РЕЖИМА | 2019 |

|

RU2710930C1 |

Изобретение относится к области радиотехники. Технический результат: высокая стабильность статического режима входных транзисторов при воздействии отрицательных температур. Для этого предложен дифференциальный каскад на комплементарных полевых транзисторах, в котором третий (10) и четвертый (11) токовые выходы устройства согласованы с первой (8) шиной источника питания, затвор третьего (12) вспомогательного полевого транзистора подключен к объединенными истокам третьего (5) и четвертого (6) входных полевых транзисторов, а его сток согласован со второй (16) шиной источника питания, исток второго (14) вспомогательного полевого транзистора связан с объединенными истоками третьего (5) и четвертого (6) входных полевых транзисторов через второй (15) вспомогательный резистор, затвор второго (14) вспомогательного полевого транзистора соединен с объединенными истоками первого (3) и второго (4) входных полевых транзисторов, а сток второго (14) вспомогательного полевого транзистора подключен ко второй (16) шине источника питания. 7 ил.

Дифференциальный каскад на комплементарных полевых транзисторах с повышенной температурной стабильностью статического режима, содержащий первый (1) и второй (2) входы устройства, первый (3) и второй (4) входные полевые транзисторы с управляющим p-n переходом, истоки которых объединены, третий (5) и четвертый (6) входные полевые транзисторы с управляющим p-n переходом, истоки которых соединены друг с другом, причем затвор первого (3) и затвор третьего (5) входных полевых транзисторов с управляющим p-n переходом подключены к первому (1) входу устройства, а затвор второго (4) и затвор четвертого (6) входных полевых транзисторов с управляющим p-n переходом связаны со вторым (2) входом устройства, первый (7) токовый выход устройства, согласованный с первой (8) шиной источника питания и подключенный к стоку первого (3) входного полевого транзистора с управляющим p-n переходом, второй (9) токовый выход устройства, согласованный с первой (8) шиной источника питания и подключенный к стоку второго (4) входного полевого транзистора с управляющим p-n переходом, третий (10) токовый выход устройства, связанный со стоком третьего (5) входного полевого транзистора с управляющим p-n переходом, четвертый (11) токовый выход устройства, связанный со стоком четвертого (6) входного полевого транзистора с управляющим p-n переходом, третий (12) вспомогательный полевой транзистор с управляющим p-n переходом, исток которого соединен с объединенными истоками первого (3) и второго (4) входных полевых транзисторов с управляющим p-n переходом через первый (13) вспомогательный резистор, второй (14) вспомогательный полевой транзистор с управляющим p-n переходом и второй (15) вспомогательный резистор, отличающийся тем, что третий (10) и четвертый (11) токовые выходы устройства согласованы с первой (8) шиной источника питания, затвор третьего (12) вспомогательного полевого транзистора с управляющим p-n переходом подключен к объединенными истокам третьего (5) и четвертого (6) входных полевых транзисторов с управляющим p-n переходом, а его сток согласован со второй (16) шиной источника питания, исток второго (14) вспомогательного полевого транзистора с управляющим p-n переходом связан с объединенными истоками третьего (5) и четвертого (6) входных полевых транзисторов с управляющим p-n переходом через второй (15) вспомогательный резистор, затвор второго (14) вспомогательного полевого транзистора с управляющим p-n переходом соединен с объединенными истоками первого (3) и второго (4) входных полевых транзисторов с управляющим p-n переходом, а сток второго (14) вспомогательного полевого транзистора с управляющим p-n переходом подключен ко второй (16) шине источника питания.

| ДИФФЕРЕНЦИАЛЬНЫЙ КАСКАД НА КОМПЛЕМЕНТАРНЫХ JFET ПОЛЕВЫХ ТРАНЗИСТОРАХ С ПОВЫШЕННЫМ ОСЛАБЛЕНИЕМ ВХОДНОГО СИНФАЗНОГО СИГНАЛА | 2019 |

|

RU2710296C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ КАСКАД КЛАССА АВ НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ С УПРАВЛЯЮЩИМ P-N ПЕРЕХОДОМ ДЛЯ РАБОТЫ В УСЛОВИЯХ НИЗКИХ ТЕМПЕРАТУР | 2019 |

|

RU2710847C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ КАСКАД НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ С УПРАВЛЯЮЩИМ P-N ПЕРЕХОДОМ КЛАССА АВ С ИЗМЕНЯЕМЫМ НАПРЯЖЕНИЕМ ОГРАНИЧЕНИЯ ПРОХОДНОЙ ХАРАКТЕРИСТИКИ | 2019 |

|

RU2712414C1 |

| US 5444413 A1, 22.08.1995. | |||

Авторы

Даты

2021-04-21—Публикация

2020-10-20—Подача