Изобретение относится к вычислительной технике и может быть использовано в высоконадежных вычислительных и управляющих системах различного назначения.

Известны схемы резервированных триггеров и устройств (патент РФ №2308147 МПК Н03К23/00; G06F11/18; H05К10/00; G06M3/00, опубл. 10.10.2007г.), патент США № 8049529 МПК Н03К19/003; H03К19/00; H03К3/02 опубл. 01.11.2011г.), в которых используется мажоритарный принцип. Для повышения сбоеустойчивости хранение данных осуществляется в трех независимых копиях запоминающих устройств (триггеров). Состояние на выходе схемы определяется мажоритарным элементом. Использование резервирования позволяет повысить устойчивость к сбоям, однако не предусматривает возможность тестирования резервных каналов на этапе контроля работоспособности изготовленной микросхемы.

Наиболее близким по совокупности существенных признаков к заявляемому решению является схема устройства для контроля и резервирования информационной системы (патент РФ № 2453079 МПК Н05К10/00; G06F11/20, опубл. 10.06.2012). Блок реконфигурации и три блока сравнения осуществляют анализ состояний выходов трех резервируемых блоков, что позволяет обеспечить проверку на сбой при появлении нескольких отказов. Результат проверки позволяет судить о работоспособности каналов и определяет состояния выходов схемы «Норма», «Снижение надежности» и «Одноканальная конфигурация». Устройство позволяет обеспечить повышение сбоеустойчивости. Однако занимает большую площадь и обладает невысоким быстродействием, обусловленным избыточной функциональностью. К недостаткам данной схемы можно отнести невозможность тестирования группы аналогичных схем в силу большого количества независимых управляющих сигналов.

Технической проблемой является обеспечение возможности тестирования микросхемы и определения исправности резервирующих элементов при сохранении повышенной стойкости к эффектам одиночных сбоев.

Технический результат заключается в обеспечении возможности определения исправности всех трёх резервирующих элементов модуля во время тестирования изготовленной микросхемы, при сохранении сбоеустойчивости схемы к одиночным отказам.

Для достижения вышеуказанных технических результатов Резервированный модуль с функцией тестирования выполнен содержащим три параллельно включенных триггера, входы данных триггеров через входной буфер соединены с информационным входом устройства, входы синхронизации триггеров соединены через буфер синхронизации с входом синхронизации устройства, дополнительные входы управления триггеров соединены через буфер управления с дополнительным входом управления, вход инициализации первого триггера соединен через буфер инициализации с входом инициализации; один вход первого элемента 2И-НЕ соединен с первым входом тестирования устройства, второй вход первого элемента 2И-НЕ соединен с инверсным выходом буфера инициализации, выход первого элемента 2И-НЕ соединен с входом инициализации второго триггера; один вход второго элемента 2И-НЕ соединен с вторым входом тестирования устройства, второй вход первого элемента 2И-НЕ соединен с инверсным выходом буфера инициализации, выход второго элемента 2И-НЕ соединен с входом инициализации третьего триггера; выходы триггеров соединены с входами мажоритарного элемента, выход которого соединен через выходной буфер с прямым и инверсным выходами устройства.

Технический результат достигается тем, что в схему триггера с троичным мажорированием добавлены два элемента тестирования с отдельными управляющими сигналами для проверки микросхемы после изготовления. Тестирование происходит путём поочерёдного отключения резервирующих элементов и сравнения результатов моделирования с эталонными выходными реакциями.

Изобретение поясняется следующими материалами:

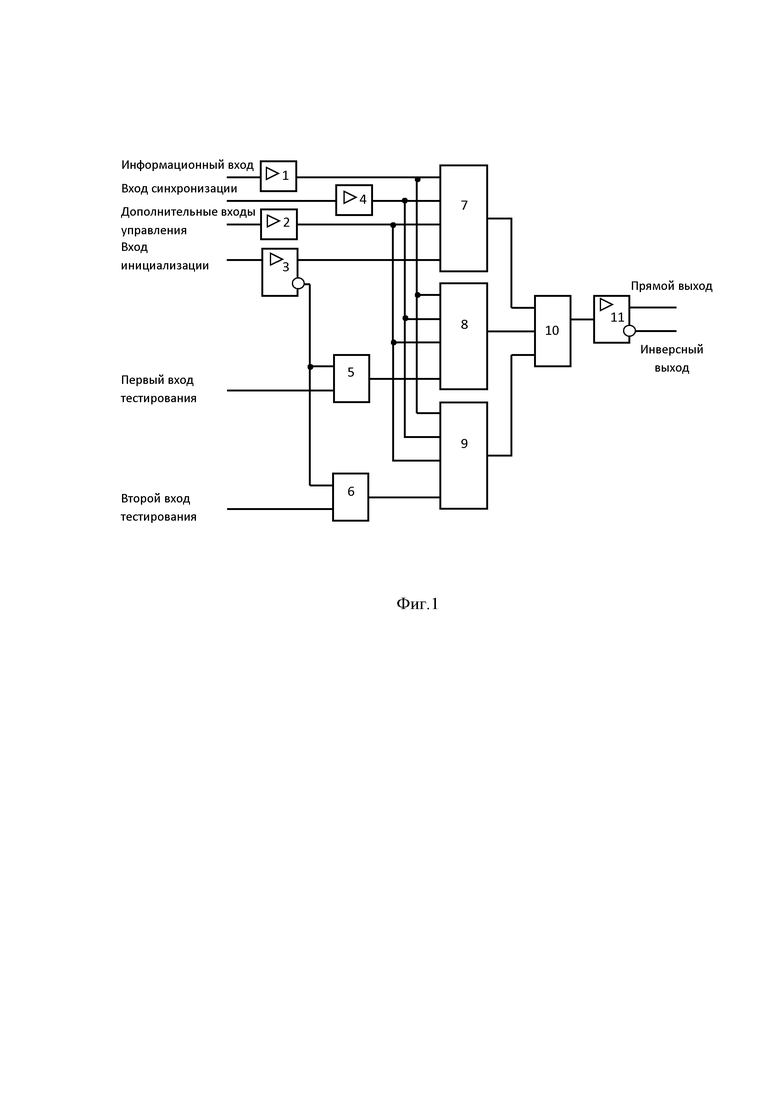

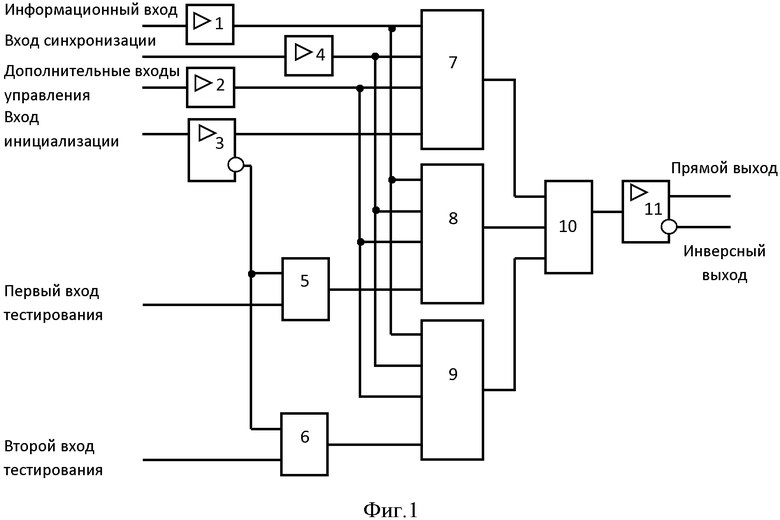

Фиг.1 - функциональная схема резервированного модуля с функцией тестирования.

Устройство является резервированным модулем (троированным триггером) с информационным входом, входом синхронизации, входом инициализации и содержит параллельно соединенные триггеры (7), (8), (9). Входы данных триггеров (7), (8), (9) объединены через входной буфер (1) с информационным входом устройства, входы синхронизации триггеров (7), (8), (9) через буфер (4) объединены с входным сигналом синхронизации устройства. Дополнительные входы управления триггеров (7), (8), (9) через буфер (2) связаны с соответствующими им входными сигналами. При этом вход инициализации триггера (7) соединен с прямым выходом буфера (3), подключенного к входу инициализации устройства. Элемент 2И-НЕ (5) связан с первым входом тестирования устройства, инверсным выходом буфера инициализации (3) и входом инициализации триггера (8). Элемент 2И-НЕ (6) связан с вторым входом тестирования устройства, инверсным выходом буфера инициализации (3) и входом инициализации третьего триггера (9). Выходы триггеров (7), (8), (9) соединены с входами мажоритарного элемента (10), подключенного к буферу (11), выходы которого являются прямым и инверсным выходами троированного триггера.

Активный логический уровень сигнала инициализации устройства, независимо от состояния других входных сигналов, устанавливает выходной сигнал резервированного триггера в низкий логический уровень, инверсный выходной сигнал – в высокий логический уровень.

При неактивном логическом уровне на входе инициализации устройства и при высоком логическом уровне на входах тестирования состояние выходных сигналов модуля соответствует логике работы триггеров (7), (8) и (9).

При неактивном логическом уровне на входе инициализации устройства, высоком уровне первого сигнала тестирования и при низком уровне второго сигнала тестирования, поступающего на вход элемента 2И-НЕ (6) на его выходе устанавливается высокий логический уровень. При этом независимо от того, в каком состоянии находился триггер (9), на его прямом выходе формируется низкий логический уровень, а на инверсном выходе – высокий логический уровень. При поступлении сигнала синхронизации состояние триггеров (7) и (8) определяется информационным входом. Выходной сигнал мажоритарного элемента (10) определяется состоянием выходных сигналов триггеров (7) и (8) при фиксированном состоянии триггера (9). Таким образом, в случае отличия результатов моделирования от эталонных диаграмм определяется сбой на выходах триггеров (7) и (8).

При неактивном логическом уровне на входе инициализации устройства, высоком логическом уровне второго сигнала тестирования, низком уровне первого сигнала тестирования, поступающего на вход элемента 2И-НЕ (5) на его выходе устанавливается высокий логический уровень. При этом независимо от того, в каком состоянии находился триггер (8), на его прямом выходе формируется низкий логический уровень, а на инверсном выходе – высокий логический уровень. При поступлении сигнала синхронизации состояние триггеров (7) и (9) определяется информационным входом. Выходной сигнал мажоритарного элемента (10) определяется состоянием выходов триггеров (7) и (9) при фиксированном состоянии триггера (8). В случае отличия результатов моделирования от эталонных диаграмм определяется сбой на выходах триггеров (7) и (9).

Таким образом, наличие сигналов тестирования позволяет обнаружить сбой на всех трех триггерах в составе устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Резервированный счетчик импульсов | 1983 |

|

SU1125790A1 |

| СБОЕУСТОЙЧИВАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2013 |

|

RU2541839C2 |

| Резервированная система | 1982 |

|

SU1101827A1 |

| ТРЕХЭЛЕМЕНТНОЕ МАЖОРИТАРНОЕ УСТРОЙСТВО РЕЗЕРВИРОВАНИЯ | 2007 |

|

RU2347264C2 |

| Резервированный делитель частоты импульсов | 1977 |

|

SU698130A2 |

| Резервированный счетчик импульсов | 1981 |

|

SU987815A1 |

| Устройство для оперативной реконфигурации резервированной системы | 1990 |

|

SU1727125A1 |

| Устройство для синхронизации резервированного делителя частоты | 1981 |

|

SU1001104A1 |

| Устройство контроля и управления реконфигурацией резервированной системы | 1989 |

|

SU1691990A1 |

| Мажоритарно-резервированный интерфейс памяти | 1990 |

|

SU1751766A1 |

Изобретение относится к вычислительной технике и может быть использовано в вычислительных и управляющих системах различного назначения. Технический результат заключается в обеспечении возможности определения исправности всех трёх резервирующих элементов модуля во время тестирования изготовленной микросхемы, при сохранении сбоеустойчивости схемы к одиночным отказам. Резервированный модуль с функцией тестирования содержит три параллельно включенных триггера, входы данных триггеров через входной буфер соединены с информационным входом устройства, входы синхронизации триггеров соединены через буфер синхронизации с входом синхронизации устройства, дополнительные входы управления триггеров соединены через буфер управления с дополнительным входом управления, вход инициализации первого триггера соединен через буфер инициализации с входом инициализации; один вход первого элемента 2И-НЕ соединен с первым входом тестирования устройства, второй вход первого элемента 2И-НЕ соединен с инверсным выходом буфера инициализации, выход первого элемента 2И-НЕ соединен с входом инициализации второго триггера; один вход второго элемента 2И-НЕ соединен с вторым входом тестирования устройства, второй вход первого элемента 2И-НЕ соединен с инверсным выходом буфера инициализации, выход второго элемента 2И-НЕ соединен с входом инициализации третьего триггера; выходы триггеров соединены с входами мажоритарного элемента, выход которого соединен через выходной буфер с прямым и инверсным выходами устройства. 1 ил.

Резервированный модуль с функцией тестирования, содержащий три параллельно включенных триггера, входы данных триггеров через входной буфер соединены с информационным входом устройства, входы синхронизации триггеров соединены через буфер синхронизации с входом синхронизации устройства, дополнительные входы управления триггеров соединены через буфер управления с дополнительным входом управления, вход инициализации первого триггера соединен через буфер инициализации с входом инициализации; один вход первого элемента 2И-НЕ соединен с первым входом тестирования устройства, второй вход первого элемента 2И-НЕ соединен с инверсным выходом буфера инициализации, выход первого элемента 2И-НЕ соединен с входом инициализации второго триггера; один вход второго элемента 2И-НЕ соединен с вторым входом тестирования устройства, второй вход первого элемента 2И-НЕ соединен с инверсным выходом буфера инициализации, выход второго элемента 2И-НЕ соединен с входом инициализации третьего триггера; выходы триггеров соединены с входами мажоритарного элемента, выход которого соединен через выходной буфер с прямым и инверсным выходами устройства.

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ И РЕЗЕРВИРОВАНИЯ ИНФОРМАЦИОННОЙ СИСТЕМЫ | 2010 |

|

RU2453079C2 |

| РЕЗЕРВИРОВАННЫЙ RS-ТРИГГЕР | 2006 |

|

RU2308147C1 |

| УСТРОЙСТВО МАЖОРИТАРНОГО РЕЗЕРВИРОВАНИЯ (ВАРИАНТЫ) | 2005 |

|

RU2298823C2 |

| US 8049529 B2, 01.11.2011. | |||

Авторы

Даты

2020-01-17—Публикация

2019-02-25—Подача