Изобретение относится .к вычислительной технике и может быть использовано для построения высоконадежных отказоустойчивых вычислительных комплексов

Известной устройство для обработки информации , Стр. 34, содержащее три компьютерных модуля, три модуля интерфейса, схему мажоритарного выбора, схему распределения и панель согласования имеет высокий показатель надежности.

Недостатком его являются большие затраты ресурсов для достижения этого показателя и низкая ресурсоемкость.

Устройство для обработки информации 2, содержащее три процессора, буферное ЗУ, блок сравнения, блок мажоритарного решения, блок мажоритарной обработки, блок коммутации и выходной блок имеет высокий показатель надежности.

Недостатком его являются большие затраты ресурсов для достижения высоких показателей надежности и низкая рссурсоемкость.

Устройство для обработки информации 3, содержащее три канала, е каждый из

которых входит резервируемый вычислительный блок, блок контроля, триггер цикла, коммутатор режима работы, два элемента связи и блок ввода-вывода имеет высокий показатель надежности.

Недостатком его являются большие затраты ресурсов для достижения высоких показателей надежности, низкая ресурсо- емкость и достаточно ограниченное общее время функционирования.

Устройство для обработки информации 4 прототип, содержащее три резервируемых вычислительных канала, группу мажоритарных элементов, первую-третью схемы сравнения, первый-шестой триггеры, пер- вый-третий элементы НЕ, первый элемент задержки, первый-шестой элементы И и элемент ИЛИ, причем информационные выходы первого-третьего резервируемых вычислительных каналов подключены к соответствующим входам мажоритарных элементов группы, а контрольные выходы схем сравнения, выходы мажоритарных элементов группы являются информационным

VJ

сл

00

о

о

выходом устройства, выходы четвертого- шестого элемента И подключены к счетным входам одноименных триггеров, выход которого является выходом управления записью системы, подключенным к одноименным входам всех резервируемых вычислительных каналов, синхровходам первого-третьего триггеров и через последовательно соединенные четвертый элемент НЕ и элемент задержки ко входам прерывания по таймеру всех вычислительных каналов, первый-тре- тий входы установки резерва устройства подключены ко входам установки, соответственно, первого-третьего триггеров, выходы которых подключены ко входам включения одноименных резервируемых вычислительных каналов и через одноименные элементы НЕ к первым входам, соответственно, четвертом-шестого элементов И. вторые входы шестого, пятого и четвертого элементов И подключены к выходам первого, второго и третьего элементов НЕ, соответственно, а третьи входы к выходам, соответственно, третьей, второй и первой схем сравнения, выходы четвертого-шесто- го триггеров подключены к первым входам первого и второго элементов И, второму входу второго и первому входу третьего элементов И и ко вторым входам третьего и первого элементов И, соответственно, а выходы первого-третьего элементов И соединены с входами отключения одноименных резервируемых каналов имеет высокие показатели надежности и ресурсосмкости.

Недостатком устройства является низкая помехоустойчивость к случайным и еди- ничным сбоям в работе, ведущих к подключению резервного канала и переводу сбойного, но работающего канала в режим ремонта, что приводит к снижению ресурсоемкости и надежности устройства,

Цель изобретения - повышение надежности и помехоустойчивости устройства от случайных и единичных сбоев в работе за счет создания режима повторного запуска сбойного канала, с записью в его память контекста задачи завершенного интервала. Подключение резервного канала производится только после использования нескольких попыток запуска сбойного канала, что снижает использование резервного канала и повышает помехоустойчивость и надежность устройства.

Поставленная цель достигается тем, что в известное устройство для обработки информации, содержащее три резервируемых вычислительных канала, группу мажоритарных элементов, первую-третью схемы сравнения, первый-шестой триггеры, первый-третий элементы НЕ, первыйшестой элементы И, первый элемент задержки и элемент ИЛИ, причем информационные выходы первого-третьего резервируемых вычислительных каналов подключены к соответствующим входам мажоритарных элементов группы, а контрольные выходы подсоединены попарно к соответствующим входам первой-третьей схем сравнения, выходы мажоритарных элементов группы являются информационным выходом устройства, выходы четвертого-шестого элементов И подключены к счетным входам одноименных триггеров, выход элемента ИЛИ подсоединен к выходам управления

записью всех резервируемых вычислительных каналов, первый-третий входы установки резерва устройства подключены к входам установки, соответственно, первого-третьего триггеров, выходы которых подключены

ко входам включения одноименных резервируемых вычислительных каналов и через одноименные элементы НЕ к первым входам, соответственно, четвертого-шестого элементов И, вторые входы шестого, четвертого и пятого элементов И подключены к выходам, соответственно, первого, второго и третьего элементов НЕ, а третьи входы - к выходам, соответственно, третьей, первой и второй схем сравнения, выход четвертого

триггера подключен к первым входам первого и второго элементов И, выход пятого триггера подключен к первому входу третьего элемента И, введены три блока сопряжения, четвертая-шестая схемы сравнения,

шесть элементов И-ИЛИ-НЕ, счетчик сбоев, первый-третий элементы ИЛИ-НЕ, седь- мой-шестнадцатый элементы И, второй и третий элементы задержки, седьмой-дёвя- тый триггера и три элемента И-НЕ, выход

четырнадцатого элемента И соединен с первыми входами десятого и пятнадцатого элементов И и со входом сброса счетчика сбоев, счетный вход которого соединен с выходом элемента ИЛИ, прямой выход переполнения счетчика сбоев соединен с первыми вхо- дами первого...шестого элементов И-ИЛИ-НЕ, выходы которых соединены с первыми и вторыми входами одиннадцато- го-тринадцатого элементов И, выходы которых соединены со входами отключения соответственно первого-третьего резервируемых вычислительных каналов и с соответствующими входами четырнадцатого элемента И, первые входы четвертой-шес5 той схем сравнения соединены с выходами мажоритарных элементов группы, а вторые входы с контрольными выходами соответственно, первого-третьего резервируемых каналов, первые группы информационных

входов-выходов которых соединены с первыми группами информационных входов- выходов первого-третьего блоков сопряжения, соответственно, вторые группы информационных входов-выходов которых соединены со вторыми группами информационных входов-выходов первого-третьего резервируемых вычислительных каналов, соответственно, выход сброса первого резервируемого вычислительного канала соединен со вторыми входами третьего и шестого элементов И-ИЛИ-НЕ, второй вход первого элемента И-ИЛИ-НЕ соединен с выходом сброса второго резервируемого вычислительного канала и со вторым входом пятого элемента И-ИЛИ-НЕ, второй вход второго элемента И-И Л И-ИЕ соединен с выходом сброса третьего резервируемого вычислительного канала и со вторым входом четвертого элемента И-ИЛИ-НЕ, третий и четвертый входы которого соединены с выходом восьмого элемента И и с первым входом третьего элемента ИЛИ-НЕ, второй вход которого соединен с выходом девятого элемента И и с третьим и четвертым входами второго элемента И-ИЛИ-НЕ, второй вход первого элемента И соединен с выходом первого элемента задержки и с первым входом седьмого элемента И, выход которого соединен с первым входом седьмого элемента И, выход которого соединен с первым входом первого элемента ИЛ И-Н Е и с трет ь- им и четвертым входами шестого элемента И-ИЛИ-НЕ, третий и четвертый входы третьего элемента И-ИЛИ-НЕ соединены с выходом первого элемента И и со вторым входом первого элемента ИЛИ-НЕ, выход которого соединен со входом синхронизации седьмого триггера, выход которого соединен со входом прерывания первого резервируемого вычислительного канала, выход пуска которого соединен со вторым входом десятого элемента И, третий вход которого соединен с выходом пуска второго резервируемого вычислительного канала, вход прерывания которого соединен с выходом восьмого триггера, четвертый вход десятого элемента И соединен с выходом пуска третьего резервируемого вычислительного канала, вход прерывания которого соединен с выходом девятого триггера, вход синхронизации которого соединен с выходом третьего элемента ИЛИ-НЕ, вход синхронизации восьмого триггера соединен с выходом второго элемента ИЛ И-Н Е, первый вход которого соединен с выходом второго элемента И и с третьим и четвертым входами первого элемента И-ИЛИ-НЕ, третий и четвертый входы пятого элемента И-ИЛИ- НЕ соединены со вторым входом второго элемента ИЛИ-НЕ и с выходом третьего элемента И, второй вход которого соединен с выходом второго элемента задержки и со вторым входом второго элемента И, первый вход элемента ИЛИ соединен с выходом

четвертого триггера, второй вход с выходом шестого триггера и со вторым входом седьмого элемента И и с первым входом девятого элемента И, второй вход которого соединен с выходом третьего элемента за0 держки и с первым входом восьмого элемента И, второй вход которого соединен с выходом пятого триггера и с третьим входом элемента ИЛИ, пятый вход десятого элемента И соединен с выходом первого элемента

5 И-НЕ. первый вход которого соединен с первым входом второго элемента И-НЁ, с выходом четвертой схемы сравнения и со входом первого элемента задержки, шестой вход десятого элемента И соединен с выхо0 дом второго элемента И-НЕ, второй вход которого соединен со входом второго элемента задержки, с первым входом третьего элемента И-НЕ и с выходом пятой схемы сравнения, выход шестой схемы сравнения

5 соединен со входом третьего элемента задержки и с вторыми входами первого и третьего элемента И-НЕ, третьи входы которых соединены с третьим входом второго элемента И-НЕ и с выходом элемента ИЛИ,

0 выход третьего элемента И-НЕ соединен с седьмым входом десятого элемента И, выход которого соединен со входами сброса четвертого-шестого триггеров, второй вход пятнадцатого элемента И соединен с

5 инверсным выходом переполнения счетчика сбоев, а выход со входами сброса первого-третьего триггеров, выходы подтверждения прерывания первого-третьего резервируемых вычислительных каналов соединены

0 с соответствующими входами шестнадцатого элемента И, выход которого соединен со входами сброса седьмого-девятого триггеров.

Сопоставительный анализ с прототи5 псм позволяет сделать вывод, что заявляемое устройство отличается наличием трех блоков сопряжения ЭВМ, трех схем сравнения, шести элементов И-ИЛИ-НЕ, счетчика сбоев, трех элементов ИЛИ-НЕ, десяти эле0 ментов И, двух элементов задержки, трех триггеров и трех элементов И-НЕ и новой организацией связей. Таким образом заявляемое устройство соответствует критерию изобретения новизна.

5 Устройство обладает существенными отличиями, так как содержит новую совокупность признаков, которая придает ему новые свойства, заключающиеся в повышении помехоустойчивости и надежности за счет создания режима повторного запуска сбойного канала с записью в его память контекста задачи завершенного интервала. Подключение резервного канала производится только после использования нескольких попыток запуска сбойного канала, что снижает использование резервного канала и повышает надежность устройства.

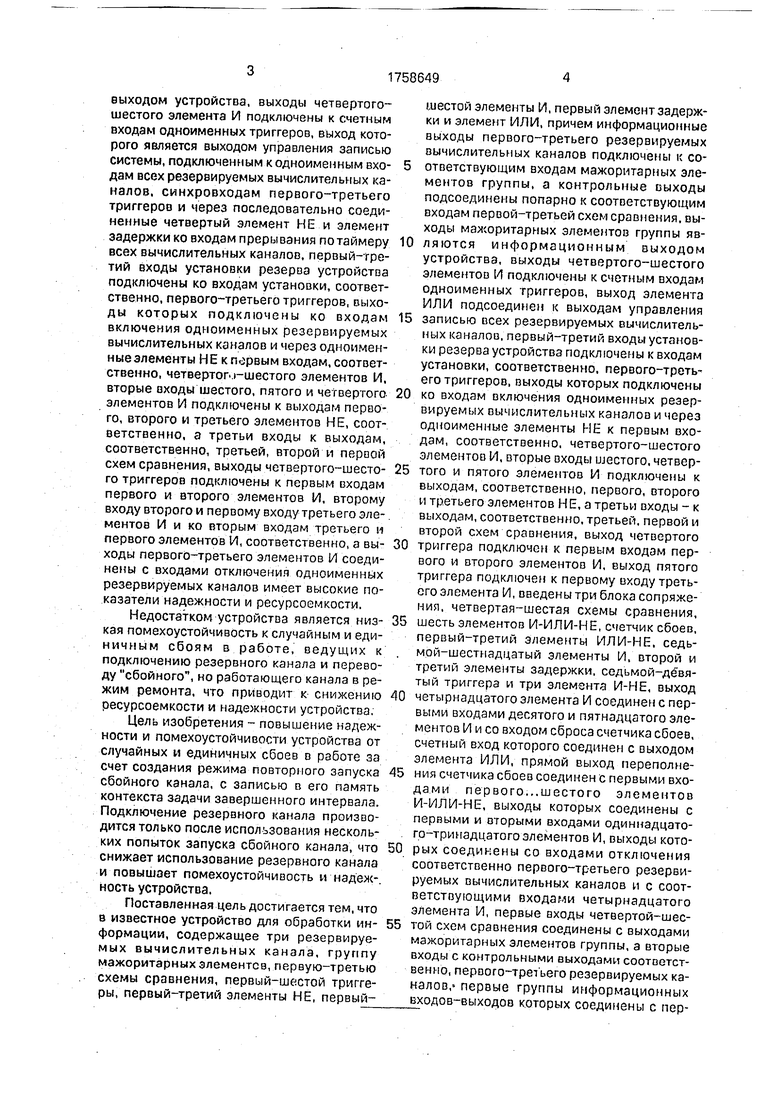

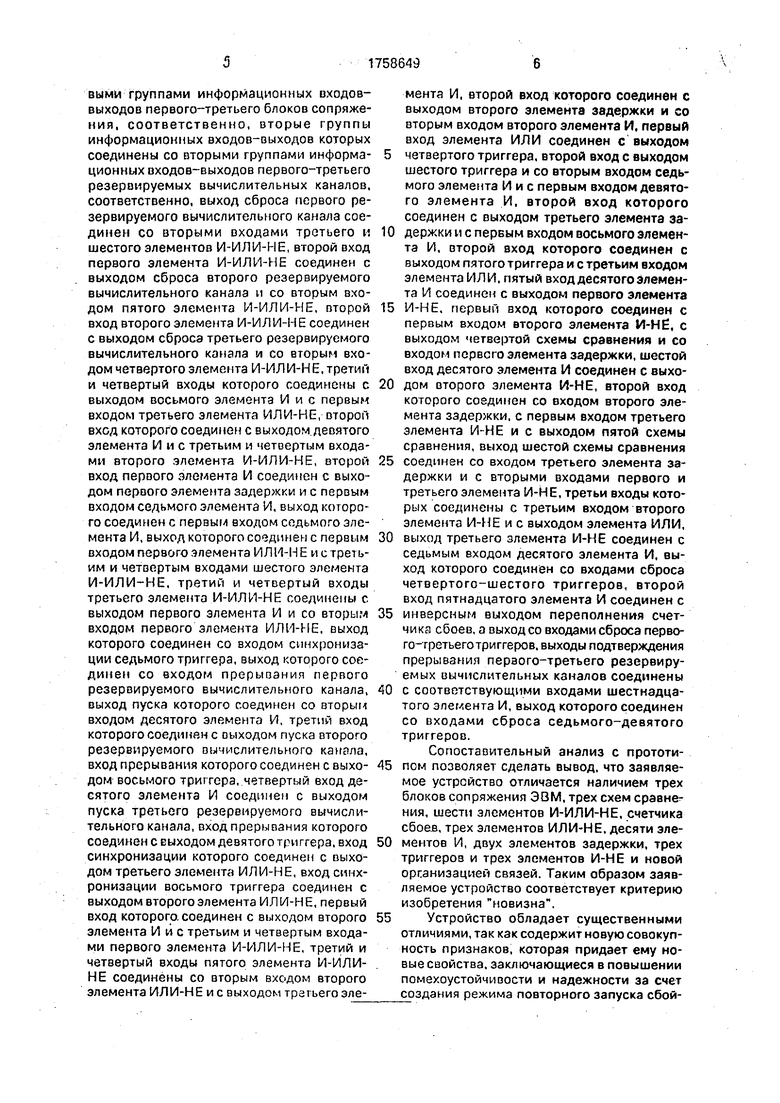

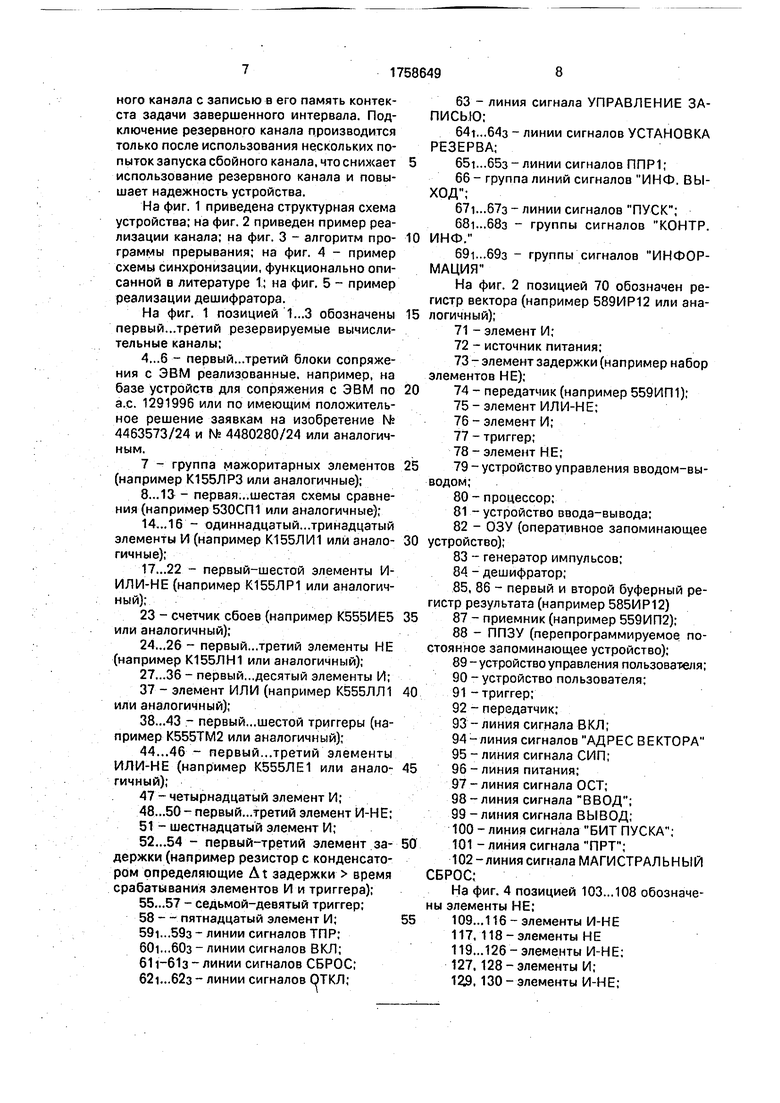

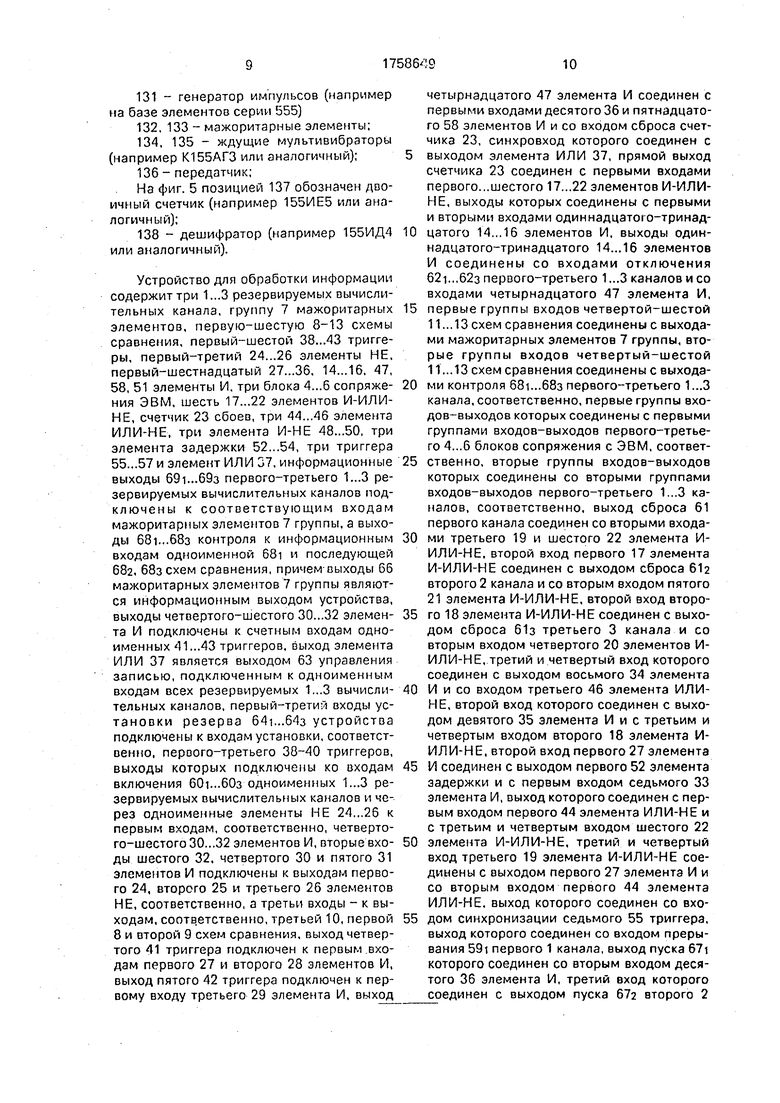

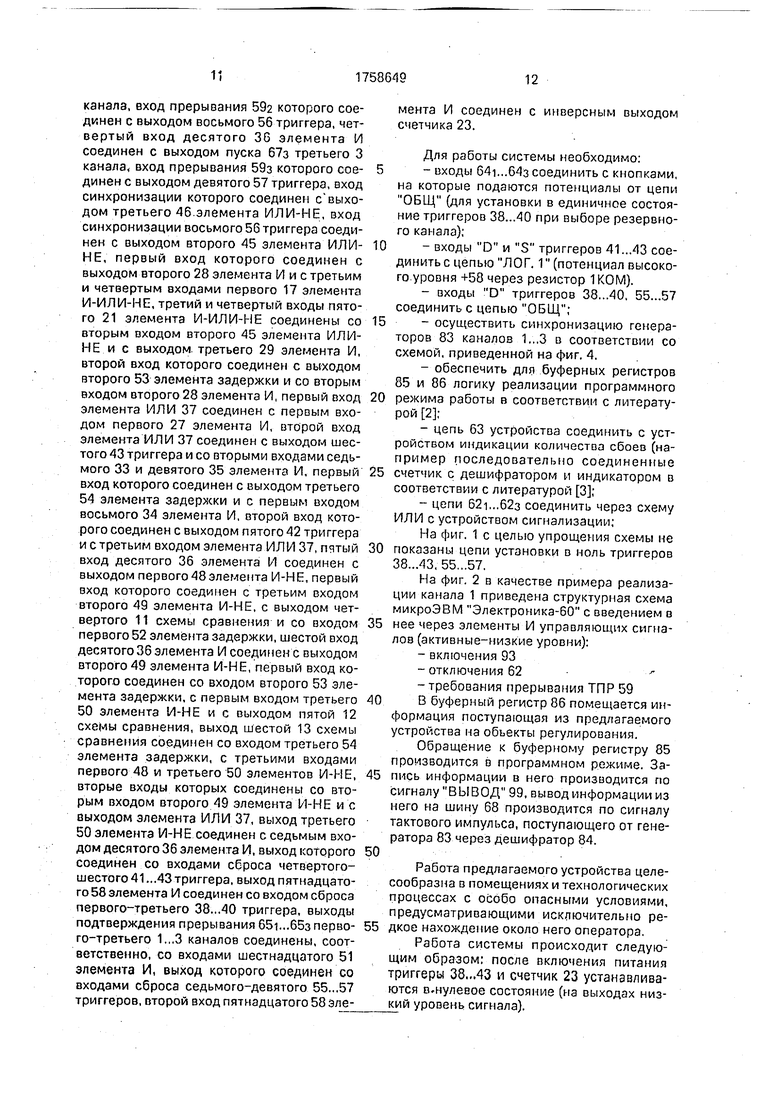

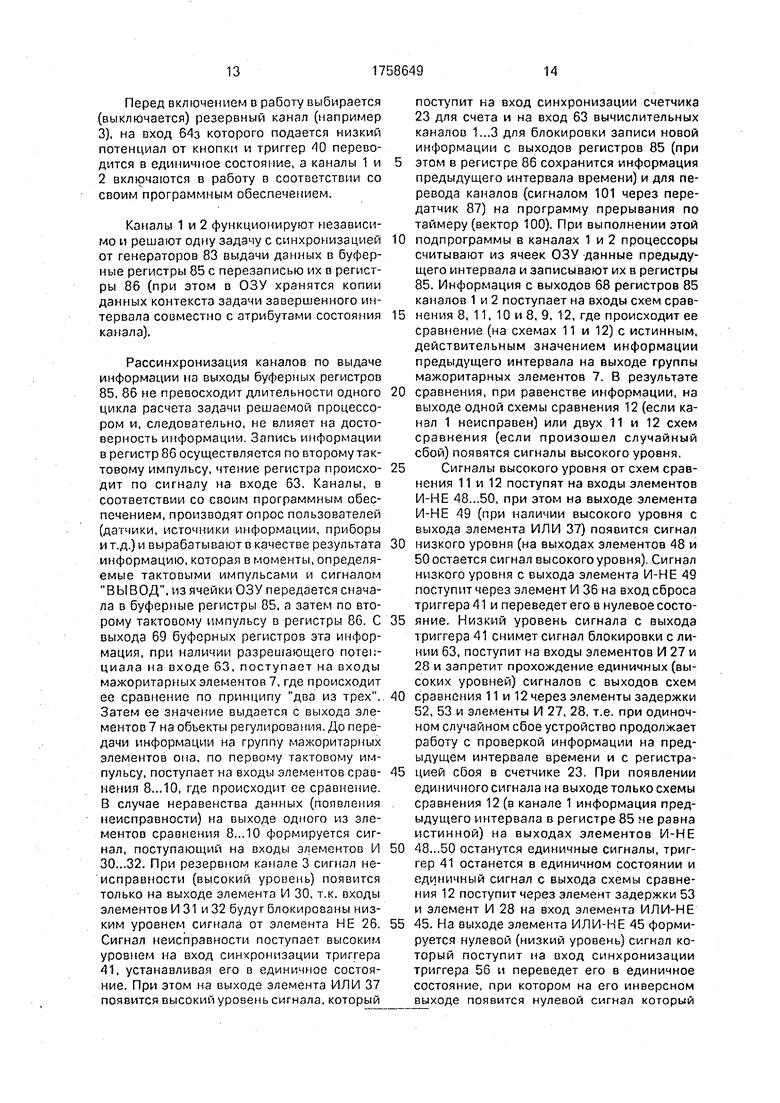

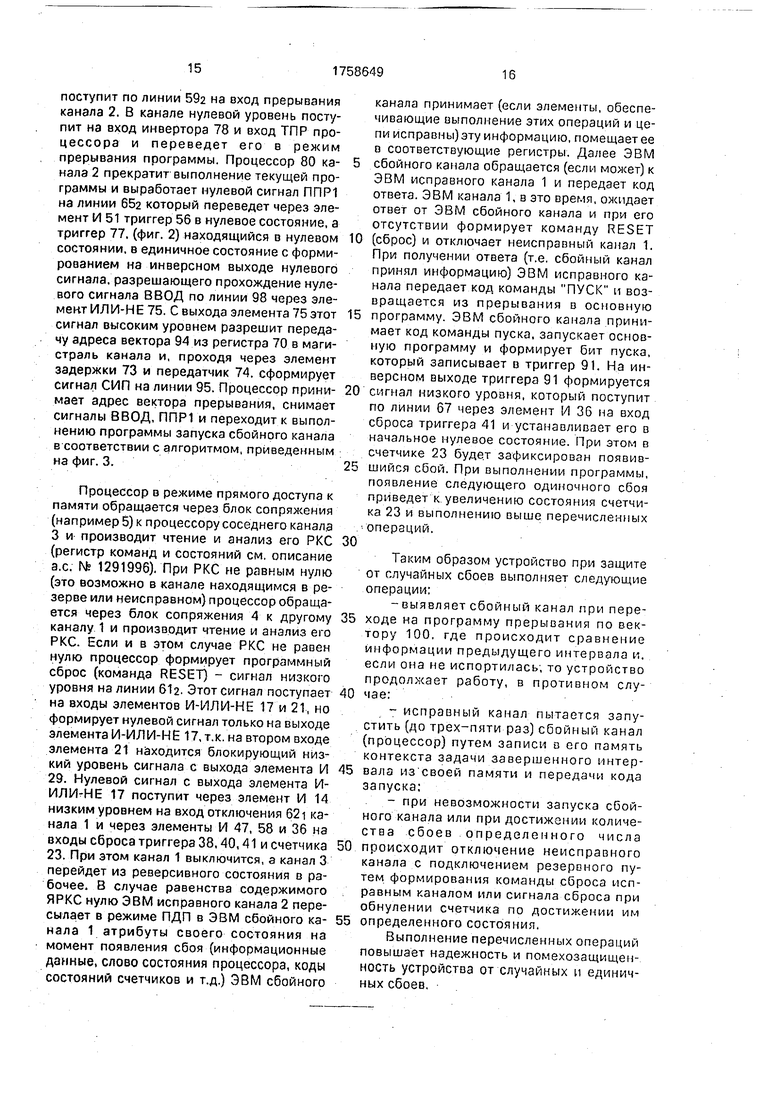

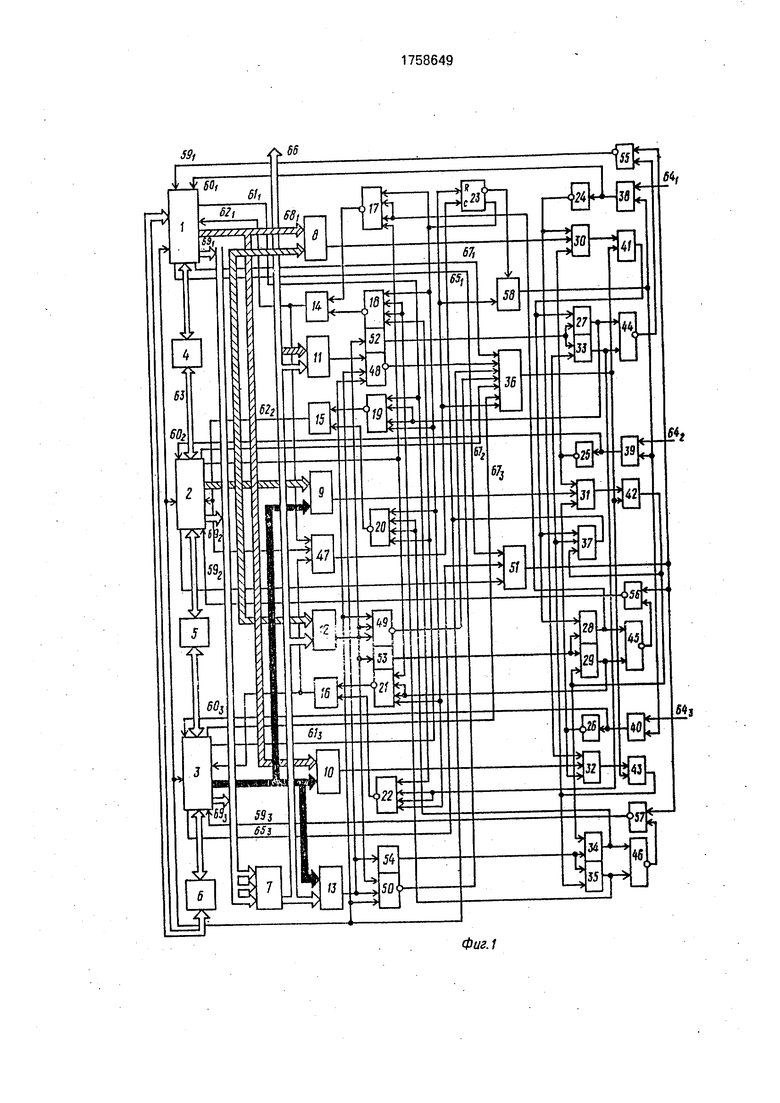

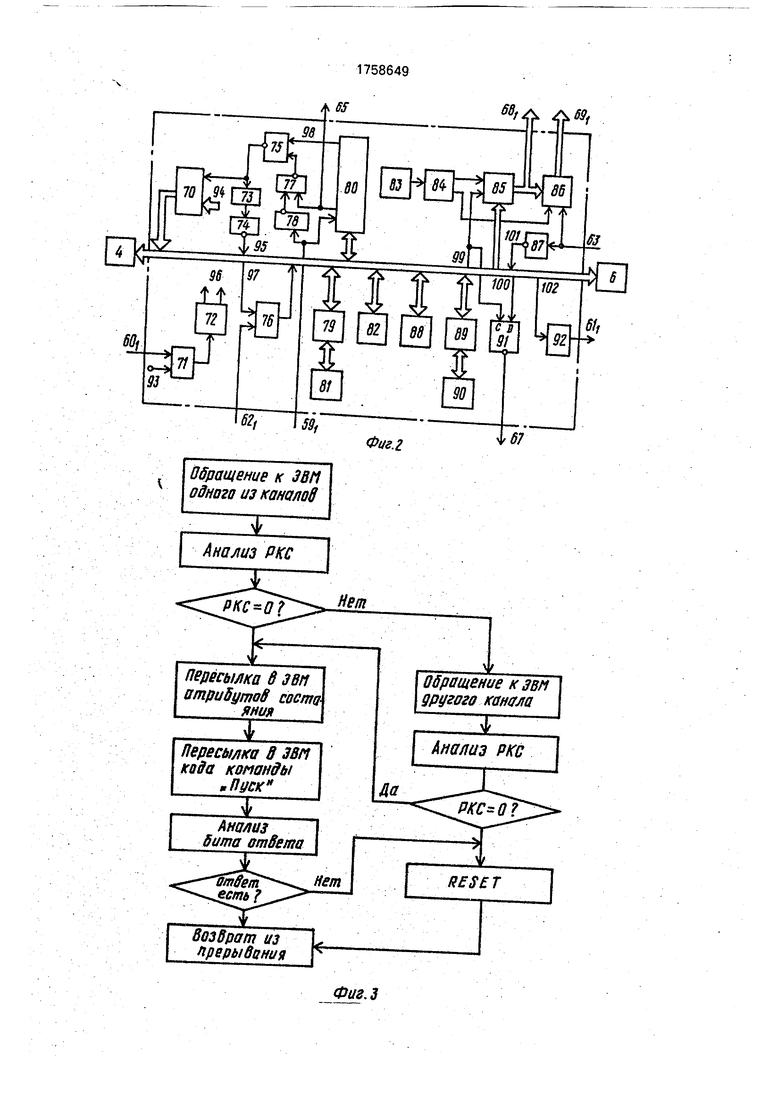

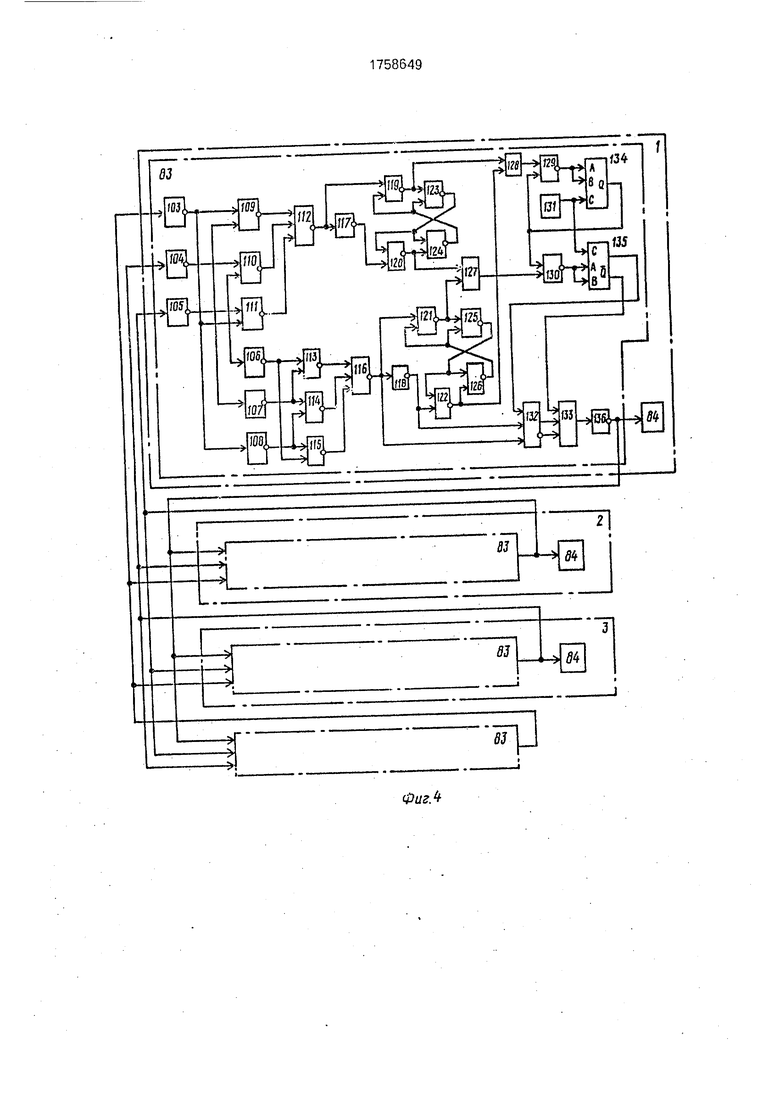

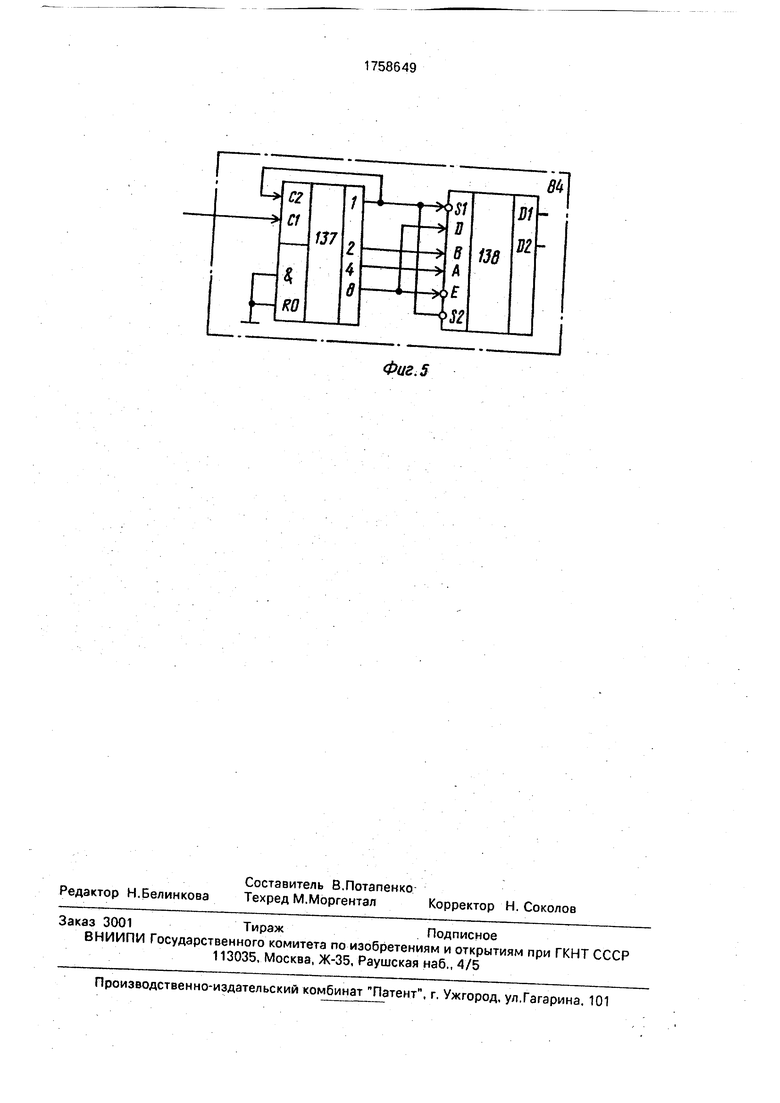

На фиг. 1 приведена структурная схема устройства; на фиг. 2 приведен пример реализации канала; на фиг. 3 - алгоритм программы прерывания; на фиг. 4 - пример схемы синхронизации, функционально описанной в литературе 1; на фиг. 5 - пример реализации дешифратора.

На фиг. 1 позицией 1...3 обозначены первый.„третий резервируемые вычислительные каналы;

4...6 - первый...третий блоки сопряжения с ЭВМ реализованные, например, на базе устройств для сопряжения с ЭВМ по а.с. 1291996 или по имеющим положительное решение заявкам на изобретение № 4463573/24 и № 4480280/24 или аналогичным.

7 - группа мажоритарных элементов (например К155ЛРЗ или аналогичные);

8... 13 - первая...шестая схемы сравнения (например 530СП1 или аналогичные);

14...16 - одиннадцатый...тринадцатый элементы И (например К155ЛИ1 или аналогичные);

17...22 - первый-шестой элементы И- ИЛИ-НЕ (например К155ЛР1 или аналогичный);

23 - счетчик сбоев (например К555ИЕ5 или аналогичный);

24...26 - первый...третий элементы НЕ (например К155ЛН1 или аналогичный);

27...36 - первый...десятый элементы И;

37 - элемент ИЛИ (например К555ЛЛ1 или аналогичный);

38...43 - первый...шестой триггеры (например К555ТМ2 или аналогичный);

44...46 - первый...третий элементы ИЛИ-НЕ (например К555ЛЕ1 или аналогичный);

47 - четырнадцатый элемент И;

48...50-первый...третий элемент И-НЕ;

51 - шестнадцатый элемент И;

52...54 - первый-третий элемент задержки (например резистор с конденсатором определяющие At задержки время срабатывания элементов И и триггера);

55...57 - седьмой-девятый триггер;

58 - пятнадцатый элемент И;

591...59з - линии сигналов ТПР;

601,..60з линии сигналов ВКЛ;

611-61з - линии сигналов СБРОС;

621...62з - линии сигналов ОТКЛ;

63 - линия сигнала УПРАВЛЕНИЕ ЗАПИСЬЮ;

64т...64з - линии сигналов УСТАНОВКА РЕЗЕРВА; 651...65з линии сигналов ППР1;

66 - группа линий сигналов ИНФ. ВЫХОД ;

671...67з - линии сигналов

681...68з - группы сигналов КОНТР. ИНФ.

69-|...69з - группы сигналов ИНФОРМАЦИЯ

На фиг. 2 позицией 70 обозначен регистр вектора (например 589ИР12 или ана- логичный);

71- элемент И;

72- источник питания;

73- элемент задержки (например набор элементов НЕ);

74 - передатчик (например 559ИП1);

75- элемент ИЛИ-НЕ;

76- элемент И;

77- триггер;

78- элемент НЕ;

79-устройствоуправления вводом-выводом;

80- процессор;

81-устройство ввода-вывода;

82- ОЗУ (оперативное запоминающее устройство);

83- генератор импульсов;

84- дешифратор;

85, 86 - первый и второй буферный регистр результата (например 585ИР12) 87-приемник (например 559ИП2);

88 - ППЗУ (перепрограммируемое постоянное запоминающее устройство);

89-устройствоуправления пользователя; 90 - устройство пользователя; 91 -триггер;

92- передатчик;

93- линия сигнала ВКЛ;

94- линия сигналов АДРЕС ВЕКТОРА

95- линия сигнала СИП; 96 - линия питания;

97 - линия сигнала ОСТ; 98-линия сигнала

99- линия сигнала ВЫВОД;

100- линия сигнала БИТ ПУСКА ; 101 - линия сигнала

102 -линия сигнала МАГИСТРАЛЬНЫЙ СБРОС;

На фиг. 4 позицией 103...108 обозначены элементы НЕ; 109...116 - элементы И-НЕ

117, 118 - элементы НЕ

119...126-элементы И-НЕ;

127,128-элементы И;

12J9, 130-элементы И-НЕ;

131 - генератор импульсов (например на базе элементов серии 555)

132. 133 - мажоритарные элементы;

134, 135 - ждущие мультивибраторы (например К155АГЗ или аналогичный);

136- передатчик;

На фиг. 5 позицией 137 обозначен двоичный счетчик (например 155ИЕ5 или аналогичный);

138 - дешифратор (например 155ИД4 или аналогичный).

Устройство для обработки информации содержит три 1...3 резервируемых вычислительных канала, группу 7 мажоритарных элементов, первую-шестую 8-13 схемы сравнения, первый-шеетой 38...43 триггеры, первый-третий 24...26 элементы НЕ, первый-шестнадцатый 27...36. 14...16, 47, 58, 51 элементы И, три блока 4...6 сопряжения ЭВМ, шесть 17...22 элементов И-ИЛИ- НЕ, счетчик 23 сбоев, три 44...46 элемента ИЛИ-НЕ, три элемента И-НЕ 48...50, три элемента задержки 52...54, три триггера 55...57 и элемент ИЛИ 37, информационные выходы 691...69з первого-третьего 1...3 резервируемых вычислительных каналов подключены к соответствующим входам мажоритарных элементов 7 группы, а выходы 681...68з контроля к информационным входам одноименной 68i и последующей 682, 68зсхем сравнения, причем выходы 66 мажоритарных элементов 7 группы являются информационным выходом устройства, выходы четвертого-шестого 30...32 элемента И подключены к счетным входам одноименных 41...43 триггеров, выход элемента ИЛИ 37 является выходом 63 управления записью, подключенным к одноименным входам всех резервируемых 1...3 вычислительных каналов, первый-третим входы установки резерва 641...64з устройства подключены к входам установки, соответственно, первого-третьего 38-40 триггеров, выходы которых подключены ко входам включения 601...60з одноименных 1...3 резервируемых вычислительных каналов и через одноименные элементы НЕ 24...26 к первым входам, соответственно, четвертого-шестого 30...32 элементов И, вторые входы шестого 32. четвертого 30 и пятого 31 элементов И подключены к выходам первого 24, второго 25 и третьего 26 элементов НЕ, соответственно, а третьи входы - к выходам, соответственно, третьей 10, первой 8 и второй 9 схем сравнения, выход четвертого 41 триггера подключен к первым входам первого 27 и второго 28 элементов И, выход пятого 42 триггера подключен к первому входу третьего 29 элемента И, выход

четырнадцатого 47 элемента И соединен с первыми входами десятого 36 и пятнадцатого 58 элементов И и со входом сброса счетчика 23, синхровход которого соединен с

выходом элемента ИЛИ 37, прямой выход счетчика 23 соединен с первыми входами первого...шестого 17...22 элементов И-ИЛИ- НЕ, выходы которых соединены с первыми и вторыми входами одиннадцатого-тринад0 цатого 14...16 элементов И, выходы один- надцатого-тринадцатого 14... 16 элементов И соединены со входами отключения 621,..62з первого-третьего 1...3 каналов и со входами четырнадцатого 47 элемента И,

5 первые группы входов четвертой-шестой 11...13 схем сравнения соединены с выходами мажоритарных элементов 7 группы, вторые группы входов четвертый-шестой 11...13 схем сравнения соединены с выхода0 ми контроля 681...68з первого-третьего 1 ...3 канала, соответственно, первые группы входов-выходов которых соединены с первыми группами входов-выходов первого-третьего 4...6 блоков сопряжения с ЭВМ, соответ5 ственно, вторые группы входов-выходов которых соединены со вторыми группами входов-выходов первого-третьего 1...3 каналов, соответственно, выход сброса 61 первого канала соединен со вторыми входа0 ми третьего 19 и шестого 22 элемента И- ИЛИ-НЕ, второй вход первого 17 элемента И-ИЛИ-НЕ соединен с выходом сброса 612 второго 2 канала и со вторым входом пятого 21 элемента И-ИЛИ-НЕ, второй вход второ5 го 18 элемента И-ИЛИ-НЕ соединен с выходом сброса 61з третьего 3 канала и со вторым входом четвертого 20 элементов И- ИЛИ-НЕ, третий и четвертый вход которого соединен с выходом восьмого 34 элемента

0 И и со входом третьего 46 элемента ИЛИ- НЕ, второй вход которого соединен с выходом девятого 35 элемента И и с третьим и четвертым входом второго 18 элемента И- ИЛ И-НЕ, второй вход первого 27 элемента

5 И соединен с выходом первого 52 элемента задержки и с первым входом седьмого 33 элемента И, выход которого соединен с первым входом первого 44 элемента ИЛИ-НЕ и с третьим и четвертым входом шестого 22

0 элемента И-ИЛИ-НЕ, третий и четвертый вход третьего 19 элемента И-ИЛИ-НЕ соединены с выходом первого 27 элемента И и со вторым входом первого 44 элемента ИЛИ-НЕ, выход которого соединен со вхо5 дом синхронизации седьмого 55 триггера, выход которого соединен со входом прерывания 59i первого 1 канала, выход пуска 67i которого соединен со вторым входом десятого 36 элемента И, третий вход которого соединен с выходом пуска 672 второго 2

канала, вход прерывания 592 которого соединен с выходом восьмого 56 триггера, четвертый вход десятого 3G элемента И соединен с выходом пуска 67з третьего 3 канала, вход прерывания 59з которого соединен с выходом девятого 57 триггера, вход синхронизации которого соединен с выходом третьего 46 элемента ИЛИ-НЕ, вход синхронизации восьмого 56 триггера соединен с выходом второго 45 элемента ИЛИ- НЕ, первый вход которого соединен с выходом второго 28 элемента И и с третьим и четвертым входами первого 17 элемента И-ИЛИ-ИЕ, третий и четвертый входы пятого 21 элемента И-ИЛИ-НЕ соединены со вторым входом второго 45 элемента ИЛИ- НЕ и с выходом третьего 29 элемента И, второй вход которого соединен с выходом второго 53 элемента задержки и со вторым входом второго 28 элемента И, первый вход элемента ИЛИ 37 соединен с первым входом первого 27 элемента И, второй вход элемента ИЛИ 37 соединен с выходом шестого 43 триггера и со вторыми входами седьмого 33 и девятого 35 элемента И, первый вход которого соединен с выходом третьего 54 элемента задержки и с первым входом восьмого 34 элемента И, второй вход которого соединен с выходом пятого 42 триггера и с третьим входом элемента ИЛ И 37, пятый вход десятого 36 элемента И соединен с выходом первого 48элемента И-НЕ, первый вход которого соединен с третьим входом второго 49 элемента И-НЕ, с выходом четвертого 11 схемы сравнения и со входом первого 52 элемента задержки, шестой вход десятого 36 элемента И соединен с выходом второго 49 элемента И-НЕ, первый вход которого соединен со входом второго 53 элемента задержки, с первым входом третьего 50 элемента И-НЕ и с выходом пятой 12 схемы сравнения, выход шестой 13 схемы сравнения соединен со входом третьего 54 элемента задержки, с третьими входами первого 48 и третьего 50 элементов И-НЕ, вторые входы которых соединены со вторым входом второго 49 элемента И-НЕ и с выходом элемента ИЛИ 37, выход третьего 50 элемента И-НЕ соединен с седьмым входом десятого 36 элемента И, выход которого соединен со входами сброса четвертого- шестого 41...43 триггера, выход пятнадцатого 58 элемента И соединен со входом сброса первого-третьего 38...40 триггера, выходы подтверждения прерывания 651...65з первого-третьего 1...3 каналов соединены, соответственно, со входами шестнадцатого 51 элемента И, выход которого соединен со входами сброса седьмого-девятого 55...57 триггеров, второй вход пятнадцатого 58 элемента И соединен с инверсным выходом счетчика 23.

Для работы системы необходимо: - входы 641...64з соединить с кнопками,

на которые подаются потенциалы от цепи ОБЩ (для установки в единичное состояние триггеров 38...40 при выборе резервного канала);

- входы D и S триггеров 41...43 соединить с цепью ЛОГ. 1 (потенциал высокого уровня +58 через резистор 1КОМ).

-входы D триггеров 38...40. 55...57 соединить с цепью

- осуществить синхронизацию генераторов 83 каналов 1...3 в соответствии со схемой, приведенной на фиг. 4.

-обеспечить для буферных регистров 85 и 86 логику реализации программного

режима работы в соответствии с литературой

-цепь 63 устройства соединить с устройством индикации количества сбоев (например последовательно соединенные

счетчик с дешифратором и индикатором в соответствии с литературой

-цепи 62ч,..62з соединить через схему ИЛИ с устройством сигнализации;

На фиг. 1 с целью упрощения схемы не показаны цепи установки в ноль триггеров 38...43, 55...57.

На фиг. 2 в качестве примера реализации канала 1 приведена структурная схема микроЭВМ Электроника-60 с введением в нее через элементы И управляющих сигналов (активные-низкие уровни):

-включения 93

-отключения 62

-требования прерывания ТПР 59

В буферный регистр 86 помещается информация поступающая из предлагаемого устройства на обьекты регулирования.

Обращение к буферному регистру 85 производится в программном режиме. Запись информации в него производится по сигналу ВЫВОД 99, вывод информации из него на шину 68 производится по сигналу тактового импульса, поступающего от генератора 83 через дешифратор 84.

Работа предлагаемого устройства целесообразна в помещениях и технологических процессах с особо опасными условиями, предусматривакж ими исключительно редкое нахождение около него оператора.

Работа системы происходит следующим образом: после включения питания триггеры 38...43 и счетчик 23 устанавливаются в.нулевое состояние (на выходах низкий уровень сигнала).

Перед включением в работу выбирается (выключается) резервный канал (например 3), на вход 64з которого подается низкий потенциал от кнопки и триггер 40 переводится в единичное состояние, а каналы 1 и 2 включаются в работу в соответствии со своим программным обеспечением.

Каналы 1 и 2 функционируют независимо и решают одну задачу с синхронизацией от генераторов 83 выдачи данных в буферные регистры 85 с перезаписью их о регистры 86 (при этом в ОЗУ хранятся копии данных контекста задачи завершенного интервала совместно с атрибутами состояния канала).

Рассинхронизация каналов по выдаче информации на выходы буферных регистров 85, 86 не превосходит длительности одного цикла расчета задачи решаемой процессором и, следовательно, не влияет на достоверность информации. Запись информации в регистр 86 осуществляется по второму тактовому импульсу, чтение регистра происходит по сигналу на входе 63. Каналы, в соответствии со своим программным обеспечением, производят опрос пользователей (датчики, источники информации, приборы и т.д.) и вырабатывают в качестве результата информацию, которая в моменты, определяемые тактовыми импульсами и сигналом ВЫВОД, из ячейки ОЗУ передается сначала в буферные регистры 85. а затем по второму тактовому импульсу в регистры 86. С выхода 69 буферных регистров эта информация, при наличии разрешающего потенциала на входе 63, поступает на входы мажоритарных элементов 7, где происходит ее сравнение по принципу два из трех. Затем ее значение выдается с выхода элементов 7 на объекты регулирования. До передачи информации на группу мажоритарных элементов она, по первому тактовому импульсу, поступает на входы элементов сравнения 8...10, где происходит ее сравнение. В случае неравенства данных (появления неисправности) на выходе одного из элементов сравнения 8... 10 формируется сигнал, поступающий на входы элементов И 30...32. При резервном канале 3 сигнал неисправности (высокий уровень) появится только на выходе элемента И 30. т.к. входы элементов И 31 и 32 будут блокированы низким уровнем сигнала от элемента НЕ 26. Сигнал неисправности поступает высоким уровнем на вход синхронизации триггера 41, устанавливая его в единичное состояние. При этом на выходе элемента ИЛИ 37 появится высокий уровень сигнала, который

поступит кэ вход синхронизации счетчика 23 для счета и на вход 63 вычислительных каналов 1...3 для блокировки записи новой информации с выходов регистров 85 (при

этом в регистре 86 сохранится информация предыдущего интервала времени) и для перевода каналов (сигналом 101 через передатчик 87) на программу прерывания по таймеру (вектор 100). При выполнении этой

0 подпрограммы в каналах 1 и 2 процессоры считывают из ячеек ОЗУ данные предыдущего интервала и записывают их в регистры 85. Информация с выходов 68 регистров 85 каналов 1 и 2 поступает на входы схем срав5 нения 8, 11, 10 и 8, 9, 12, где происходит ее сравнение (на схемах 11 и 12) с истинным, действительным значением информации предыдущего интервала на выходе группы мажоритарных элементов 7. В результате

0 сравнения, при равенстве информации, на выходе одной схемы сравнения 12 (если канал 1 неисправен) или двух 11 и 12 схем сравнения (если произошел случайный сбой) появятся сигналы высокого уровня.

5 Сигналы высокого уровня от схем сравнения 11 и 12 поступят на входы элементов И-НЕ 48...50, при этом на выходе элемента И-НЕ 49 (при наличии высокого уровня с выхода элемента ИЛИ 37) появится сигнал

0 низкого уровня (на выходах элементов 48 и 50 остается сигнал высокого уровня). Сигнал низкого уровня с выхода элемента И-НЕ 49 поступит через элемент И 36 на вход сброса триггера 41 и переведет его в нулевое состо5 яние. Низкий уровень сигнала с выхода триггера 41 снимет сигнал блокировки с линии 63, поступит на входы элементов И 27 и 28 и запретит прохождение единичных (высоких уровней) сигналов с выходов схем

0 сравнения 11 и 12 через элементы задержки 52, 53 и элементы И 27, 28, т.е. при одиночном случайном сбое устройство продолжает работу с проверкой информации на предыдущем интервале времени и с регистра5 цией сбоя в счетчике 23. При появлении единичного сигнала на выходе только схемы сравнения 12 (в канале 1 информация предыдущего интервала в регистре 85 не равна истинной) на выходах элементов И-НЕ

0 48...50 останутся единичные сигналы, триггер 41 останется в единичном состоянии и единичный сигнал с выхода схемы сравнения 12 поступит через элемент задержки 53 и элемент И 28 на вход элемента ИЛИ-НЕ

5 45. На выходе элемента ИЛИ-НЕ 45 формируется нулевой (низкий уровень) сигнал который поступит на вход синхронизации триггера 56 и переведет его в единичное состояние, при котором на его инверсном выходе появится нулевой сигнал который

поступит по линии 592 на вход прерывания канала 2. В канале нулевой уровень поступит на вход инвертора 78 и вход ТПР процессора и переведет его в режим прерывания программы. Процессор 80 канала 2 прекратит выполнение текущей программы и выработает нулевой сигнал ППР1 на линии 652 который переведет через элемент И 51 триггер 56 в нулевое состояние, а триггер 77. (фиг. 2) находящийся в нулевом состоянии, в единичное состояние с формированием на инверсном выходе нулевого сигнала, разрешающего прохождение нулевого сигнала ВВОД по линии 98 через элемент ИЛИ-НЕ 75. С выхода элемента 75 этот сигнал высоким уровнем разрешит передачу адреса вектора 94 из регистра 70 в магистраль канала и, проходя через элемент задержки 73 и передатчик 74. сформирует сигнал СИП на линии 95. Процессор принимает адрес вектора прерывания, снимает сигналы ВВОД, ППР1 и переходит к выполнению программы запуска сбойного канала в соответствии с алгоритмом, приведенным на фиг. 3.

Процессор в режиме прямого доступа к памяти обращается через блок сопряжения (например 5) к процессору соседнего канала 3 и производит чтение и анализ его РКС (регистр команд и состояний см, описание а.с. № 1291996). При РКС не равным нулю (это возможно в канале находящимся в резерве или неисправном} процессор обращается через блок сопряжения 4 к другому каналу 1 и производит чтение и анализ его РКС. Если и в этом случае РКС не равен нулю процессор формирует программный сброс (команда RESET) - сигнал низкого уровня на линии 612. Этот сигнал поступает на входы элементов И-ИЛИ-НЕ 17 и 21, но формирует нулевой сигнал только на выходе элемента И-ЙЛИ-НЕ 17, т.к. на втором входе элемента 21 находится блокирующий низкий уровень сигнала с выхода элемента И 29. Нулевой сигнал с выхода элемента И- ИЛИ-НЕ 17 поступит через элемент И 14 низким уровнем на вход отключения 621 канала 1 и через элементы И 47, 58 и 36 на входы сброса триггера 38,40,41 и счетчика 23. При этом канал 1 выключится, а канал 3 перейдет из реверсивного состояния в рабочее. В случае равенства содержимого ЯРКС нулю ЭВМ исправного канала 2 пересылает в режиме ПДП в ЭВМ сбойного канала 1 атрибуты своего состояния на момент появления сбоя (информационные данные, слово состояния процессора, коды состояний счетчиков и т.д.) ЭВМ сбойного

канала принимает (если элементы, обеспечивающие выполнение этих операций и цепи исправны) эту информацию, помещает ее в соответствующие регистры. Далее ЭВМ

сбойного канала обращается (если может) к ЭВМ исправного канала 1 и передает код ответа. ЭВМ канала 1, в это время, ожидает ответ от ЭВМ сбойного канала и при его отсутствии формирует команду RESET

(сброс) и отключает неисправный канал 1. При получении ответа (т.е. сбойный канал принял информацию) ЭВМ исправного канала передает код команды ПУСК и возвращается из прерывания в основную

программу. ЭВМ сбойного канала принимает код команды пуска, запускает основную программу и формирует бит пуска, который записывает в триггер 91. На инверсном выходе триггера 91 формируется

сигнал низкого уровня, который поступит по линии 67 через элемент И 36 на вход сброса триггера 41 и устанавливает его в начальное нулевое состояние. При этом в счетчике 23 будет зафиксирован появившийся сбой. При выполнении программы, появление следующего одиночного сбоя приведет к увеличению состояния счетчика 23 и выполнению выше перечисленных операций.

Таким образом устройство при защите от случайных сбоев выполняет следующие операции;

-выявляет сбойный канал при пере- ходе на программу прерывания по вектору 100, где происходит сравнение информации предыдущего интервала и. если она не испортилась, то устройство продолжает работу, в противном случае:

-исправный канал пытается запустить (до трех-пяти раз) сбойный канал (процессор) путем записи в его память контекста задачи завершенного интервала из своей памяти и передачи кода запуска;

-при невозможности запуска сбойного канала или при достижении количества сбоев определенного числа

происходит отключение неисправного канала с подключением резервного путем формирования команды сброса исправным каналом или сигнала сброса при обнулении счетчика по достижении им

определенного состояния.

Выполнение перечисленных операций повышает надежность и помехозащищенность устройства от случайных и единичных сбоев.

Формула изобретения

Устройство для обработки информации, содержащее три резервируемых вычислительных канала, группу мажоритарных элементов, первую-третыо схемы сравнения, перпый-шестой триггеры, первый-третмй элементы НЕ, первый-шестой элементы И, первый элемент задержки и элемент ИЛИ, причем информационные выходы первого- третьего резервируемых вычислительных каналов подключены к соответствующим входам мажоритарных элементов группы, а контрольные выходы подсоединены попарно к соответствующим входам первой-третьей схем сравнения, выходы мажоритарных элементов группы являются информационным выходом устройства, выходы четвертого- шестого элементов И подключены к счетным входам одноименных триггеров, выход элемента ИЛИ подсоединен к входам управления записью всех резервируемых вычислительных каналов, первый-третий входы установки резерва устройства подключены к входам установки соответственно первого-третьего триггеров, выходы которых подключены к входам включения одноименных резервируемых вычислительных каналов и через одноименные элементы НЕ - к первым входам соответственно четвертого-шестого элементов И, вторые входы шестого, четвертого и пятого элементов И подключены к выходам соответственно первого, второго и третьего элементов НЕ, а третьи входы - к выходам соответственно третьей, первой и второй схем сравнения, выход четвертого триггера подключен к первым входам первого и второго элементов И, выход пятого триггера подключен к первому входу третьего элемента И, отличающееся тем, что, с целью повышения помехоустойчивости и надежности устройства, в него введены три блока сопряжения, четвертая-шестая схемы сравнения, шесть элементов И-ИЛИ-НЕ, счетчик сбоев, первый-третий элементы ИЛИ-НЕ, седьмой-шестнадцатый элементы И, второй и третий элементы задержки, седьмой-девятый триггеры и три элемента И-НЕ, выход четырнадцатого элемента И соединен с первыми входами десятого и пятнадцатого элементов И и с входом сброса счетчика сбоев, счетный вход которого соединен с выходом элемента ИЛИ, прямой выход переполнения счетчика сбоев соединен с первыми входами первого-шестого элементов И-ИЛИ-НЕ, выходы которых соединены с первыми и вторыми входами один- надцатого-тринадцатого элементов И, выходы которых соединены с входами отключения соответственно первого-третьего резервируемых вычислительных каналов и с соответствующими входами четырнадцатого элемента И, первые входы четвертой-шестой схем сравнения соединены с выходами мажоритарных элементов группы, а вторые входы - с контрольными выходами соответственно первого-третьего резервируемых вычислительных каналов, первые группы

0 информационных входов-выходов которых соединены с первыми группами информационных входов-выходов первого-третьего блоков сопряжения соответственно, вторые группы информационных выходов-входов

5 соединены с вторыми группами информационных входов-выходов второго, третьего и первого резервируемых вычислительных каналов соответственно, выход сброса первого резервируемого вычислительного канала

0 соединен с вторыми входами третьего и шестого элементов И-ИЛИ-НЕ, второй вход первого элемента И-ИЛИ-НЕ соединен с выходом сброса второго резервируемого вычислительного канала и с вторым входом

5 пятого элемента И-ИЛИ-НЕ, второй вход второго элемента И-ИЛИ-НЕ соединен с выходом сброса третьего резервируемого вычислительного канала и с вторым входом четвертого элемента И-ИЛИ-НЕ, третий и

0 четвертый входы которого соединены с выходом восьмого элемента И и с первым входом третьего элемента ИЛИ-НЕ, второй вход которого соединен с выходом девятого элемента И и с третьим и четвертым входа5 ми второго элемента И-ИЛИ-НЕ, второй вход первого элемента И соединен с выходом первого элемента задержки и с первым входом седьмого элемента И, выход которого соединен с первым входом первого эле0 мента ИЛИ-НЕ и с третьим и четвертым входами шестого элемента И-ИЛИ-НЕ, третий и четвертый входы третьего элемента И-ИЛИ-НЕ соединены с выходом первого элемента И и с вторым входом первого эле5 мента ИЛИ-НЕ, выход которого соединен с входом синхронизации седьмого триггера, выход которого соединен с входом прерывания первого резервируемого вычислительного канала, выход пуска которого соединен

0 с вторым входом десятого элемента И. третий вход которого соединен с выходом пуска второго резервируемого вычислительного канала, вход прерывания которого соединен с выходом восьмого триггера, четвертый вход

5 десятого элемента И соединен с выходом пуска третьего резервируемого вычислительного канала, вход прерывания которого соединен с выходом девятого триггера, вход синхронизации которого соединен с выходом третьего элемента ИЛИ-НЕ. вход синхронизации восьмого триггера соединен с выходом второго элемента ИЛИ-НЕ. первый вход которого соединен с выходом второго элемента И и с третьим и четвертым входами первого элемента И-ИЛИ-НЕ, третий и четвертый входы пятого элемента И-ИЛИ- НЕ соединены с вторым входом второго элемента ИЛИ-НЕ и с выходом третьего элемента И. второй вход которого соединен с выходом второго элемента задержки и с вторым входом второго элемента И, первый вход элемента ИЛИ соединен с выходом четвертого триггера, второй вход - с выходом шестого триггера и с вторым входом седьмого элемента И и с первым входом девятого элемента И. второй вход которого соединен с выходом третьего элемента задержки и с первым входом восьмого элемента И, второй вход которого соединен с выходом пятого триггера и с третьим входом элемента ИЛИ, пятый вход десятого элемента И соединен с выходом первого элемента И-НЕ, первый вход которого соединен с первым входом второго элемента И-НЕ, с выходом четвертой схемы сравнения и с входом первого элемента задержки, шестой вход десятого элемента И соединен с выходом второго элемента И-НЕ, второй вход которого соединен с входом второго элемента задержки, с первым входом третьего элемента И-НЕ и с выходом пятой схемы сравнения, выход шестой схемы сравнения соединен с входом третьего элемента задержки и с вторыми входами первого и третьего элементов И-НЕ, третьи

входы которых соединены с третьим входом второго элемента И-НЕ и с выходом элемента ИЛИ, выход третьего элемента И-НЕ соединен с седьмым входом десятого элемента И, выход которого соединен с входами сброса четвертого-шестого триггеров, второй вход пятнадцатого элемента И соединен с инверсным выходом переполнения счетчика сбоев, а выход - с входами сброса первого-третьего триггерое, выходы подтверждения прерывания первого-третьего резервируемых вычислительных каналов соединены с соответствующими входами шестнадцатого элемента И, выход которого соединен

с входами сброса седьмого-девятого триггеров.

/л л/а

&л.г

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство контроля и управления реконфигурацией резервированной системы | 1989 |

|

SU1691990A1 |

| Резервированное устройство | 1981 |

|

SU982006A1 |

| ТРЕХКАНАЛЬНАЯ АСИНХРОННАЯ СИСТЕМА | 1991 |

|

RU2029365C1 |

| Резервированное устройство с перестраиваемой структурой | 1981 |

|

SU993502A1 |

| Мажоритарно-резервированный интерфейс памяти | 1990 |

|

SU1751766A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ КАЧЕСТВА МАГНИТНОГО НОСИТЕЛЯ | 1992 |

|

RU2040050C1 |

| Устройство для контроля | 1981 |

|

SU1072052A1 |

| Устройство для мажоритарного выбора асинхронных сигналов | 1991 |

|

SU1820386A1 |

| Устройство для резервирования и восстановления микропроцессорной системы | 1986 |

|

SU1374235A1 |

| Двухканальное устройство для контроля и восстановления процессорных систем | 1986 |

|

SU1397917A1 |

Использование: в высоконадежных отказоустойчивых вычислительных комплексах для повышения помехоустойчивости. Сущность изобретения: устройство содержит 3 резервируемых вычислительных канала, 1 группу мажоритарных элементов, 6 схем сравнения, 9 триггеров. 3 элемента НЕ, 16 элементов И. 3 элемента задержки, 1 элемент ИЛИ, 6 элементов ИЛИ-НЕ, 1 счетчик сбоев, 3 элемента ИЛИ-НЕ. 3 элемента И-НЕ. 5 ил.

Обращение к ЗВП одного из каналов

пересылка в звп атрибутов состд яния

Пересылка В 38(1 кода команды т Пуск

Анализ бита ответа

Возврат из прерывония

Фиг.З

Обращение кзвм другого каняла

6fr98Sa

G

8 C1

137

i

RO

Bk

т

D1 П

1

Фиг. 5

| Мажоритарно-резервированная управляющая система | 1984 |

|

SU1221658A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для электрической сигнализации | 1918 |

|

SU16A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| принято положительное решение - прототип. | |||

Авторы

Даты

1992-08-30—Публикация

1990-08-14—Подача