7/ЛЩЦ-

Фие1

315382 9

бирования, семь входов переменных, элементы И 18-20, элементы ИЛИ 26 и 27, шины нулевого 21 и единичного 22 логических сигналов. Для достижения поставленной цели в устройство дополнительно введены третий 3 и четвертый 4 коммутаторы 1 из 8, дешифратор 5 с тремя входами и восемью выходами, пороговый элемент 23 k или более из 5, пороговый элемент 2k 3 или более из 5, пороговый элемент 25 2 или более из 5, восьмой 1, девятый 15, десятый 16 и одиннадцатый 17 входы переменных мажоритарного элемента. 3 з.п.ф-лы, k ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Мажоритарный элемент | 1987 |

|

SU1499487A1 |

| Мажоритарный элемент | 1990 |

|

SU1750052A1 |

| Пороговое логическое устройство | 1987 |

|

SU1422400A1 |

| Мажоритарный элемент | 1987 |

|

SU1448406A1 |

| Пороговое логическое устройство | 1987 |

|

SU1499488A1 |

| Пороговое логическое устройство | 1986 |

|

SU1325686A1 |

| Мажоритарный элемент "4 или более из 7 | 1988 |

|

SU1531210A1 |

| Многоканальное устройство для синхронизации | 1980 |

|

SU883888A2 |

| Устройство для воспроизведения цифровых сигналов с носителя магнитной записи | 1986 |

|

SU1352527A1 |

| Устройство для управления графопостроителем | 1980 |

|

SU898471A1 |

Изобретение относится к цифровой автоматике и вычислительной технике и может быть использовано для построения различных устройств обработки дискретной информации. Целью изобретения является расширение функциональных возможностей и области применения путем обеспечения мажоритарных функций "5 или более из 9" и "6 или более из 11". Мажоритарный элемент содержит первый 1 и второй 2 коммутаторы "1 из 8" с входами стробирования, семь входов 7-13 переменных, элементы И 18-20, элементы ИЛИ 26 и 27, шины нулевого 21 и единичного 22 логических сигналов. Для достижения поставленной цели в устройство дополнительно введены третий 3 и четвертый 4 коммутаторы "1 из 8", дешифратор 5 с тремя входами и восемью выходами, пороговый элемент 23 "4 или более из 5", пороговый элемент 24 "3 или более из 5", пороговый элемент 25 "2 или более из 5", восьмой 14, девятый 15, десятый 16 и одиннадцатый 17 входы переменных мажоритарного элемента. 5 ил.

Изобретение относится к цифровой автоматике и вычислительной технике и может быть использовано для построения различных устройств переработки дискретной информации.

Целью изобретения является расширение функциональных возможностей и области применения за счет обеспечения мажоритарных функций 5 или более из 9 и 6 или более из 11.

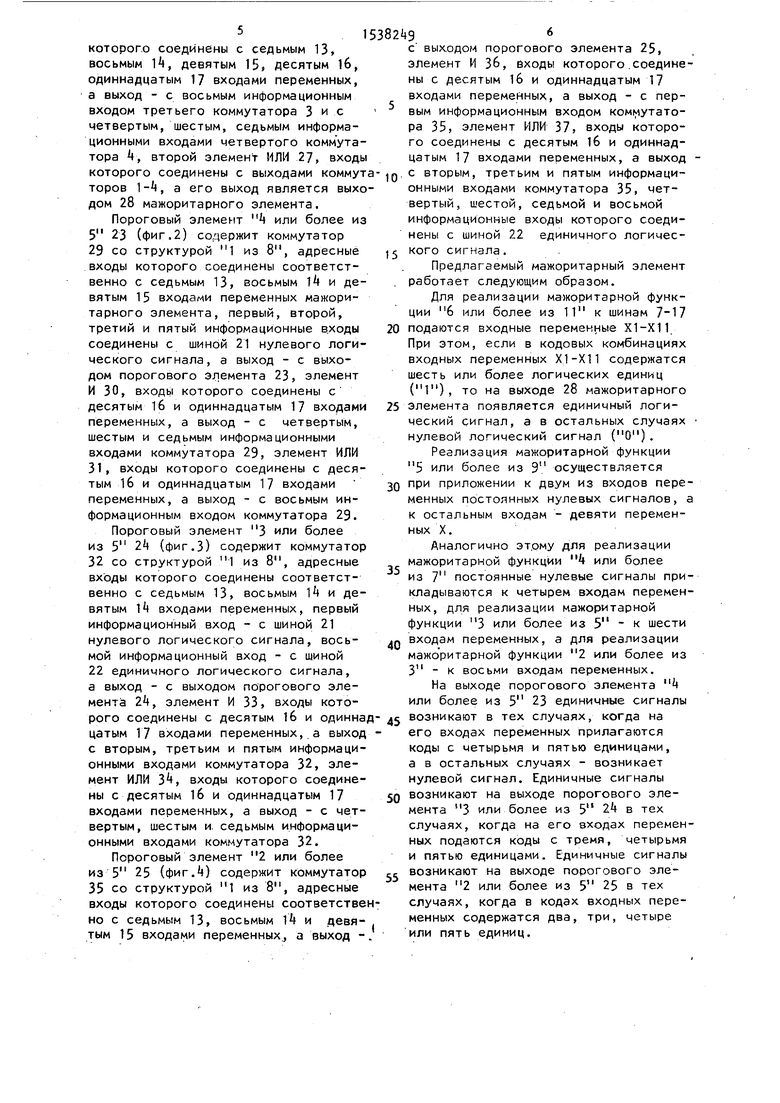

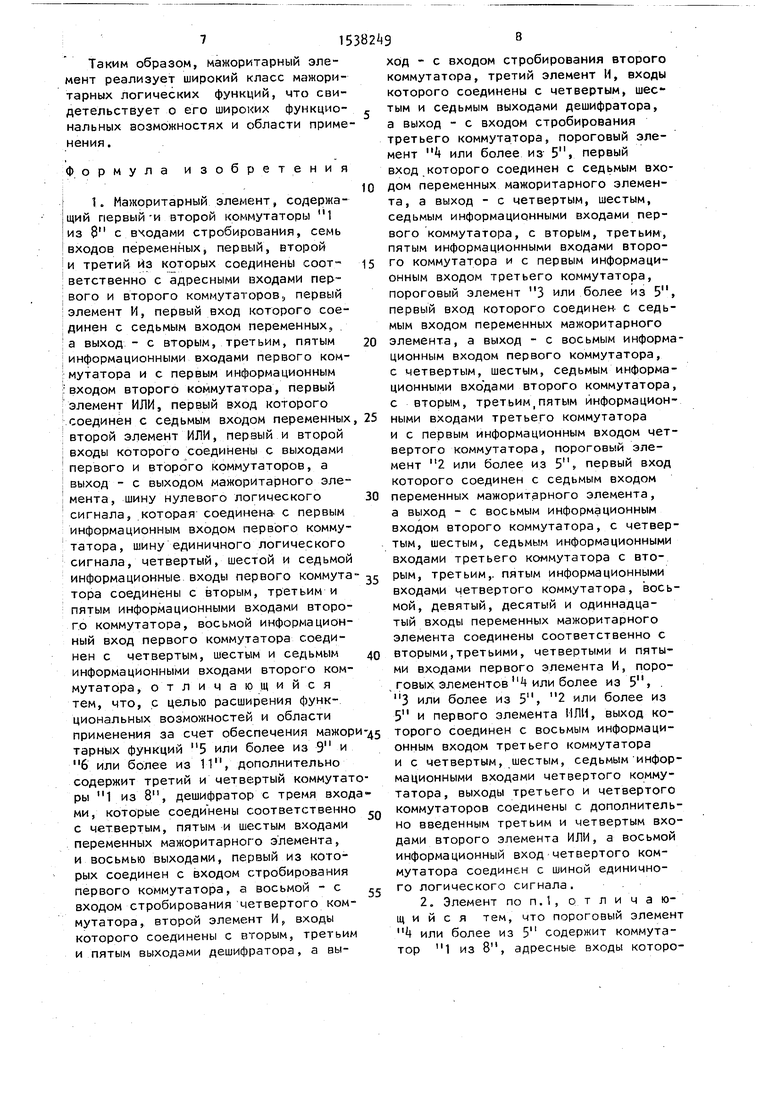

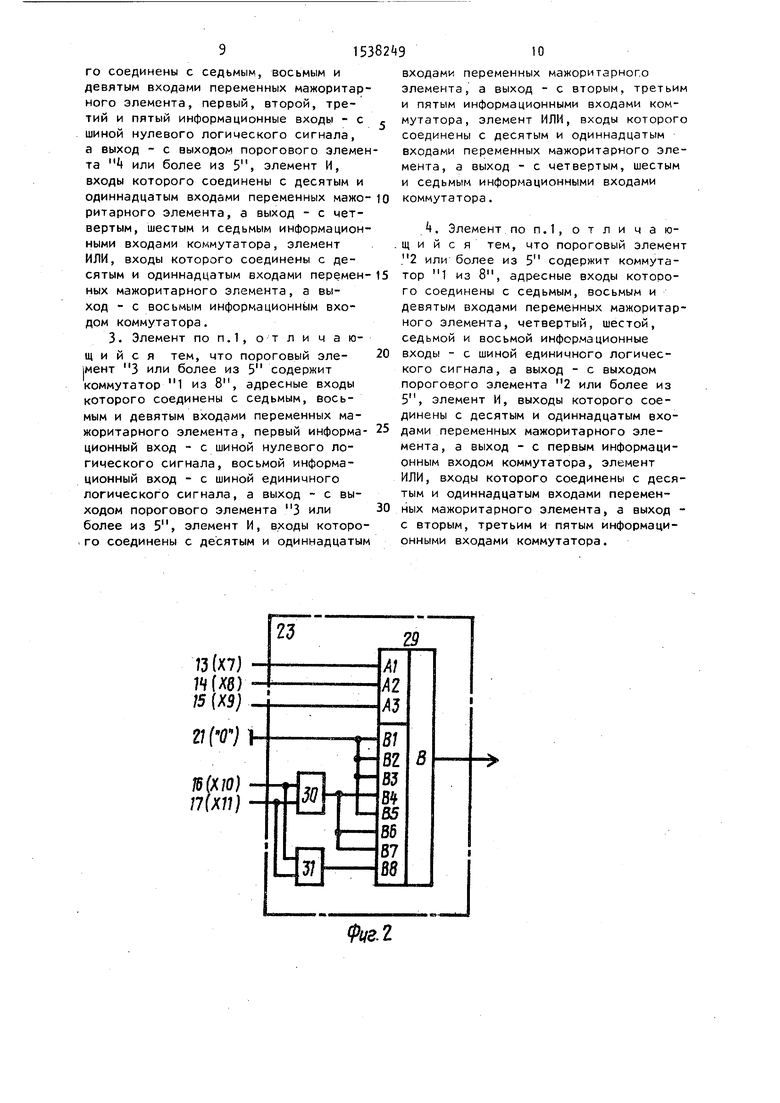

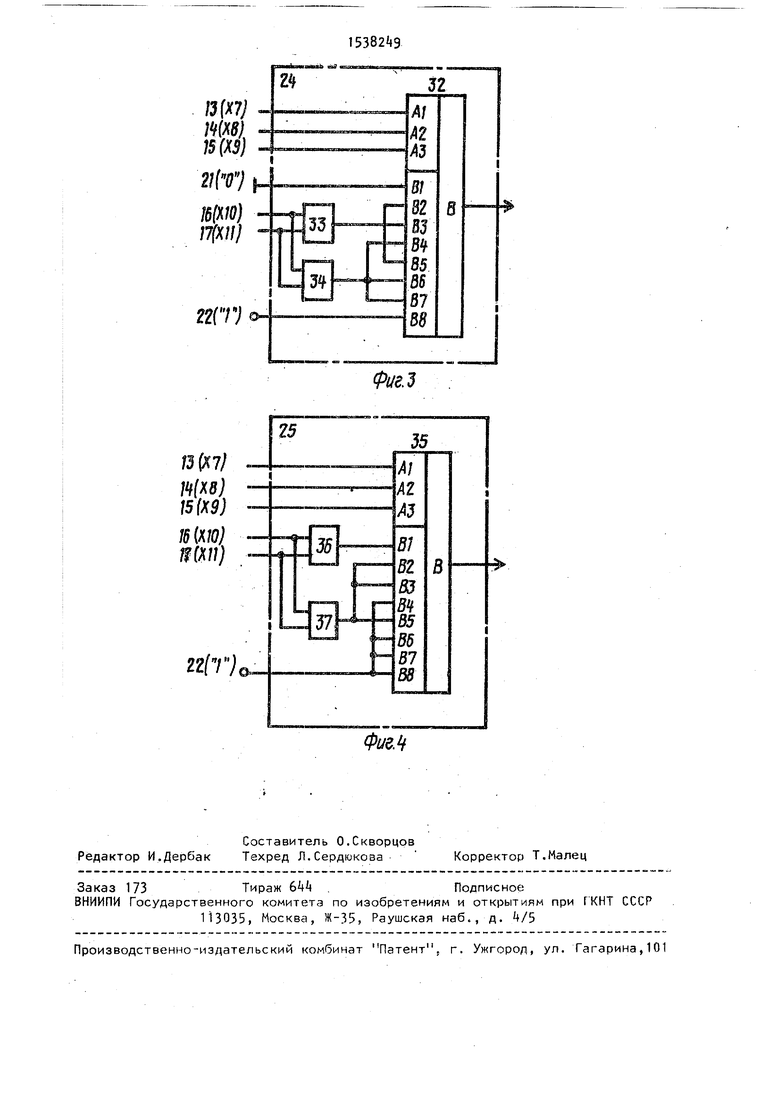

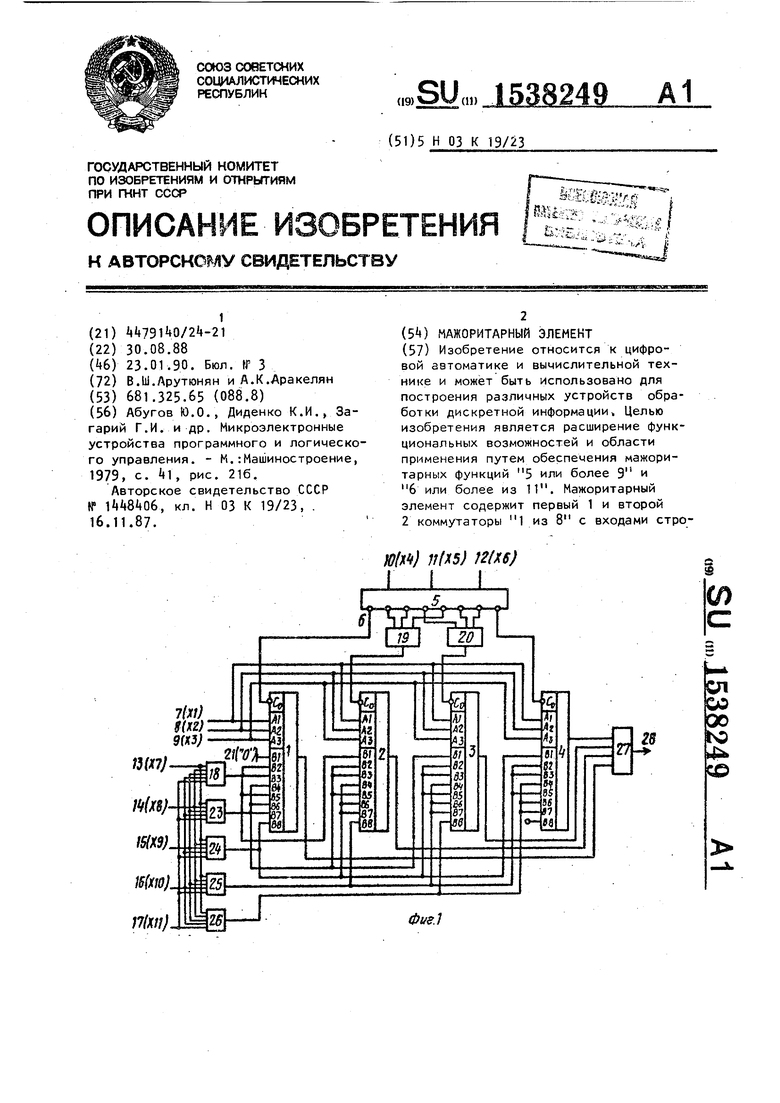

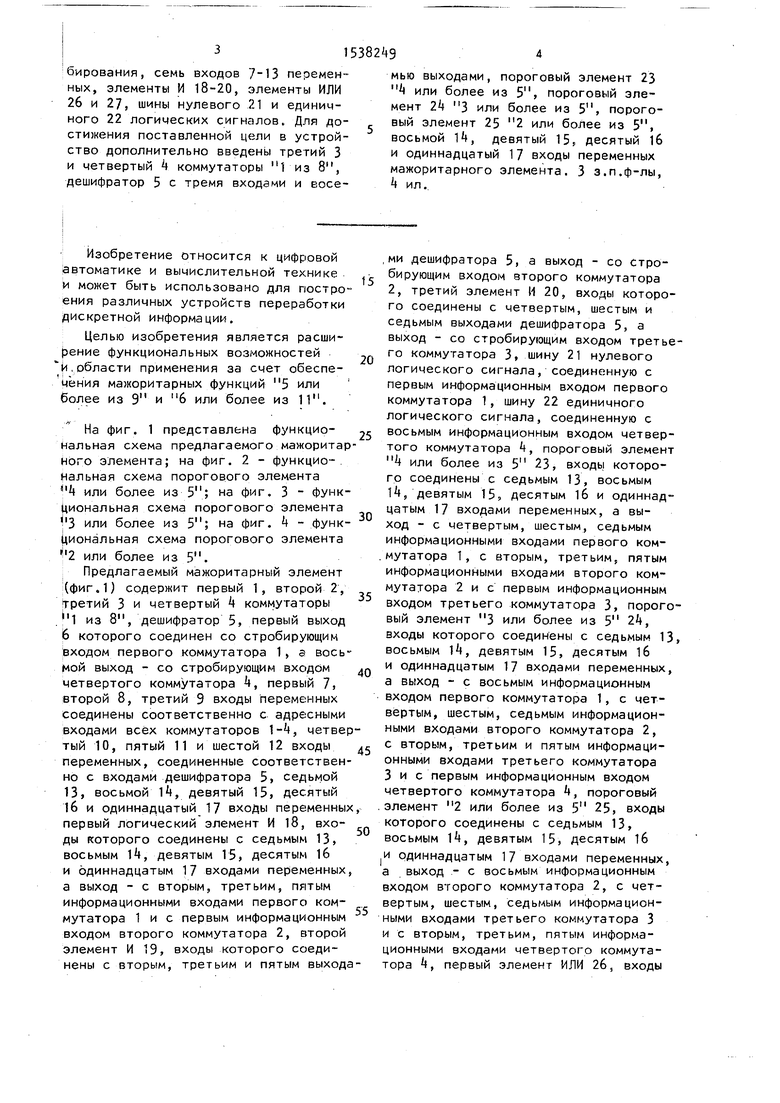

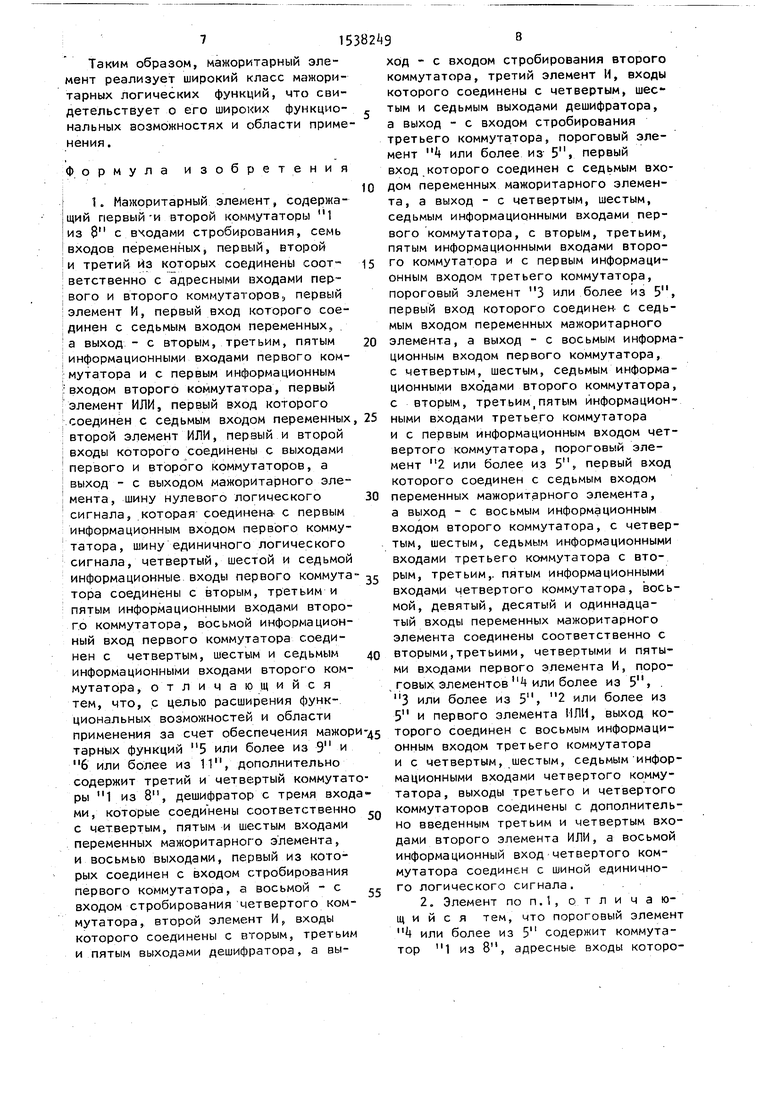

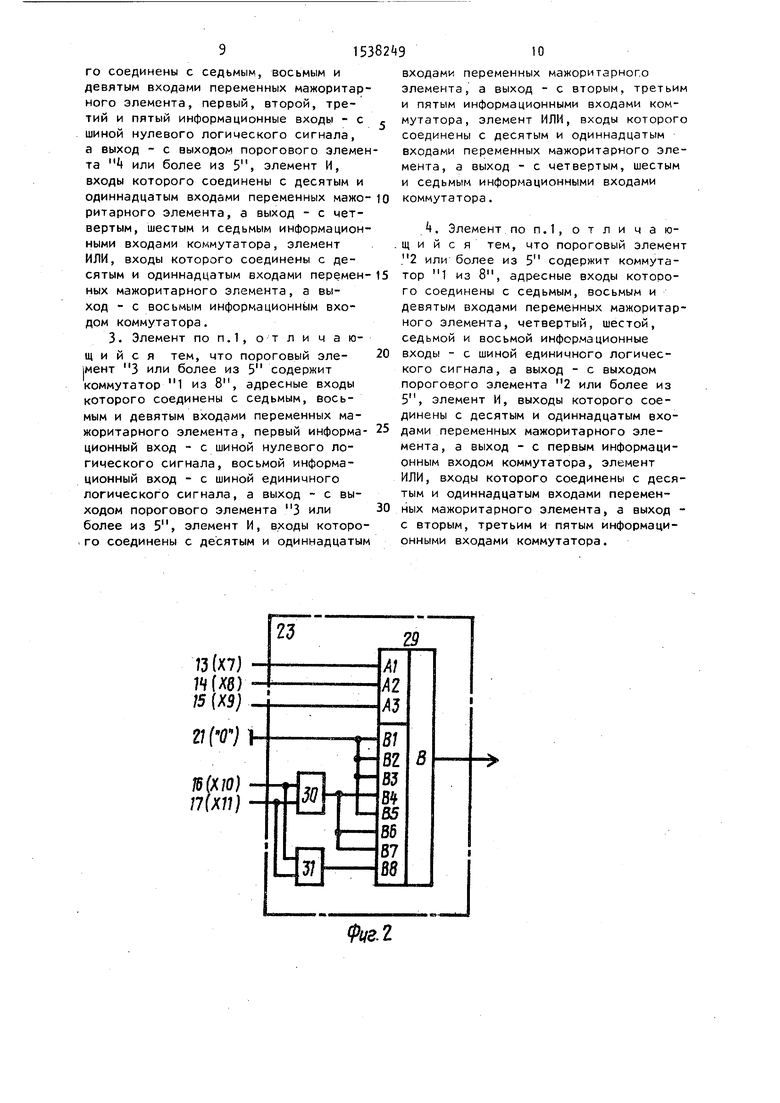

На фиг. 1 представлена функциональная схема предлагаемого мажоритарного элемента; на фиг. 2 - функциональная схема порогового элемента °А или более из на фиг. 3 - функциональная схема порогового элемента 3 или более из на фиг. 4 - функциональная схема порогового элемента 2 или более из 5.

Предлагаемый мажоритарный элемент (фиг.1) содержит первый 1, второй 2, Третий 3 и четвертый 4 коммутаторы Ч из 8, дешифратор 5, первый выход 6 которого соединен со стробирующим входом первого коммутатора 1, э восьмой выход - со стробирующим входом четвертого коммутатора , первый 7, второй 8, третий 9 входы переменных соединены соответственно с адресными входами всех коммутаторов 1-, четвер тый 10, пятый 11 и шестой 12 входы переменных, соединенные соответственно с входами дешифратора 5, седьмой 13, восьмой И, девятый 15, десятый 16 и одиннадцатый 17 входы переменных первый логический элемент И 18, входы которого соединены с седьмым 13, восьмым 14, девятым 15, десятым 16 и одиннадцатым 17 входами переменных, а выход - с вторым, третьим, пятым информационными входами первого коммутатора 1 и с первым информационным входом второго коммутатора 2, второй элемент И 19, входы которого соединены с вторым, третьим и пятым выхода

5

0

5

0

5

0

5

0

5

ми дешифратора 5, а выход - со стробирующим входом второго коммутатора 2, третий элемент И 20, входы которого соединены с четвертым, шестым и седьмым выходами дешифратора 5, а выход - со стробирующим входом третьего коммутатора 3, шину 21 нулевого логического сигнала, соединенную с первым информационным входом первого коммутатора 1, шину 22 единичного логического сигнала, соединенную с восьмым информационным входом четвертого коммутатора k, пороговый элемент 4 или более из 5 23, входы которого соединены с седьмым 13, восьмым 14, девятым 15, десятым 16 и одиннадцатым 17 входами переменных, а выход - с четвертым, шестым, седьмым информационными входами первого коммутатора 1, с вторым, третьим, пятым информационными входами второго коммутатора 2 и с первым информационным входом третьего коммутатора 3, пороговый элемент 3 или более из 5 2, входы которого соединены с седьмым 13, восьмым И, девятым 15, десятым 16 и одиннадцатым 17 входами переменных, а выход - с восьмым информационным входом первого коммутатора 1, с четвертым, шестым, седьмым информационными входами второго коммутатора 2, с вторым, третьим и пятым информационными входами третьего коммутатора 3 и с первым информационным входом четвертого коммутатора h, пороговый элемент 2 или более из 5 25, входы которого соединены с седьмым 13, восьмым И, девятым 15, десятым 16

и одиннадцатым 17 входами переменных, а выход - с восьмым информационным входом второго коммутатора 2, с четвертым, шестым, седьмым информационными входами третьего коммутатора 3 и с вторым, третьим, пятым информационными входами четвертого коммутатора , первый элемент ИЛИ 26, входы

15

20

которого соединены с седьмым 13, восьмым 1, девятым 15, десятым 16, одиннадцатым 17 входами переменных, а выход - с восьмым информационным входом третьего коммутатора 3 и с четвертым, шестым, седьмым информационными входами четвертого коммутатора Ц, второй элемент ИЛИ 27, входы которого соединены с выходами коммута- « торов 1-4, а его выход является выходом 28 мажоритарного элемента.

Пороговый элемент 4 или более из 5 23 (фиг.2) соцержит коммутатор 29 со структурой 1 из 8, адресные входы которого соединены соответственно с седьмым 13, восьмым 14 и девятым 15 входами переменных мажоритарного элемента, первый, второй, третий и пятый информационные входы соединены с шиной 21 нулевого логического сигнала, а выход - с выходом порогового элемента 23, элемент И 30, входы которого соединены с десятым 16 и одиннадцатым 17 входами переменных, а выход - с четвертым, шестым и седьмым информационными входами коммутатора 29, элемент ИЛИ 31, входы которого соединены с десятым 16 и одиннадцатым 17 входами переменных, а выход - с восьмым информационным входом коммутатора 29.

Пороговый элемент 3 или более из 5 24 (фиг.З) содержит коммутатор 32 со структурой 1 из 8, адресные входы которого соединены соответственно с седьмым 13, восьмым 14 и девятым 14 входами переменных, первый информационный вход - с шиной 21 нулевого логического сигнала, восьмой информационный вход - с шиной 22 единичного логического сигнала, а выход - с выходом порогового элемента 24, элемент И 33, входы котос выходом порогового элемента 25,

элемент И 36, входы которого соеди ны с десятым 16 и одиннадцатым 17 входами переменных, а выход - с пе вым информационным входом коммутат ра 35, элемент ИЛИ 37, входы котор го соединены с десятым 16 и одинна цатым 17 входами пеоеменных, а вых с вторым, третьим и пятым информац онными входами коммутатора 35, чет вертый, шестой, седьмой и восьмой информационные входы которого соед нены с шиной 22 единичного логиче кого сигнала.

Предлагаемый мажоритарный элеме работает следующим образом.

Для реализации мажоритарной фун ции 6 или более из 11 к шинам 7подаются входные переменные Х1-Х11 При этом, если в кодовых комбинаци входных переменных Х1-Х11 содержат шесть или более логических единиц (1), то на выходе 28 мажоритарно 25 элемента появляется единичный логи ческий сигнал, а в остальных случа нулевой логический сигнал (О).

Реализация мажоритарной функции

5 или более из 9 осуществляется 30 при приложении к двум из входов пе менных постоянных нулевых сигналов к остальным входам - девяти переме ных X.

Аналогично этому для реализации мажоритарной функции 4 или более из 7 постоянные нулевые сигналы п кладываются к четырем входам перем ных, для реализации мажоритарной функции 3 или более из 5 - к шес входам переменных, а для реализаци мажоритарной функции 2 или более 3 - к восьми входам переменных.

На выходе порогового элемента или более из 5м 23 единичные сигна

35

40

рого соединены с десятым 16 и одиннад- 45 возникают в тех случаях, когда на

цатым 17 входами переменных, а выход - с вторым, третьим и пятым информационными входами коммутатора 32, элемент ИЛИ 34, входы которого соединены с десятым 16 и одиннадцатым 17 входами переменных, а выход - с четвертым, шестым и седьмым информационными входами коммутатора 32.

Пороговый элемент 2 или более из 5 25 (фиг.4) содержит коммутатор 35 со структурой 1 из 8, адресные входы которого соединены соответственно с седьмым 13, восьмым 14 и девятым 15 входами переменных, а выход -.

50

55

его входах переменных прилагаются коды с четырьмя и пятью единицами, а в остальных случаях - возникает нулевой сигнал. Единичные сигналы возникают на выходе порогового эле мента 3 или более из 5 24 в тех случаях, когда на его входах перем ных подаются коды с тремя, четырь и пятью единицами. Единичные сигна возникают на выходе порогового эле мента 2 или более из 5 25 в тех случаях, когда в кодах входных пер менных содержатся два, три, четыре или пять единиц.

15

20

382496

с выходом порогового элемента 25,

элемент И 36, входы которого соединены с десятым 16 и одиннадцатым 17 входами переменных, а выход - с первым информационным входом коммутатора 35, элемент ИЛИ 37, входы которого соединены с десятым 16 и одиннадцатым 17 входами пеоеменных, а выход - с вторым, третьим и пятым информационными входами коммутатора 35, четвертый, шестой, седьмой и восьмой информационные входы которого соединены с шиной 22 единичного логического сигнала.

Предлагаемый мажоритарный элемент работает следующим образом.

Для реализации мажоритарной функции 6 или более из 11 к шинам 717 подаются входные переменные Х1-Х11 При этом, если в кодовых комбинациях входных переменных Х1-Х11 содержатся шесть или более логических единиц (1), то на выходе 28 мажоритарного 25 элемента появляется единичный логический сигнал, а в остальных случаях нулевой логический сигнал (О).

Реализация мажоритарной функции

5 или более из 9 осуществляется при приложении к двум из входов переменных постоянных нулевых сигналов, а к остальным входам - девяти переменных X.

Аналогично этому для реализации мажоритарной функции 4 или более из 7 постоянные нулевые сигналы прикладываются к четырем входам переменных, для реализации мажоритарной функции 3 или более из 5 - к шести входам переменных, а для реализации мажоритарной функции 2 или более из 3 - к восьми входам переменных.

На выходе порогового элемента 4 или более из 5м 23 единичные сигналы

0

5

его входах переменных прилагаются коды с четырьмя и пятью единицами, а в остальных случаях - возникает нулевой сигнал. Единичные сигналы возникают на выходе порогового элемента 3 или более из 5 24 в тех случаях, когда на его входах переменных подаются коды с тремя, четырьмя и пятью единицами. Единичные сигналы возникают на выходе порогового элемента 2 или более из 5 25 в тех случаях, когда в кодах входных переменных содержатся два, три, четыре или пять единиц.

Таким образом, мажоритарный элемент реализует широкий класс мажоритарных логических функций, что свидетельствует о его широких функциональных возможностях и области применения .

Формула изобретения

применения за счет обеспечения мажори- торого соединен с восьмым информацитарных функций 5 или более из 9 и 6 или более из 11, дополнительно содержит третий и четвертый коммутаторы 1 из 8, дешифратор с тремя входами, которые соединены соответственно с четвертым, пятым и шестым входами переменных мажоритарного элемента, и восьмью выходами, первый из которых соединен с входом стробирования первого коммутатора, а восьмой - с входом стробирования четвертого коммутатора, второй элемент И, входы которого соединены с вторым, третьим и пятым выходами дешифратора, а вы50

55

онным входом третьего коммутатора и с четвертым, шестым, седьмым информационными входами четвертого коммутатора, выходы третьего и четвертого коммутаторов соединены с дополнительно введенным третьим и четвертым входами второго элемента ИЛИ, а восьмой информационный вход четвертого коммутатора соединен с шиной единичного логического сигнала.

s 0 5 0 0

ход - с входом стробирования второго коммутатора, третий элемент И, входы которого соединены с четвертым, шестым и седьмым выходами дешифратора, а выход - с входом стробирования третьего коммутатора, пороговый элемент 4 или более из 5, первый вход.которого соединен с седьмым входом переменных мажоритарного элемента, а выход - с четвертым, шестым, седьмым информационными входами первого коммутатора, с вторым, третьим, пятым информационными входами второго коммутатора и с первым информационным входом третьего коммутатора, пороговый элемент 3 или более из 5, первый вход которого соединен с седьмым входом переменных мажоритарного элемента, а выход - с восьмым информационным входом первого коммутатора, с четвертым, шестым, седьмым информационными входами второго коммутатора, с вторым, третьим,пятым информационными входами третьего коммутатора и с первым информационным входом четвертого коммутатора, пороговый элемент 2 или более из 5, первый вход которого соединен с седьмым входом переменных мажоритарного элемента, а выход - с восьмым информационным входом второго коммутатора, с четвертым, шестым, седьмым информационными входами третьего коммутатора с вторым, третьим,, пятым информационными входами четвертого коммутатора, восьмой, девятый, десятый и одиннадцатый входы переменных мажоритарного элемента соединены соответственно с вторыми,третьими, четвертыми и пятыми входами первого элемента И, поро- , говых элементов 4 или более из 5,

или более из

5,

2 или более из

и первого элемента ИЛИ, выход ко0

5

онным входом третьего коммутатора и с четвертым, шестым, седьмым информационными входами четвертого коммутатора, выходы третьего и четвертого коммутаторов соединены с дополнительно введенным третьим и четвертым входами второго элемента ИЛИ, а восьмой информационный вход четвертого коммутатора соединен с шиной единичного логического сигнала.

13(Х7)

14{W

15fXSj

21W

/5(Х/0) 17(Х11)

.2

0 5

0

входами переменных мажоритарного элемента, а выход - с вторым, третьим и пятым информационными входами коммутатора, элемент ИЛИ, входы которого соединены с десятым и одиннадцатым входами переменных мажоритарного элемента, а выход - с четвертым, шестым и седьмым информационными входами коммутатора.

. Элемент поп.1,отличаю- щ и и с я тем, что пороговый элемент .2 или более из 5 содержит коммутатор 1 из 8, адресные входы KOTODO- го соединены с седьмым, восьмым и девятым входами переменных мажоритарного элемента, четвертый, шестой, седьмой и восьмой информационные входы - с шиной единичного логического сигнала, а выход - с выходом порогового элемента 2 или более из 5, элемент И, выходы которого соединены с десятым и одиннадцатым входами переменных мажоритарного элемента, а выход - с первым информационным входом коммутатора, элемент ИЛИ, входы которого соединены с десятым и одиннадцатым входами переменных мажоритарного элемента, а выход - с вторым, третьим и пятым информационными входами коммутатора.

vtW

15 №)

15 (МО) П(КП)

)(

Р№.3

ФиъМ

| Абугов Ю.О., Диденко К.И., За- гарий Г.И | |||

| и др | |||

| Микроэлектронные устройства программного и логического управления | |||

| - М.:Машиностроение, 1979, с | |||

| k, рис | |||

| Приспособление для подвешивания тележки при подъемках сошедших с рельс вагонов | 1920 |

|

SU216A1 |

| Авторское свидетельство СССР fP , кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| ( МАЖОРИТАРНЫЙ ЭЛЕМЕНТ | |||

Авторы

Даты

1990-01-23—Публикация

1988-08-30—Подача