Изобретение относится к радиотехнике и вычислительной технике и предназначено для моделирования процессов, протекающих в сложных информационных вычислительных системах, комплексах средств центров обработки данных.

Известен вероятностный автомат, содержащий генератор тактовых импульсов, элементы И и ИЛИ, регистр сдвига, блоки памяти и задания времени (см. авт. св. СССР №1045232, G06F 15/36, 1983, бюл. 36).

Однако данный вероятностный автомат имеет узкую область применения, так как моделирует неуправляемые полумарковские цепи без учета внешних управляющих воздействий, что не позволяет применять его для анализа реально протекающих процессов в сложных информационных вычислительных системах, например, таких как центры обработки данных (ЦОД).

Известен вероятностный автомат (патент РФ №2099781, G06F 17/00, 1997, бюл. 35), содержащий блок элементов И, блок памяти, блок задания времени, элемент ЗАПРЕТ, элемент ИЛИ, датчик случайной последовательности, блок формирования корректирующей последовательности, блок коррекции, блок формирования значений матрицы, блок формирования значений индикаторов, блок управления, дешифратор и генератор тактовых импульсов.

Однако данный вероятностный автомат также имеет ограниченную область применения, так как моделирует управляемые полумарковские процессы с раз и навсегда заданными пороговыми значениями (границами) состояний - не способен динамически корректировать границы состояний моделируемого процесса, что не позволяет применять его для динамического анализа состояния, поскольку большое количество процессов, протекающих в сложных информационных вычислительных системах, таких как ЦОД, могут в динамике функционирования изменять пороговые значения своих состояний под влиянием управляющих воздействий или внешних факторов.

Наиболее близким по технической сущности к заявляемому устройству (прототипом) является вероятностный автомат (см. патент РФ №2139569, G06F 17/18, 1999, бюл. 28) содержащий датчик случайной последовательности, блок формирования нецелочисленных значений индикаторов, блок коррекции, блок формирования значений матрицы, блок управления, блок пороговых устройств, блок формирования значений индикаторов, блок элементов И, блок памяти, блок задания времени, дешифратор, элемент ЗАПРЕТ, элемент ИЛИ и генератор тактовых импульсов, выход которого соединен с прямым входом элемента ЗАПРЕТ и тактовым входом блока задания времени, выходов которого являются соответственно выходами автомата и подключены к соответствующим входам элемента ИЛИ, выход которого соединен с инверсным входом элемента ЗАПРЕТ, выход которого подключен к тактовым входам блока элементов И, блока формирования значений индикаторов и блока управления, управляющий вход которого является управляющим входом автомата, а управляющий выход подключен к входам дешифратора и блока формирования значений матрицы, выходов блока формирования значений индикаторов соединены с соответствующими m входами блока элементов И, выходов которого подключены к соответствующим входам блока памяти, выходов которого соединены с соответствующими входами блока задания времени, управляющий вход которого подключей к выходу дешифратора, управляющих входов блока формирования нецелочисленных значений индикаторов соединены с соответствующими выходами блока формирования значений матрицы, интерполяционных входов блока формирования нецелочисленных значений индикаторов подключены к соответствующим выходам блока памяти, выходов блока формирования нецелочисленных значений индикаторов соединены с соответствующими вспомогательными входами блока формирования значений индикаторов и с информационными входами блока коррекции, стартовый вход которого подключен к выходу датчика случайной последовательности, выход блока коррекции соединен с входом блока пороговых устройств, выходов которого подключены к соответствующим информационным входам блока формирования значений индикаторов, пороговых выходов блока управления подключены к соответствующим пороговым входам блока коррекции и блока пороговых устройств.

Достоинством прототипа является его способность моделировать управляемые полумарковские цепи с динамической коррекцией пороговых значений (границ) состояний случайных процессов, протекающих в сложных информационных вычислительных системах.

Однако прототип имеет недостаток - относительно низкую достоверность моделирования параметров реального процесса функционирования сложных информационных вычислительных систем в условиях как неоднозначности (нечеткости), так и недостоверности (недостаточности, неполноты, противоречивости) исходных данных, т.е. относительно низкую достоверность моделирования состояний сложных информационных вычислительных систем как с неоднозначно, так и недостоверно заданными параметрами. Это связано с тем, что моделирование осуществляется на основе вводимых количественных значений исходных данных (элементов матриц переходных вероятностей, пороговых значений (границ) состояний), что делает малоэффективным применение прототипа для динамического многокритериального анализа сложных информационных вычислительных системах, комплексов средств центров обработки данных. Данный вероятностный автомат позволяет моделировать управляемые полумарковские цепи с динамической коррекцией пороговых значений (границ) состояний лишь тех случайных процессов, исходные данные для которых заданы количественно, в то время как исходные данные для моделирования большого количества процессов, реально протекающих в сложных информационных вычислительных системах могут быть заданы лишь неоднозначно и (или) недостоверно, опираясь на мнения большого количества экспертов.

Целью предлагаемого изобретения является создание вероятностного автомата, обеспечивающего повышение достоверности моделирования параметров реального процесса функционирования сложных информационных вычислительных систем, комплексов средств центров обработки данных в условиях неоднозначности (нечеткости), и (или) недостоверности (недостаточности, неполноты, противоречивости) исходных данных, вероятностного автомата, способного с высокой достоверностью моделировать управляемые полумарковские цепи, формируемые с учетом как количественно, так и качественно (неоднозначно (нечетко), и (или) недостоверно (недостаточно, неполно, противоречиво)) заданных исходных данных, описывающих пороговые значения (границы) и вероятностно-временной механизм (элементы матриц переходных вероятностей) смены состояний моделируемых случайных процессов.

Указанная цель достигается тем, что в известный вероятностный автомат, содержащий датчик случайной последовательности, блок формирования нецелочисленных значений индикаторов, блок коррекции, блок формирования значений матрицы, блок управления, блок пороговых устройств, блок формирования значений индикаторов, блок элементов И, блок памяти, блок задания времени, дешифратор, элемент ЗАПРЕТ, элемент ИЛИ и генератор тактовых импульсов, выход которого соединен с прямым входом элемента ЗАПРЕТ и тактовым входом блока задания времени, выходов которого являются соответствующими выходами автомата и подключены к соответствующим входам элемента ИЛИ, выход которого соединен с инверсным входом элемента ЗАПРЕТ, выход которого подключен к тактовым входам блока элементов И, блока формирования значений индикаторов и блока управления, управляющий вход которого является управляющим входом автомата, выходов блока формирования значений индикаторов соединены с соответствующими входами блока элементов И, выходов которого подключены к соответствующим входам блока памяти, выходов которого соединены с соответствующими интерполяционными входами блока формирования нецелочисленных значений индикаторов и с входами блока задания времени, управляющий вход которого подключен к выходу дешифратора, управляющих входов блока формирования нецелочисленных значений индикаторов соединены с соответствующими выходами блока формирования значений матрицы, выходов блока формирования нецелочисленных значений индикаторов соединены с соответствующими вспомогательными входами блока формирования значений индикаторов и с информационными входами блока коррекции, стартовый вход которого подключен к выходу датчика случайной последовательности, выход блока коррекции соединен с входом блока пороговых устройств, выходов которого подключены к соответствующим информационным входам блока формирования значений индикаторов, дополнительно введен блок нейронечеткой сети. Управляющий вход блока нейронечеткой сети подключен к управляющему выходу блока управления, пороговые выходы которого соединены с соответствующими пороговыми входами блока нейронечеткой сети, управляющий выход которого подключен к входам дешифратора и блока формирования значений матрицы, пороговые выходы блока нейронечеткой сети подключены к соответствующим пороговым входам блока коррекции и блока пороговых устройств.

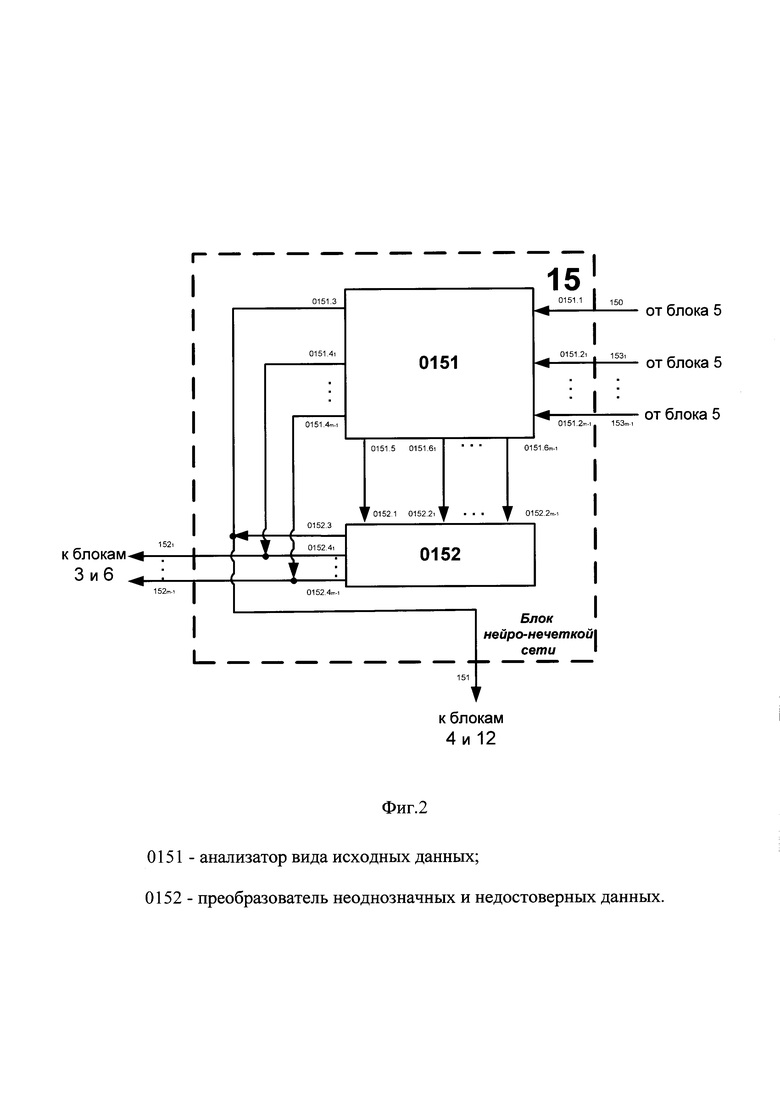

Блок нейронечеткой сети состоит из анализатора вида исходных данных и преобразователя неоднозначных и недостоверных данных, пороговые входы которого соединены с соответствующими пороговыми выходами анализатора вида исходных данных, управляющий выход которого подключен к управляющему входу преобразователя неоднозначных и недостоверных данных. Управляющий вход анализатора вида исходных данных является управляющим входом блока, управляющий выход анализатора вида исходных данных соединен с управляющим выходом преобразователя неоднозначных и недостоверных данных и является управляющим выходом блока, пороговые входы анализатора вида исходных данных являются соответствующими пороговыми входами блока, пороговые выходы преобразователя неоднозначных и недостоверных данных соединены с соответствующими пороговыми выходами анализатора вида исходных данных и являются соответствующими пороговыми выходами блока нейронечеткой сети.

Блок формирования значений матрицы состоит из запоминающего элемента и счетчика. Вход счетчика является входом блока, выход счетчика соединен с входом запоминающего элемента, m выходов которого являются соответствующими m выходами блока.

Блок управления состоит из управляющего оперативного запоминающего элемента (ОЗЭ), порогового ОЗЭ и счетчика. Первый и второй выходы счетчика подключены к тактовым входам соответственно управляющего и порогового ОЗЭ, первый и второй входы счетчика соединены со сбрасывающими выходами соответственно управляющего и порогового ОЗЭ, третий вход счетчика является тактовым входом блока, информационные входы управляющего и порогового ОЗЭ объединены и являются управляющим входом блока, выход управляющего ОЗЭ является управляющим выходом блока, m-1 выходы порогового ОЗЭ являются соответствующими т-1 пороговыми выходами блока.

Благодаря новой совокупности существенных признаков за счет введения блока нейро-нечеткой сети, обеспечивающего последовательное сравнение (по количеству разрядов) поступающих в двоичном коде исходных данных, принятие решения об их математической природе и преобразование исходных данных, в заявленном вероятностном автомате достигается возможность предварительного анализа и трансформирования исходных данных, заданных одновременно как неоднозначно (нечетко), так и недостоверно (недостаточно, неполно, противоречиво) к виду, пригодному для осуществления процедуры параметрического моделирования, что обуславливает повышение достоверности моделирования процесса смены состояний параметров сложных информационных вычислительных систем, таких как ЦОД, в условиях, присущих реальному процессу его функционирования - в условиях как неоднозначности (нечеткости), так и недостоверности (недостаточности, неполноты, противоречивости) исходных данных

Проведенный анализ уровня техники позволил установить, что аналоги, характеризующиеся совокупностью признаков, тождественных всем признакам заявленного технического решения, отсутствуют, что указывает на соответствие заявленного устройства условию патентоспособности «новизна».

Результаты поиска известных решений в данной и смежных областях техники с целью выявления признаков, совпадающих с отличительными от прототипа признаками заявленного объекта, показали, что они не следуют явным образом из уровня техники. Из уровня техники также не выявлена известность влияния предусматриваемых существенными признаками заявленного изобретения преобразований на достижение указанного технического результата. Следовательно, заявленное изобретение соответствует условию патентоспособности «изобретательский уровень».

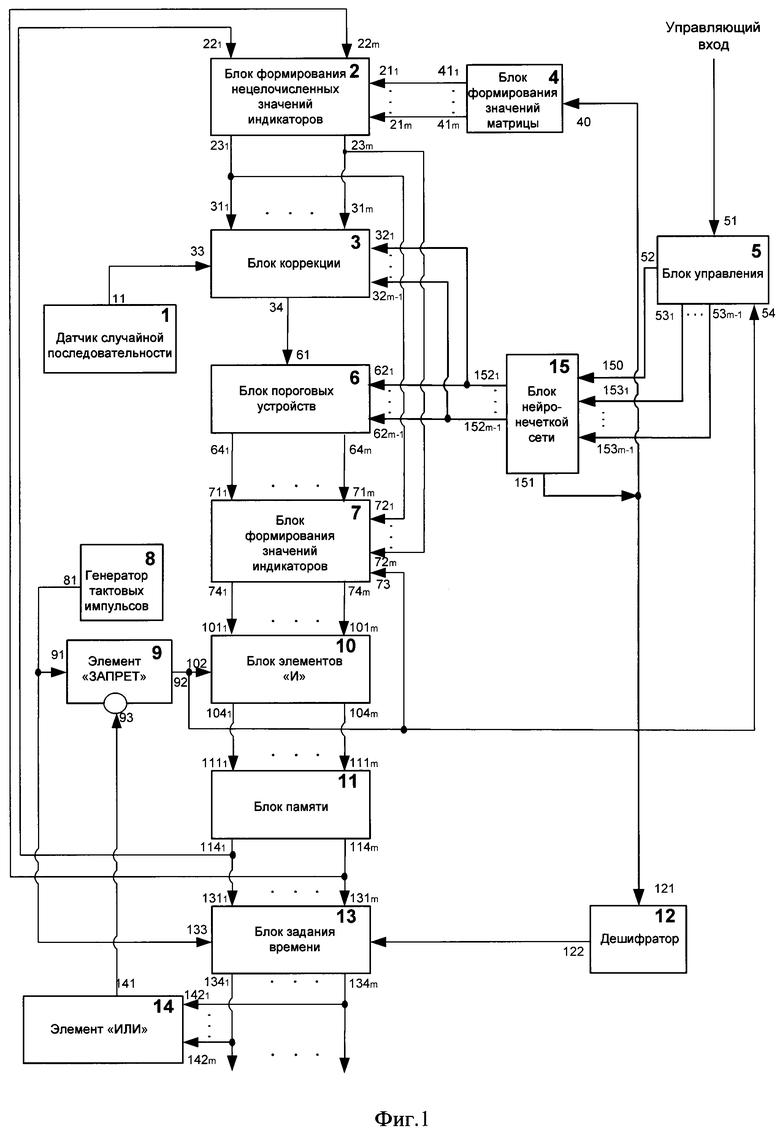

Заявленное устройство поясняется чертежами, на которых представлены:

на фиг. 1 - структурная схема управляемого вероятностного автомата;

на фиг. 2 - структурная схема блока нейро-нечеткой сети;

на фиг. 3 - структурная схема анализатора вида исходных данных;

на фиг. 4 - структурная схема преобразователя неоднозначных и недостоверных данных;

Управляемый вероятностный автомат, изображенный на фиг. 1, состоит из датчика случайной последовательности 1, блока формирования нецелочисленных значений индикаторов 2, блока коррекции 3, блока формирования значений матрицы 4, блока управления 5, блока пороговых устройств 6, блока формирования значений индикаторов 7, генератора тактовых импульсов 8, элемента ЗАПРЕТ 9, блока элементов И 10, блока памяти 11, дешифратора 12, блока задания времени 13, элемента ИЛИ 14 и блока нейро-нечеткой сети 15. Выход генератора тактовых импульсов 8 соединен с прямым входом элемента ЗАПРЕТ 9 и тактовым входом блока задания времени 13, выходов которого являются соответствующими выходами автомата и подключены к соответствующим входам элемента ИЛИ 14, выход которого соединен с инверсным входом элемента ЗАПРЕТ 9, выход которого подключен к тактовому входу блока элементов И 10, тактовому входу 73 блока формирования значений индикаторов 7 и тактовому входу 54 блока управления 5, управляющий вход 51 которого является управляющим входом автомата, выходов блока формирования значений индикаторов 7 соединены с соответствующими входами блока элементов И 10, выходы которого подключены к соответствующим входам блока памяти 11, выходы которого соединены с соответствующими интерполяционными входами 221-22m блока формирования нецелочисленных значений индикаторов 2 и с входами блока задания времени 13, управляющий вход которого подключен к выходу дешифратора 12, управляющие входы 211-21m блока формирования нецелочисленных значений индикаторов 2 соединены с соответствующими выходами 411-41m блока формирования значений матрицы 4, выходы 231-23m блока формирования нецелочисленных значений индикаторов 2 соединены с соответствующими вспомогательными входами 721-72m блока формирования значений индикаторов 7 и с информационными входами 311-31m блока коррекции 3, стартовый вход 33 которого подключен к выходу датчика случайной последовательности 1. Выход 34 блока коррекции 3 соединен с входом блока пороговых устройств 6, выходов которого подключены к соответствующим информационным входам блока формирования значений индикаторов 7. Управляющий вход 150 блока нейро-нечеткой сети 15 подключен к управляющему выходу 52 блока управления 5, пороговых выходов 531-53m-1 которого соединены с соответствующими пороговыми входами 1531-153m-1 блока нейро-нечеткой сети 15, управляющий выход 151 которого подключен к входу дешифратора 12 и входу 40 блока формирования значений матрицы 4, пороговые выходы 1521-152m-1 блока нейро-нечеткой сети 15 подключены к соответствующим пороговым входам 321-32m-1 блока коррекции 3 и к пороговым входам 621-62m-1 блока пороговых устройств 6.

Число «m», «m≥3» (входов, выходов, сумматоров, умножителей, счетчиков, элементов сравнения и т.п.) определяется в соответствии с необходимой и достаточной степенью детализации пространства состояний (количеством состояний) моделируемого процесса и, как правило, составляет от 3 (трех) до 20 (двадцати).

Блок нейро-нечеткой сети 15 (фиг. 2) предназначен для осуществления процедур последовательного сравнения (по количеству разрядов) поступающих в двоичном коде исходных данных, принятия решения об их математической природе и преобразования исходных данных, заданных как неоднозначно (нечетко), так и недостоверно (недостаточно, неполно, противоречиво), к виду, пригодному для осуществления процедуры параметрического моделирования.

Блок нейро-нечеткой сети 15 состоит из анализатора вида исходных данных 0151 и преобразователя неоднозначных и недостоверных данных 0152, пороговые входы 0152.21-0152.2m-1 которого соединены с соответствующими пороговыми выходами 0151.61-0151.6m-1 анализатора вида исходных данных 0151. Управляющий выход 0151.5 анализатора вида исходных данных 0151 подключен к управляющему входу 0152.1 преобразователя неоднозначных и недостоверных данных 0152. Управляющий вход 0151.1 анализатора вида исходных данных 0151 является управляющим входом 150 блока нейро-нечеткой сети 15, управляющий выход 0151.3 анализатора вида исходных данных 0151 соединен с управляющим выходом 0152.3 преобразователя неоднозначных и недостоверных данных 0152 и является управляющим выходом 151 блока нейро-нечеткой сети 15, пороговые входы 0151.21-0151.2m-1 анализатора вида исходных данных 0151 являются соответствующими пороговыми входами 1531-153m-1 блока нейро-нечеткой сети 15, пороговые выходы 0152.41-0152.4m-1 преобразователя неоднозначных и недостоверных данных 0152 соединены с соответствующими пороговыми выходами 0151.41-0151.4m-1 анализатора вида исходных данных 0151 и являются соответствующими пороговыми выходами 1521-152m-1 блока нейро-нечеткой сети 15.

Анализатор вида исходных данных 0151 блока нейро-нечеткой сети 15 (фиг. 3) предназначен для осуществления процедуры последовательного сравнения (по количеству разрядов) поступающих в двоичном коде исходных данных и принятия решения об их математической природе - исходные данные заданы одновременно как неоднозначно (нечетко), так и недостоверно (недостаточно, неполно, противоречиво) с использованием аналитически сформулированных субъективных мнений экспертов о конкретных значениях порогов и элементов вероятностно-временного механизма (элементов матриц переходных вероятностей) смены состояний моделируемых случайных процессов. Анализатор вида исходных данных 0151 состоит из элемента сдвига 01510 и элемента хранения 01511. Вход 01510-1 элемента сдвига 01510 является управляющим входом 0151.1 анализатора вида исходных данных 0151, прямой выход 01510-2 элемента сдвига 01510 является управляющим выходом 0151.3 анализатора вида исходных данных 01510. Выход 01510-3 элемента сдвига 01510 является управляющим выходом 0151.5 анализатора вида исходных данных 0151, входы 01511-41-01511-4m-1 элемента хранения 01511 являются пороговыми входами 0151.21-0151.2m-1 анализатора вида исходных данных 0151, прямые выходы 01511-51-01511-5m-1 элемента хранения 01511 являются пороговыми выходами 0151.41-0151.4m-1 анализатора вида исходных данных 0151, выходы 01511-61-01511-6m-1 элемента хранения 01511 являются пороговыми выходами 0151.61-0151.6m-1 анализатора вида исходных данных 0151. Элемент сдвига 01510 может быть технически реализован в виде сдвигающего регистра для сдвига влево, как показано в литературе [Пухальский Г.И., Новосельцева Т.Я. Цифровые устройства: Учебное пособие для вузов. - СПб.: Политехника, 1996. С. 589-599, рис. 7.1(6)]. Элемент хранения 01511 может быть реализован на базе типового регистра хранения на D-триггерах, описанного в литературе [Сидоров A.M., Гусев В.В., Лебедев О.Н. Основы импульсной и цифровой техники. - СПб.: СПВВИУС, 1995. С. 156-158, рис. 5.27].

Преобразователь неоднозначных и недостоверных данных 0152 блока нейро-нечеткой сети 15 (фиг. 4) предназначен для осуществления процедуры преобразование исходных данных, заданных одновременно как неоднозначно (нечетко), так и недостоверно (недостаточно, неполно, противоречиво), к виду, пригодному для осуществления процедуры параметрического моделирования. Преобразователь неоднозначных и недостоверных данных 0152 представляет собой перепрограммируемый постоянный запоминающий элемент-вычислитель (ПЗЭВ) с одним разрешающим входом, одним разрешающим выходом, входами и выходами, где m может принимать значения от 3 до 20.

Разрешающий вход V ПЗЭВ является управляющим входом 0152.1 преобразователя неоднозначных и недостоверных данных 0152, разрешающий выход S ПЗЭВ является управляющим выходом 0152.3 преобразователя недостоверных данных 0152, m-1 входы и m-1 выходы ПЗЭВ являются соответственно m-1 пороговыми входами 0152.21-0152.2m-1 и соответственно m-1 пороговыми выходами 0152.41-0152.4m-1 преобразователя неоднозначных и недостоверных данных 0152. Преобразователь неоднозначных и не-достоверных данных 0152 может быть технически реализован на основе перепрограммируемого постоянного запоминающего устройства SN 74184N как показано в работе [Нефедов А.В. Интегральные микросхемы и их зарубежные аналоги. Справочник. Т. 2. - М.: РадиоСофт, 2000. С. 172, рис. 1.126].

Датчик случайной последовательности 1, входящий в общую структурную схему, предназначен для генерации значений случайной вспомогательной последовательности с нормальной плотностью распределения и может быть реализован в виде серийно выпускаемого датчика, описанного в [Мальцева Л.А., Франберг Э.М., Ямпольский B.C. Основы цифровой техники. - М.: Радио и связь, 1980. С. 42, рис. 25].

Блок формирования нецелочисленных значений индикаторов 2, входящий в общую структурную схему, предназначен для формирования элементов вектора нецелочисленных значений индикаторов состояния. Его структурная схема и принцип действия известны и описаны в прототипе (см. патент РФ №2139569, фиг. 2)

Блок коррекции 3, входящий в общую структурную схему, предназначен для динамической коррекции математического ожидания (МО) и дисперсии случайной последовательности в соответствии с условиями, определяемыми принятой математической моделью. Его структурная схема и принцип действия известны и описаны в прототипе (см. патент РФ №2139569, фиг. 3-7).

Блок формирования значений матрицы 4 предназначен для регистрации поступающих значений элементов матрицы переходных вероятностей, хранения, считывания управляющей информации и состоит из запоминающего элемента 401 и счетчика 402. Вход счетчика 402 является входом 40 блока 4, выход счетчика 402 соединен с входом запоминающего элемента 401, m выходов которого являются соответствующими m выходами 411-41m блока 4. Запоминающий элемент 401 может быть технически реализован в виде запоминающего устройства, описанного в [Быстрое Ю.А., Великсон Я.М., Вогман В.Д. и др. Электроника: Справочная книга / Под ред. Быстрова Ю.А. - СПб.: Энергоатомиздат, 1996. С. 291-292, рис. 6.7]. Счетчик 402 может быть технически реализован на базе серийно выпускаемого счетчика, как показано в [Соботка З., Стары Я. Микропроцессорные системы. - М.: Энергоиздат, 1981. С. 96-100].

Блок управления 5 предназначен для формирования управляющей кодовой последовательности, а также последовательности пороговых значений состояний и состоит из управляющего ОЗЭ 501, порогового ОЗЭ 502 и счетчика 503. Первый 5.1 и второй 5.3 выходы счетчика 503 подключены соответственно к тактовым входам 5.6 управляющего ОЗЭ 501 и 5.9 порогового ОЗЭ 502. Первый 5.2 и второй 5.4 входы счетчика 503 соединены соответственно со сбрасывающими выходами 5.7 управляющего ОЗЭ 501 и 5.10 порогового ОЗЭ 502, третий вход 5.0 счетчика 503 является тактовым входом 54 блока 5. Информационные входы 5.5 управляющего ОЗЭ 501 и 5.8 порогового ОЗЭ 502 объединены и являются управляющим входом 51 блока 5, выход 5.12 управляющего ОЗЭ 501 является управляющим выходом 52 блока 5, m-1 выходы 5.111-5.11m-1 порогового ОЗЭ 502 являются соответствующими m-1 пороговыми выходами 531-53m-1 блока управления 5. Управляющий ОЗЭ 501 может быть технически реализован в виде типового оперативного запоминающего устройства, которое подробно описано в [Соботка 3., Стары Я. Микропроцессорные системы. - М.: Энергоиздат, 1981. С. 94-96]. Частный случай технической реализации счетчика 503 описан в [Соботка З., Стары Я. Микропроцессорные системы. - М.: Энергоиздат, 1981. С. 96-100]. Техническая реализация порогового ОЗЭ 502 возможна по аналогии с серийно выпускаемым динамическим оперативным запоминающим устройством, описанным в [Сидоров A.M., Гусев В.В., Лебедев О.Н. Основы импульсной и цифровой техники. - СПб.: СПВВИУС, 1995. С. 194-196, рис. 6.9].

Блок пороговых устройств 6, входящий в общую структурную схему, предназначен для получения предварительных значений элементов вектора индикаторов состояния процесса. Его структурная схема и принцип действия известны и описаны в прототипе (см. патент РФ №2139569, фиг. 9).

Блок формирования значений индикаторов 7, входящий в общую структурную схему, предназначен для получения окончательных значений элементов вектора индикаторов состояния процесса. Его структурная схема и принцип действия известны и описаны в прототипе (см. патент РФ №2139569, фиг. 10).

Генератор тактовых импульсов 8, входящий в общую структурную схему, предназначен для определения моментов выхода вероятностного автомата из предыдущего состояния и реализуется в виде известного генератора пилообразного напряжения, описанного в работе [Быстрое Ю.А., Великсон Я.М., Вогман В.Д. и др. Электроника: Справочная книга / Под ред. Быстрова Ю.А. - СПб.: Энергоатомиздат, 1996. С. 149-151, рис. 3.14 (а)].

Элемент ЗАПРЕТ 9 и элемент ИЛИ 14, входящие в общую структурную схему, предназначены для поддержки процедуры определения моментов выхода вероятностного автомата из предыдущего состояния и могут быть построены на базе серийно выпускаемых элементов ЗАПРЕТ и ИЛИ, подробно описанных в [Мальцева Л.А., Франберг Э.М., Ямпольский B.C. Основы цифровой техники. - М.: Радио и связь, 1980. С. 20-24, рис. 9, 11].

Блок элементов И 10, входящий в общую структурную схему, предназначен для осуществления записи полученных значений элементов вектора индикаторов состояния в блок памяти. Элементы И, входящие в блок элементов И 10, реализуются в виде известных и описанных в [Сидоров A.M., Гусев В.В., Лебедев О.Н. Основы импульсной и цифровой техники. - СПб.: СПВВИУС, 1995. С. 13-14, рис. 1.2].

Блок памяти 11, входящий в общую структурную схему, предназначен для хранения значений элементов вектора индикаторов состояния до момента истечения периода смены состояний и реализуется в виде типового регистра хранения в соответствии с описанием, представленным в работе [Сидоров A.M., Гусев В.В., Лебедев О.Н. Основы импульсной и цифровой техники. - СПб.: СПВВИУС, 1995. С. 156-158, рис. 5.27].

Дешифратор 12, входящий в общую структурную схему, предназначен для преобразования управляющей кодовой последовательности в код, соответствующий временному интервалу периода смены состояний и построен в виде серийно выпускаемого дешифратора, описанного в книге [Богданович М.И., Грель И.Н., Прохоренко В.А. и др. Цифровые интегральные микросхемы: Справочник. - Минск: Беларусь, 1991. С. 432-436, рис. 4.46].

Блок задания времени 13, входящий в общую структурную схему, предназначен для формирования нулевой комбинации, определяющей момент истечения периода смены состояний и реализуется в виде цифрового таймера, аналогично описанному в работе [Фролкин В.Т., Попов Л.Н. Импульсные и цифровые устройства. - М.: Радио и связь, 1992. С. 264-267, рис. 7.48].

Вероятностный автомат работает следующим образом. Известно, что для аналитического вероятностно-временного описания системы функционирования сложных информационных вычислительных систем применяется аппарат управляемых цепей Маркова в форме разностных стохастических уравнений. Вместе с тем, анализ работ [1, 5-8] позволяет сформировать математически корректный алгоритм приведения одновременно как неоднозначно (нечетко), так и недостоверно (недостаточно, неполно, противоречиво) заданных исходных данных - элементов матриц переходных вероятностей, пороговых значений состояний, к ближайшему достоверному множеству. Таким образом, в рамках моделирования управляемых полумарковских цепей, формируемых с учетом одновременно как неоднозначно (нечетко),так и недостоверно (недостаточно, неполно, противоречиво) заданных исходных данных, ряд характеристик сложных информационных вычислительных систем, комплексов средств центров обработки данных моделируется на основе параметрически заданных исходных данных, традиционными методами, а моделирование одновременно заданных как неоднозначно (нечетко), так и недостоверно (не-достаточно, неполно, противоречиво) параметров сложных информационных вычислительных, путем последовательных преобразований с использованием нейронечетких вычислительных методов и алгоритмов, сводится к возможности их относительно параметрического моделирования.

Для решения задачи объединения одновременно как неоднозначных (нечетких), так и недостоверных (недостаточных, неполных, противоречивых) мнений экспертов о значениях исходных данных для моделирования - элементов матрицы переходных вероятностей и пороговых значений состояний моделируемого процесса, используется вычислительный алгоритм теории нейро-нечетких сетей (ННС) [5, 9].

Нейро-нечеткие сети, объединяющие в себе нейронные сети и нечеткую логику, собирают наилучшие свойства обоих методов, и в то же время освобождаются от их проблем. С одной стороны, такие структуры включают вычислительную мощность и способность к обучению нейронных сетей, а с другой стороны интеллектуальные возможности нейронных сетей усиливаются свойственными "человеческому" способу мышления не-четкими правилами выработки решений.

В нейро-нечетких сетях вывод осуществляется на основе аппарата нечеткой логики, а параметры функций принадлежности настраиваются при помощи алгоритмов обучения нейронной сети. Модуль нечеткого управления представляется в форме многослойной сети, в которой слои выполняют функции элементов системы нечеткого вывода. Для устранения неполноты и противоречивости ННС реализована на базе структуры ANFIS {Adaptive-Network-Based Fuzzy Inference System). Это пятислойная нейронная сеть прямого распространения сигнала, включающая адаптивную сеть нечеткого вывода функционирующая по следующему алгоритму.

Первый (входной) слой L1 реализует функции принадлежности для каждого терма каждой входной переменной - значений матрицы переходных вероятностей (МПВ), пороговых значений (границ) состояний. На первый и второй вход слоя поступают входные сигналы, характеризующие значения МПВ, пороговых значений (границ) состояний. На выходе слоя получаем значение функции принадлежности  для этих сигналов.

для этих сигналов.

Это процедура фаззификации - преобразования численных входных переменных в нечеткую форму.

Параметры функций принадлежности становятся весами связей для нейронов первого слоя сети, и они будут модифицироваться в процессе обучения. В качестве функций принадлежностей входных и выходных переменных используется функция Гаусса в виде

где

Конфигурация связей второго слоя соответствует структуре правил нечеткого вывода ННС для устранения неполноты и противоречивости знаний о значениях МПВ.

Правило R1: если Х1 есть  и Х2 есть В1;

и Х2 есть В1;

Правило R2: если X1 есть  и Х2 есть В2;

и Х2 есть В2;

Правило Rn: если Х1 есть  и Х2 есть Bn,

и Х2 есть Bn,

где  - нечеткие множества.

- нечеткие множества.

Тогда правило (R1, R2, …, Rn) можно представить в виде нечеткой импликации (соединением двух высказываний в одно)

Сам второй слой L2 реализует блок логического вывода. Число нейронов в слое равно количеству правил.

Каждый узел слоя связан с предыдущим слоем таким образом, что узел слоя L2, соответствующий k-му правилу, соединен со всеми нейронами слоя L1, соответствующими нечетким множествам условий этого правила. Выходным значением второго слоя L2 будет являться вес правила α:

Элементы третьего слоя L3 осуществляют нормализацию степеней выполнения правил и вычисляют нормализованные значения МПВ, пороговых значений (границ) состояний β:

Четкое значение МПВ, пороговых значений (границ) состояний β, задающее заключение каждого правила, в четвертом слое L4 рассматривается как нечеткое множество с гауссовской функцией принадлежности. Адаптивные узлы четвертого слоя L4 рассчитывают вклад каждого нечеткого правила в выход сети по формуле

где Y - численное значение МПВ, пороговых значений (границ) состояний.

Это значение, благодаря применению ННС, учитывает одновременно оба вида неопределенности: неоднозначность (нечеткость) и (или) недостоверность (недостаточность, неполноту, противоречивость) исходной информации.

Таким образом, пятый слой L5 представляет собой реализацию блока дефаззификации - преобразования нечетких выходных переменных (значений показателя качества) в численную форму. На выходе слоя L5, в сумматоре, формируется четкое суммарное значение Y важности (предпочтительности) конкретного показателя качества.

Рассмотренный вычислительный нейро-нечеткий алгоритм позволяет уточнить, реконструировать, устранить одновременно как неоднозначность (нечеткость), так и недостоверность (недостаточность, неполноту, противоречивость) при формировании исходных данных для моделирования процесса смены состояний сложных информационных вычислительных систем, комплексов средств центров обработки данных. Уточнение, реконструкция одновременно как неоднозначно (нечетко), так и недостоверно (недостаточно, неполно, противоречиво) заданных параметров позволяют повысить объективность задания исходных данных, а в конечном итоге, повысить достоверность моделирования процессов, происходящих в сложных информационных вычислительных системах, комплексах средств центров обработки данных, с учетом как неоднозначно (нечетко), так и недостоверно (недостаточно, неполно, противоречиво) заданной информации о его состоянии.

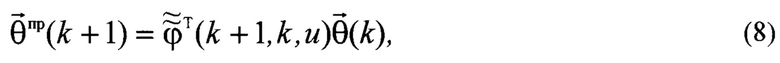

С учетом этого осуществляется моделирование в заявленном вероятностном автомате. С выхода датчика случайной последовательности 1 значения случайной вспомогательной последовательности x' с нормальной плотностью распределения в двоичном коде поступают на стартовый вход 33 блока коррекции 3. В блоке формирования нецелочисленных значений индикаторов 2, на основе полученных в двоичном коде с интерполяционных входов 221-22m элементов вектора целочисленных значений индикаторов состояния моделируемого процесса на предыдущем шаге и полученных в двоичном коде с управляющих входов 211-21m элементов матрицы вероятностей перехода процесса из одного состояния в другое, осуществляется вычисление элементов вектора нецелочисленных значений индикаторов состояния в соответствии с выражением:

являющимся модификацией известного уравнения Колмогорова-Чепмена [4].

Здесь  - вектор нецелочисленных значений индикаторов состояния моделируемого процесса, имеющий математический смысл пошаговых и, в конечном итоге, финальных вероятностей нахождения случайного процесса в том или ином состоянии;

- вектор нецелочисленных значений индикаторов состояния моделируемого процесса, имеющий математический смысл пошаговых и, в конечном итоге, финальных вероятностей нахождения случайного процесса в том или ином состоянии;  - матрица вероятностей перехода процесса из одного состояния в другое с учетом как неоднозначности, так и недостоверности заданных параметров;

- матрица вероятностей перехода процесса из одного состояния в другое с учетом как неоднозначности, так и недостоверности заданных параметров;

Знак «≈» характеризует одновременно неоднозначность (нечеткость) и (или) недостоверность (недостаточность, неполноту, противоречивость) заданных параметров.  - вектор целочисленных значений индикаторов состояния моделируемого процесса на предыдущем шаге. С выходов 231-23m блока 2 элементы вектора нецелочисленных значений индикаторов

- вектор целочисленных значений индикаторов состояния моделируемого процесса на предыдущем шаге. С выходов 231-23m блока 2 элементы вектора нецелочисленных значений индикаторов  в двоичном коде подаются на информационные входы 311-31m блока коррекции 3 и на вспомогательные входы 721-72m блока формирования значений индикаторов 7.

в двоичном коде подаются на информационные входы 311-31m блока коррекции 3 и на вспомогательные входы 721-72m блока формирования значений индикаторов 7.

В блоке 3 по нецелочисленным значениям индикаторов состояния (вероятностям состояний), поступающим в двоичном коде на информационные входы 311-31m и с учетом пороговой информации, поступающей в двоичном коде на пороговые входы 321-32m-1 производится динамическая коррекция математического ожидания (МО) и дисперсии случайной последовательности x' в соответствии с условиями, определяемыми принятой моделью. В результате, на выходе 34 блока коррекции 3 в двоичном коде, в моменты выхода автомата из предыдущего состояния (смена такта), имеем выборочное значение случайной величины х*, полученное из модифицированной случайной последовательности x' с МО и дисперсией, соответствующими заданным условиям моделирования.

Выборочное значение случайной величины х* с МО и дисперсией, соответствующими заданным условиям моделирования поступает в двоичном коде на информационный вход блока пороговых устройств 6. На пороговые входы 621-62m-1 блока 6 с пороговых выходов 1521-152m-1 блока нейро-нечеткой сети 15 поступают в двоичном коде пороговые значения состояний процесса Хпор 1 - Хпор m-1. В результате - предварительные значения индикаторов состояний выдаются в двоичном коде на выходы 641-64m блока пороговых устройств 6. Таким образом, на m выходах блока пороговых устройств 6 имеем элементы вектора  предварительных значений индикаторов состояний моделируемого процесса, которые используются в дальнейшем для формирования значений индикаторов в соответствии с выражениями, описанными в [4].

предварительных значений индикаторов состояний моделируемого процесса, которые используются в дальнейшем для формирования значений индикаторов в соответствии с выражениями, описанными в [4].

Вычисление значений индикаторов состояния  реализует блок формирования значений индикаторов 7 с учетом поступающих в двоичном коде на вспомогательные входы 721-72m параметров элементов вектора нецелочисленных значений индикаторов

реализует блок формирования значений индикаторов 7 с учетом поступающих в двоичном коде на вспомогательные входы 721-72m параметров элементов вектора нецелочисленных значений индикаторов  из блока 2. Полученные элементы вектора индикаторов состояний

из блока 2. Полученные элементы вектора индикаторов состояний  через выходы блока формирования значений индикаторов 7 подаются в двоичном коде на входы блока элементов И 10.

через выходы блока формирования значений индикаторов 7 подаются в двоичном коде на входы блока элементов И 10.

Блок управления 5 представляет собой куб оперативной памяти, в котором записана программа работы устройства. Формирование управляющей кодовой последовательности и последовательности пороговых значений производится следующим образом. С внешнего источника через управляющий вход 51 блока управления 5 на информационный вход 5.5 управляющего ОЗЭ 501 производится запись в двоичном коде как неоднозначных (нечетких), так и недостоверных (недостаточных, неполных, противоречивых) значений элементов матрицы переходных вероятностей (ПВ), соответствующих вводимому управлению, в ячейки памяти управляющего ОЗЭ 501. Через этот же управляющий вход 51 блока управления 5 на информационный вход 5.8 порогового ОЗЭ 502 производится запись в двоичном коде количественных пороговых значений Хпор 1 - Хпор m-1 либо качественных неоднозначных и (или) недостоверных пороговых значений  состояний моделируемого процесса, в ячейки памяти порогового ОЗЭ 502. Отсчеты моментов выхода автомата из предыдущего состояния поступают от элемента ЗАПРЕТ 9 через тактовый вход 54 блока управления 5 на третий 5.0 вход счетчика 503 и определяют, поступая с выходов 5.1 и 5.3 счетчика 503 на тактовые входы 5.6 управляющего ОЗЭ 501 и 5.9 порогового ОЗЭ 502 соответственно, момент начала считывания значений элементов хранящейся в ОЗЭ 501 новой как неоднозначной (нечеткой), так и недостоверной (недостаточной, неполной, противоречивой) матрицы ПВ в двоичном коде через управляющий выход 52 блока управления 5 на управляющий вход 150 блока нейро-нечеткой сети 15, а также момент начала считывания в двоичном коде новых количественных (Хпор 1 - Xпор m-1) либо качественных

состояний моделируемого процесса, в ячейки памяти порогового ОЗЭ 502. Отсчеты моментов выхода автомата из предыдущего состояния поступают от элемента ЗАПРЕТ 9 через тактовый вход 54 блока управления 5 на третий 5.0 вход счетчика 503 и определяют, поступая с выходов 5.1 и 5.3 счетчика 503 на тактовые входы 5.6 управляющего ОЗЭ 501 и 5.9 порогового ОЗЭ 502 соответственно, момент начала считывания значений элементов хранящейся в ОЗЭ 501 новой как неоднозначной (нечеткой), так и недостоверной (недостаточной, неполной, противоречивой) матрицы ПВ в двоичном коде через управляющий выход 52 блока управления 5 на управляющий вход 150 блока нейро-нечеткой сети 15, а также момент начала считывания в двоичном коде новых количественных (Хпор 1 - Xпор m-1) либо качественных  пороговых значений состояний моделируемого процесса, хранящихся в ячейках памяти порогового ОЗЭ 502. Считывание пороговых значений производится с m-1 выходов 5.111-5.11m-1 порогового ОЗЭ 502 через m-1 пороговые выходы 531-53m-1 блока управления 5 на пороговые m-1 входы 1531-153m-1 блока нейро-нечеткой сети 15. Со сбрасывающих выходов 5.7 и 5.10 управляющего ОЗЭ 501 и порогового ОЗЭ 502 соответственно на первый 5.2 и второй 5.4 входы счетчика 503 в момент считывания матрицы ПВ или пороговых значений поступает сигнал, сбрасывающий значения счетчика 503 и дающий команду счетчику 503 начать новый отсчет для вновь введенных неоднозначных (нечетких), и (или) недостоверных (недостаточных, неполных, противоречивых) управляющих воздействий и пороговых значений (Xпор 1 - Хпор m-1 или

пороговых значений состояний моделируемого процесса, хранящихся в ячейках памяти порогового ОЗЭ 502. Считывание пороговых значений производится с m-1 выходов 5.111-5.11m-1 порогового ОЗЭ 502 через m-1 пороговые выходы 531-53m-1 блока управления 5 на пороговые m-1 входы 1531-153m-1 блока нейро-нечеткой сети 15. Со сбрасывающих выходов 5.7 и 5.10 управляющего ОЗЭ 501 и порогового ОЗЭ 502 соответственно на первый 5.2 и второй 5.4 входы счетчика 503 в момент считывания матрицы ПВ или пороговых значений поступает сигнал, сбрасывающий значения счетчика 503 и дающий команду счетчику 503 начать новый отсчет для вновь введенных неоднозначных (нечетких), и (или) недостоверных (недостаточных, неполных, противоречивых) управляющих воздействий и пороговых значений (Xпор 1 - Хпор m-1 или  ).

).

Блок нейро-нечеткой сети 15 может быть реализован по схеме, представленной на фиг.2. Последовательное сравнение (по количеству разрядов) поступающих в двоичном коде исходных данных, принятие решения об их математической природе и преобразование исходных данных, заданных одновременно как неоднозначно (нечетко), так и недостоверно (недостаточно, неполно, противоречиво) к виду, пригодному для осуществления процедуры параметрического моделирования осуществляется следующим образом. Изначально информация, поступающая из блока управления 5 различается по количеству разрядов: для записи в двоичном коде количественной информации (как управляющей, так и пороговой) достаточно 5 (пяти) разрядов двоичного кода, тогда как одновременно неоднозначная (нечеткая), так и недостоверная (недостаточная, неполная, противоречивая) информация заведомо избыточна, несет в себе помимо обычного числа еще и характеристику причинно-следственных когнитивных отношений, формулируемых экспертами, что объективно требует использования 10 (десяти) разрядов двоичного кода.

С учетом этого факта построен анализатор вида исходных данных 0151 блока нейро-нечеткой сети 15, изображенный на фиг. 3. Процедура последовательного сравнения (по количеству разрядов) поступающих в двоичном коде исходных данных и принятие решения об их математической природе в анализаторе вида исходных данных 0151 осуществляется следующим образом. Элемент сдвига 01510 и элемент хранения 01511 анализаторе вида исходных данных 01510 рассчитаны на хранение пяти разрядов поступающей информации, если количество разрядов превышает данную цифру, значит, с точки зрения математики - эта информация поступает либо в неоднозначной (нечеткой), и (или) в недостоверной (недостаточной, неполной, противоречивой) форме. В этом случае оба элемента (01510 и 01511) анализатора вида исходных данных 0151 выполняют функции транзитного узла, отправляя информацию сразу на входы преобразователя неоднозначных недостоверных данных 0152 блока нейро-нечеткой сети 15. Если на вход 0151-1 элемента сдвига 01510 поступает в двоичном коде управляющая информация в количестве пяти разрядов, элемент сдвига 01510 записывает эту информацию и с прямого выхода 01510-2 направляет ее через управляющий выход 0151.3 анализатора вида исходных данных 0151 и управляющий выход 151 блока 15 на вход 40 блока формирования значений матрицы 4 и на вход дешифратора 12. В случае, когда количество разрядов управляющей информации больше пяти, элемент сдвига 01510 не записывает эту информацию, а с транзитного выхода 01510-3 направляет ее через управляющий выход 0151.5 анализатора вида исходных данных 0151 на управляющий вход 0152.1 преобразователя неоднозначных недостоверных данных 0152. Если на каждый из входов 0151-41-0151-4m-1 элемента хранения 01511 поступает в двоичном коде пороговая информация в количестве пяти разрядов, элемент хранения 01511 записывает эту информацию и с прямых выходов 01511-51-01511-5m-1 направляет ее через пороговые выходы 0151.41-0151.4m-1 анализа-тора вида исходных данных 01510 и пороговые выходы 1521-152m-1 блока 15 на пороговые входы 321-32m-1 блока коррекции 3 и на пороговые входы 621-62m-1 блока пороговых устройств 6. В случае, когда количество разрядов пороговой информации больше пяти, элемент хранения 01511 не записывает эту информацию, а с транзитных выходов 01511-61-01511-6m-1 направляет ее через пороговые выходы 0151.61-0151.6m-1 анализатора вида исходных данных 0151 на пороговые входы 0152.21-0152.2m-1 преобразователя неоднозначных недостоверных данных 0152 блока нейро-нечеткой сети 15.

Преобразователь неоднозначных недостоверных данных 0152 блока нейро-нечеткой сети 15 может быть технически реализован в виде перепрограммируемого (с точки зрения матрицы весов (1) - причинно-следственных когнитивных отношений, формулируемых экспертами) ПЗЭВ, реализующего вычислительный нейро-нечеткий алгоритм (1)-(7). Преобразование исходных данных, заданных как неоднозначно (нечетко), так и недостоверно (недостаточно, неполно, противоречиво), к виду, пригодному для осуществления процедуры параметрического моделирования осуществляется следующим образом. Неоднозначная (нечеткая), и (или) недостоверная (недостаточная, неполная, противоречивая) управляющая информация (элементы матрицы переходных вероятностей  ) в двоичном коде поступает с управляющего выхода 0151.5 анализатора вида исходных данных 0151 на управляющий вход 0152.1 преобразователя неоднозначных и недостоверных данных 0152 и на разрешающий вход V ПЗЭВ. Неоднозначная (нечеткая), и (или) недостоверная (недостаточная, неполная, противоречивая) пороговая информация

) в двоичном коде поступает с управляющего выхода 0151.5 анализатора вида исходных данных 0151 на управляющий вход 0152.1 преобразователя неоднозначных и недостоверных данных 0152 и на разрешающий вход V ПЗЭВ. Неоднозначная (нечеткая), и (или) недостоверная (недостаточная, неполная, противоречивая) пороговая информация  в двоичном коде поступает с пороговых выходов 0151.61-0151.6m-1 анализатора вида исходных данных 0151 на пороговые входы 0152.21-0152.2m-1 преобразователя неоднозначных и недостоверных данных 0152 и на m-1 входов (1, …, m-1) перепрограммируемого ПЗЭВ. Перепрограммируемый ПЗЭВ в соответствии с запрограммированными элементами матрицы весов, осуществляет процедуру вычисления (экстраполяции) в соответствии с вычислительным нейро-нечетким алгоритмом (1)-(7). При этом как разрешающий вход V, так и m-1 входы (1, …, m-1) перепрограммируемого ПЗЭВ являются группой равноправных m входов (mвх) вычислителей (нейронов) входного слоя нейро-нечеткой сети, на которую в двоичном коде подаются элементы вектора,

в двоичном коде поступает с пороговых выходов 0151.61-0151.6m-1 анализатора вида исходных данных 0151 на пороговые входы 0152.21-0152.2m-1 преобразователя неоднозначных и недостоверных данных 0152 и на m-1 входов (1, …, m-1) перепрограммируемого ПЗЭВ. Перепрограммируемый ПЗЭВ в соответствии с запрограммированными элементами матрицы весов, осуществляет процедуру вычисления (экстраполяции) в соответствии с вычислительным нейро-нечетким алгоритмом (1)-(7). При этом как разрешающий вход V, так и m-1 входы (1, …, m-1) перепрограммируемого ПЗЭВ являются группой равноправных m входов (mвх) вычислителей (нейронов) входного слоя нейро-нечеткой сети, на которую в двоичном коде подаются элементы вектора,  имеющие физический смысл неоднозначной (нечеткой), и (или) в недостоверной (недостаточной, неполной, противоречивой) управляющей

имеющие физический смысл неоднозначной (нечеткой), и (или) в недостоверной (недостаточной, неполной, противоречивой) управляющей  и пороговой

и пороговой  информации. Набор прямых и обратных связей mвх с mвых нейро-нечеткой сети, программно реализованный в рамках перепрограммируемого ПЗЭВ позволяет учитывать при вычислениях значения элементов матрицы весов и получать, в результате арифметических вычислений в соответствии с вычислительным нейро-нечетким алгоритмом (1)-(7), экстраполированные значения элементов вектора

информации. Набор прямых и обратных связей mвх с mвых нейро-нечеткой сети, программно реализованный в рамках перепрограммируемого ПЗЭВ позволяет учитывать при вычислениях значения элементов матрицы весов и получать, в результате арифметических вычислений в соответствии с вычислительным нейро-нечетким алгоритмом (1)-(7), экстраполированные значения элементов вектора  полностью (достоверно) характеризующие интегрированное мнение экспертов о значениях элементов матрицы переходных вероятностей (ϕТ(k+1,k,u)) и пороговых значениях (границах) состояний моделируемого процесса (Хпор 1 - Xпор m-1). При этом подача (и запись на хранение) в двоичном коде на любой i-ый вход ПЗЭВ (в любую i-ую ячейку памяти ПЗЭВ) значения неоднозначно (нечетко), и (или) недостоверно (недостаточно, неполно, противоречиво) заданного параметра (управляющего или порогового), инициирует выдачу в двоичном коде с i-го выхода ПЗЭВ запрограммированного, в соответствии с вычислительным нейро-нечетким алгоритмом (1)-(7), значения математически корректно преобразованного, относительно достоверно заданного управляющего или порогового параметра. Таким образом, с m-1 (1, …, m-1) выходов ПЗЭВ полученные количественные пороговые значения (границы) состояний моделируемого процесса (Хпор 1 - Хпор m-1) в двоичном коде через пороговые выходы 0152.41-0152.4m-1 преобразователя неоднозначных и недостоверных данных 0152 и пороговые выходы 1521-152m-1 блока нейро-нечеткой сети 15 поступают на пороговые входы 321-32m-1 блока коррекции 3 и на пороговые входы 621-62m-1 блока пороговых устройств 6, а с разрешающего выхода S ПЗЭВ полученные количественные значения элементов матрицы ПВ (ϕT(k+1,k,u)) в двоичном коде через управляющий выход 0152.3 преобразователя неоднозначных и недостоверных данных 0152 и управляющий выход 151 блока нейро-нечеткой сети 15 поступают на вход дешифратора 12 и на вход 40 блока формирования значений матрицы 4.

полностью (достоверно) характеризующие интегрированное мнение экспертов о значениях элементов матрицы переходных вероятностей (ϕТ(k+1,k,u)) и пороговых значениях (границах) состояний моделируемого процесса (Хпор 1 - Xпор m-1). При этом подача (и запись на хранение) в двоичном коде на любой i-ый вход ПЗЭВ (в любую i-ую ячейку памяти ПЗЭВ) значения неоднозначно (нечетко), и (или) недостоверно (недостаточно, неполно, противоречиво) заданного параметра (управляющего или порогового), инициирует выдачу в двоичном коде с i-го выхода ПЗЭВ запрограммированного, в соответствии с вычислительным нейро-нечетким алгоритмом (1)-(7), значения математически корректно преобразованного, относительно достоверно заданного управляющего или порогового параметра. Таким образом, с m-1 (1, …, m-1) выходов ПЗЭВ полученные количественные пороговые значения (границы) состояний моделируемого процесса (Хпор 1 - Хпор m-1) в двоичном коде через пороговые выходы 0152.41-0152.4m-1 преобразователя неоднозначных и недостоверных данных 0152 и пороговые выходы 1521-152m-1 блока нейро-нечеткой сети 15 поступают на пороговые входы 321-32m-1 блока коррекции 3 и на пороговые входы 621-62m-1 блока пороговых устройств 6, а с разрешающего выхода S ПЗЭВ полученные количественные значения элементов матрицы ПВ (ϕT(k+1,k,u)) в двоичном коде через управляющий выход 0152.3 преобразователя неоднозначных и недостоверных данных 0152 и управляющий выход 151 блока нейро-нечеткой сети 15 поступают на вход дешифратора 12 и на вход 40 блока формирования значений матрицы 4.

Регистрация поступающих значений элементов матрицы переходных вероятностей, хранение и считывание управляющей информации в блоке формирования значений матрицы 4 осуществляется следующим образом. Значения элементов матрицы ПВ в двоичном коде поступают на вход счетчика 402, где происходит их подсчет и регистрация - совпадает ли количество поступивших значений элементов матрицы ПВ с размерностью самой матрицы, определяемой условиями моделирования. С выхода счетчика управляющая информация поступает на вход запоминающего элемента 401, предназначенного для хранения и считывания значений элементов матрицы ПВ. При поступлении новых управляющих воздействий запоминающий элемент 401 освобождает ячейки памяти, передавая управляющую информацию построчно (отдельно каждую строку матрицы ПВ - через отдельный выход) через m выходов 411-41m блока формирования значений матрицы 4 соответственно на m управляющих входов 211-21m блока формирования нецелочисленных значений индикаторов 2.

Значения элементов матрицы переходных вероятностей поддерживаются постоянными на выходах блока 4 в течение цикла управления, определяемого генератором тактовых импульсов 8. Пороговые значения состояний моделируемого процесса Хпор 1 - Хпор m-1 в течение цикла управления поддерживаются постоянными на пороговых выходах 1521-152m-1 нейро-нечеткой сети 15 и служат для реализации вычислений, проводимых в блоке коррекции 3, а также используются для получения элементов вектора предварительных значений индикаторов состояния процесса, осуществляемого в блоке пороговых устройств 6.

Моменты выхода автомата из предыдущего состояния определяются генератором тактовых импульсов 8, элементом ИЛИ 14, элементом ЗАПРЕТ 9 при формировании ну-левой комбинации на выходе блока задания времени 13. С помощью блока элементов И 10 производится запись полученных значений элементов вектора индикаторов состояний  моделируемого процесса в блок памяти 11, где они хранятся до момента истечения периода k (периода смены состояния), определяемого блоком задания времени 13 по значениям кода, формируемого на основе управляющий воздействий. При этом значения управляющей кодовой последовательности с управляющего выхода 151 блока нейро-нечеткой сети 15 поступают на дешифратор 12, преобразуются им в код, соответствующий временному интервалу периода смены состояний k, записываются в реверсивный счетчик блока 13 и считываются генератором тактовых импульсов 8 до момента появления нулевой комбинации на выходе блока 13, свидетельствующей об истечении времени пребывания автомата в данном состоянии. Управление вероятностно-временным механизмом смены состояний автомата и пороговыми значениями состояний осуществляется по управляющим кодовым и пороговым комбинациям, поступающим с управляющего и пороговых выходов (соответственно 151 и 1521-152m-1) блока нейро-нечеткой сети и 15 в моменты выхода автомата из предыдущего состояния.

моделируемого процесса в блок памяти 11, где они хранятся до момента истечения периода k (периода смены состояния), определяемого блоком задания времени 13 по значениям кода, формируемого на основе управляющий воздействий. При этом значения управляющей кодовой последовательности с управляющего выхода 151 блока нейро-нечеткой сети 15 поступают на дешифратор 12, преобразуются им в код, соответствующий временному интервалу периода смены состояний k, записываются в реверсивный счетчик блока 13 и считываются генератором тактовых импульсов 8 до момента появления нулевой комбинации на выходе блока 13, свидетельствующей об истечении времени пребывания автомата в данном состоянии. Управление вероятностно-временным механизмом смены состояний автомата и пороговыми значениями состояний осуществляется по управляющим кодовым и пороговым комбинациям, поступающим с управляющего и пороговых выходов (соответственно 151 и 1521-152m-1) блока нейро-нечеткой сети и 15 в моменты выхода автомата из предыдущего состояния.

В итоге, на выходах блока 13 имеем записанные в двоичном коде значения индикаторов состояния управляемого вероятностного автомата  в каждый из моментов времени (определяемых генератором тактовых импульсов 8), с учетом управляющих воздействий и динамически изменяемых пороговых значений (границ) состояний, задаваемых как неоднозначно (нечетко), так и недостоверно (недостаточно, неполно, противоречиво).

в каждый из моментов времени (определяемых генератором тактовых импульсов 8), с учетом управляющих воздействий и динамически изменяемых пороговых значений (границ) состояний, задаваемых как неоднозначно (нечетко), так и недостоверно (недостаточно, неполно, противоречиво).

Таким образом, анализ принципа работы заявляемого вероятностного автомата показывает очевидность того факта, что наряду с сохраненными возможностями моделирования управляемых полумарковских цепей с динамической коррекцией пороговых значений (границ) состояний моделируемых случайных процессов, автомат способен повысить достоверность моделирования управляемых полумарковских цепей, формируемых с учетом как неоднозначно (нечетко), так и недостоверно (недостаточно, неполно, противоречиво) заданных исходных данных, описывающих пороговые значения (границы) и вероятностно-временной механизм (элементы матриц переходных вероятностей) смены состояний моделируемых случайных процессов, имеющих место в реальных в сложных информационных вычислительных системах, комплексах средств центров обработки данных.

Данный вероятностный автомат обеспечивает повышение достоверности моделирования параметров реального процесса функционирования сложных информационных вычислительных систем, комплексов средств центров обработки данных в условиях одновременно как неоднозначной (нечеткой), так и недостоверной (недостаточной, неполной, противоречивой) информации о их состоянии. Это, в свою очередь, позволяет повысить степень адекватности модели, уровень достоверности результатов анализа качества и эффективности функционирования сложных информационных вычислительных систем, комплексов средств центров обработки данных и, как следствие, повысить обоснованность принимаемых решений по управлению структурой, параметрами и режимами их работы, что существенно расширяет функциональные возможности аппаратуры, где заявленный вероятностный автомат будет использован.

ИСТОЧНИКИ ИНФОРМАЦИИ

1. Уоссермен Ф. Нейрокомпьютерная техника: Теория и практика. - М.: Мир, 1992. - 240 с.;

2. Петухов Г.Б. Основы теории эффективности целенаправленных процессов. Часть I. Методология, методы, модели. - М.: МО СССР, 1989. - 660 с.;

3. Терентьев В.М., Санин Ю.В. Анализ эффективности функционирования автоматизированных сетей многоканальной радиосвязи. - СПб.: ВАС, 1992. - 80 с.;

4. Терентьев В.М., Паращук И.Б. Теоретические основы управления сетями многоканальной радиосвязи. - СПб.: ВАС, 1995. - 195 с.;

5. Kosko В. Fuzzy cognitive maps // International Journal of Man-Machine Studies. V. 24. N.Y., 1986. P. 16-22;

6. Щербаков M.A. Искусственные нейронные сети. - Пенза: ПГТУ, 1996. - 44 с.;

7. Трахтенгерц Э.А. Компьютерная поддержка принятия решений. - М.: СИНТЕГ, 1998. - 342 с

8. Горбань А.Н., Россиев Д.А. Нейронные сети на персональном компьютере. - Новосибирск: Наука. Сибирская издательская фирма РАН, 1996. - 146 с.

9. Рутковская Д., Пильинский М., Рутковский Л. Нейронные сети, генетические алгоритмы и нечеткие системы: Пер. с польск. И.Д. Рудинского. - М.: Горячая линия - Телеком, 2004. - 452 с.: ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| ВЕРОЯТНОСТНЫЙ АВТОМАТ | 2005 |

|

RU2276402C1 |

| ВЕРОЯТНОСТНЫЙ АВТОМАТ | 2021 |

|

RU2777531C1 |

| ВЕРОЯТНОСТНЫЙ АВТОМАТ | 2000 |

|

RU2169944C1 |

| ВЕРОЯТНОСТНЫЙ АВТОМАТ | 2001 |

|

RU2195697C1 |

| ВЕРОЯТНОСТНЫЙ АВТОМАТ | 1998 |

|

RU2139569C1 |

| ГЕНЕРАТОР СЛУЧАЙНОЙ ПОСЛЕДОВАТЕЛЬНОСТИ | 2022 |

|

RU2797406C1 |

| УСТРОЙСТВО ДЛЯ СТОХАСТИЧЕСКОГО И НЕЧЁТКОГО МОДЕЛИРОВАНИЯ ПРОЦЕССА ФУНКЦИОНИРОВАНИЯ ПЕРСПЕКТИВНЫХ ТЕЛЕКОММУНИКАЦИОННЫХ СЕТЕЙ | 2021 |

|

RU2773870C1 |

| УСТРОЙСТВО ДЛЯ ПРОГНОЗИРОВАНИЯ СЛУЧАЙНЫХ СОБЫТИЙ | 2024 |

|

RU2828686C1 |

| УСТРОЙСТВО ОБСЛУЖИВАНИЯ РАЗНОПРИОРИТЕТНЫХ ЗАПРОСОВ АБОНЕНТОВ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ | 2005 |

|

RU2290684C1 |

| УСТРОЙСТВО ДЛЯ ПАРАМЕТРИЧЕСКОЙ ОЦЕНКИ ЗАКОНА РАСПРЕДЕЛЕНИЯ ПОТОКОВ СООБЩЕНИЙ | 2004 |

|

RU2281548C1 |

Изобретение относится к радиотехнике и вычислительной технике. Технический результат заключается в расширении арсенала средств. Вероятностный автомат содержит датчик случайной последовательности, блок формирования нецелочисленных значений индикаторов, блок коррекции, блок формирования значений матрицы, блок управления, блок пороговых устройств, блок формирования значений индикаторов, генератор тактовых импульсов, элемент ЗАПРЕТ, блок элементов И, блок памяти, дешифратор, блок задания времени, элемент ИЛИ, блок нейронечеткой сети 15 и позволяет с высокой достоверностью моделировать управляемые полумарковские цепи с учетом управляющих воздействий и динамически изменяемых пороговых значений состояний, задаваемых как неоднозначно, так и не достоверно за счет последовательного сравнения поступающих в двоичном коде исходных данных, принятия решения об их математической природе и нейронечеткого преобразования в блоке 15 исходных данных, заданных как неоднозначно, так и недостоверно к виду, пригодному для осуществления процедуры параметрического моделирования. 1 з.п. ф-лы, 4 ил.

1. Вероятностный автомат, содержащий датчик случайной последовательности (1), блок формирования нецелочисленных значений индикаторов (2), блок коррекции (3), блок формирования значений матрицы (4), блок управления (5), блок пороговых устройств (6), блок формирования значений индикаторов (7), блок элементов И (10), блок памяти (11), блок задания времени (13), дешифратор (12), элемент ЗАПРЕТ (9), элемент ИЛИ (14) и генератор тактовых импульсов (8), выход (81) которого соединен с прямым входом (91) элемента ЗАПРЕТ (9) и тактовым входом (133) блока задания времени (13), выходы (1341-134m), где число «m», «m≥3» (входов, выходов, сумматоров, умножителей, счетчиков, элементов сравнения и т.п.) определяется в соответствии с необходимой и достаточной степенью детализации пространства состояний (количеством состояний) моделируемого процесса и, как правило, составляет от 3 (трех) до 20 (двадцати), которого являются соответствующими выходами автомата и подключены к соответствующим входам (1421-142m) элемента ИЛИ (14), выход (141) которого соединен с инверсным входом (93) элемента ЗАПРЕТ (9), выход (92) которого подключен к тактовым входам (102, 73, 54) блока элементов И (10), блока формирования значений индикаторов (7) и блока управления (5), управляющий вход (51) которого является управляющим входом автомата, выходы (741-74m) блока формирования значений индикаторов (7) соединены с соответствующими входами (1011-101m) блока элементов И (10), выходы (1041-104m) которого подключены к соответствующим входам(1111-111m) блока памяти (11), выходы (1141-114m) которого соединены с соответствующими интерполяционными входами (221-22m) блока формирования нецелочисленных значений индикаторов (2) и с входами (1311-131m) блока задания времени (13), управляющий вход (132) которого подключен к выходу (122) дешифратора, управляющие входы (211-21m) блока формирования нецелочисленных значений индикаторов (2) соединены с соответствующими выходами (411-41m) блока формирования значений матрицы (4), выходы (231-23m) блока формирования нецелочисленных значений индикаторов (2) соединены с соответствующими вспомогательными входами (721-72m) блока формирования значений индикаторов (7) и с информационными входами (311-31m) блока коррекции (3), стартовый вход (33) которого подключен к выходу (11) датчика случайной последовательности (1), выход (34) блока коррекции (3) соединен с входом (61) блока пороговых устройств (6), выходы (641-64m) которого подключены к соответствующим информационным входам (711-71m) блока формирования значений индикаторов (7), отличающийся тем, что дополнительно введен блок нейронечеткой сети (15), управляющий вход (150) блока нейронечеткой сети (15) подключен к управляющему выходу (52) блока управления (5), пороговые выходы (531-53m-1) которого соединены с соответствующими пороговыми входами (1531-153m-1) блока нейронечеткой сети (15), управляющий выход (151) которого подключен к входам (121, 40) дешифратора (12) и блока формирования значений матрицы (4), пороговые выходы (1521-152m-1) блока нейронечеткой сети (15) подключены к соответствующим пороговым входам (321-32m-1), (621-62m-1) блока коррекции (3) и блока пороговых устройств (6).

2. Автомат по п. 1, отличающийся тем, что блок нейронечеткой сети (15) состоит из анализатора вида исходных данных (0151) и преобразователя неоднозначных и недостоверных данных (0152), пороговые входы (0152.21-0152.2m-1) которого соединены с соответствующими пороговыми выходами (0151.61-0151.6m-1) анализатора вида исходных данных (0151), управляющий выход (0151.5) анализатора вида исходных данных (0151) подключен к управляющему входу (0152.1) преобразователя неоднозначных и недостоверных данных (0152), управляющий вход (0151.1) анализатора вида исходных данных (0151) является управляющим входом (150) блока нейронечеткой сети (15), управляющий выход (0151.3) анализатора вида исходных данных (0151) соединен с управляющим выходом (0152.3) преобразователя неоднозначных и недостоверных данных (0152) и является управляющим выходом (151) блока нейронечеткой сети (15), пороговые входы (0151.21-0151.2m-1) анализатора вида исходных данных (0151) являются соответствующими пороговыми входами (1531-153m-1) блока нейронечеткой сети (15), пороговые выходы (0152.41-0152.4m-1) преобразователя неоднозначных и недостоверных данных (0152) соединены с соответствующими пороговыми выходами (0151.41-0151.4m-1) анализатора вида исходных данных (0151) и являются соответствующими пороговыми выходами (1521-152m-1) блока нейронечеткой сети (15).

| ВЕРОЯТНОСТНЫЙ АВТОМАТ | 1998 |

|

RU2139569C1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| ВЕРОЯТНОСТНЫЙ АВТОМАТ | 1994 |

|

RU2099781C1 |

| ВЕРОЯТНОСТНЫЙ АВТОМАТ | 2000 |

|

RU2169944C1 |

| ВЕРОЯТНОСТНЫЙ АВТОМАТ | 2005 |

|

RU2276402C1 |

Авторы

Даты

2020-03-31—Публикация

2018-11-26—Подача