ОБЛАСТЬ ТЕХНИКИ

Изобретение относится к области вычислительной техники, в частности к устройствам обработки данных, и может быть использовано для построения средств автоматики и функциональных узлов систем управления, а также для обработки результатов физических экспериментов.

ПРЕДШЕСТВУЮЩИЙ УРОВЕНЬ ТЕХНИКИ

Известно устройство для определения количества единиц в упорядоченном двоичном числе (RU №2522875, МПК Н03К 21/12, заявлено 24.05.2012, опубликовано 20.07.2014, Бюл. №20), содержащее буферы с тремя состояниями с прямым и инверсным входами разрешения, n разрядов входного двоичного числа, (k+1) разрядов выходного двоичного кода (k=[log2n] меньшее целое), причем буферы с тремя состояниями объединены в пирамидальную структуру, состоящую из (m-1) ступеней (m=]log2n[большее целое), и в выходной блок, содержащий к буферов с тремя состояниями с инверсным входом разрешения и k буферов с тремя состояниями с прямым входом разрешения, при этом каждая i-я ступень (i=1, …, (m-1)) содержит (2i-1) буферов с тремя состояниями с инверсным входом разрешения и 2i-1 буферов с тремя состояниями с прямым входом разрешения.

Недостатком данного устройства является определение количества единиц в упорядоченном двоичном числе, а не выявление диапазона единичных бит.

Известно устройство для упорядочения единиц (SU №1751746 А1, МПК G06F 7/38, 7/06, заявлено 26.11.1990, опубликовано 30.07.1992, Бюл. №28), содержащее по (n-1)-й группе элементов И и ИЛИ (где n - четное число, разрядность операнда, n=2К), две группы К-разрядных входов упорядоченных единиц и n-разрядный выход упорядоченных единиц.

Недостатком данного устройства является формирование на выходах упорядоченного кода, а не выявление диапазона единичных бит.

Известно устройство для определения количества единиц (нулей) в двоичном числе (RU №2446442, МПК G06F 7/50, Н03К 21/00, заявлено 11.04.2011, опубликовано 27.03.2012, Бюл. №9), содержащее блок управляемой инверсии, состоящий из n-элементов «ИСКЛЮЧАЮЩЕЕ ИЛИ» (n - количество разрядов входного числа), элементы ИЛИ и модули, состоящие из элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и элемента И, которые объединены в группы, состоящие из ярусов, и объединены в k-каскадов (k=]log2n[), так, что каждый i-й каскад содержит g(i)=n/2i групп (i=1, …, k), каждая группа i-го каскада разделена на j ярусов (j=1, …, i), при этом первый ярус каждой группы i-го каскада содержит i модулей, а каждый j-й ярус каждой группы i-го каскада (j=2, …, i,) содержит (i-j) модулей и элемент «ИЛИ».

Недостатком данного устройства является определение только общего количества единиц (нулей) в двоичном числе, а не выявление диапазона единичных бит.

Известен указатель старшей единицы (Угрюмов Е.П. Цифровая схемотехника. - СПб.: БХВ-Петербург, 2000. - 528 с., рис. 2.8 с. 50-54), содержащий группу элементов И и группу элементов запрета И с одним инверсным входом. В данном устройстве реализована цепочечная схема передачи сигнала опроса путем последовательного опроса, начиная со старшего разряда, и прекращения дальнейшего опроса при выявлении первой же единицы.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является, принятый за прототип, указатель старшей единицы (Схемотехника ЭВМ. Сборник задач: учебное пособие. М.: НИЯУ МИФИ, 2012. - 240 с, рис. 53, с. 55-56), содержащий группу элементов ИЛИ объединенных в цепочку и группу элементов запрета И с одним инверсным входом.

Недостатком данных устройств является выявление только одного старшего единичного бита.

ЗАДАЧА ИЗОБРЕТЕНИЯ

Задачей изобретения является выявление левого (старшего) бита и правого (младшего) бита во входных данных и заполнение диапазона разрядов между ними единичными значениями.

При обработке результатов физических экспериментов устройство предназначено для выявления диапазона событий. Кроме того изобретение может применяться для индикации диапазона единичных бит.

Техническим результатом изобретения является расширение функциональных возможностей в части возможности выявления диапазона единичных бит.

КРАТКОЕ ОПИСАНИЕ СУЩНОСТИ ИЗОБРЕТЕНИЯ

Указанный технический результат при осуществлении изобретения достигается тем, что устройство для детектирования диапазона единичных бит содержит N разрядную входную шину D, N разрядную выходную шину О, первую группу из (N-2) элементов ИЛИ 11, 12, …, 1(N-2), вторую группу из (N-2) элементов ИЛИ 21, 22, …, 2(N-2) и группу из (N-2) элементов И 31, 32, …, 3(N-2),

причем (N-2) разрядов D2, D3, …, D(N-2) входной шины D, начиная со второго до (N-1)-го разрядов, соединены со вторыми входами соответствующих (N-2) элементов первой группы ИЛИ 11, 12, …, 1(N-2), начиная с первого до (N-2)-го элементов, и соединены с первыми входами соответствующих (N-2) элементов второй группы ИЛИ 21, 22, …, 2N, начиная с первого до (N-2)-го элементов,

при этом первые входы первых (N-3) элементов 11, 12, …, 1(N-3) из первой группы элементов ИЛИ, начиная с первого до (N-3)-го элементов, соединены с выходами соответствующих последующих (N-3) элементов 12, 13, …, 1(N-2) из первой группы элементов ИЛИ, начиная со второго до (N-2)-го элементов, а первый вход последнего (N-2)-го элемента 1(N-2) из первой группы элементов ИЛИ соединен с последним N-м разрядом DN входной шины D,

причем вторые входы (N-3) элементов второй группы ИЛИ 22, 23, …, 2(N-2), начиная со второго до (N-2)-го элементов, соединены с выходами соответствующих предыдущих (N-3) элементов 21, 22, …, 2(N-2) из второй группы элементов ИЛИ, начиная с первого до (N-3)-го элементов, а первый вход первого элемента 21 из второй группы элементов ИЛИ соединен с первым разрядом D1 входной шины D,

кроме того выходы (N-2) элементов первой группы ИЛИ 11, 12, …, 1(N-2), начиная с первого до (N-2)-го элементов, также соединены с первыми входами соответствующих одноименных элементов группы из (N-2) элементов И 31, 32, …, 3(N-2), у которых вторые входы соединены с соответствующими одноименными выходами (N-2) элементов второй группы ИЛИ 21, 22, …, 2(N-2),

причем выходы (N-2) элементов группы элементов И 31, 32, …, 3(N-2) являются соответствующими (N-2) разрядами выходной шины Q, начиная со второго до (N-1)-го разряда, а первый и N-й разряды выходной шины Q соединены соответственно с первым и N-м разрядами входной шины D.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

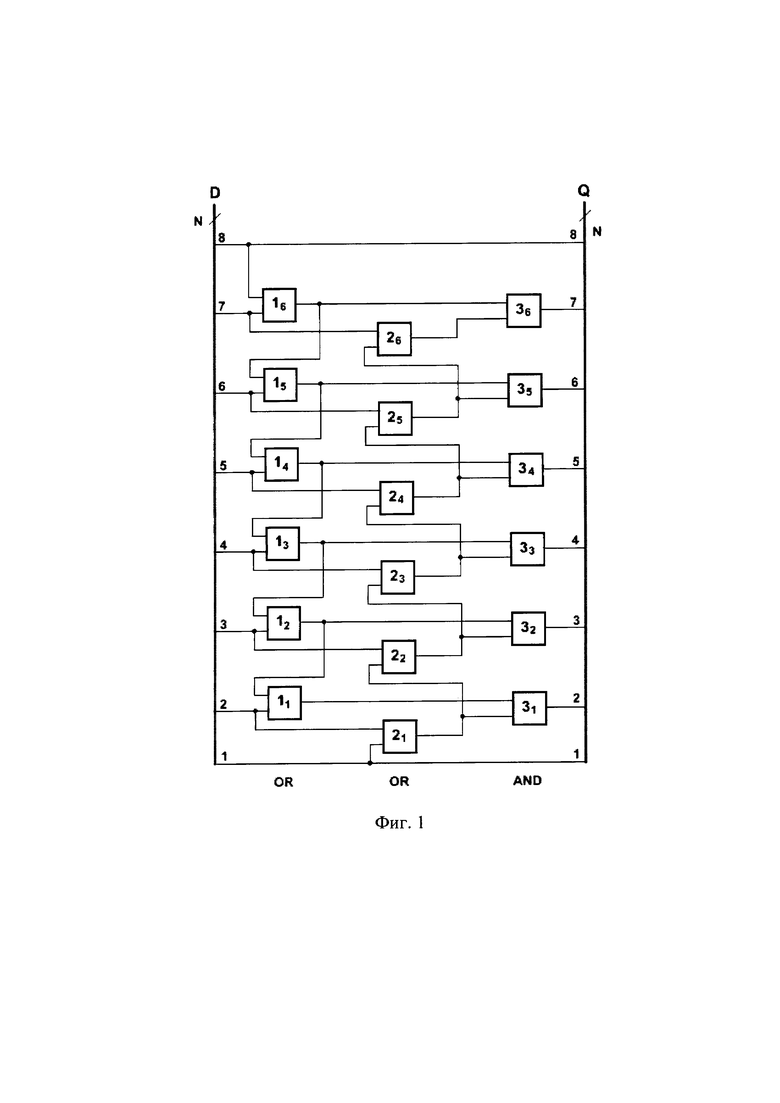

На фиг. 1 представлена функциональная схема предлагаемого устройства для детектирования диапазона единичных бит при количестве разрядов N=8 входной шины D - D1, D2, …, D8(N). В таблице 1 приведены тестовые примеры формирования единичных диапазонов при количестве разрядов N=8.

На фиг. 1 и в тексте введены следующие обозначения:

D - N разрядная входная шина,

D1, D2, …, D8 - разряды входной шины,

О - N разрядная выходная шина,

Q1, Q2, …, Q8 - разряды выходной шины,

i - правый (младший) разряд, имеющий единичное значение, где 1≤i≤N;

j - левый (старший) разряд, имеющий единичное значение, где i≤j;

11, 12, …, 1(N-2) - первая группа из (N-2) элементов ИЛИ,

21, 22, …, 2(N-2) - вторая группа из (N-2) элементов ИЛИ,

31, 32, …, 3(N-2) - группа из (N-2) элементов И.

Предлагаемое устройство для детектирования диапазона единичных бит содержит N разрядов входной шины D - D1, D2, …, DN, N разрядов выходной шины Q - Q1, Q2, …, QN, первую группу из (N-2) элементов ИЛИ 11, 12, …, 1(N-2), вторую группу из (N-2) элементов ИЛИ 21, 22, …, 2(N-2) и группу из (N-2) элементов И 31, 32, …, 3(N-2).

Первая группа элементов ИЛИ 11, 12, …, 1(N-2) предназначена для формирования упорядоченной группы единиц (подряд идущих) в младших разрядах, начиная со второго разряда до j-го левого (старшего) разряда, а вторая группа элементов ИЛИ 21, 22, …, 2(N-2) предназначена для формирования упорядоченной группы единиц в старших разрядах, начиная с i-го правого (младшего) разряда до (N-1)-го разряда. В группе элементов И 31, 32, …, 3(N-2) осуществляется проверка единичных значений в одноименных разрядах упорядоченных групп единиц.

Причем (N-2) разрядов D2, D3, …, D(N-2) входной шины D, начиная со второго до (N-1)-го разрядов, соединены со вторыми входами соответствующих (N-2) элементов первой группы ИЛИ 11, 12, …, 1(N-2), начиная с первого до (N-2)-го элементов, и соединены с первыми входами соответствующих (N-2) элементов второй группы ИЛИ 21, 22, …, 2N, начиная с первого до (N-2)-го элементов.

При этом первые входы первых (N-3) элементов 11, 12, …, 1(N-3) из первой группы элементов ИЛИ, начиная с первого до (N-3)-го элементов, соединены с выходами соответствующих последующих (N-3) элементов 12, 13, …, 1(N-2) из первой группы элементов ИЛИ, начиная со второго до (N-2)-го элементов, а первый вход последнего (N-2)-го элемента 1(N-2) из первой группы элементов ИЛИ соединен с последним N-м разрядом DN входной шины D.

Причем вторые входы (N-3) элементов второй группы ИЛИ 22, 23, …, 2(N-2), начиная со второго до (N-2)-го элементов, соединены с выходами соответствующих предыдущих (N-3) элементов 21, 22, …, 2(N-2) из второй группы элементов ИЛИ, начиная с первого до (N-3)-го элементов, а первый вход первого элемента 21 из второй группы элементов ИЛИ соединен с первым разрядом D1 входной шины D.,

Кроме того выходы (N-2) элементов первой группы ИЛИ 11, 12, …, 1(N-2), начиная с первого до (N-2)-го элементов, также соединены с первыми входами соответствующих одноименных элементов группы из (N-2) элементов И 31, 32, …, 3(N-2), у которых вторые входы соединены с соответствующими одноименными выходами (N-2) элементов второй группы ИЛИ 21, 22, …, 2(N-2).

Выходы (N-2) элементов группы элементов И 31, 32, …, 3(N-2) являются соответствующими (N-2) разрядами выходной шины Q, начиная со второго до (N-1)-го разряда, а первый и N-й разряды выходной шины Q соединены соответственно с первым и N-м разрядами входной шины D.

ПОДРОБНОЕ ОПИСАНИЕ СУЩНОСТИ ИЗОБРЕТЕНИЯ

Принцип работы предлагаемого устройства состоит в следующем.

Предлагаемое устройство позволяет детектировать правый (младший) i разряд (где 1≤i≤N) и левый (старший) j разряд (где i≤j) входной шины D, которые имеют единичное значение, и заполнить диапазон разрядов между ними, начиная с i-го до j-го разрядов, выходной шины Q единичными значениями. При отсутствии единичных значений в разрядах выходной шины Q устанавливаются нулевые значения.

На входы устройства одновременно поступают N разрядов входной шины D - D1, D2, …, DN. При выявлении только одного единичного значения в i-м разряде (где 1≤i≤N, при этом j=i) входной шины D на выходах элементов ИЛИ, начиная с первого до (i-1)-го элементов, первой группы элементов ИЛИ 11, …, 1(i-1) устанавливаются единичные значения и одновременно на выходах элементов ИЛИ, начиная с (i-1)-го до (N-2)-го элементов, второй группы элементов ИЛИ 2(i-1), …, 2(N-2) также устанавливаются единичные значения. При этом на два входа только одного (i-1)-го элемента И 3(i-1) группы из (N-2) элементов И поступают единичные значения и поэтому на выходе только одного элемента И 3(i-1) устанавливается единичное значение.

При одновременном поступлении нескольких единичных значений на входной шине D и выявлении единичных значений в правом (младшем) i-м разряде и в левом (старшем) j-м разряде (где i≤j) на выходах элементов ИЛИ, начиная с первого до (j-1)-го элементов, первой группы элементов ИЛИ 11, …, 1(j-1) и на выходах элементов ИЛИ, начиная с (i-1)-го до (N-2)-го элементов, второй группы элементов ИЛИ 2(i-1), …, 2(N-2) устанавливаются единичные значения. При этом единичные значения поступают на два входа элементов И, начиная с (i-1)-го до (j-1)-го элементов, группы из (N-2) элементов И 31, 32, …, 3(N-2) и поэтому единичные значения устанавливаются на выходах элементов И 3(i-1), …, 3(j-1), которые далее передаются на разряды, начиная i-го разряда до j-го разряда, выходной шины Q - Qi, …, Qj.

Кроме того, значения младшего первого разряда и старшего N-го разряда входной шины D непосредственно поступают на младший первый разряд и старший N-й разряд выходной шины Q.

Таким образом, в диапазоне разрядов с i-го до j-го выходной шины О устанавливаются единичные значения.

Предлагаемое устройство работает следующим образом.

На входную шину шины D одновременно поступают N разрядов - D1, D2, …, DN. Значения с входной шины D поступают на соответствующие входы первой группы элементов ИЛИ 11, 12, …1(N-2) и второй группы элементов ИЛИ 21, 22, …, 2(N-2).

При выявлении единичных значений в правом (младшем) i-ом разряде (где 1≤i≤N) и в левом (старшем) j-ом разряде, единичные значение последовательно передаются на выходы элементов ИЛИ, начиная с (j-1)-го до первого элементов, первой группы элементов ИЛИ 11, …, 1(j-1), а также последовательно передаются на выходы элементов ИЛИ, начиная с (i-1)-го до (N-2)-го элементов, второй группы элементов ИЛИ 2(i-1), …, 2(N-2). Далее значения с выходов первой группы 11, 12, …, 1(N-2) и второй группы 21, 22, …, 2(N-2) элементов ИЛИ поступают на входы группы элементов И 31, 32, …, 3(N-2), выходы которых совместно с первым D1 и N-м разрядами входной шины D являются соответствующими разрядами выходной шины Q.

В таблице 1 приведены тестовые примеры формирования единичных диапазонов при количестве разрядов N=8.

В тесте №1 единичное значение поступает только в одном четвертом разряде D4 входной шины D, при этом i=4 и j=4. Поэтому единичные значения последовательно устанавливаются на выходах элементов первой группы 11, …, 13 и элементов второй группы 23, …, 26, которые далее поступают на входы группы элементов И 31, 32, …, 36. При этом единичное значение устанавливается только на одном (i-1)-м элементе И 33. Значения с выходов группы элементов И 31, 32, …, 36, а также с разрядов D1 и D8 входной шины передаются на соответствующие разряды Q1, …, Q8 выходной шины Q, на которых устанавливается только одно единичное значение в четвертом разряде Q4.

В тесте №2 единичные значения поступают в третьем D3, четвертом D4 и шестом D6 разрядах входной шины D. При этом детектируются единичные значения в правом (младшем) i=3 и левом (старшем) j=6 разрядах. Поэтому единичные значения последовательно устанавливаются на выходах элементов первой группы 11, …, 15 и элементов второй группы 22, …, 26, которые далее поступают на входы группы элементов И 31, 32, …, 36. При этом единичные значения устанавливаются на элементах И 32, …, 35. Далее единичные значения устанавливаются в разрядах с третьего по шестой выходной шины Q, что соответствует значениям i=3 и j=6.

В тестовых примерах №3 - №8 приведены особые случаи, когда по входной шине D поступают единичные значения по последнему восьмому разряду D8 (тест №3) или первому разряду D1 (тест №4) одновременно с единичными значениями в других разрядах входной шины D, или поступают только нулевые значения (тест №5), или единичные значения поступают во всех разрядах (тест №6), или единичные значения поступают только по последнему восьмому разряду D8 (тест №7) или только по первому разряду D1 (тест №8).

В тесте №3 единичные значения поступают в третьем D3, шестом D6, седьмом D7 и восьмом D8 разрядах входной шины D. При этом детектируются единичные значения в правом (младшем) i=3 и левом (старшем) j=8 разрядах. Поэтому единичные значения последовательно устанавливаются на выходах всех элементов первой группы 11, …, 16 и элементов второй группы 22, …, 26, которые далее поступают на входы группы элементов И 31, 32, …, 36. При этом единичные значения устанавливаются на элементах И 32, …, 36. Далее единичные значения устанавливаются в разрядах с третьего по седьмой Q3, …, Q7 выходной шины Q, а также устанавливается единичное значение в разряде Q8 с восьмого разряда D8 входной шины, что соответствует значениям i=3 и j=8 входной шины D.

В тесте №4 единичные значения поступают в первом D1 и третьем D3 разрядах входной шины D. При этом детектируются единичные значения в правом (младшем) i=1 и левом (старшем) j=3 разрядах. Поэтому единичные значения последовательно устанавливаются на выходах элементов первой группы 11, …, 12 и всех элементов второй группы 21, …, 26, которые далее поступают на входы группы элементов И 31, 32, …, 36. При этом единичные значения устанавливаются на двух элементах И - 31, 32. Далее единичные значения устанавливаются во втором и третьем разрядах Q2, Q3 выходной шины Q, а также устанавливается единичное значение в разряде Q1 с разряда D1 входной шины, что соответствует значениям i=1 и j=3 входной шины D.

В тесте №5 единичные значения отсутствуют в разрядах входной шины D, при этом i=0 и j=0. Поэтому нулевые значения устанавливаются на выходах всех элементов первой группы 11, …, 16 и всех элементов второй группы 21, …, 26, которые далее поступают на входы группы элементов И 31, 32, …, 36, и далее на соответствующие разряды выходной шины Q, на которую также поступают нулевые значения с D1 и D8 разрядов входной шины D. Поэтому нулевые значения устанавливаются во всех разрядах выходной шины Q, что соответствует значениям i=0 и j=0 входной шины D.

В тесте №6 единичные значения поступают во всех разрядах входной шины D. При этом детектируются единичные значения в правом (младшем) i=1 и левом (старшем) j=8 разрядах. Поэтому единичные значения устанавливаются на выходах всех элементов первой группы 11, …, 16 и всех элементов второй группы 21, …, 26, которые далее поступают на входы группы элементов И 31, 32, …, 36, и далее на соответствующие разряды выходной шины Q, на которую также поступают единичные значения с D1 и D8 разрядов входной шины D. Поэтому единичные значения устанавливаются во всех разрядах выходной шины Q, что соответствует значениям i=1 и j=8 входной шины D.

В тесте №7 единичное значение поступает только в одном восьмом разряде D8 входной шины D, при этом i=8 и j=8. Поэтому единичные значения последовательно устанавливаются на выходах всех элементов первой группы 11, …, 13 и нулевые значения на выходах всех элементов второй группы 23, …, 26, которые далее поступают на входы группы элементов И 31, 32, …, 36. При этом нулевые значения устанавливаются на выходах всех элементов группы элементов И 31, 32, …, 36, и далее на соответствующих разрядах выходной шины Q. При этом также нулевое значение поступает с первого разряда D1 и единичное значение поступает с восьмого разряда D8 входной шины D соответственно на первый Q1 и восьмой Q8 разряды выходной шины Q. Поэтому на выходной шине Q формируется только одно единичное значение в восьмом разряде Q8.

В тесте №8 единичное значение поступает только в первом восьмом разряде D1 входной шины D, при этом i=1 и j=1. Поэтому нулевые значения последовательно устанавливаются на выходах всех элементов первой группы 11, …, 13 и единичные значения на выходах всех элементов второй группы 23, …, 26, которые далее поступают на входы группы элементов И 31, 32, …, 36. При этом нулевые значения устанавливаются на выходах всех элементов группы элементов И 31, 32, …, 36, и далее на соответствующих разрядах выходной шины Q. При этом также нулевое значение поступает с восьмого разряда D8 и единичное значение поступает с первого разряда D1 входной шины D соответственно на восьмой Q8 и первый Q1 разряды выходной шины Q. Поэтому на выходной шине Q формируется только одно единичное значение в первом разряде Q1.

Таким образом, на выходах предлагаемого устройства между выявленными левым (старшим) битом и правым (младшим) битом формируется диапазон единичных бит.

Вышеизложенные сведения позволяют сделать вывод, что предлагаемое устройство решает поставленную задачу и соответствует заявляемому техническому результату.

УСТРОЙСТВО ДЛЯ ДЕТЕКТИРОВАНИЯ ДИАПАЗОНА ЕДИНИЧНЫХ БИТ

Изобретение относится к области вычислительной техники, в частности к устройствам обработки данных, и может быть использовано для построения средств автоматики и функциональных узлов систем управления, а также для обработки результатов физических экспериментов. Техническим результатом изобретения является обеспечение возможности выявления диапазона единичных бит. Устройство содержит N разрядов входной шины D - D1, D2, …, DN, N разрядов выходной шины Q - Q1, Q2, …, QN, первую группу из (N-2) элементов ИЛИ 11, 12, …, 1(N-2), вторую группу из (N-2) элементов ИЛИ 21, 22, …, 2(N-2) и группу из (N-2) элементов И 31, 32, …, 3(N-2). Причем первая группа элементов ИЛИ 11, 12, …, 1(N-2), объединенных в цепочку, формирует упорядоченную группу подряд идущих единиц в младших разрядах, вторая группа элементов ИЛИ 21, 22, …, 2(N-2) формирует упорядоченную группу единиц в старших разрядах, а в группе элементов И 31, 32, …, 3(N-2) осуществляется проверка единичных значений в одноименных разрядах упорядоченных групп единиц. 1 ил., 1 табл.

Устройство для детектирования диапазона единичных бит содержит N разрядную входную шину D, N разрядную выходную шину Q, первую группу из (N-2) элементов ИЛИ 11, 12, …, 1(N-2), вторую группу из (N-2) элементов ИЛИ 21, 22, …, 2(N-2) и группу из (N-2) элементов И 31, 32, …, 3(N-2),

причем (N-2) разрядов D2, D3, …, D(N-2) входной шины D, начиная со второго до (N-1)-го разрядов, соединены со вторыми входами соответствующих (N-2) элементов первой группы ИЛИ 11, 12, …, 1(N-2), начиная с первого до (N-2)-го элементов, и соединены с первыми входами соответствующих (N-2) элементов второй группы ИЛИ 21, 22, …, 2N, начиная с первого до (N-2)-го элементов,

при этом первые входы первых (N-3) элементов 11, 12, …, 1(N-3) из первой группы элементов ИЛИ, начиная с первого до (N-3)-го элементов, соединены с выходами соответствующих последующих (N-3) элементов 12, 13, …, 1(N-2) из первой группы элементов ИЛИ, начиная со второго до (N-2)-го элементов, а первый вход последнего (N-2)-го элемента 1(N-2) из первой группы элементов ИЛИ соединен с последним N-м разрядом DN входной шины D,

причем вторые входы (N-3) элементов второй группы ИЛИ 22, 23, …, 2(N-2), начиная со второго до (N-2)-го элементов, соединены с выходами соответствующих предыдущих (N-3) элементов 21, 22, …, 2(N-2) из второй группы элементов ИЛИ, начиная с первого до (N-3)-го элементов, а первый вход первого элемента 21 из второй группы элементов ИЛИ соединен с первым разрядом D1 входной шины D,

кроме того, выходы (N-2) элементов первой группы ИЛИ 11, 12, …, 1(N-2), начиная с первого до (N-2)-го элементов, также соединены с первыми входами соответствующих одноименных элементов группы из (N-2) элементов И 31, 32, …, 3(N-2), у которых вторые входы соединены с соответствующими одноименными выходами (N-2) элементов второй группы ИЛИ 21, 22, …, 2(N-2),

причем выходы (N-2) элементов группы элементов И 31, 32, …, 3(N-2) являются соответствующими (N-2) разрядами выходной шины Q, начиная со второго до (N-1)-го разряда, а первый и N-й разряды выходной шины О соединены соответственно с первым и N-м разрядами входной шины D.

| УСТРОЙСТВО ГРУППОВОЙ СТРУКТУРЫ ДЛЯ ДЕТЕКТИРОВАНИЯ ГРУПП НУЛЕВЫХ И ЕДИНИЧНЫХ БИТ И ОПРЕДЕЛЕНИЕ ИХ КОЛИЧЕСТВА | 2018 |

|

RU2680762C1 |

| УСТРОЙСТВО ПОСЛЕДОВАТЕЛЬНОГО ТИПА ДЛЯ ДЕТЕКТИРОВАНИЯ ГРУПП НУЛЕВЫХ И ЕДИНИЧНЫХ БИТ И ОПРЕДЕЛЕНИЕ ИХ КОЛИЧЕСТВА | 2018 |

|

RU2680759C1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ КОЛИЧЕСТВА СТАРШИХ ЕДИНИЦ (НУЛЕЙ) В ДВОИЧНОМ ЧИСЛЕ | 2016 |

|

RU2633110C1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ КОЛИЧЕСТВА ЕДИНИЦ (НУЛЕЙ) В ДВОИЧНОМ ЧИСЛЕ | 2011 |

|

RU2446442C1 |

| Способ приготовления мыла | 1923 |

|

SU2004A1 |

| US 5568410 A, 22.10.1996. | |||

Авторы

Даты

2020-03-24—Публикация

2019-11-07—Подача