Изобретение относится к области электроники и радиотехники и может быть использовано в качестве преобразователя входного дифференциального напряжения в пропорциональный выходной ток. Потребность в устройствах данного класса возникает в задачах проектирования активных RC фильтров и других устройств автоматики и систем связи (интеграторов, генераторов различных сигналов, непрерывных стабилизаторов напряжения, операционных усилителей и т.п.). Таким образом, преобразователи «напряжение-ток» являются базовым элементов многих электронных устройств, в т.ч. работающих при низких температурах и воздействии радиации [1].

Известны схемы преобразователей дифференциального входного напряжения с парафазными токовыми выходами [2-9], в т.ч. на комплементарных КМОП полевых транзисторах [2-4] и комплементарных полевых транзисторах с управляющим p-n переходом (JFet) [5], которые стали основой многих серийных аналоговых микросхем. Причем для работы при низких температурах при жестких ограничениях на уровень шумов перспективно использование JFet полевых транзисторов [11-13]. ДК данного класса активно применяются в структуре малошумящих аналоговых интерфейсов для обработки сигналов датчиков [14-16].

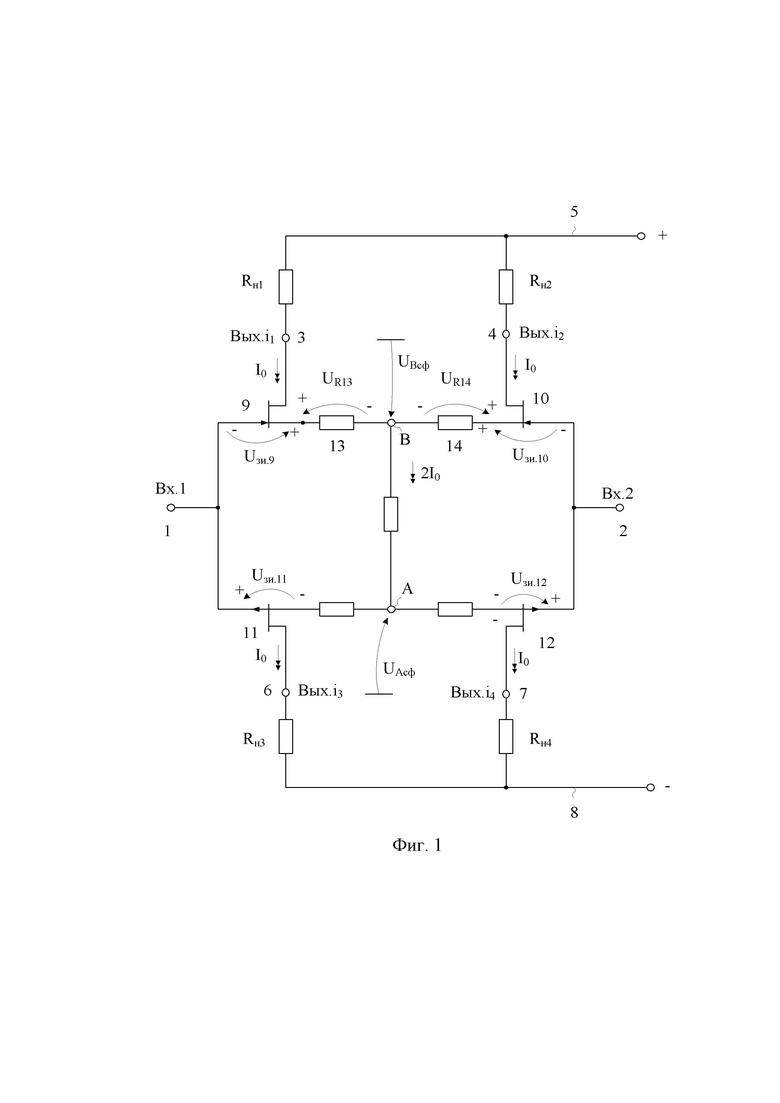

Ближайшим прототипом (фиг. 1) заявляемого устройства является преобразователь входного дифференциального напряжения (ПДН), представленный в патенте RU 2688225, fig.2, 2019 г. Он содержит первый 1 и второй 2 входы устройства, первый 3 и второй 4 противофазные токовые выходы, согласованные с первой 5 шиной источника питания, третий 6 и четвертый 7 противофазные токовые выходы, согласованные со второй 8 шиной источника питания, первый 9 входной полевой транзистор, затвор которого соединен с первым 1 входом устройства, а сток подключен к первому 3 токовому выходу, второй 10 входной полевой транзистор, затвор которого связан со вторым 2 входом устройства, а сток подключен ко второму 4 токовому выходу, третий 11 входной полевой транзистор, сток которого соединен с третьим 6 токовым выходом, четвертый 12 входной полевой транзистор, сток которого соединен с четвертым 7 токовым выходом, причем между истоком первого 9 входного полевого транзистора и истоком второго 10 входного полевого транзистора включены первый 13 и второй 14 последовательно соединенные резисторы.

Существенный недостаток известного устройства состоит в том, что оно имеет повышенные входные емкости по первому 1 и второму 2 входам, которые складываются соответственно из емкостей затвор-сток первого 9 и третьего 11 входных транзисторов, а также второго 10 и четвертого 12 входных транзисторов.

Основная задача предполагаемого изобретения состоит в уменьшении входной емкости устройства по первому 1 и второму 2 входам. Дополнительная задача – повышение крутизны преобразования входного дифференциального напряжения в выходные токи устройства.

Решение поставленных задач достигается тем, что в преобразователе дифференциального напряжения фиг.1, содержащем первый 1 и второй 2 входы устройства, первый 3 и второй 4 противофазные токовые выходы, согласованные с первой 5 шиной источника питания, третий 6 и четвертый 7 противофазные токовые выходы, согласованные со второй 8 шиной источника питания, первый 9 входной полевой транзистор, затвор которого соединен с первым 1 входом устройства, а сток подключен к первому 3 токовому выходу, второй 10 входной полевой транзистор, затвор которого связан со вторым 2 входом устройства, а сток подключен ко второму 4 токовому выходу, третий 11 входной полевой транзистор, сток которого соединен с третьим 6 токовым выходом, четвертый 12 входной полевой транзистор, сток которого соединен с четвертым 7 токовым выходом, причем между истоком первого 9 входного полевого транзистора и истоком второго 10 входного полевого транзистора включены первый 13 и второй 14 последовательно соединенные резисторы, предусмотрены новые элементы и связи – исток первого 9 входного полевого транзистора связан с истоком третьего 11 входного полевого транзистора, исток второго 10 входного полевого транзистора соединен с истоком четвертого 12 входного полевого транзистора, объединенные затворы третьего 11 и четвертого 12 входных полевых транзисторов связаны с общим узлом последовательно соединенных первого 13 и второго 14 резисторов, причем общий узел последовательно соединенных первого 13 и второго 14 резисторов подключен к источнику опорного тока 15.

На чертеже фиг. 1 показана схема ПДН-прототипа.

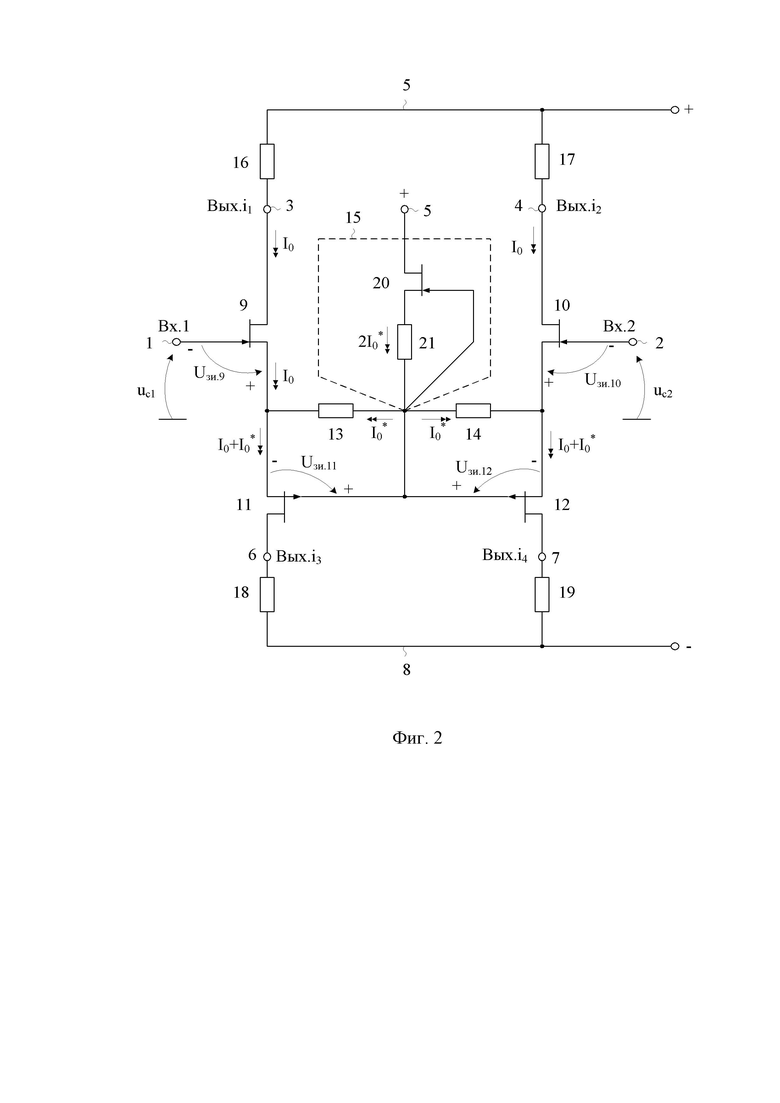

На чертеже фиг. 2 приведена схема заявляемого ПДН в соответствии с п. 1 и п. 2 формулы изобретения.

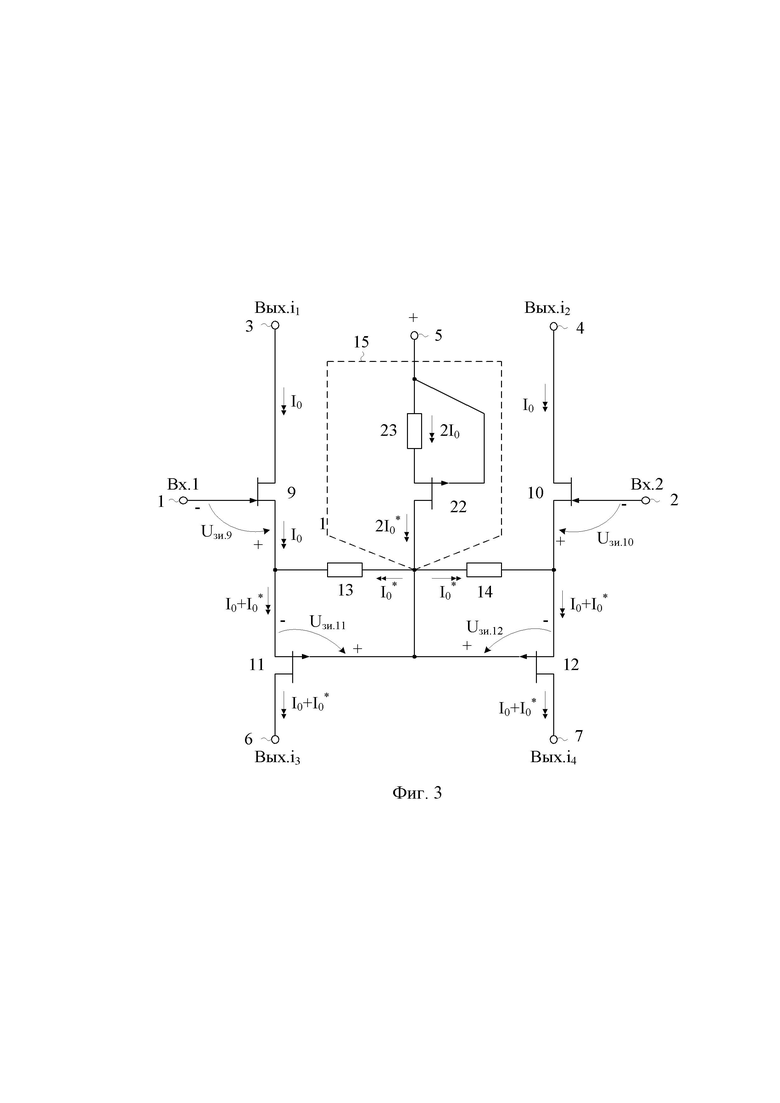

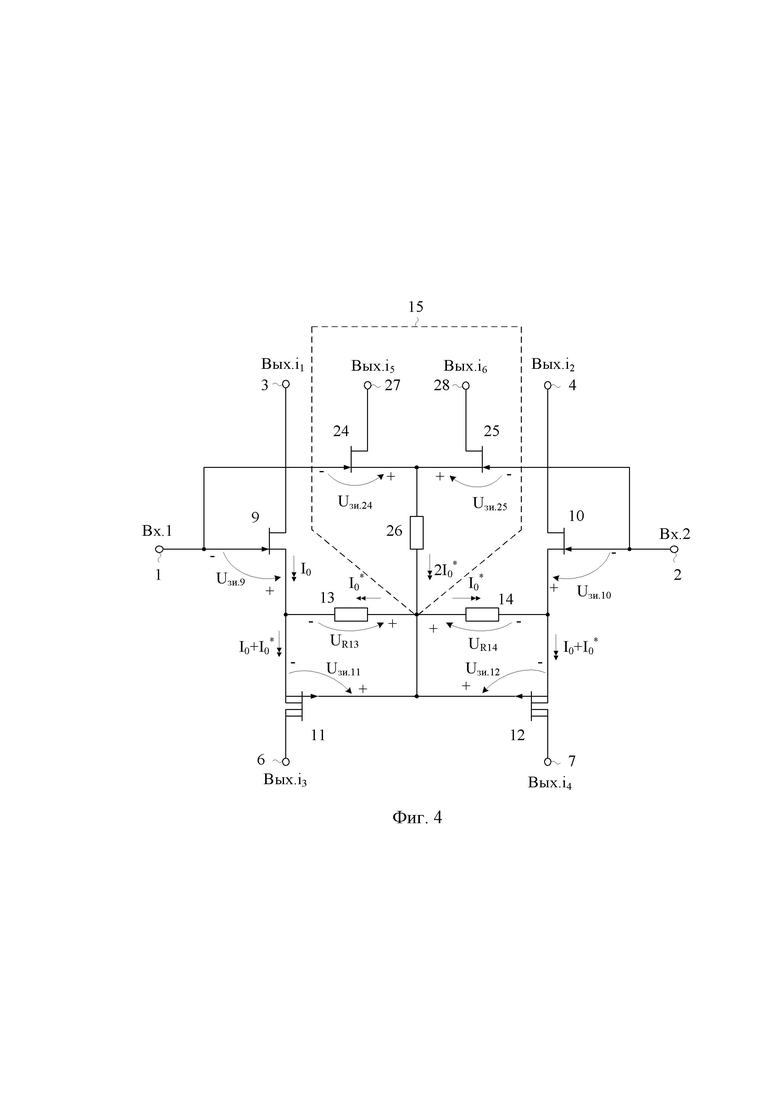

На чертеже фиг. 3 представлена схема заявляемого ПДН в соответствии с п. 3, а на чертеже фиг. 4 – п. 4 формулы изобретения.

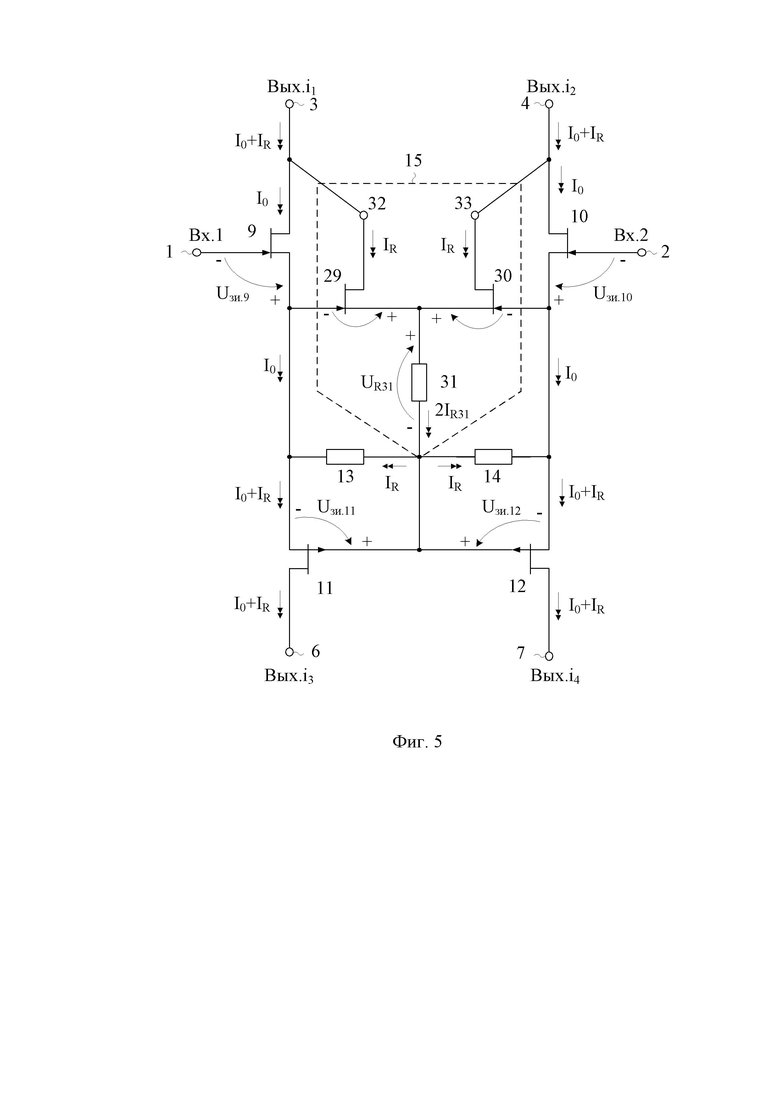

На чертеже фиг. 5 приведена схема заявляемого ПДН в соответствии с п. 5 формулы изобретения.

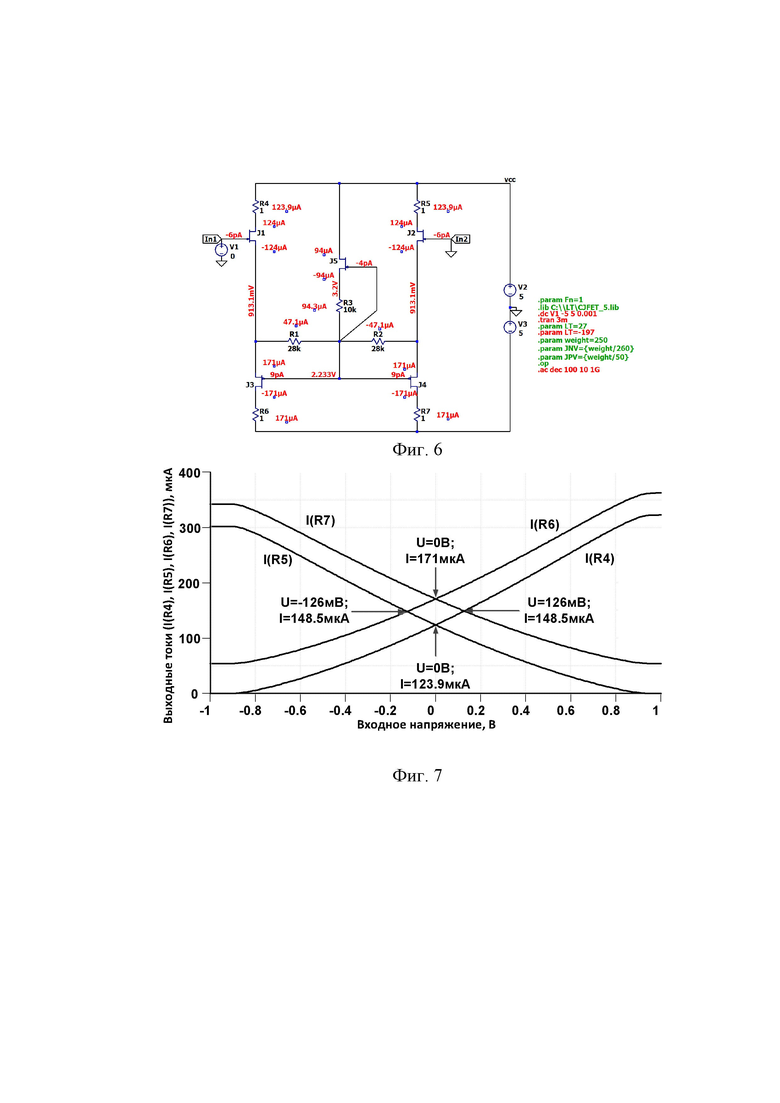

На чертеже фиг. 6 показан статический режим преобразователя дифференциального напряжения фиг.2 в среде LTSpice на моделях CJFet транзисторов ОАО «Интеграл» (г. Минск, Беларусь) при 27°С, R1=R2=28кОм, R3=10кОм.

На чертеже фиг. 7 представлены зависимости выходных токов ПДН фиг. 6 I(R4), I(R5), I(R6), I(R7) от входного напряжения V1.

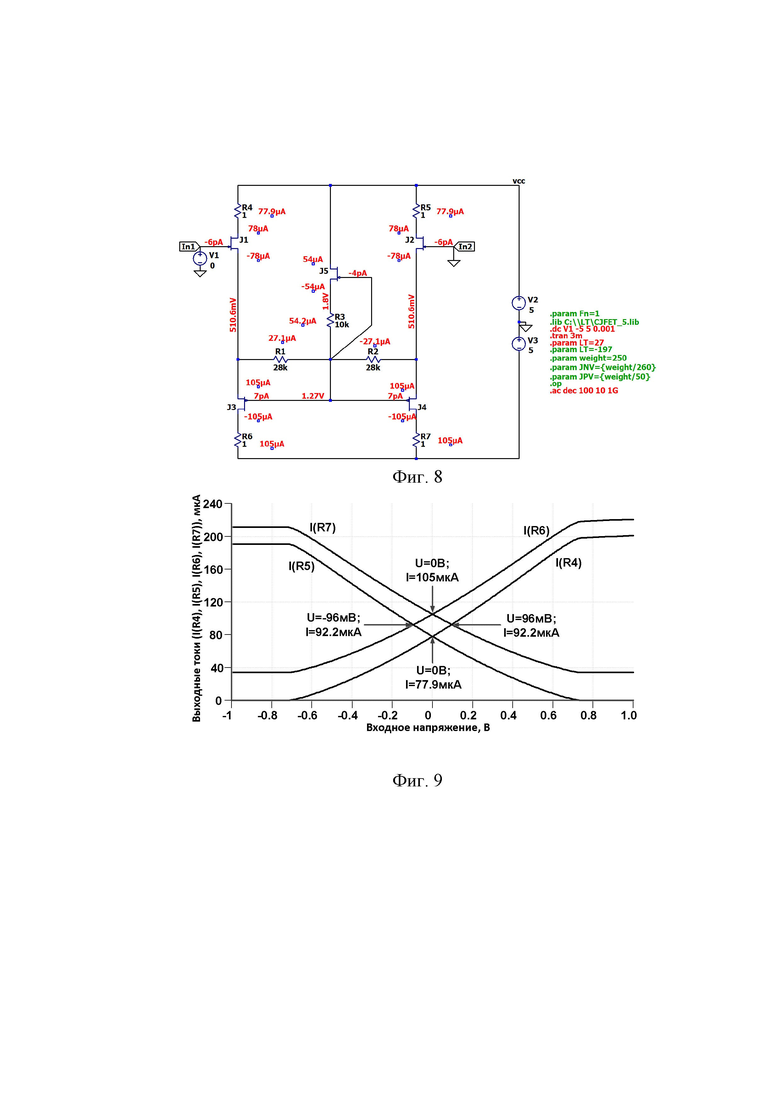

На чертеже фиг. 8 приведен статический режим ПДН фиг.2 в среде LTSpice на моделях CJFet транзисторов ОАО «Интеграл» (г. Минск, Беларусь) при -197°С, R1=R2=28кОм, R3=10кОм.

На чертеже фиг. 9 показаны зависимости выходных токов ПДН фиг. 8 I(R4), I(R5), I(R6), I(R7) от входного напряжения V1.

Преобразователь дифференциального входного напряжения с парафазными токовыми выходами на основе комплементарных полевых транзисторов с управляющим p-n переходом фиг. 2 содержит первый 1 и второй 2 входы устройства, первый 3 и второй 4 противофазные токовые выходы, согласованные с первой 5 шиной источника питания, третий 6 и четвертый 7 противофазные токовые выходы, согласованные со второй 8 шиной источника питания, первый 9 входной полевой транзистор, затвор которого соединен с первым 1 входом устройства, а сток подключен к первому 3 токовому выходу, второй 10 входной полевой транзистор, затвор которого связан со вторым 2 входом устройства, а сток подключен ко второму 4 токовому выходу, третий 11 входной полевой транзистор, сток которого соединен с третьим 6 токовым выходом, четвертый 12 входной полевой транзистор, сток которого соединен с четвертым 7 токовым выходом, причем между истоком первого 9 входного полевого транзистора и истоком второго 10 входного полевого транзистора включены первый 13 и второй 14 последовательно соединенные резисторы. Исток первого 9 входного полевого транзистора связан с истоком третьего 11 входного полевого транзистора, исток второго 10 входного полевого транзистора соединен с истоком четвертого 12 входного полевого транзистора, объединенные затворы третьего 11 и четвертого 12 входных полевых транзисторов связаны с общим узлом последовательно соединенных первого 13 и второго 14 резисторов, причем общий узел последовательно соединенных первого 13 и второго 14 резисторов подключен к источнику опорного тока 15.

На чертеже фиг. 2 первый 3 и второй 4 токовые выходы устройства связаны с первой 5 шиной источника питания через соответствующие двухполюсники 16 и 17, которые моделируют свойства нагрузки. Аналогично, третий 6 и четвертый 7 токовые выходы подключены ко второй 8 шине источника питания через соответствующие двухполюсники 18, 19. В частных случаях, в качестве двухполюсников 16-19 могут использоваться резисторы или токовые зеркала, осуществляющие дальнейшее преобразование сигналов парафазных токовых выходов устройства.

На чертеже фиг. 2, в соответствии с п. 2 формулы изобретения, источник опорного тока 15 выполнен на основе первого 20 вспомогательного полевого транзистора, сток которого согласован с первой 5 шиной источника питания, а исток соединен с общим узлом последовательно соединенных первого 13 и второго 14 резисторов через первый 21 вспомогательный резистор, причем затвор первого 20 вспомогательного полевого транзистора подключен к общему узлу последовательно соединенных первого 13 и второго 14 резисторов.

На чертеже фиг. 3, в соответствии с п. 3 формулы изобретения, источник опорного тока 15 выполнен на основе второго 22 вспомогательного полевого транзистора, сток которого подключен к общему узлу последовательно соединенных первого 13 и второго 14 резисторов, а исток связан с первой 5 шиной источника питания через второй 23 вспомогательный резистор, причем затвор второго 22 вспомогательного полевого транзистора согласован с первой 5 шиной источника питания.

На чертеже фиг. 4, в соответствии с п. 4 формулы изобретения, источник опорного тока 15 выполнен на основе третьего 24 и четвертого 25 вспомогательных полевых транзисторов, истоки которых объединены и связаны с общим узлом последовательно соединенных первого 13 и второго 14 резисторов через третий 26 вспомогательный резистор, причем затвор третьего 24 вспомогательного полевого транзистора соединен с первым 1 входом устройства, затвор четвертого 25 вспомогательного полевого транзистора соединен со вторым 2 входом устройства, сток третьего 24 вспомогательного полевого транзистора подключен к первому 27 дополнительному токовому выходу устройства, а сток четвертого 25 вспомогательного полевого транзистора подключен ко второму 28 дополнительному токовому выходу устройства.

На чертеже фиг. 5, в соответствии с п. 5 формулы изобретения, источник опорного тока 15 выполнен на основе пятого 29 и шестого 30 вспомогательных полевых транзисторов, истоки которых объединены и связаны с общим узлом последовательно соединенных первого 13 и второго 14 резисторов через четвертый 31 вспомогательный резистор, причем затвор пятого 29 вспомогательного полевого транзистора соединен с истоком первого 9 входного полевого транзистора, затвор шестого 30 вспомогательного полевого транзистора соединен с истоком второго 10 входного полевого транзистора, сток пятого 29 вспомогательного полевого транзистора подключен к третьему 32 дополнительному токовому выходу устройства, а сток шестого 30 вспомогательного полевого транзистора подключен к четвертому 33 дополнительному токовому выходу устройства.

Рассмотрим работу заявляемого устройства фиг. 2 при известной (типовой) аппроксимации вольт-амперной характеристики JFET.

Статический режим первого 9, второго 10 и третьего 11 и четвертого 12 входных полевых транзисторов в схеме фиг. 2 устанавливается источником опорного тока 15

,

,  ,

,

,

,

где Uотс – напряжение отсечки стоко-затворной характеристики JFET;

Iс.max – максимальный ток стока стоко-затворной характеристики JFET;

- ток источника опорного тока 15;

- ток источника опорного тока 15;

I0 – ток стока первого 9 (второго 10) JFET.

Как следует из фиг.2, входная емкость заявляемого устройства по первому 1 входу (Свх) определяется только входными емкостями соответствующих транзисторов 9 и 10. Следовательно, в предлагаемой схеме численные значения Свх в 2 раза меньше, чем в ПДН-прототипе.

Особенность схемы ПДН фиг. 2 состоит в том, что ее крутизна преобразования входного дифференциального напряжения в выходные токи определяется только крутизной стоко-затворной характеристики полевых транзисторов 9 (11) и 10 (12) и слабо зависит (как это наблюдается в ПДН-прототипе) от сопротивления первого 13 и второго 14 резисторов. В этой связи, заявляемое устройство характеризуется более высокой крутизной преобразования входного дифференциального напряжения в выходные токи парафазных выходов.

Указанные выше особенности ПДН подтверждаются результатами компьютерного моделирования, представленными на чертежах фиг. 7 и фиг. 9.

Таким образом, заявляемое устройство имеет существенные преимущества в сравнении с прототипом.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. O. V. Dvornikov, V. L. Dziatlau, N. N. Prokopenko, K. O. Petrosiants, N. V. Kozhukhov and V. A. Tchekhovski, "The accounting of the simultaneous exposure of the low temperatures and the penetrating radiation at the circuit simulation of the BiJFET analog interfaces of the sensors," 2017 International Siberian Conference on Control and Communications (SIBCON), Astana, 2017, pp. 1-6. DOI: 10.1109/SIBCON.2017.7998507

2. Патент US 4.377.789, fig. 1, 1983 г.

3. Патентная заявка US 2006/0125522, 2006 г.

4. Патент US 7.907.011, 2011 г.

5. Патент US 5.291.149 fig. 4, 1991 г.

6. Патент US 6.750.515, 2004 г.

7. Патент US 4.573.020, 1986 г.

8. Ashley Ingmire. Differential Amplifiers and common mode feedback. https://slideplayer.com/slide/1496714/

9. Патент US 6.556.081, fig. 1, 2003 г.

10. N. N. Prokopenko, N. V. Butyrlagin, A. V. Bugakova and A. A. Ignashin, "Method for speeding the micropower CMOS operational amplifiers with dual-input-stages," 2017 24th IEEE International Conference on Electronics, Circuits and Systems (ICECS), Batumi, 2017, pp. 78-81.

11. K. O. Petrosyants, M. R. Ismail-zade, L. M. Sambursky, O. V. Dvornikov, B. G. Lvov and I. A. Kharitonov, "Automation of parameter extraction procedure for Si JFET SPICE model in the −200…+110°C temperature range," 2018 Moscow Workshop on Electronic and Networking Technologies (MWENT), Moscow, 2018, pp. 1-5. DOI: 10.1109/MWENT.2018.8337212

12. Создание низкотемпературных аналоговых ИС для обработки импульсных сигналов датчиков. Часть 2 / О. Дворников, В. Чеховский, В. Дятлов, Н. Прокопенко // Современная электроника, 2015, № 5. С. 24-28

13. O. V. Dvornikov, N. N. Prokopenko, N. V. Butyrlagin and I. V. Pakhomov, "The differential and differential difference operational amplifiers of sensor systems based on bipolar-field technological process AGAMC," 2016 International Siberian Conference on Control and Communications (SIBCON), Moscow, 2016, pp. 1-6. DOI: 10.1109/SIBCON.2016.7491792

14. Дворников О.В., Чеховский В.А., Дятлов В.Л., Прокопенко Н.Н. "Малошумящий электронный модуль обработки сигналов лавинных фотодиодов" Приборы и методы измерений, no. 2 (7), 2013, pp. 42-46.

15. Дворников О. Чеховский В., Дятлов В., Прокопенко Н. Применение структурных кристаллов для создания интерфейсов датчиков //Современная электроника. – 2014. – №. 1. – С. 32-37.

16. O. V. Dvornikov, A. V. Bugakova, N. N. Prokopenko, V. L. Dziatlau and I. V. Pakhomov, "The microcircuits MH2XA010-02/03 for signal processing of optoelectronic sensors," 2017 18th International Conference of Young Specialists on Micro/Nanotechnologies and Electron Devices (EDM), Erlagol, 2017, pp. 396-402. DOI: 10.1109/EDM.2017.7981781.

Изобретение относится к области электроники и радиотехники. Технический результат: уменьшение входной емкости устройства по первому и второму входам, а также повышение крутизны преобразования входного дифференциального напряжения в выходные токи устройства. Для этого предложен преобразователь дифференциального входного напряжения с парафазными токовыми выходами на основе комплементарных полевых транзисторов с управляющим p-n переходом, у которого в отличие от прототипа исток первого (9) входного полевого транзистора связан с истоком третьего (11) входного полевого транзистора, исток второго (10) входного полевого транзистора соединен с истоком четвертого (12) входного полевого транзистора, объединенные затворы третьего (11) и четвертого (12) входных полевых транзисторов связаны с общим узлом последовательно соединенных первого (13) и второго (14) резисторов, причем общий узел последовательно соединенных первого (13) и второго (14) резисторов подключен к источнику опорного тока (15). 4 з.п. ф-лы, 9 ил.

1. Преобразователь дифференциального входного напряжения с парафазными токовыми выходами на основе комплементарных полевых транзисторов с управляющим p-n переходом, содержащий первый (1) и второй (2) входы устройства, первый (3) и второй (4) противофазные токовые выходы, согласованные с первой (5) шиной источника питания, третий (6) и четвертый (7) противофазные токовые выходы, согласованные со второй (8) шиной источника питания, первый (9) входной полевой транзистор, затвор которого соединен с первым (1) входом устройства, а сток подключен к первому (3) токовому выходу, второй (10) входной полевой транзистор, затвор которого связан со вторым (2) входом устройства, а сток подключен ко второму (4) токовому выходу, третий (11) входной полевой транзистор, сток которого соединен с третьим (6) токовым выходом, четвертый (12) входной полевой транзистор, сток которого соединен с четвертым (7) токовым выходом, причем между истоком первого (9) входного полевого транзистора и истоком второго (10) входного полевого транзистора включены первый (13) и второй (14) последовательно соединенные резисторы, отличающийся тем, что исток первого (9) входного полевого транзистора связан с истоком третьего (11) входного полевого транзистора, исток второго (10) входного полевого транзистора соединен с истоком четвертого (12) входного полевого транзистора, объединенные затворы третьего (11) и четвертого (12) входных полевых транзисторов связаны с общим узлом последовательно соединенных первого (13) и второго (14) резисторов, причем общий узел последовательно соединенных первого (13) и второго (14) резисторов подключен к источнику опорного тока (15).

2. Преобразователь дифференциального входного напряжения с парафазными токовыми выходами на основе комплементарных полевых транзисторов с управляющим p-n переходом по п. 1, отличающийся тем, что источник опорного тока (15) выполнен на основе первого (20) вспомогательного полевого транзистора, сток которого согласован с первой (5) шиной источника питания, а исток соединен с общим узлом последовательно соединенных первого (13) и второго (14) резисторов через первый (21) вспомогательный резистор, причем затвор первого (20) вспомогательного полевого транзистора подключен к общему узлу последовательно соединенных первого (13) и второго (14) резисторов.

3. Преобразователь дифференциального входного напряжения с парафазными токовыми выходами на основе комплементарных полевых транзисторов с управляющим p-n переходом по п. 1, отличающийся тем, что источник опорного тока (15) выполнен на основе второго (22) вспомогательного полевого транзистора, сток которого подключен к общему узлу последовательно соединенных первого (13) и второго (14) резисторов, а исток связан с первой (5) шиной источника питания через второй (23) вспомогательный резистор, причем затвор второго (22) вспомогательного полевого транзистора согласован с первой (5) шиной источника питания.

4. Преобразователь дифференциального входного напряжения с парафазными токовыми выходами на основе комплементарных полевых транзисторов с управляющим p-n переходом по п. 1, отличающийся тем, что источник опорного тока (15) выполнен на основе третьего (24) и четвертого (25) вспомогательных полевых транзисторов, истоки которых объединены и связаны с общим узлом последовательно соединенных первого (13) и второго (14) резисторов через третий (26) вспомогательный резистор, причем затвор третьего (24) вспомогательного полевого транзистора соединен с первым (1) входом устройства, затвор четвертого (25) вспомогательного полевого транзистора соединен со вторым (2) входом устройства, сток третьего (24) вспомогательного полевого транзистора подключен к первому (27) дополнительному токовому выходу устройства, а сток четвертого (25) вспомогательного полевого транзистора подключен ко второму (28) дополнительному токовому выходу устройства.

5. Преобразователь дифференциального входного напряжения с парафазными токовыми выходами на основе комплементарных полевых транзисторов с управляющим p-n переходом по п. 1, отличающийся тем, что источник опорного тока (15) выполнен на основе пятого (29) и шестого (30) вспомогательных полевых транзисторов, истоки которых объединены и связаны с общим узлом последовательно соединенных первого (13) и второго (14) резисторов через четвертый (31) вспомогательный резистор, причем затвор пятого (29) вспомогательного полевого транзистора соединен с истоком первого (9) входного полевого транзистора, затвор шестого (30) вспомогательного полевого транзистора соединен с истоком второго (10) входного полевого транзистора, сток пятого (29) вспомогательного полевого транзистора подключен к третьему (32) дополнительному токовому выходу устройства, а сток шестого (30) вспомогательного полевого транзистора подключен к четвертому (33) дополнительному токовому выходу устройства.

| Дифференциальный усилитель на комплементарных полевых транзисторах с управляющим p-n переходом | 2018 |

|

RU2688225C1 |

| ПРЕОБРАЗОВАТЕЛЬ "НАПРЯЖЕНИЕ-ТОК" | 2007 |

|

RU2331964C1 |

| Преобразователь напряжения в ток | 1972 |

|

SU456341A1 |

| US 5021730 A1, 04.06.1991. | |||

Авторы

Даты

2020-06-29—Публикация

2020-03-13—Подача