Изобретение относится к области радиотехники и аналоговой микроэлектроники и может быть использовано в аналоговых и аналого-цифровых интерфейсах для обработки сигналов датчиков, работающих в условиях синфазных помех.

В современной радиоэлектронной аппаратуре находят применение дифференциальные операционные усилители (ОУ) с существенными различными параметрами. Особое место занимают ОУ на основе комплементарных входных каскадов (так называемых dual-input-stage), двух токовых зеркал, согласованных с шинами положительного и отрицательного источников питания, и буферного усилителя [1-31]. ОУ данного класса реализуются как на биполярных, так и на КМОП транзисторах. Такая архитектура ОУ [1-31] является основой более чем 50 серийных микросхем, выпускаемых ведущими микроэлектронными фирмами мира.

Одним из важных динамических параметров современных операционных усилителей является коэффициент ослабления входного синфазного сигнала (Кос.сф), оказывающий существенное влияние на предельные точностные параметры многих вариантов построения аналоговых интерфейсов, работающих в условиях синфазных помех.

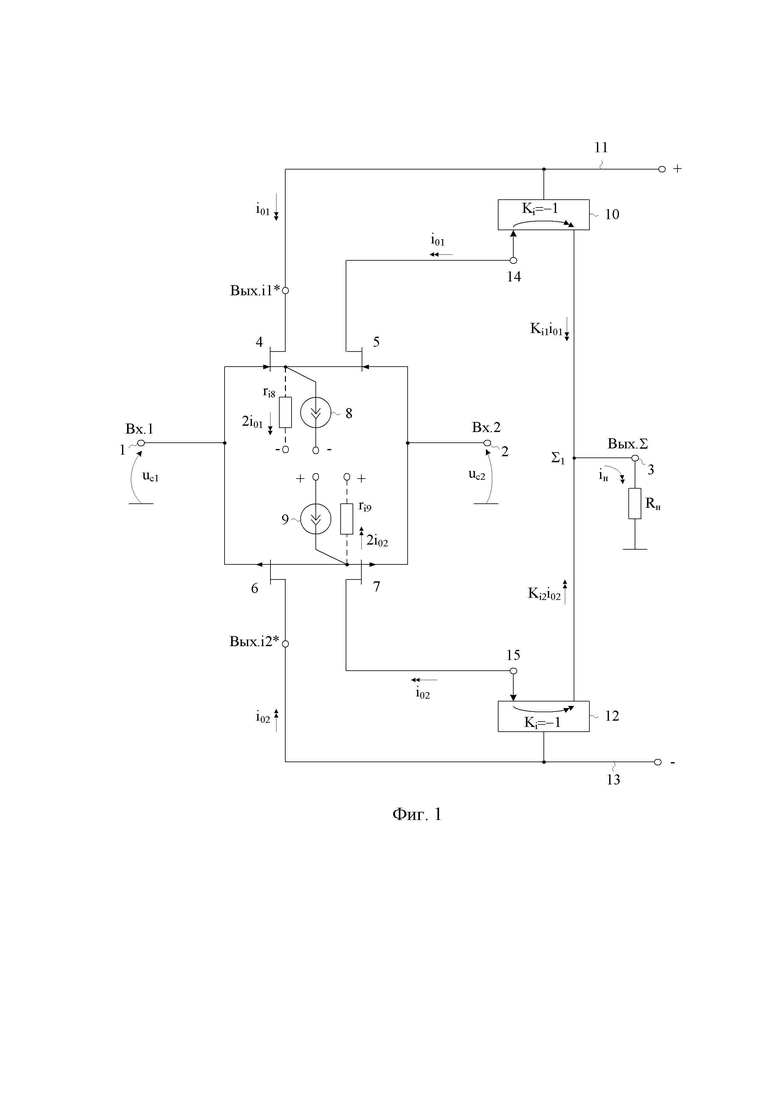

Ближайшим прототипом (фиг. 1) заявляемого устройства является ОУ по патентной заявке US 2006/0125522, fig.1a, fig.3, 2006г. Он содержит первый 1 и второй 2 входы устройства, основной выход 3 устройства, первый 4 и второй 5 входные полевые транзисторы с объединенными истоками, третий 6 и четвертый 7 входные полевые транзисторы с объединенными истоками, первый 8 источник опорного тока, связанный с объединенными истоками первого 4 и второго 5 входных полевых транзисторов, второй 9 источник опорного тока, связанный с объединенными истоками третьего 6 и четвертого 7 входных полевых транзисторов, первое 10 токовое зеркало согласованное с первой 11 шиной источника питания, второе 12 токовое зеркало согласованное со второй 13 шиной источника питания, причем первый 1 вход устройства соединён с затворами первого 4 и третьего 6 входных полевых транзисторов, второй 2 вход устройства соединен с затворами второго 5 и четвертого 7 входных полевых транзисторов, сток второго 5 входного полевого транзистора подключен к основному входу 14 первого 10 токового зеркала, сток четвертого 7 входного полевого транзистора связан с основным входом 15 второго 12 токового зеркала, выходы первого 10 и второго 12 токовых зеркал объединены и подключены к основному выходу 3 устройства, сток первого 4 входного полевого транзистора согласован с первой 11 шиной источниками питания, а сток третьего 6 входного полевого транзистора согласован со второй 13 шиной источника питания.

Существенный недостаток известного ОУ состоит в том, что при его практической реализации на основе комплементарных полевых транзисторов с управляющим p-n переходом он не обеспечивает повышенные значения Кос.сф в диапазоне низких температур. Это связано с тем, что в схеме ОУ-прототипа на его Кос.сф оказывают существенное влияние выходные сопротивления первого 8 (ri8) и второго 9 (ri9) источников опорного тока, которые создают паразитные каналы передачи входного синфазного сигнала на выход устройства 3. Если передачу по этим каналам минимизировать, то Кос.сф ОУ существенно возрастет.

Основная задача предполагаемого изобретения состоит в повышении коэффициента ослабления входных синфазных сигналов ОУ при низких температурах.

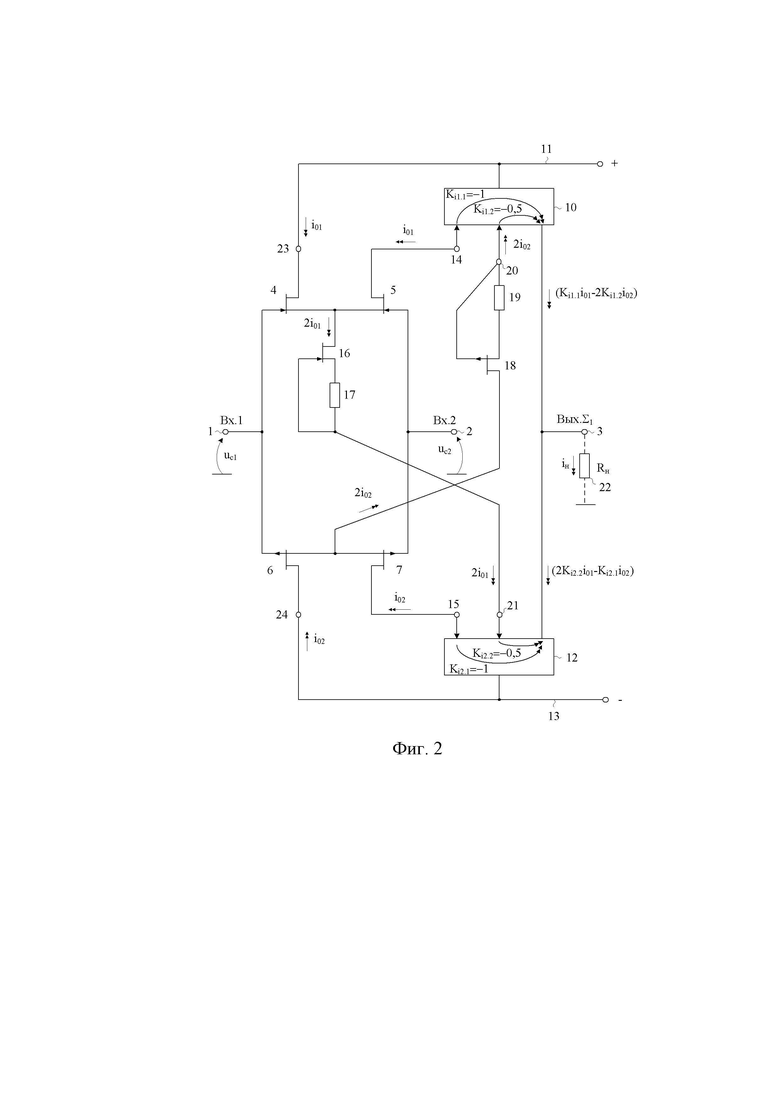

Поставленная задача решается тем, что в операционном усилителе фиг. 1, содержащем первый 1 и второй 2 входы устройства, основной выход 3 устройства, первый 4 и второй 5 входные полевые транзисторы с объединенными истоками, третий 6 и четвертый 7 входные полевые транзисторы с объединенными истоками, первый 8 источник опорного тока, связанный с объединенными истоками первого 4 и второго 5 входных полевых транзисторов, второй 9 источник опорного тока, связанный с объединенными истоками третьего 6 и четвертого 7 входных полевых транзисторов, первое 10 токовое зеркало согласованное с первой 11 шиной источника питания, второе 12 токовое зеркало согласованное со второй 13 шиной источника питания, причем первый 1 вход устройства соединён с затворами первого 4 и третьего 6 входных полевых транзисторов, второй 2 вход устройства соединен с затворами второго 5 и четвертого 7 входных полевых транзисторов, сток второго 5 входного полевого транзистора подключен к основному входу 14 первого 10 токового зеркала, сток четвертого 7 входного полевого транзистора связан с основным входом 15 второго 12 токового зеркала, выходы первого 10 и второго 12 токовых зеркал объединены и подключены к основному выходу 3 устройства, сток первого 4 входного полевого транзистора согласован с первой 11 шиной источниками питания, а сток третьего 6 входного полевого транзистора согласован со второй 13 шиной источника питания, предусмотрены новые элементы и связи – первый 8 источник опорного тока реализован на основе первого 16 дополнительного полевого транзистора, исток которого соединен с затвором первого 16 дополнительного полевого транзистора через первый вспомогательный резистор 17, а сток соединен с объединенными истоками первого 4 и второго 5 входных полевых транзисторов, второй 9 источник опорного тока реализован на основе второго 18 дополнительного полевого транзистора, исток которого соединен с затвором второго 18 дополнительного полевого транзистора через второй вспомогательный резистор 19, а сток соединен с объединенными истоками третьего 6 и четвертого 7 входных полевых транзисторов, причем в первом 10 токовом зеркале предусмотрен дополнительный токовый вход 20, связанный с затвором второго 18 дополнительного полевого транзистора, а во втором 12 токовом зеркале предусмотрен дополнительный токовый вход 21, связанный с затвором первого 16 дополнительного полевого транзистора.

На чертеже фиг. 1 показана схема операционного усилителя-прототипа.

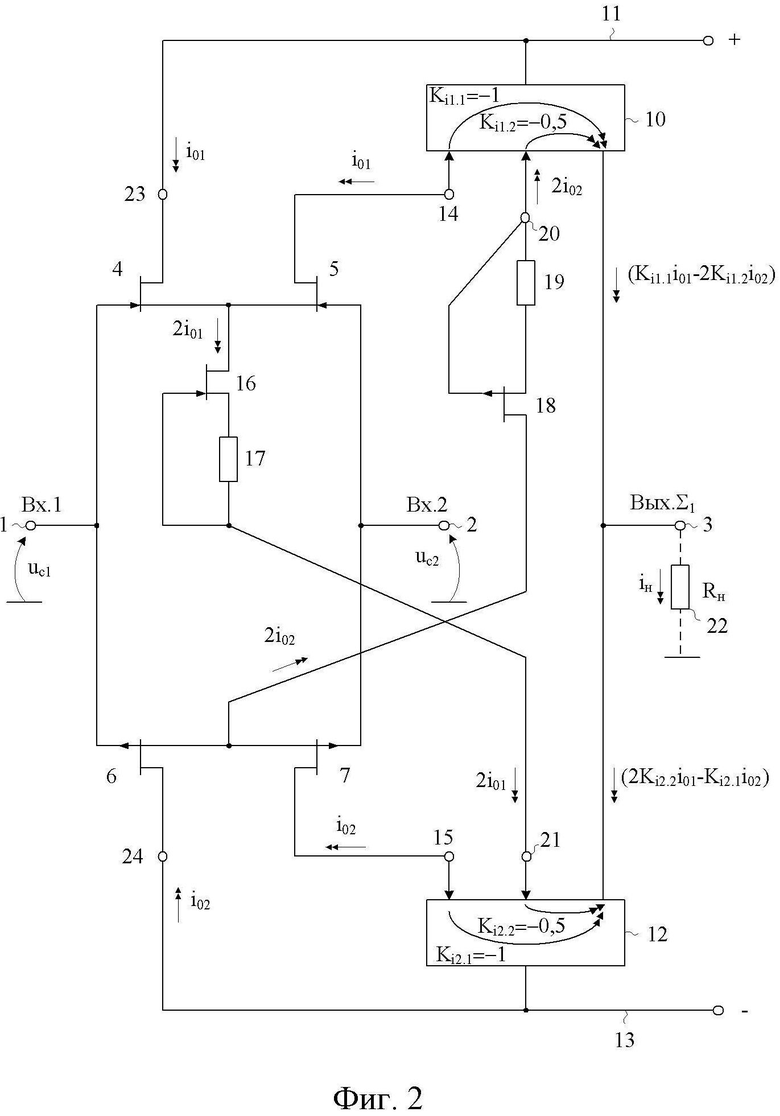

На чертеже фиг. 2 приведена схема заявляемого устройства в соответствии с п.1 и п.2 формулы изобретения.

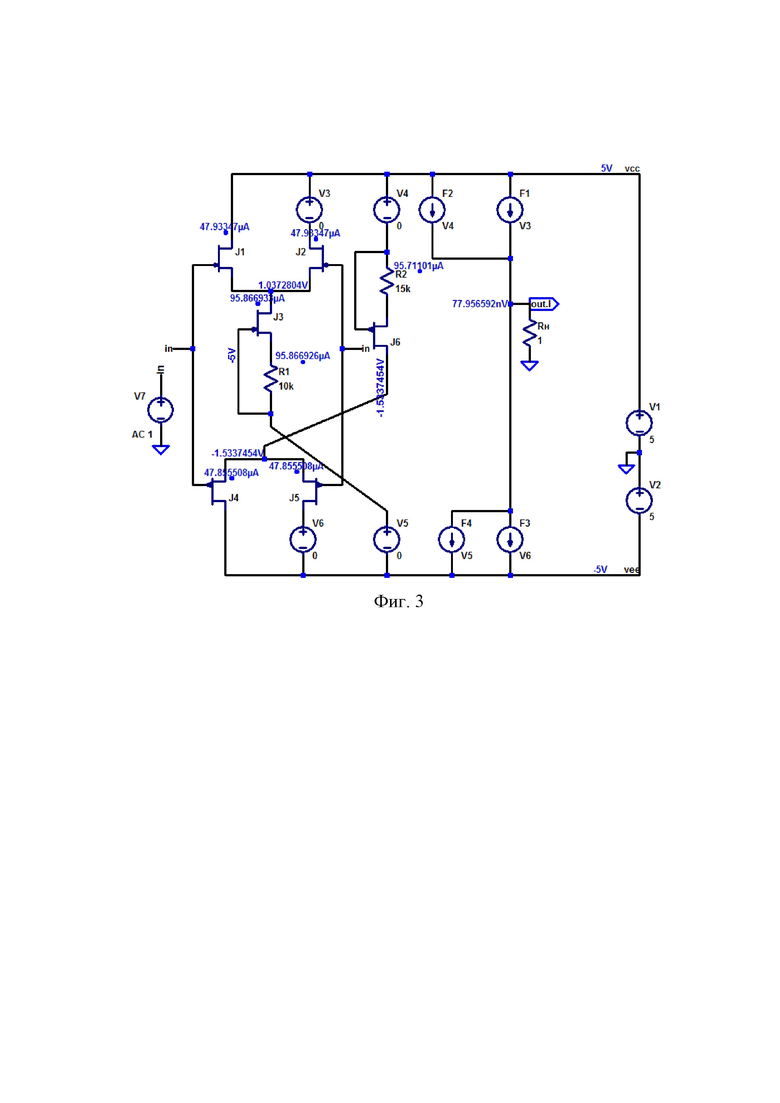

На чертеже фиг. 3 представлен статический режим ОУ фиг. 2 для случая, соответствующего реализации в данной более общей схеме свойств ОУ-прототипа фиг. 1 за счет соответствующего выбора коэффициентов передачи токовых зеркал 10 и 12 (Кi1.1=-1, Кi1.2=0; Кi2.1=-1, Кi2.2=0): среда моделирования LTSpice на моделях интегральных транзисторов ОАО «Интеграл» (г.Минск) [32] при t=27°C, R1=10kОм, R2=15kОм.

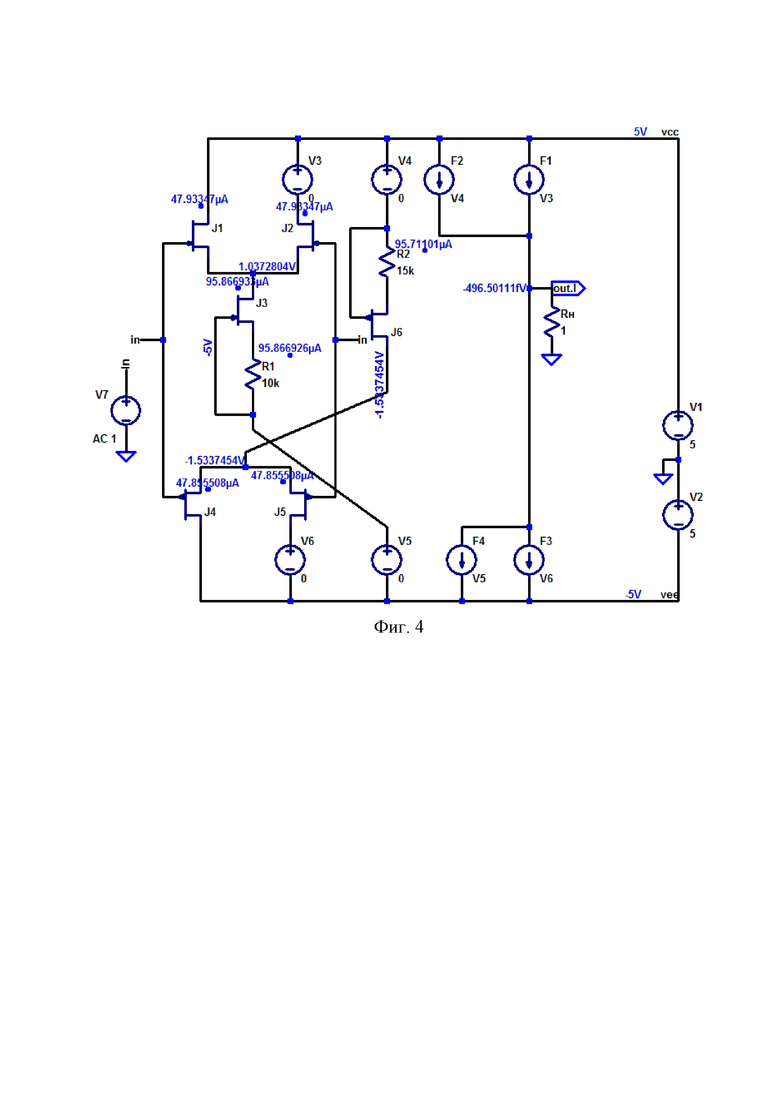

На чертеже фиг. 4 показан статический режим заявляемого ОУ фиг. 2 в среде моделирования LTSpice на моделях интегральных транзисторов ОАО «Интеграл» (г.Минск) при температуре при t=27°C, R1=10kОм, R2=15kОм и коэффициентах передачи токовых зеркал 10 и 12 Кi1.1=-1, Кi1.2=-0.5; Кi2.1=-1, Кi2.2=-0.5, соответствующих п. 2 формулы изобретения.

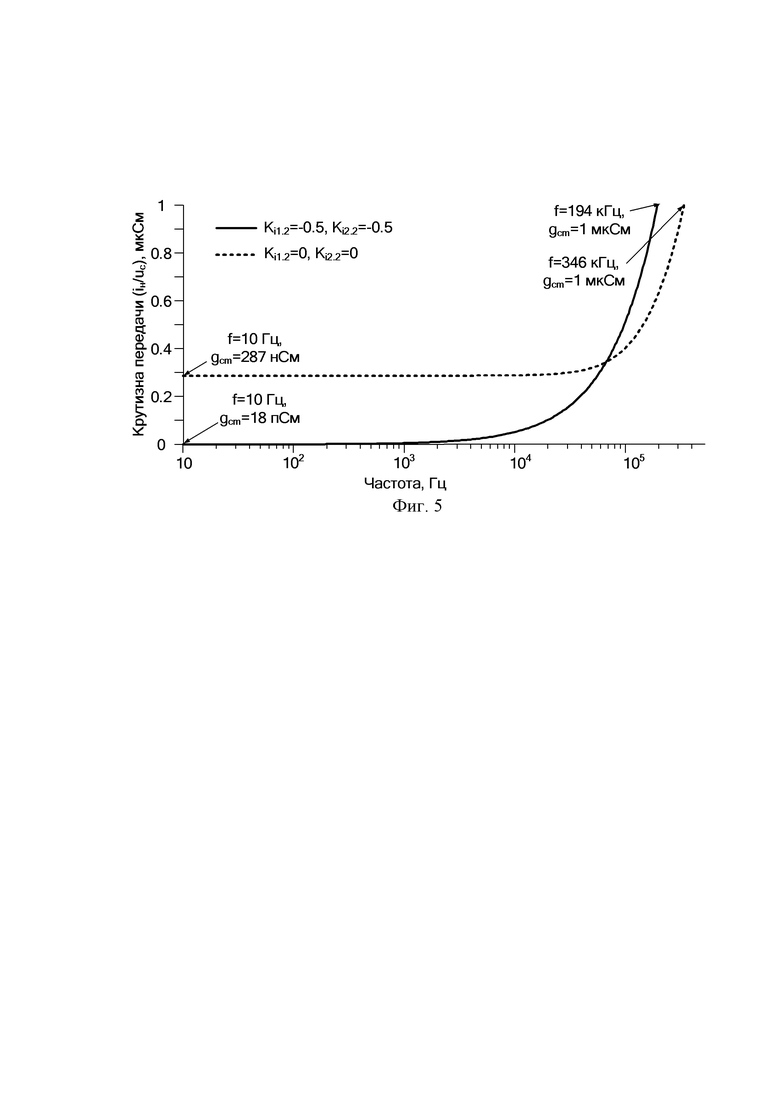

На чертеже фиг. 5 приведено сравнение частотной зависимости крутизны передачи входного синфазного сигнала gm=iвых/uc заявляемого ОУ фиг. 4 (сплошные линии) и ОУ-прототипа фиг. 3 (пунктирные линии) при комнатной температуре t=27°C.

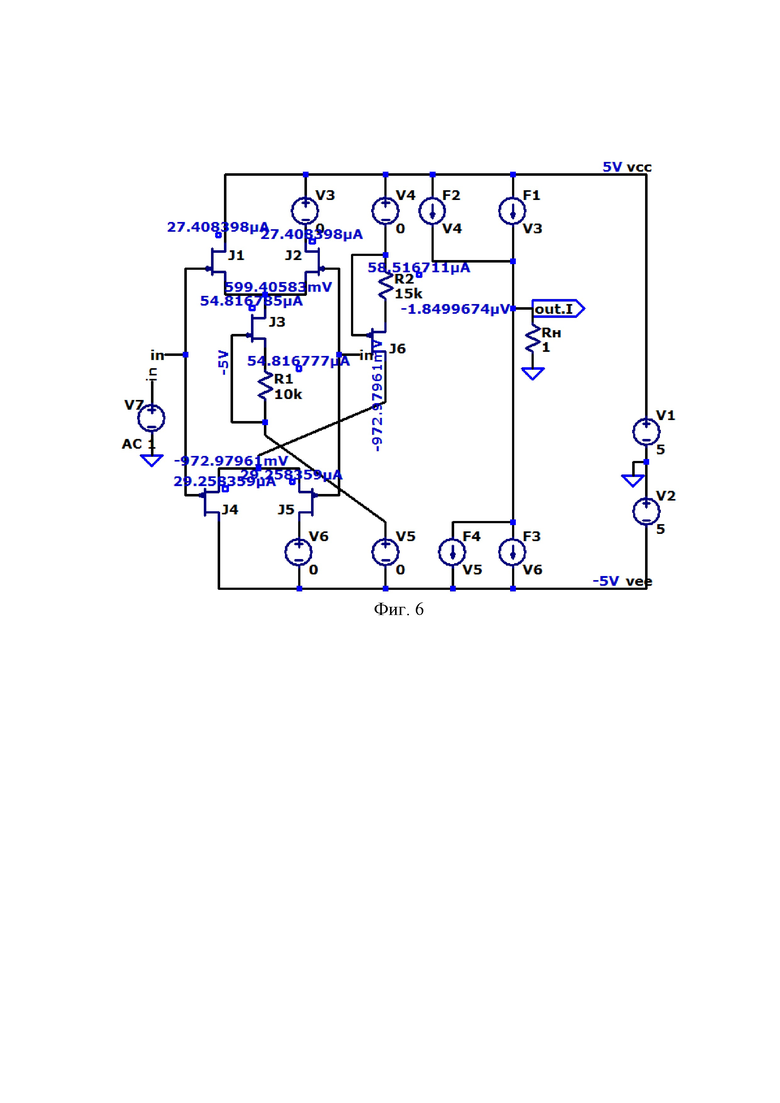

На чертеже фиг. 6 представлен статический режим ОУ фиг. 2 при

t=-197°C для случая, соответствующего реализации в данной более общей схеме свойств ОУ-прототипа фиг. 1 за счет соответствующего выбора коэффициентов передачи первого 10 и второго 12 токовых зеркал (Кi1.1=-1, Кi1.2=0; Кi2.1=-1, Кi2.2=0): среда моделирования LTSpice на моделях интегральных транзисторов ОАО «Интеграл» (г.Минск) при R1=10kОм, R2=15kОм.

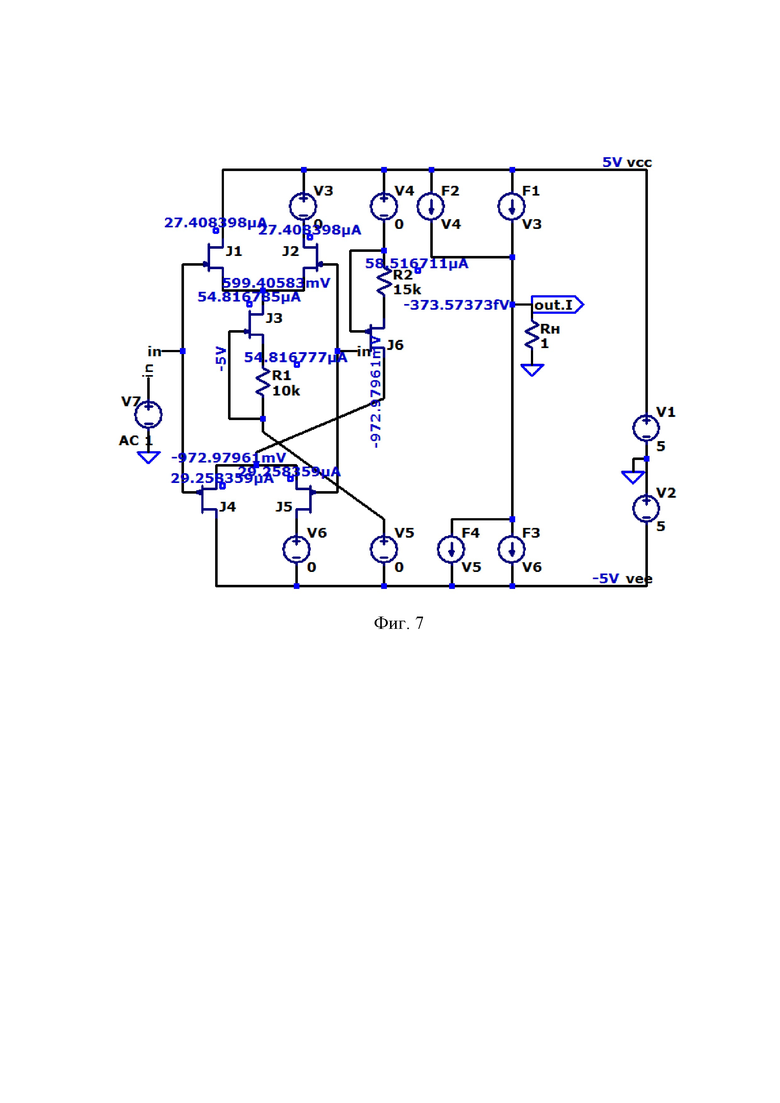

На чертеже фиг. 7 показан статический режим заявляемого ОУ фиг. 2 для t=-197°C в среде моделирования LTSpice на моделях интегральных транзисторов ОАО «Интеграл» (г.Минск) [32] при R1=10kОм, R2=15kОм и коэффициентах передачи первого 10 и второго 12 токовых зеркал Кi1.1=-1, Кi1.2=-0.5; Кi2.1=-1, Кi2.2=-0.5, соответствующих п. 2 формулы изобретения.

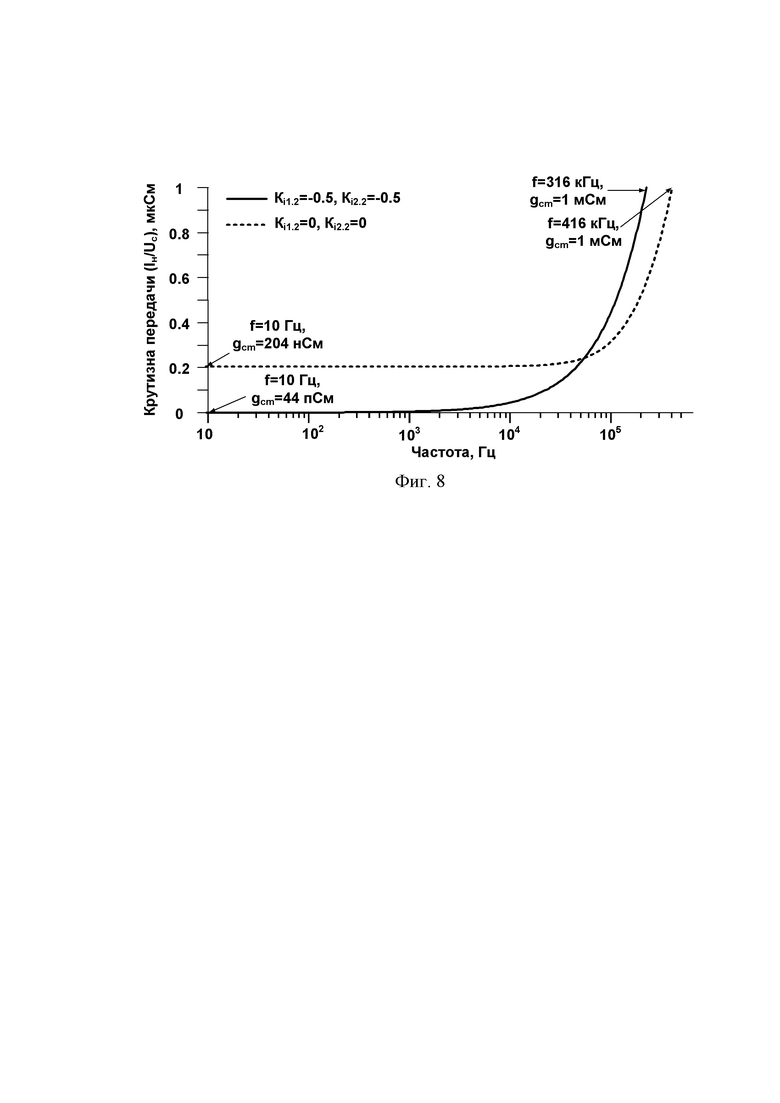

На чертеже фиг. 8 приведено сравнение частотной зависимости крутизны передачи gm входного синфазного сигнала заявляемого ОУ фиг. 7 (сплошные линии) и ОУ-прототипа фиг. 6 (пунктирные линии) при криогенных температурах (t=-197°C).

Низкотемпературный операционный усилитель с повышенным ослаблением входного синфазного сигнала на комплементарных полевых транзисторах с управляющим p-n переходом фиг. 2 содержит первый 1 и второй 2 входы устройства, основной выход 3 устройства, первый 4 и второй 5 входные полевые транзисторы с объединенными истоками, третий 6 и четвертый 7 входные полевые транзисторы с объединенными истоками, первый 8 источник опорного тока, связанный с объединенными истоками первого 4 и второго 5 входных полевых транзисторов, второй 9 источник опорного тока, связанный с объединенными истоками третьего 6 и четвертого 7 входных полевых транзисторов, первое 10 токовое зеркало, согласованное с первой 11 шиной источника питания, второе 12 токовое зеркало согласованное со второй 13 шиной источника питания, причем первый 1 вход устройства соединён с затворами первого 4 и третьего 6 входных полевых транзисторов, второй 2 вход устройства соединен с затворами второго 5 и четвертого 7 входных полевых транзисторов, сток второго 5 входного полевого транзистора подключен к основному входу 14 первого 10 токового зеркала, сток четвертого 7 входного полевого транзистора связан с основным входом 15 второго 12 токового зеркала, выходы первого 10 и второго 12 токовых зеркал объединены и подключены к основному выходу 3 устройства, сток первого 4 входного полевого транзистора согласован с первой 11 шиной источниками питания, а сток третьего 6 входного полевого транзистора согласован со второй 13 шиной источника питания. Первый 8 источник опорного тока реализован на основе первого 16 дополнительного полевого транзистора, исток которого соединен с затвором первого 16 дополнительного полевого транзистора через первый вспомогательный резистор 17, а сток соединен с объединенными истоками первого 4 и второго 5 входных полевых транзисторов, второй 9 источник опорного тока реализован на основе второго 18 дополнительного полевого транзистора, исток которого соединен с затвором второго 18 дополнительного полевого транзистора через второй вспомогательный резистор 19, а сток соединен с объединенными истоками третьего 6 и четвертого 7 входных полевых транзисторов, причем в первом 10 токовом зеркале предусмотрен дополнительный токовый вход 20, связанный с затвором второго 18 дополнительного полевого транзистора, а во втором 12 токовом зеркале предусмотрен дополнительный токовый вход 21, связанный с затвором первого 16 дополнительного полевого транзистора. Двухполюсник 22 на чертеже фиг. 2 моделирует свойства нагрузки, подключаемой к основному выходу 3 устройства.

В частных случаях включения заявляемого ОУ фиг. 2, например, в схемах ОУ с парафазным выходом, в нем могут использоваться дополнительные токовые выходы 23 и 24, связанные со стоками соответствующих полевых транзисторов 4 и 6 и согласованные с первой 11 и второй 13 шинами источников питания. К этим выходам могут подключаться дополнительные токовые зеркала, аналогичные первому 10 и второму 12 токовым зеркалам на чертеже фиг.2, что позволяет организовать в такой схеме ОУ парафазный выход.

На чертеже фиг. 2, в соответствии с п. 2 формулы изобретения, коэффициенты передачи по току по основному входу 14 первого 10 токового зеркала больше коэффициента передачи по току по его дополнительному токовому входу 20 в 2 раза, а коэффициенты передачи по току по основному входу 15 второго 12 токового зеркала больше коэффициента передачи по току по его дополнительному токовому входу 21 в 2 раза.

Рассмотрим работу заявляемого устройства фиг. 2.

Изменение входного синфазного сигнала uc=uc1=uc2 приводит к изменению токов стока первого 16 и второго 18 дополнительных полевых транзисторов на величины 2i01 и 2i02, которые передаются на основной выход 3 устройства по двум дополнительным компенсирующим каналам, организованным в первом 10 и втором 12 токовых зеркалах. При этом для выходов первого 10 и второго 12 токовых зеркал и нагрузки Rн в схеме фиг. 2 справедливы следующие токовые соотношения

iвых.10 = Ki1.1i01-2Ki1.2i02, (1)

iвых.12 = 2Ki2.2i01-Ki2.1i02, (2)

iн = iвых.10 – iвых.12, (3)

где Ki1.1, Ki1.2, Ki2.2, Ki2.1 - коэффициенты передачи по току первого 10 и второго 12 токовых зеркал по основным 14 и 15, а также дополнительным 20 и 21 входам;

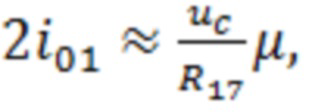

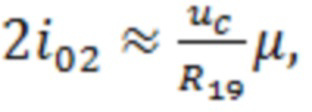

i01, i02 - приращение токов стока первого 16 и второго 18 дополнительных полевых транзисторов, обусловленные конечными значениями их выходных сопротивлений. Причем

(4)

(4)

(5)

(5)

где R17, R19 – сопротивления первого 17 и второго 19 вспомогательных резисторов,

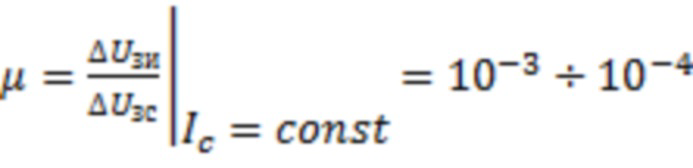

μ - коэффициент внутренней обратной связи полевых транзисторов 16 и 18, учитывающий влияние изменений напряжений на стоках этих транзисторов на смещение их стоко-затворных характеристик при постоянном токе стока:

. (6)

. (6)

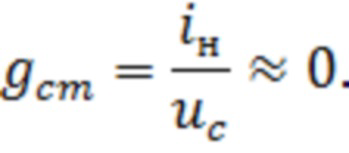

Из уравнений (1)-(5) следует, что за счет выбора коэффициентов передачи Ki1.1=-1, Ki1.2=-0,5, Ki2.2=-0,5, Ki2.1=-1, в схеме фиг. 2 обеспечивается нулевая проводимость передачи gcm входного синфазного сигнала uc=uc1=uc2 к основному выходу устройства 3

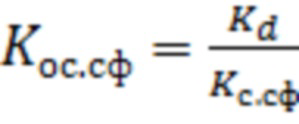

В результате, Кос.сф ОУ фиг. 2 существенно возрастает, так как:

, (7)

, (7)

где Кd –коэффициент передачи дифференциального входного сигнала ОУ фиг. 1 со входов 1, 2 устройства на основной выход 3;

Kс.сф – коэффициент передачи входного синфазного сигнала со входов 1, 2 устройства uc=uc1=uc2 на основной выход 3.

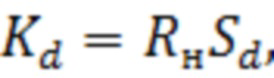

Для рассматриваемой схемы ОУ

(8)

(8)

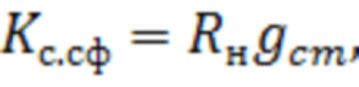

(9)

(9)

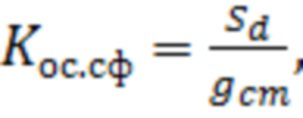

(10)

(10)

где Sd – крутизна передачи входного дифференциального напряжения uвх=uс1=uс2 на первом 1 и втором 2 входах устройства на основной выход 3 ОУ;

gcm<<Sd – крутизна передачи входного синфазного сигнала uc=uc1=uc2 на основной выход 3 ОУ.

Таким образом, как следует из формулы (9), минимизация Kс.сф в предлагаемом устройстве существенно повышает его синфазную помехоустойчивость (10). Следовательно, заявляемый ОУ обладает существенным преимуществом по Kос.сф в сравнении с ОУ-прототипом.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Заявка на патент US 2006/0125522, fig.1a, fig.3, 2006 г.

2. Заявка на патент US 2005/0024140, fig.12, 2005 г.

3. Патент US 5.714.906, fig. 1a, 1998 г.

4. Патент US 7.915.948, fig. 6, fig. 10, 2011 г.

5. Патент US 4.783.637, fig. 1, 1988 г.

6. Патент US 5.515.005, fig.1, fig. 2, 1996 г.

7. Патент SU № 1220105, 1984 г.

8. Патент US 3.968.451, fig.7, 1976 г.

9. Патент US 5.374.897, fig. 3, 1994 г.

10. Патент US 6.504.419, fig. 2, 2003 г.

11. Патент US 5.512.859, fig. 1, 1996 г.

12. Патент US 4.636.743, fig. 1,1987 г.

13. Патент US 6.268.769, fig. 3, 2001 г.

14. Патент US 3.974.455, fig. 7, 1976 г.

15. Патент US 5.291.149, 1994 г.

16. Авт. свид. СССР № 530425

17. Патент US 5.814.953, 1998 г.

18. Патент US 5.225.791, 1993 г.

19. Авт. свид. СССР № 611288

20. Патент US 6.794.940, fig. 1, 2004 г.

21. Патентная заявка US 2006/0226908, fig. 4, 2006 г.

22. Патентная заявка US 2001/0052818, fig. 1, 2001 г.

23. Заявка на патент US 2004/0174216, fig. 1, fig. 2, 2004 г.

24. Патент EP 1150423, fig.2, 2001 г.

25. Патентная заявка US 2003/0206060, fig. 1, 2003 г.

26. Патент US 6.642.789, fig. 1, 2003 г.

27. Патент US 4.377.789, fig. 1, 1983 г.

28. Патент US 6.100.762, fig. 1, 2000 г.

29. Патент US 5.909.146, fig. 5, 1999 г.

30. Патент US 5.621.357, fig. 4, 1997 г.

31. Патент US 6.844.781, fig.2, 2005 г.

32.O. V. Dvornikov, V. L. Dziatlau, N. N. Prokopenko, K. O. Petrosiants, N. V. Kozhukhov and V. A. Tchekhovski, "The accounting of the simultaneous exposure of the low temperatures and the penetrating radiation at the circuit simulation of the BiJFET analog interfaces of the sensors," 2017 International Siberian Conference on Control and Communications (SIBCON), Astana, 2017, pp. 1-6. DOI: 10.1109/SIBCON.2017.7998507.

Изобретение относится к области радиотехники и аналоговой микроэлектроники. Технический результат заключается в повышении коэффициента ослабления входных синфазных сигналов ОУ для работы при низких температурах, оказывающего существенное влияние на погрешности классических аналоговых интерфейсов. Усилитель содержит входные полевые транзисторы с объединенными истоками, токовые зеркала, дополнительный полевой транзистор, вспомогательный резистор, дополнительный токовый вход, связанный с затвором первого дополнительного полевого транзистора. 1 з.п. ф-лы, 8 ил.

1. Низкотемпературный операционный усилитель с повышенным ослаблением входного синфазного сигнала на комплементарных полевых транзисторах с управляющим p-n переходом, содержащий первый (1) и второй (2) входы устройства, основной выход (3) устройства, первый (4) и второй (5) входные полевые транзисторы с объединенными истоками, третий (6) и четвертый (7) входные полевые транзисторы с объединенными истоками, первый (8) источник опорного тока, связанный с объединенными истоками первого (4) и второго (5) входных полевых транзисторов, второй (9) источник опорного тока, связанный с объединенными истоками третьего (6) и четвертого (7) входных полевых транзисторов, первое (10) токовое зеркало, согласованное с первой (11) шиной источника питания, второе (12) токовое зеркало, согласованное со второй (13) шиной источника питания, причем первый (1) вход устройства соединён с затворами первого (4) и третьего (6) входных полевых транзисторов, второй (2) вход устройства соединен с затворами второго (5) и четвертого (7) входных полевых транзисторов, сток второго (5) входного полевого транзистора подключен к основному входу (14) первого (10) токового зеркала, сток четвертого (7) входного полевого транзистора связан с основным входом (15) второго (12) токового зеркала, выходы первого (10) и второго (12) токовых зеркал объединены и подключены к основному выходу (3) устройства, сток первого (4) входного полевого транзистора согласован с первой (11) шиной источниками питания, а сток третьего (6) входного полевого транзистора согласован со второй (13) шиной источника питания, отличающийся тем, что первый (8) источник опорного тока реализован на основе первого (16) дополнительного полевого транзистора, исток которого соединен с затвором первого (16) дополнительного полевого транзистора через первый вспомогательный резистор (17), а сток соединен с объединенными истоками первого (4) и второго (5) входных полевых транзисторов, второй (9) источник опорного тока реализован на основе второго (18) дополнительного полевого транзистора, исток которого соединен с затвором второго (18) дополнительного полевого транзистора через второй вспомогательный резистор (19), а сток соединен с объединенными истоками третьего (6) и четвертого (7) входных полевых транзисторов, причем в первом (10) токовом зеркале предусмотрен дополнительный токовый вход (20), связанный с затвором второго (18) дополнительного полевого транзистора, а во втором (12) токовом зеркале предусмотрен дополнительный токовый вход (21), связанный с затвором первого (16) дополнительного полевого транзистора.

2. Низкотемпературный операционный усилитель по п. 1, отличающийся тем, что коэффициенты передачи по току по основному входу (14) первого (10) токового зеркала больше коэффициента передачи по току по его дополнительному токовому входу (20) в 2 раза, а коэффициенты передачи по току по основному входу (15) второго (12) токового зеркала больше коэффициента передачи по току по его дополнительному токовому входу (21) в 2 раза.

| Пломбировальные щипцы | 1923 |

|

SU2006A1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ КОЭФФИЦИЕНТОМ УСИЛЕНИЯ ПО НАПРЯЖЕНИЮ | 2010 |

|

RU2419197C1 |

| ИНСТРУМЕНТАЛЬНЫЙ УСИЛИТЕЛЬ ДЛЯ РАБОТЫ ПРИ НИЗКИХ ТЕМПЕРАТУРАХ | 2016 |

|

RU2624565C1 |

| US 7030696 B2, 18.04.2006. | |||

Авторы

Даты

2020-09-21—Публикация

2020-01-30—Подача