Изобретение относится к области радиотехники и аналоговой микроэлектроники и может быть использовано в аналоговых и аналого-цифровых интерфейсах для обработки сигналов датчиков, работающих в условиях низких температур и воздействия радиации.

В современной радиоэлектронной аппаратуре находят применение дифференциальные операционные усилители (ОУ) с существенными различными параметрами входных каскадов (ВК). Особое место занимают ВК с парафазным выходом [1-51], которые обеспечивают более широкий динамический диапазон выходного напряжения, что важно при низковольтном питании, а также эффективное подавление синфазных сигналов и помех.

Одним из важных динамических параметров современных операционных усилителей, работающих в условиях низких температур и проникающей радиации, является дифференциальный коэффициент усиления разомкнутого ОУ (K0), оказывающий существенное влияние на предельные точностные параметры многих вариантов построения аналоговых интерфейсов. Как правило, данный параметр ОУ с традиционной схемотехникой существенно зависит от входного каскада и деградирует в тяжелых условиях эксплуатации.

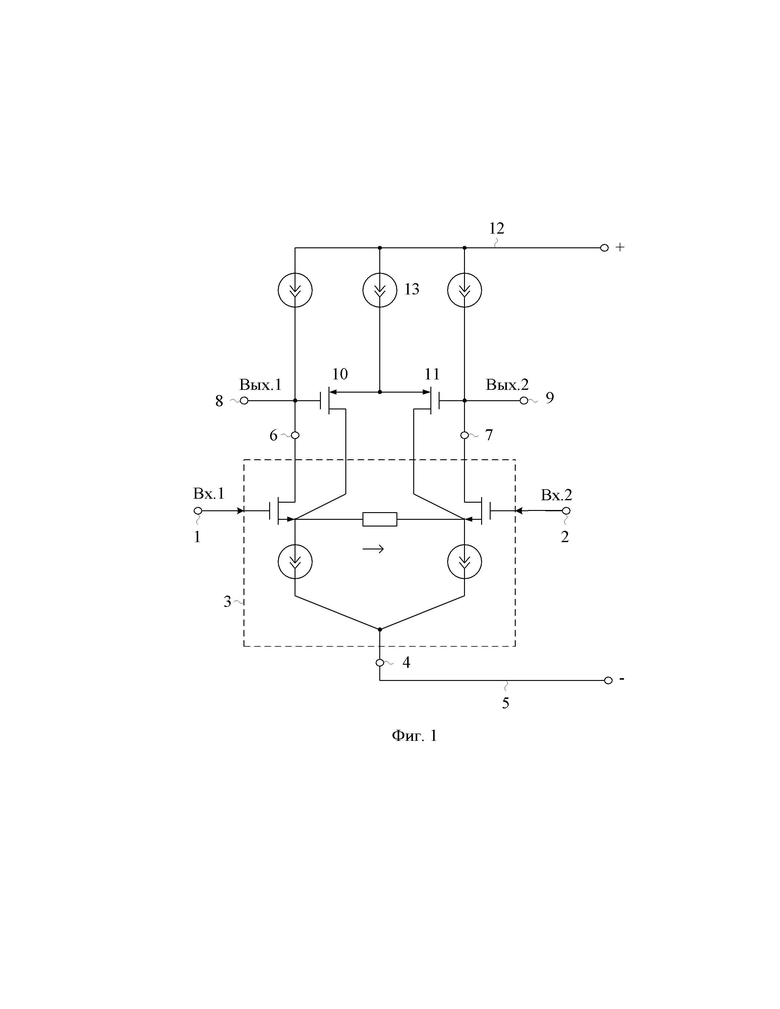

Ближайшим прототипом (фиг. 1) заявляемого устройства является входной каскад ОУ по патентной заявке фирмы Broadcom Corporation (США) US № 8.169.263, fig. 5, 2012г. Он содержит первый 1 и второй 2 входы входного дифференциального каскада 3, общая истоковая цепь 4 которого согласована с первой 5 шиной источника питания, первый 6 и второй 7 токовые выходы входного дифференциального каскада 3, первый 8 и второй 9 противофазные выходы устройства, первый 10 и второй 11 выходные полевые транзисторы, истоки которых объединены и связаны со второй 12 шиной источника питания через первый 13 токостабилизирующий двухполюсник.

Существенный недостаток известного ВК состоит в том, что при его практической реализации на основе комплементарных полевых транзисторах с управляющим p-n переходом он не обеспечивает повышенные значения Ку в диапазоне низких температур и флюенса электронов.

Основная задача предполагаемого изобретения состоит в обеспечении работоспособности ВК и ОУ на его основе в диапазоне криогенных температур и воздействии проникающей радиации, а также получении повышенных значений дифференциального коэффициента усиления.

Поставленная задача решается тем, что в входном каскаде операционного усилителя фиг. 1, содержащем первый 1 и второй 2 входы входного дифференциального каскада 3, общая истоковая цепь 4 которого согласована с первой 5 шиной источника питания, первый 6 и второй 7 токовые выходы входного дифференциального каскада 3, первый 8 и второй 9 противофазные выходы устройства, первый 10 и второй 11 выходные полевые транзисторы, истоки которых объединены и связаны со второй 12 шиной источника питания через первый 13 токостабилизирующий двухполюсник, предусмотрены новые элементы и связи – в схему введены первый 14 и второй 15 дополнительные полевые транзисторы, объединенные истоки которых связаны с токостабилизирующим элементом 16, затвор первого 14 дополнительного полевого транзистора связан с первым 8 выходом устройства и соединен со стоком первого 10 выходного полевого транзистора, затвор второго 15 дополнительного полевого транзистора связан со вторым 9 выходом устройства и соединен со стоком второго 11 выходного полевого транзистора, объединенные стоки первого 14 и второго 15 дополнительных полевых транзисторов соединены с объединенными стоками первый 10 и второй 11 выходных полевых транзисторов, первый 6 токовый выход входного дифференциального каскада 3 соединен с первым 8 выходом устройства, второй 7 токовый выход входного дифференциального каскада 3 связан со вторым 9 выходом устройства, причем затворы первого 10 и второго 11 выходных полевых транзисторов связаны со второй 12 шиной источника питания, а в качестве всех упомянутых выше полевых транзисторов используются полевые транзисторы с управляющим p-n переходом.

На чертеже фиг. 1 представлена схема ВК-прототипа.

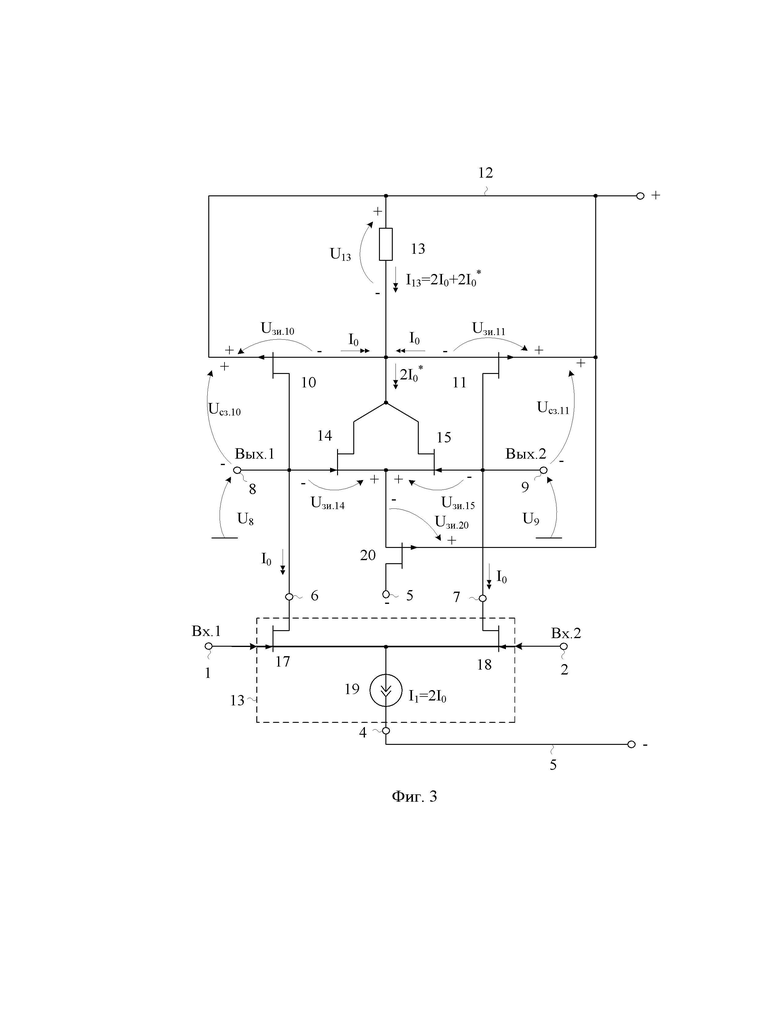

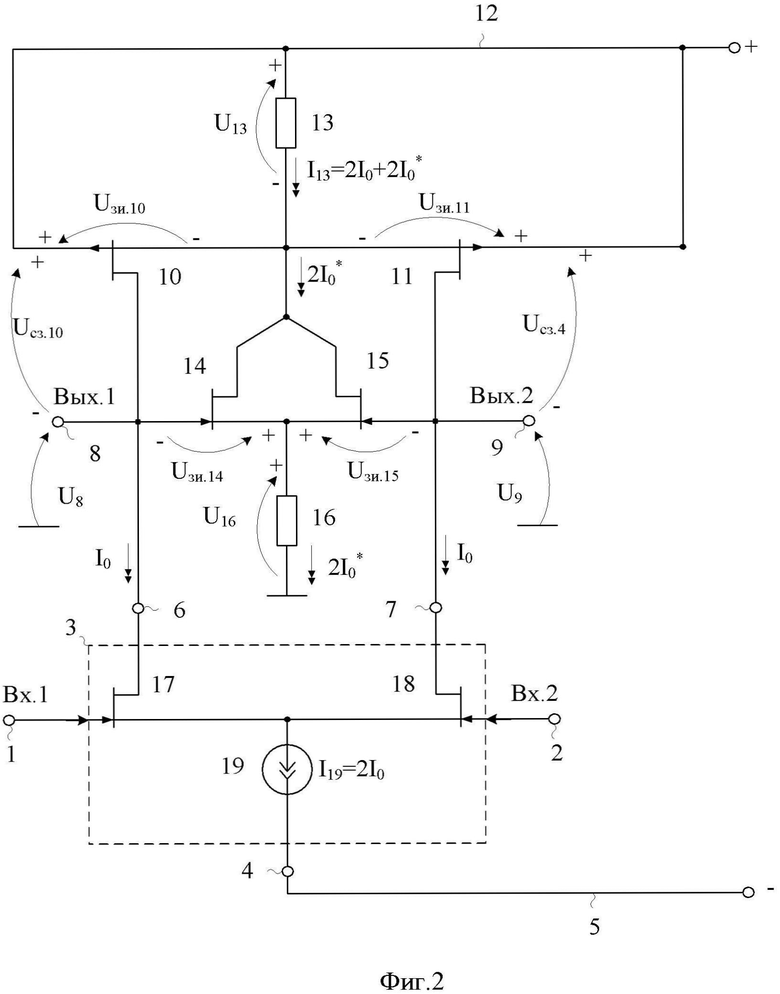

На чертеже фиг. 2 приведена схема заявляемого устройства в соответствии с п.1 формулы изобретения, а на чертеже фиг. 3 – в соответствии с п. 2 формулы изобретения.

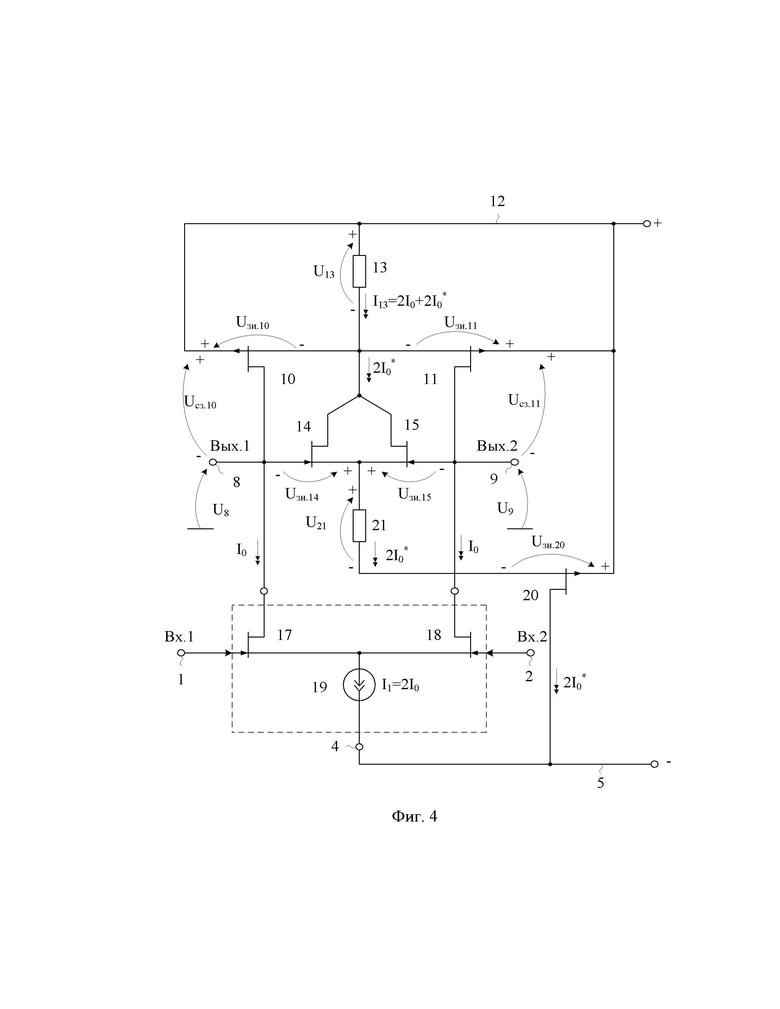

На чертеже фиг. 4 показана схема заявляемого устройства в соответствии с п. 3 формулы изобретения.

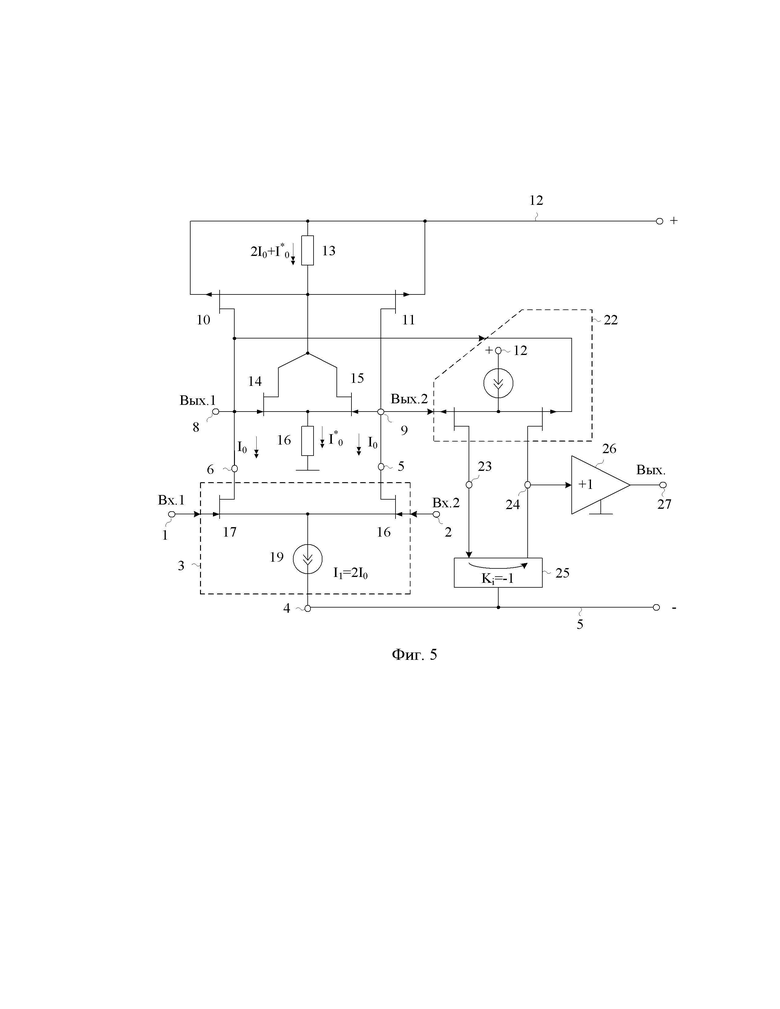

На чертеже фиг. 5 представлена схема включения заявляемого ВК фиг. 2, соответствующего п. 4 формулы изобретения, в операционном усилителе.

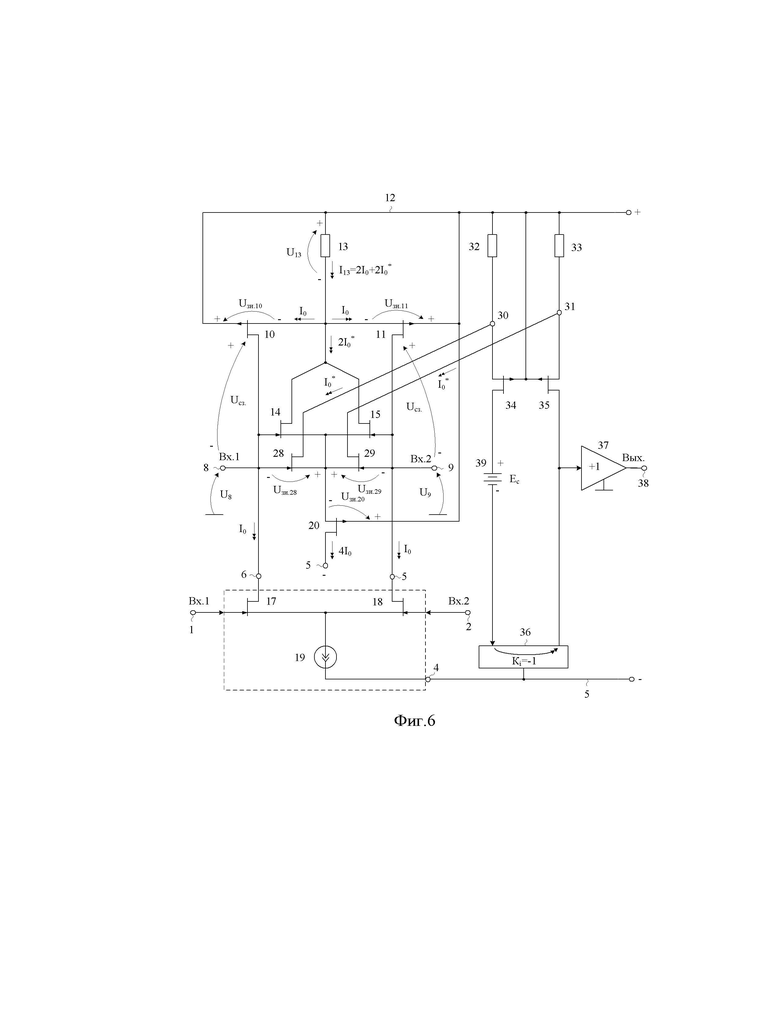

На чертеже фиг. 6 показана схема заявляемого входного каскада по п. 5 формулы изобретения и пример его подключения к выходному каскаду операционного усилителя, реализованного на элементах 31-39.

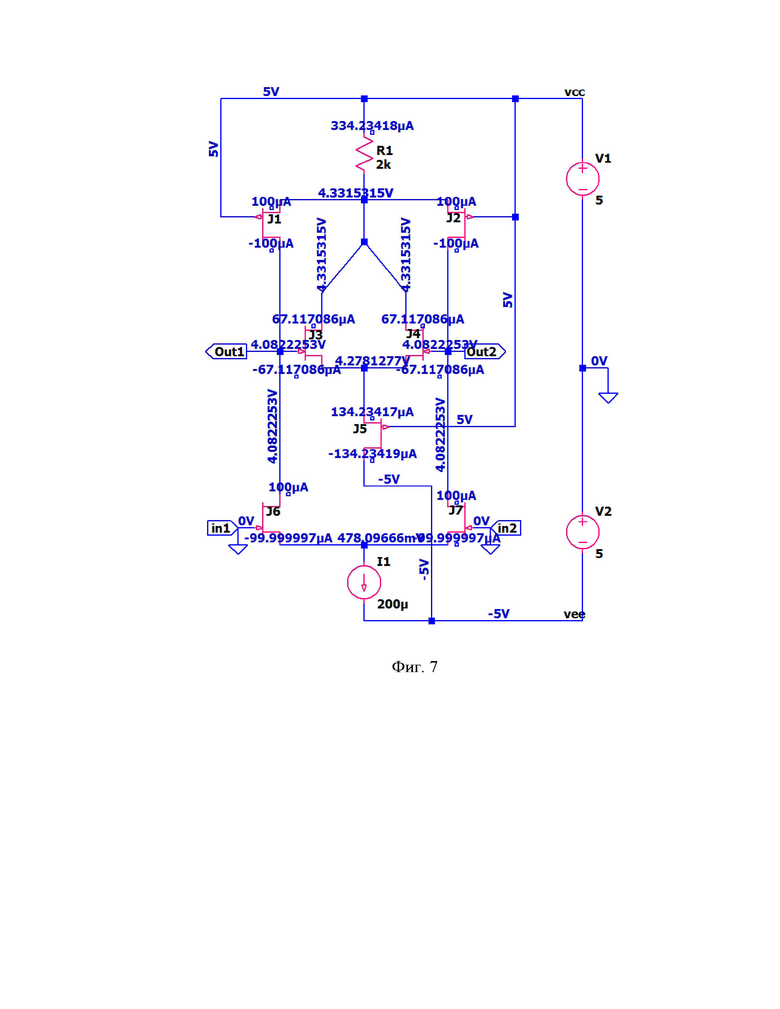

На чертеже фиг. 7 приведен статический режим ВК фиг.3 в среде LTspice на моделях интегральных транзисторов ОАО «Интеграл»( г. Минск) при температуре 27 °С, представленных в [52].

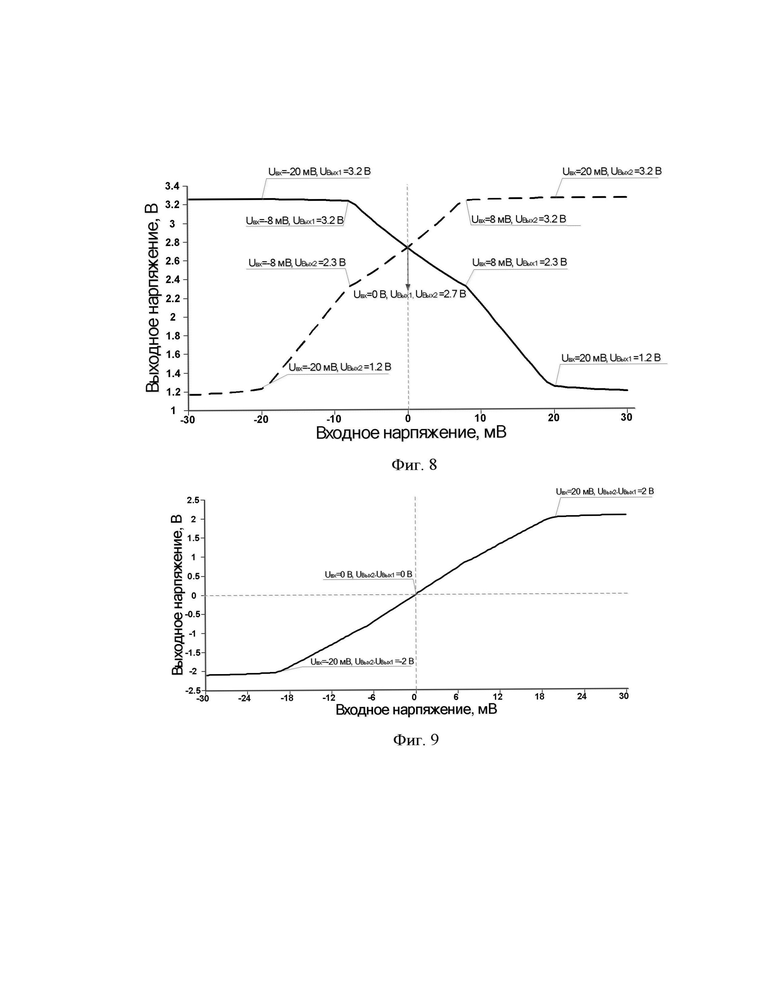

На чертеже фиг. 8 представлена зависимость выходных напряжений ВК фиг. 7 от входного напряжения при температуре 27°С, R1=5кОм, I1=200мкА.

На чертеже фиг. 9 показана зависимость дифференциального выходного напряжения (UВых. 2-UВых. 1) ВК фиг. 7 от входного дифференциального напряжения при температуре -19°С, R1=5кОм, I1=200 мкА.

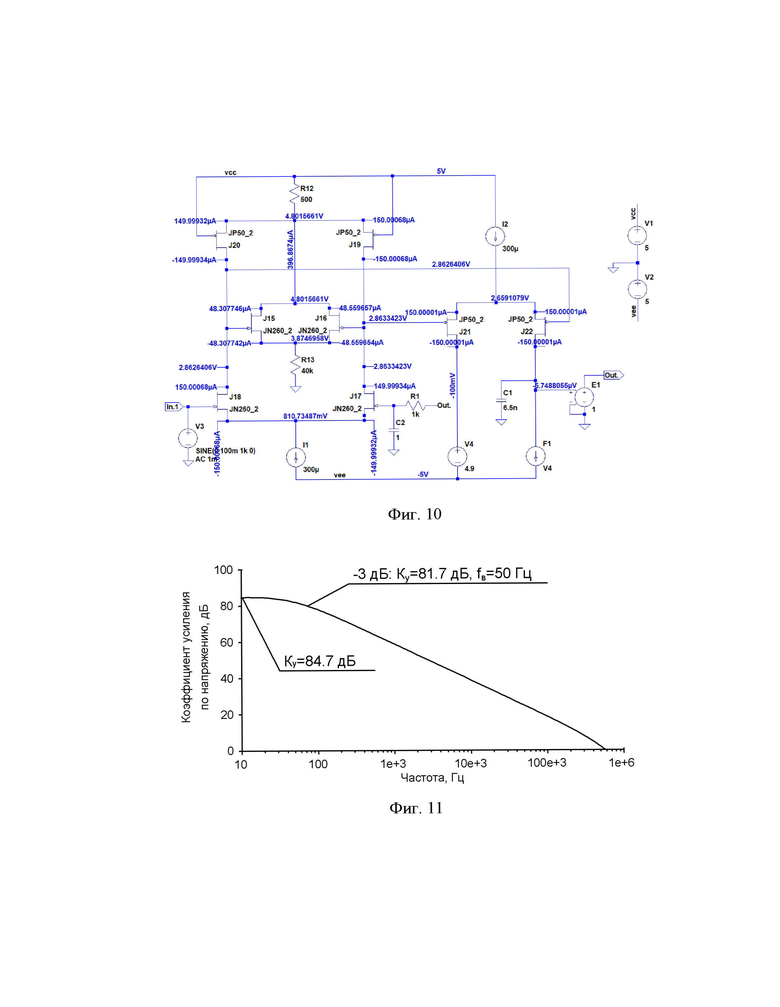

На чертеже фиг. 10 представлен статический режим схемы включения ВК фиг. 2 в ОУ фиг. 5 в среде LTspice при температуре -197ᵒС.

На чертеже фиг. 11 показана логарифмическая амплитудно-частотная характеристика (ЛАЧХ) коэффициента усиления по напряжению разомкнутого ОУ фиг. 8 с предлагаемым ВК при температуре -197ᵒ С.

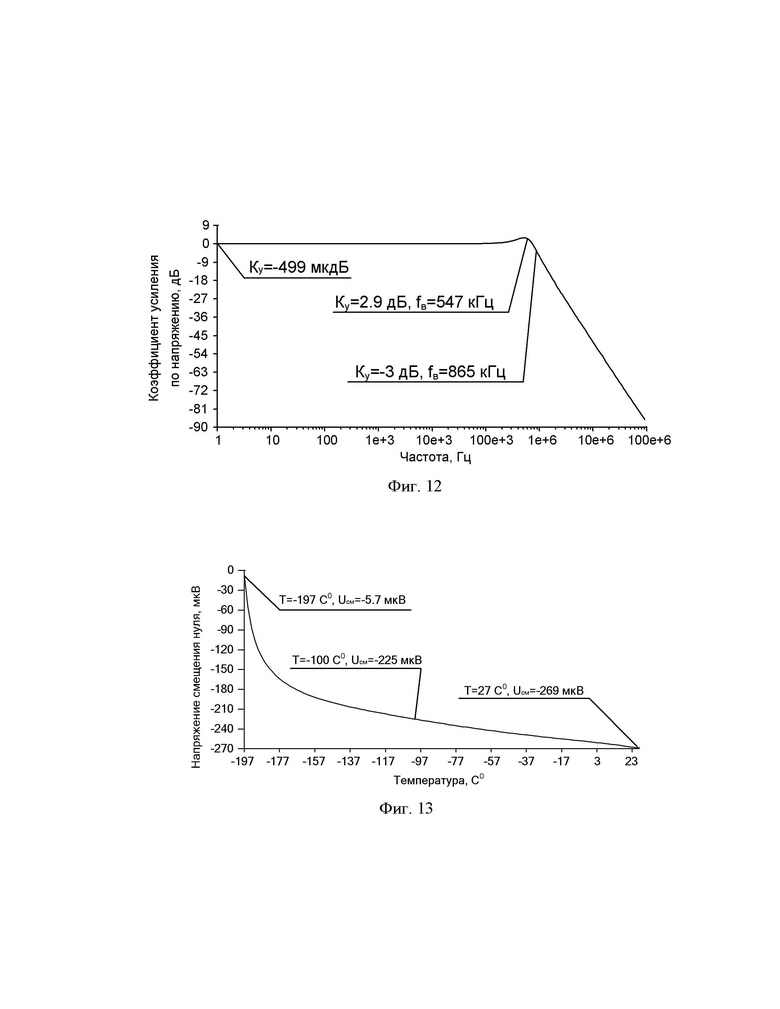

На чертеже фиг. 12 приведена ЛАЧХ коэффициента усиления по напряжению ОУ фиг. 10 со 100% отрицательной обратной связью при температуре -197°С.

На чертеже фиг. 13 представлена зависимость систематической составляющей напряжения смещения нуля ОУ фиг. 10 от температуры.

Входной каскад дифференциального операционного усилителя с парафазным выходом на комплементарных полевых транзисторах фиг. 2 содержит первый 1 и второй 2 входы входного дифференциального каскада 3, общая истоковая цепь 4 которого согласована с первой 5 шиной источника питания, первый 6 и второй 7 токовые выходы входного дифференциального каскада 3, первый 8 и второй 9 противофазные выходы устройства, первый 10 и второй 11 выходные полевые транзисторы, истоки которых объединены и связаны со второй 12 шиной источника питания через первый 13 токостабилизирующий двухполюсник. В схему введены первый 14 и второй 15 дополнительные полевые транзисторы, объединенные истоки которых связаны с токостабилизирующим элементом 16, затвор первого 14 дополнительного полевого транзистора связан с первым 8 выходом устройства и соединен со стоком первого 10 выходного полевого транзистора, затвор второго 15 дополнительного полевого транзистора связан со вторым 9 выходом устройства и соединен со стоком второго 11 выходного полевого транзистора, объединенные стоки первого 14 и второго 15 дополнительных полевых транзисторов соединены с объединенными стоками первый 10 и второй 11 выходных полевых транзисторов, первый 6 токовый выход входного дифференциального каскада 3 соединен с первым 8 выходом устройства, второй 7 токовый выход входного дифференциального каскада 3 связан со вторым 9 выходом устройства, причем затворы первого 10 и второго 11 выходных полевых транзисторов связаны со второй 12 шиной источника питания, а в качестве всех упомянутых выше полевых транзисторов используются полевые транзисторы с управляющим p-n переходом.

На чертеже фиг. 2 входной дифференциальный каскад 3 реализован на полевых транзисторах 17, 18 и источнике опорного тока 19.

На чертеже фиг. 3, в соответствии с п. 2 формулы изобретения, в качестве токостабилизирующего элемента 16 используется третий 20 дополнительный полевой транзистор с управляющим p-n переходом, исток которого связан с объединенными истоками первого 14 и второго 15 дополнительных полевых транзисторов с управляющим p-n переходом, затвор соединен со второй 12 шиной источника питания, а сток согласован с первой 5 шиной источника питания.

На чертеже фиг. 4, в соответствии с п. 3 формулы изобретения, исток третьего 20 дополнительного полевого транзистора с управляющим p-n переходом связан с объединенными истоками первого 14 и второго 15 дополнительных полевых транзисторов с управляющим p-n переходом через второй 21 токостабилизирующий двухполюсник.

На чертеже фиг. 5, в соответствии с п. 4 формулы изобретения, в схему введен дополнительный дифференциальный каскад 22, входы которого соединены с первым 8 и вторым 9 противофазными выходами устройства, а первый 23 и второй 24 дополнительные токовые выходы дополнительного дифференциального каскада 22 согласованы с первой 5 шиной источника питания.

В частном случае (фиг. 5) первый 23 и второй 24 дополнительные токовые выходы дополнительного дифференциального каскада 22 связаны с токовым зеркалом 25 и буферным усилителем 26, потенциальный выход которого 27 является выходом ОУ.

На чертеже фиг. 6, в соответствии с п. 5 формулы изобретения, в схему введены первый 28 и второй 29 вспомогательные полевые транзисторы с управляющим p-n переходом, истоки которых объединены и связаны с истоком третьего 20 дополнительного полевого транзистора с управляющим p-n переходом, стоки связаны с третьим 30 и четвертым 31 дополнительными токовыми выходами устройства, затвор первого 28 вспомогательного полевого транзистора с управляющим p-n переходом подключен к затвору первого 14 дополнительного полевого транзистора с управляющим p-n переходом, а затвор второго 29 вспомогательного полевого транзистора с управляющим p-n переходом подключен к затвору второго 15 дополнительного полевого транзистора с управляющим p-n переходом.

В схеме включения фиг. 6 выходная подсхема ОУ реализована на основе резисторов 32, 33, полевых транзисторов 34, 35, токовом зеркале 36, буферном усилителе 37, имеющего потенциальный выход 38. Для симметрирования статического режима в схеме фиг. 6 может использоваться цепь смещения потенциалов 39.

Рассмотрим работу заявляемого устройства фиг. 2.

Основная особенность заявляемой схемы ВК фиг. 2 – фиг. 4 состоит в нетрадиционном введении сигнала отрицательной обратной связи по выходному синфазному сигналу, которая реализуется за счет полевого транзистора с управляющим p-n переходом 20 и двухполюсника 21. Такое схемотехническое решение обеспечивает работу схемы при низких температурах, а также в условиях проникающей радиации.

Графики, представленные на чертежах фиг. 9, фиг. 11, показывают, что в широком диапазоне температур заявляемая схема ВК удовлетворяет многим применениям в структуре ОУ для задач космического приборостроения и физики высоких энергий.

Таким образом, предлагаемое устройство имеет существенные преимущества в сравнении с входным каскадом-прототипом.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

Патент US 6.937.100, 2005 г.

Патент US 6.956.434, fig.1, 2005 г.

Патент US 7.894.727, fig.3, 2011 г.

Патент US 5.880.634, fig.4,fig.7B, 1999 г.

Патент US 5.146.179, fig.2, 1992 г.

Патент US 6.924.701, fig.1B, fig.3, fig.1a, 2005 г.

Патент US 6.624.697, fig.1, 2003 г.

Патент US 6.356.152, fig.4, 2002 г.

Патент US 6.329.849, fig.8, 2001 г.

Патент US 5.376.899, fig.1, 1994 г.

Патент US 6.750.715, fig.4, 2004 г.

Патент US 5.604.464, fig.2, 1997 г.

Патент US 5.847.607, fig.8, 1998 г.

Патент US 5.406.220, fig.2, 1995 г.

Заявка на патент US 2005/0258907, 2005 г.

Патент US 6.628.168, fig.2, 2003 г.

Патент US 4.714.895, fig.1, 1997 г.

Патент EP 0 632 581, fig.3, 1995 г.

Патент US 4.697.152, fig.2,1987 г.

Патент US 5.212.455, 1993 г.

Патент US 6.804.305, fig.1, 2004 г.

Патент US 4.600.893, fig. 4, 1986 г.

Патент US 3.979.689, fig. 2, 1976 г.

Патент US RE 30.587, 1981 г.

Патент US 4.151.483, fig. 4, 1979 г.

Патент US 4.151.484, fig. 4, 1979 г.

Патент US 4.406.990, fig. 3, 1983 г.

Патент US 4.463.319, 1984 г.

Патент US 7.791.414, fig. 6, 2010 г.

Патент US 5.455.535, 1995 г.

Патент US 6.788.143, fig. 2, 2004 г.

Патент US 5.153.529, 1995 г.

Патентная заявка US 2003/0090321, fig. 8, 2007 г.

Патентная заявка US 2007/0069815, fig. 1, 2007 г.

Патент US 6.696.894, 2004 г.

Патент US 5.963.085, 1999 г.

Патент US 5.966.050, fig. 4, 1999 г.

Патент US 5.166.637, fig. 3, 1992 г.

Патент US 6.529.076, 2003 г.

Патент US 6.483.382, fig.2, fig.1, 2002 г.

Патент US 5.627.495, fig. 2, 1997 г.

Патент US 5.327.100, fig. 1, 1994 г.

Патент US 4.390.850, fig. 1, 1983 г.

Патент US 5.610.557, fig. 2A, 1997 г.

Патент US 8.350.622, 2013 г.

Патент US 5.418.491, fig.1, 1995 г.

Патент US 4.783.637, fig. 2, 1988 г.

Патент US 5.091.701, fig. 1, 1992 г.

Патент US 5.140.280, 1992 г.

Патент US 5.786.729, 1998 г.

I.M. Filanovsky, V.V. Ivanov, “Operational Amplifier Speed and Accuracy Improvement: Analog Circuit Design with Structural Methodology,” Kluwer Academic Publishers, New York, Boston, Dordrecht, London, 2004, 194 p.

1. O. V. Dvornikov, V. L. Dziatlau, N. N. Prokopenko, K. O. Petrosiants, N. V. Kozhukhov and V. A. Tchekhovski, "The accounting of the simultaneous exposure of the low temperatures and the penetrating radiation at the circuit simulation of the BiJFET analog interfaces of the sensors," 2017 International Siberian Conference on Control and Communications (SIBCON), Astana, 2017, pp. 1-6. DOI: 10.1109/SIBCON.2017.7998507

| название | год | авторы | номер документа |

|---|---|---|---|

| АРСЕНИД-ГАЛЛИЕВЫЙ ВХОДНОЙ ДИФФЕРЕНЦИАЛЬНЫЙ КАСКАД КЛАССА АВ БЫСТРОДЕЙСТВУЮЩЕГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ | 2022 |

|

RU2786943C1 |

| ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ ДЛЯ АКТИВНЫХ RC-ФИЛЬТРОВ, РАБОТАЮЩИХ В УСЛОВИЯХ ВОЗДЕЙСТВИЯ ПОТОКА НЕЙТРОНОВ И НИЗКИХ ТЕМПЕРАТУР | 2020 |

|

RU2724921C1 |

| Арсенид-галлиевый операционный усилитель | 2023 |

|

RU2813140C1 |

| ПРОМЕЖУТОЧНЫЙ КАСКАД CJFET ОПЕРАЦИОННОГО УСИЛИТЕЛЯ С ПАРАФАЗНЫМ ТОКОВЫМ ВЫХОДОМ | 2019 |

|

RU2712411C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ ПИТАНИЯ | 2015 |

|

RU2613842C1 |

| Арсенид-галлиевый операционный усилитель с повышенным коэффициентом усиления и малым уровнем систематической составляющей напряжения смещения нуля | 2023 |

|

RU2820562C1 |

| АРСЕНИД-ГАЛЛИЕВЫЙ ВЫХОДНОЙ КАСКАД БЫСТРОДЕЙСТВУЮЩЕГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ | 2022 |

|

RU2773912C1 |

| ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ «ПЕРЕГНУТОГО» КАСКОДА И КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРОВ | 2022 |

|

RU2773907C1 |

| Операционный усилитель на основе широкозонных полупроводников | 2023 |

|

RU2822157C1 |

| ВЫХОДНОЙ КАСКАД АНАЛОГОВЫХ МИКРОСХЕМ НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ С УПРАВЛЯЮЩИМ P-N-ПЕРЕХОДОМ | 2019 |

|

RU2710917C1 |

Изобретение относится к области радиотехники и аналоговой микроэлектроники. Технический результат заключается в обеспечении работоспособности ВК и ОУ на его основе в диапазоне криогенных температур и воздействии проникающей радиации, а также получении повышенных значений дифференциального коэффициента усиления. Входной каскад дифференциального операционного усилителя содержит источники питания, выходные полевые транзисторы, токостабилизирующий двухполюсник, дополнительные полевые транзисторы, в качестве всех упомянутых выше полевых транзисторов используются полевые транзисторы с управляющим p-n-переходом. 4 з.п. ф-лы, 13 ил.

1. Входной каскад дифференциального операционного усилителя с парафазным выходом на комплементарных полевых транзисторах, содержащий первый (1) и второй (2) входы входного дифференциального каскада (3), общая истоковая цепь (4) которого согласована с первой (5) шиной источника питания, первый (6) и второй (7) токовые выходы входного дифференциального каскада (3), первый (8) и второй (9) противофазные выходы устройства, первый (10) и второй (11) выходные полевые транзисторы, истоки которых объединены и связаны со второй (12) шиной источника питания через первый (13) токостабилизирующий двухполюсник, отличающийся тем, что в схему введены первый (14) и второй (15) дополнительные полевые транзисторы, объединенные истоки которых связаны с токостабилизирующим элементом (16), затвор первого (14) дополнительного полевого транзистора связан с первым (8) выходом устройства и соединен со стоком первого (10) выходного полевого транзистора, затвор второго (15) дополнительного полевого транзистора связан со вторым (9) выходом устройства и соединен со стоком второго (11) выходного полевого транзистора, объединенные стоки первого (14) и второго (15) дополнительных полевых транзисторов соединены с объединенными стоками первого (10) и второго (11) выходных полевых транзисторов, первый (6) токовый выход входного дифференциального каскада (3) соединен с первым (8) выходом устройства, второй (7) токовый выход входного дифференциального каскада (3) связан со вторым (9) выходом устройства, причем затворы первого (10) и второго (11) выходных полевых транзисторов связаны со второй (12) шиной источника питания, а в качестве всех упомянутых выше полевых транзисторов используются полевые транзисторы с управляющим p-n-переходом.

2. Входной каскад дифференциального операционного усилителя с парафазным выходом на комплементарных полевых транзисторах по п. 1, отличающийся тем, что в качестве токостабилизирующего элемента (16) используется третий (20) дополнительный полевой транзистор с управляющим p-n-переходом, исток которого связан с объединенными истоками первого (14) и второго (15) дополнительных полевых транзисторов с управляющим p-n-переходом, затвор соединен со второй (12) шиной источника питания, а сток согласован с первой (5) шиной источника питания.

3. Входной каскад дифференциального операционного усилителя с парафазным выходом на комплементарных полевых транзисторах по п. 2, отличающийся тем, что исток третьего (20) дополнительного полевого транзистора с управляющим p-n-переходом связан с объединенными истоками первого (14) и второго (15) дополнительных полевых транзисторов с управляющим p-n-переходом через второй (21) токостабилизирующий двухполюсник.

4. Входной каскад дифференциального операционного усилителя с парафазным выходом на комплементарных полевых транзисторах по п. 1, отличающийся тем, что в схему введен дополнительный дифференциальный каскад (22), входы которого соединены с первым (8) и вторым (9) противофазными выходами устройства, а первый (23) и второй (24) дополнительные токовые выходы дополнительного дифференциального каскада (22) согласованы с первой (5) шиной источника питания.

5. Входной каскад дифференциального операционного усилителя с парафазным выходом на комплементарных полевых транзисторах по п. 2, отличающийся тем, что в схему введены первый (28) и второй (29) вспомогательные полевые транзисторы с управляющим p-n-переходом, истоки которых объединены и связаны с истоком третьего (20) дополнительного полевого транзистора с управляющим p-n-переходом, стоки связаны с третьим (30) и четвертым (31) дополнительными токовыми выходами устройства, затвор первого (28) вспомогательного полевого транзистора с управляющим p-n-переходом подключен к затвору первого (14) дополнительного полевого транзистора с управляющим p-n-переходом, а затвор второго (29) вспомогательного полевого транзистора с управляющим p-n-переходом подключен к затвору второго (15) дополнительного полевого транзистора с управляющим p-n-переходом.

| Способ приготовления лака | 1924 |

|

SU2011A1 |

| ТОКОВОЕ ЗЕРКАЛО | 2008 |

|

RU2365969C1 |

| US 7463013 B2, 09.12.2008 | |||

| Повторитель тока | 1987 |

|

SU1529410A1 |

Авторы

Даты

2020-05-25—Публикация

2020-01-31—Подача