Изобретение относится к области радиотехники и аналоговой микроэлектроники и может быть использовано в аналоговых и аналого-цифровых интерфейсах для обработки сигналов датчиков.

В современной радиоэлектронной аппаратуре находят применение дифференциальные операционные усилители (ОУ) с существенными различными параметрами. Особое место занимают ОУ на основе комплементарных входных каскадов (так называемых dual-input-stage) [1-31]. Входные каскады (ВК) данного класса реализуются как на биполярных [1-16], так и на КМОП транзисторах [17-30]. Архитектура ОУ с такими ВК [1-31] является основой более чем 50 серийных микросхем, выпускаемых ведущими микроэлектронными фирмами мира.

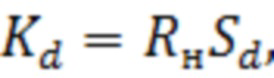

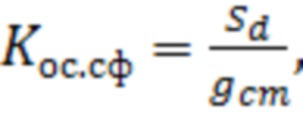

Ближайшим прототипом (фиг. 1) заявляемого устройства является входной каскад в структуре операционного усилителя на основе токовых зеркал ПТ1, ПТ2 по патентной заявке US 2006/0125522, fig. 1a, fig. 3, 2006 г. Он содержит (фиг. 1) первый 1 и второй 2 входы устройства, первый 3 токовый выход устройства, согласованный с первой 4 шиной источника питания, второй 5 токовый выход устройства, согласованный со второй 6 шиной источника питания, первый 7 и второй 8 входные полевые транзисторы с объединенными истоками, третий 9 и четвертый 10 входные полевые транзисторы с объединенными истоками, первый 11 источник опорного тока, связанный с объединенными истоками первого 7 и второго 8 входных полевых транзисторов с объединенными истоками, второй 12 источник опорного тока, связанный с объединенными истоками третьего 9 и четвертого 10 входных полевых транзисторов с объединенными истоками, причем первый 1 вход устройства соединён с затворами первого 7 и третьего 9 входных полевых транзисторов, второй 2 вход устройства соединен с затворами второго 8 и четвертого 10 входных полевых транзисторов, сток второго 8 входного полевого транзистора подключен к первому 3 токовому выходу устройства, сток четвертого 10 входного полевого транзистора связан со вторым 5 токовым выходом устройства, сток первого 7 входного полевого транзистора соединен с третьим 13 токовым выходом устройства, согласованным с первой 4 шиной источника питания, а сток третьего 9 входного полевого транзистора соединен с четвертым 14 токовым выходом устройства, согласованным со второй 6 шиной источника питания.

Существенный недостаток известного входного каскада ОУ состоит в том, что при его практической реализации на основе комплементарных полевых транзисторов с управляющим p-n переходом он обеспечивает небольшие значения коэффициента ослабления входных синфазных сигналов (Кос.сф). Это связано с тем, что в схеме ВК-прототипа на его Кос.сф оказывают существенное влияние выходные сопротивления первого 11 (ri11) и второго 12 (ri12) источников опорного тока, которые создают "паразитные" каналы передачи входного синфазного сигнала uc=uc1=uc2 к первому 3 и второму 5 токовым выходам устройства.

Основная задача предполагаемого изобретения состоит в повышении коэффициента ослабления входных синфазных сигналов при реализации ВК на комплементарных полевых транзисторах с управляющим p-n переходом, оказывающего существенное влияние на погрешности различных аналоговых интерфейсов с заявляемым устройством.

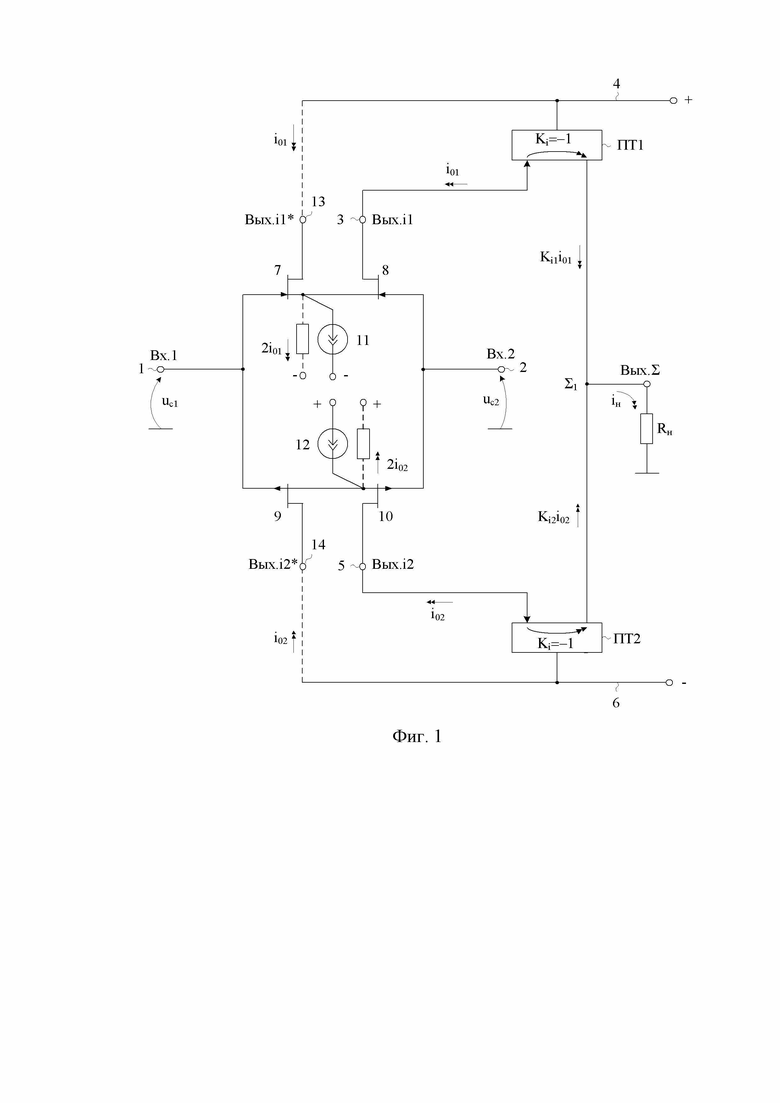

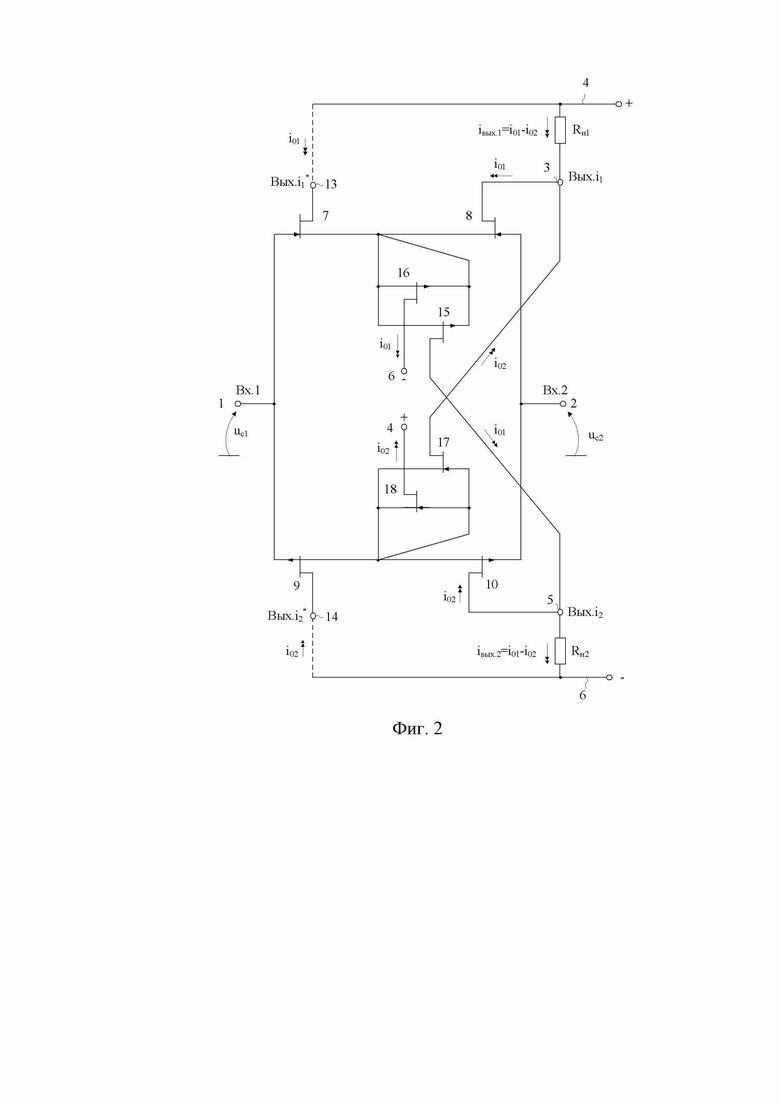

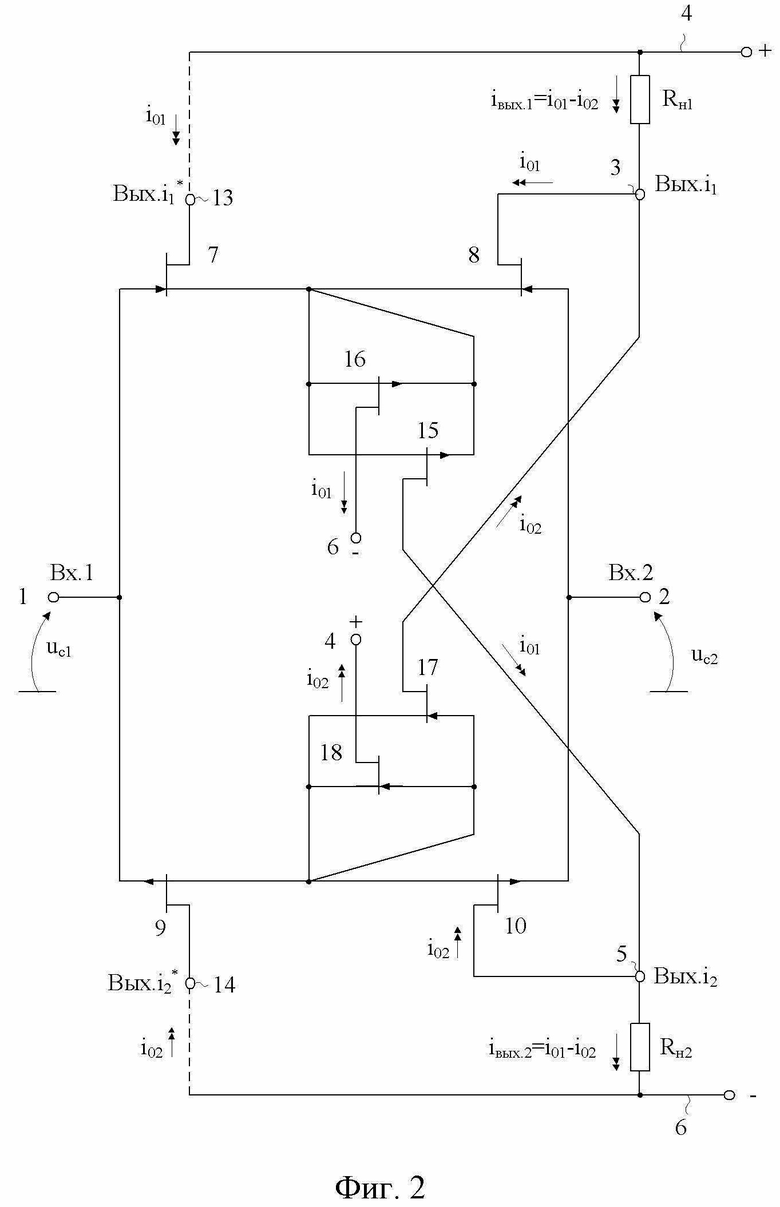

Поставленная задача решается тем, что во входном каскаде операционного усилителя фиг. 2, содержащем первый 1 и второй 2 входы устройства, первый 3 токовый выход устройства, согласованный с первой 4 шиной источника питания, второй 5 токовый выход устройства, согласованный со второй 6 шиной источника питания, первый 7 и второй 8 входные полевые транзисторы с объединенными истоками, третий 9 и четвертый 10 входные полевые транзисторы с объединенными истоками, первый 11 источник опорного тока, связанный с объединенными истоками первого 7 и второго 8 входных полевых транзисторов с объединенными истоками, второй 12 источник опорного тока, связанный с объединенными истоками третьего 9 и четвертого 10 входных полевых транзисторов с объединенными истоками, причем первый 1 вход устройства соединён с затворами первого 7 и третьего 9 входных полевых транзисторов, второй 2 вход устройства соединен с затворами второго 8 и четвертого 10 входных полевых транзисторов, сток второго 8 входного полевого транзистора подключен к первому 3 токовому выходу устройства, сток четвертого 10 входного полевого транзистора связан со вторым 5 токовым выходом устройства, сток первого 7 входного полевого транзистора соединен с третьим 13 токовым выходом устройства, согласованным с первой 4 шиной источника питания, а сток третьего 9 входного полевого транзистора соединен с четвертым 14 токовым выходом устройства, согласованным со второй 6 шиной источника питания, предусмотрены новые элементы и связи – первый 11 источник опорного тока выполнен на основе первого 15 и второго 16 дополнительных полевых транзисторах, затворы которых подключены к объединенным истокам первого 7 и второго 8 входных полевых транзисторов, а истоки связаны с объединенными истоками первого 7 и второго 8 входных полевых транзисторов, причем сток первого 15 дополнительного полевого транзистора соединен со вторым 5 токовым выходом устройства, а сток второго 16 дополнительного полевого транзистора согласован со второй 6 шиной источника питания, второй 12 источник опорного тока выполнен на основе третьего 17 и четвертого 18 дополнительных полевых транзисторов, затворы которых подключены к объединенным истокам третьего 9 и четвертого 10 входных полевых транзисторов, а истоки связаны с объединенными истоками третьего 9 и четвертого 10 входных полевых транзисторов, причем, сток третьего 17 дополнительного полевого транзистора соединен с первым 3 токовым выходом устройства, а сток четвертого 18 дополнительного полевого транзистора согласован с первой 4 шиной источника питания, причем в качестве упомянутых выше полевых транзисторов применены полевые транзисторы с управляющим p-n переходом.

На чертеже фиг. 1 представлен входной каскад-прототип в структуре типового операционного усилителя на основе токовых зеркал ПТ1, ПТ2.

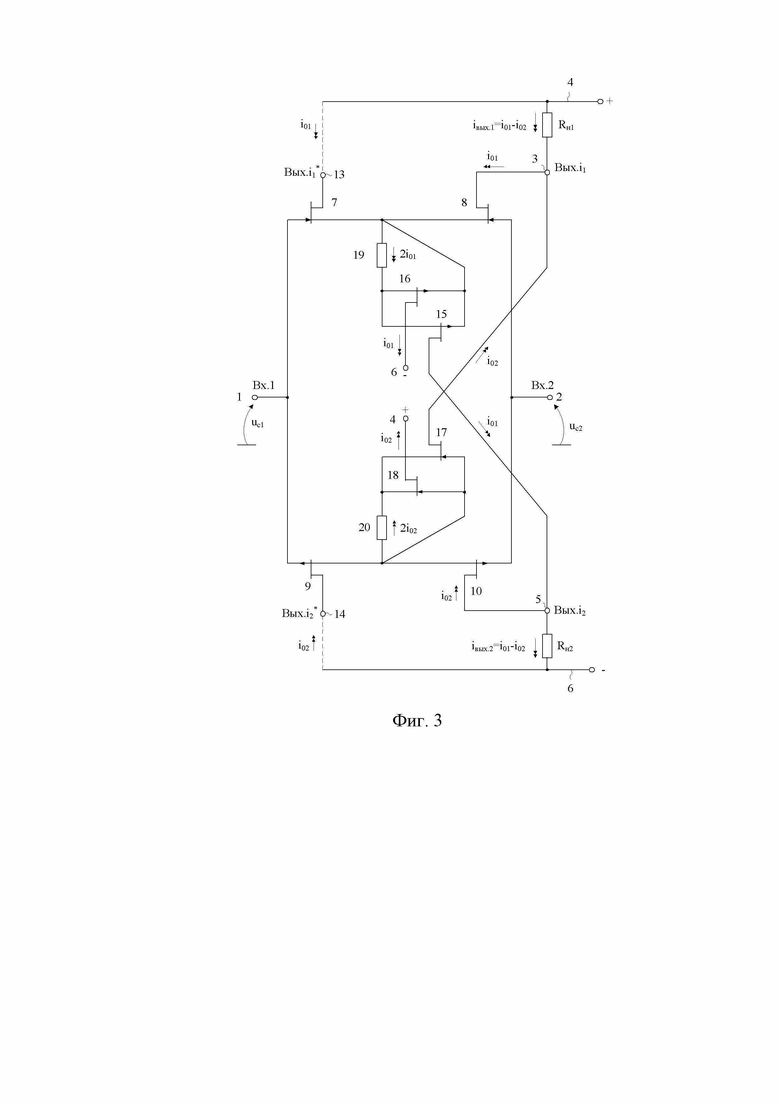

На чертеже фиг. 2 приведена схема заявляемого устройства в соответствии с п.1 формулы изобретения, а на чертеже фиг. 3 - схема ВК в соответствии с п.2 формулы изобретения.

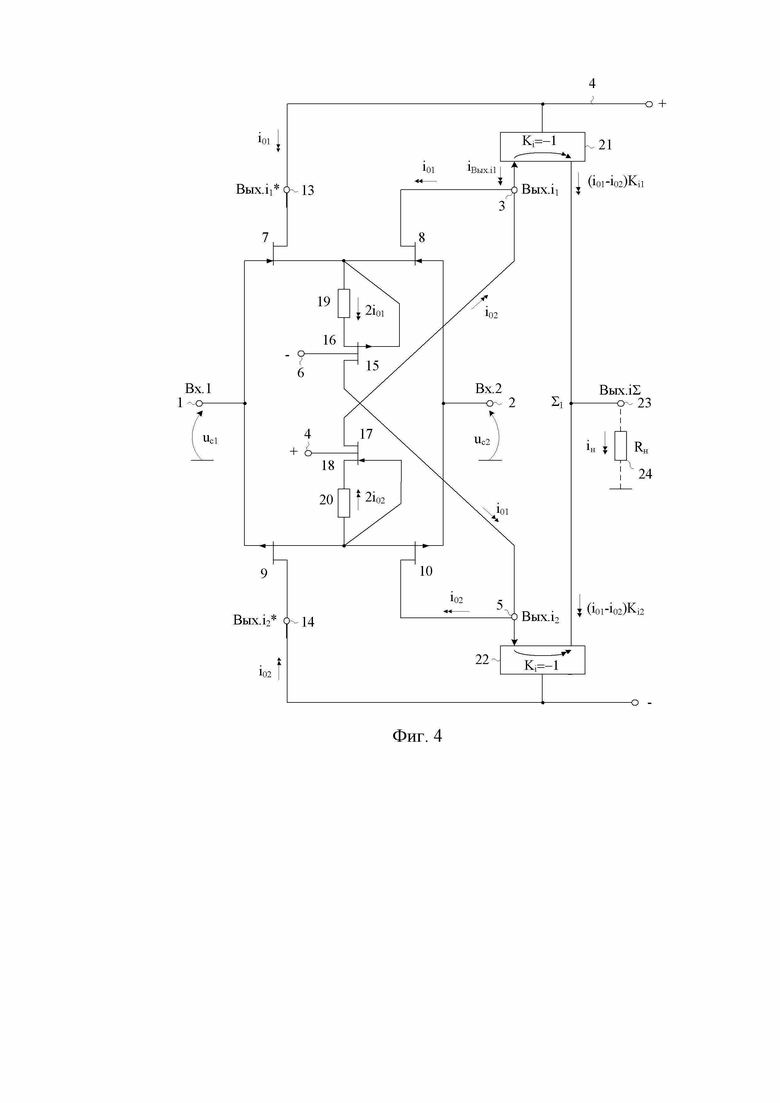

На чертеже фиг. 4 показана схема включения заявляемого входного каскада фиг. 3 в структуре ОУ на токовых зеркалах 21 и 22.

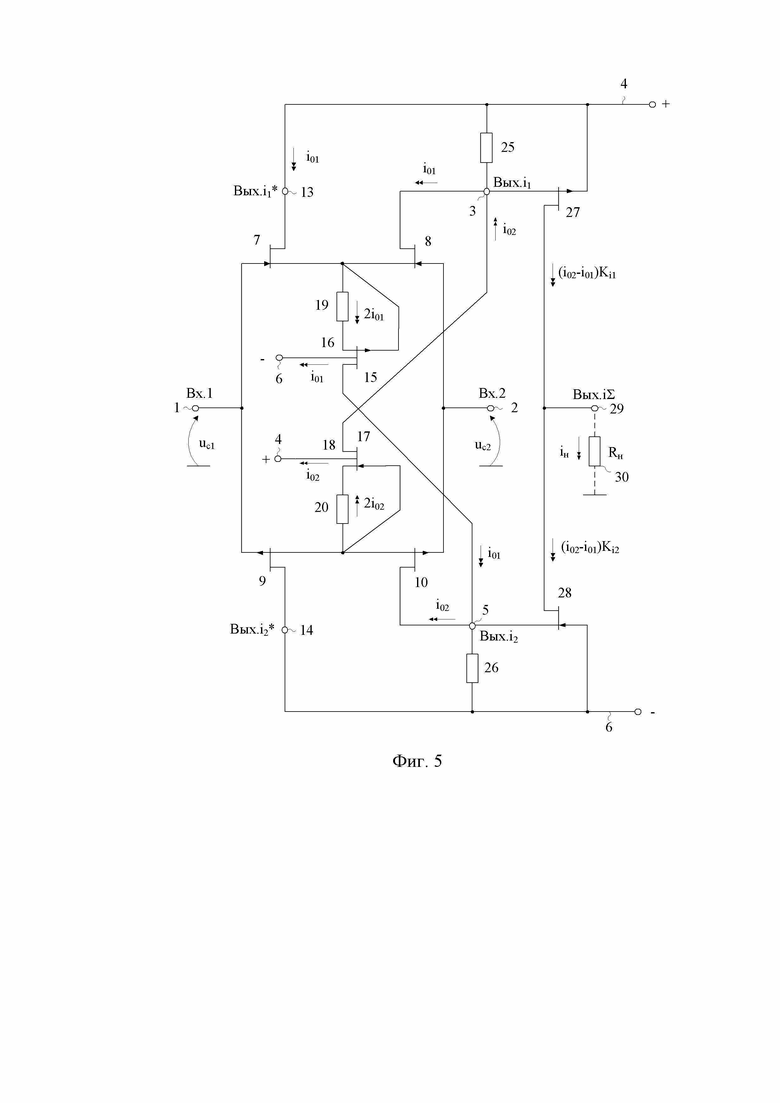

На чертеже фиг. 5 приведена схема включения заявляемого входного каскада фиг. 3 в структуре ОУ на «перегнутых» каскодах (элементы 25-28).

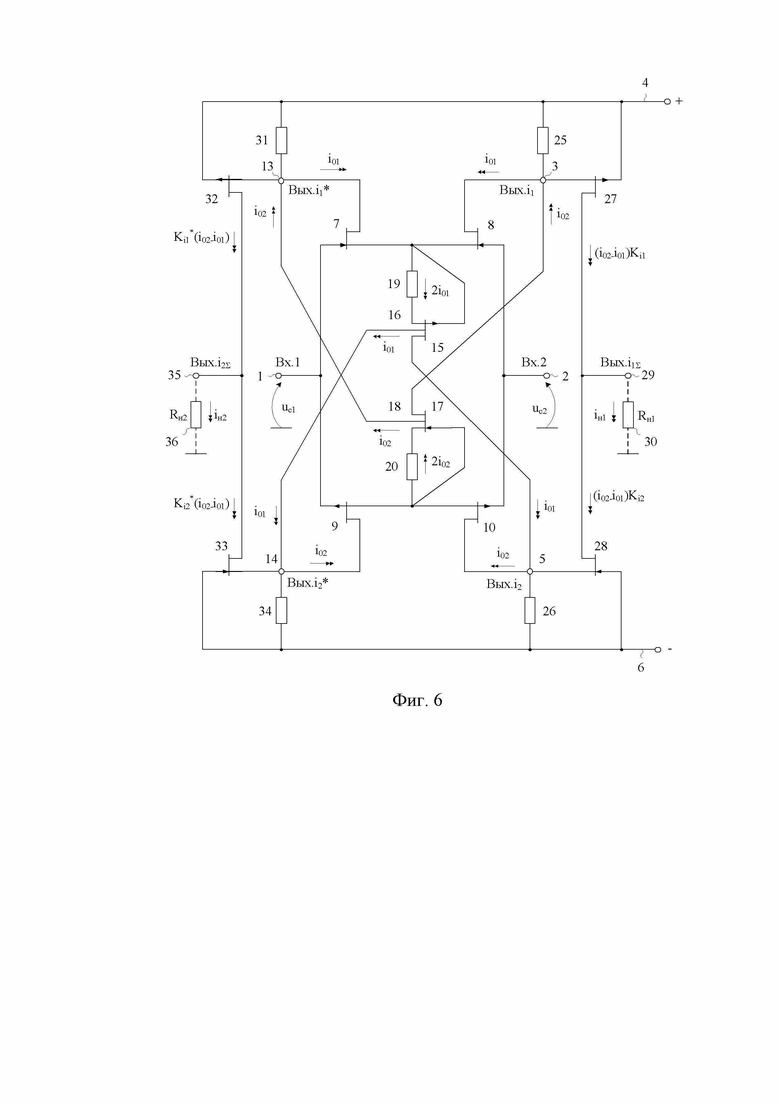

На чертеже фиг. 6 представлена схема включения заявляемого входного каскада фиг. 3 в структуре ОУ с парафазным выходом, выходные каскады которого реализованы на «перегнутых» каскодах (элементы 25-28 и 31-34).

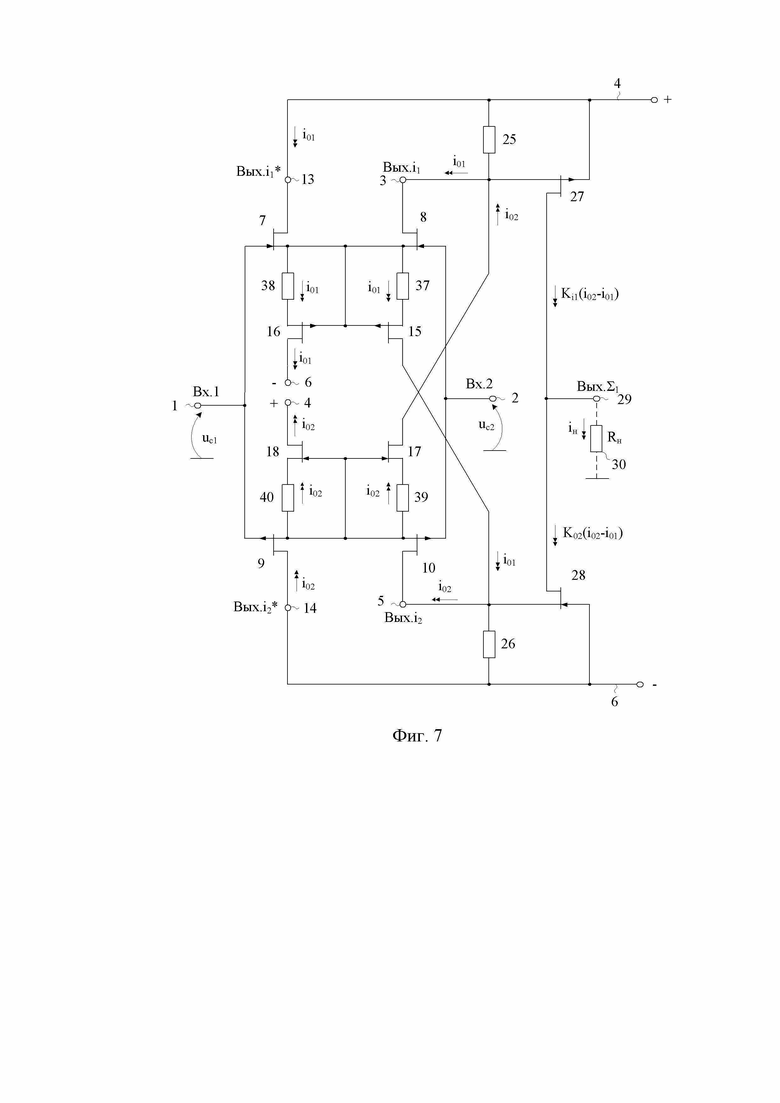

На чертеже фиг. 7 показана схема включения заявляемого входного каскада по п. 3 формулы изобретения в структуре ОУ на «перегнутых» каскодах (элементы 25-28).

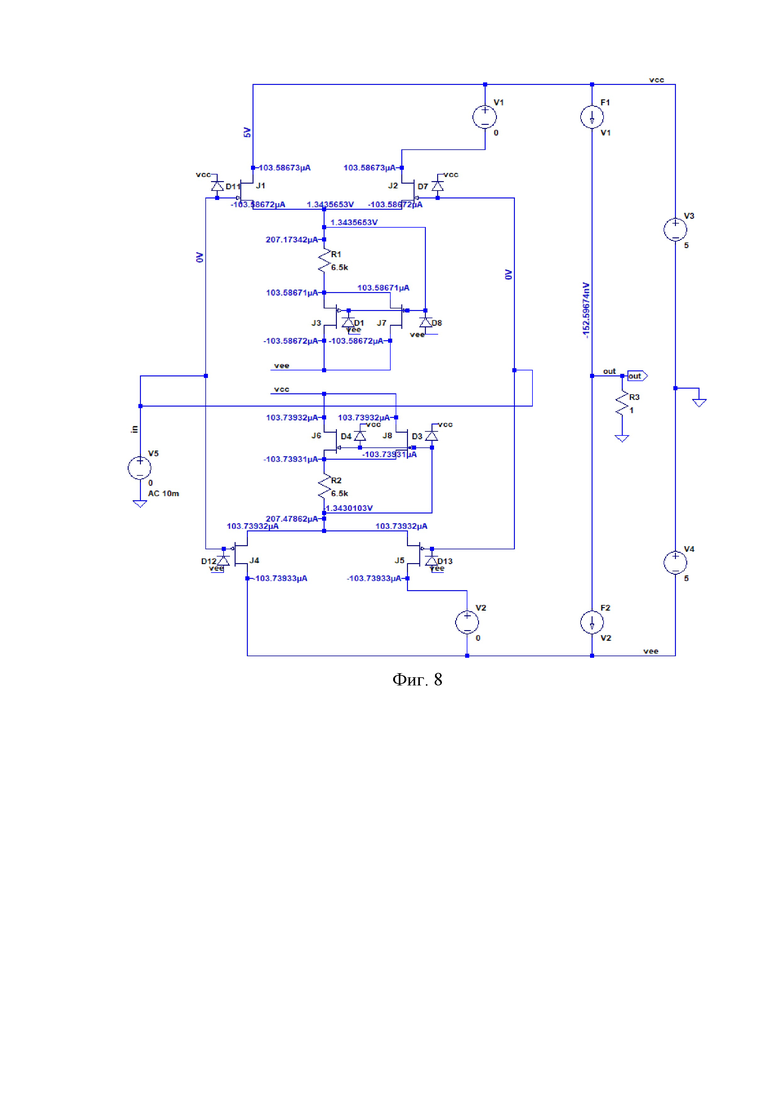

На чертеже фиг. 8 приведен статический режим входного каскада - прототипа фиг. 1 в структуре ОУ на основе токовых зеркал в среде моделирования LTSpice на моделях интегральных транзисторов ОАО «Интеграл» (г.Минск) при t=27°C.

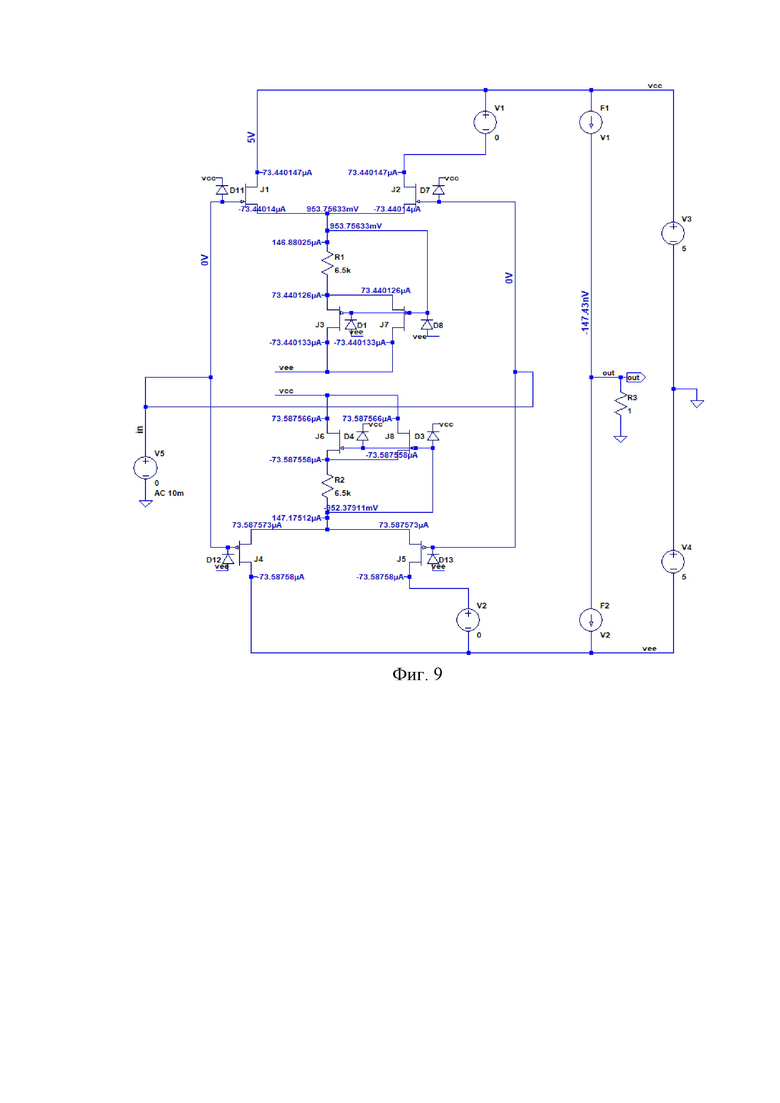

На чертеже фиг. 9 представлен статический режим входного каскада - прототипа фиг. 1 в структуре ОУ на основе токовых зеркал в среде моделирования LTSpice на моделях интегральных транзисторов ОАО «Интеграл» (г.Минск) при температуре t=-197°C.

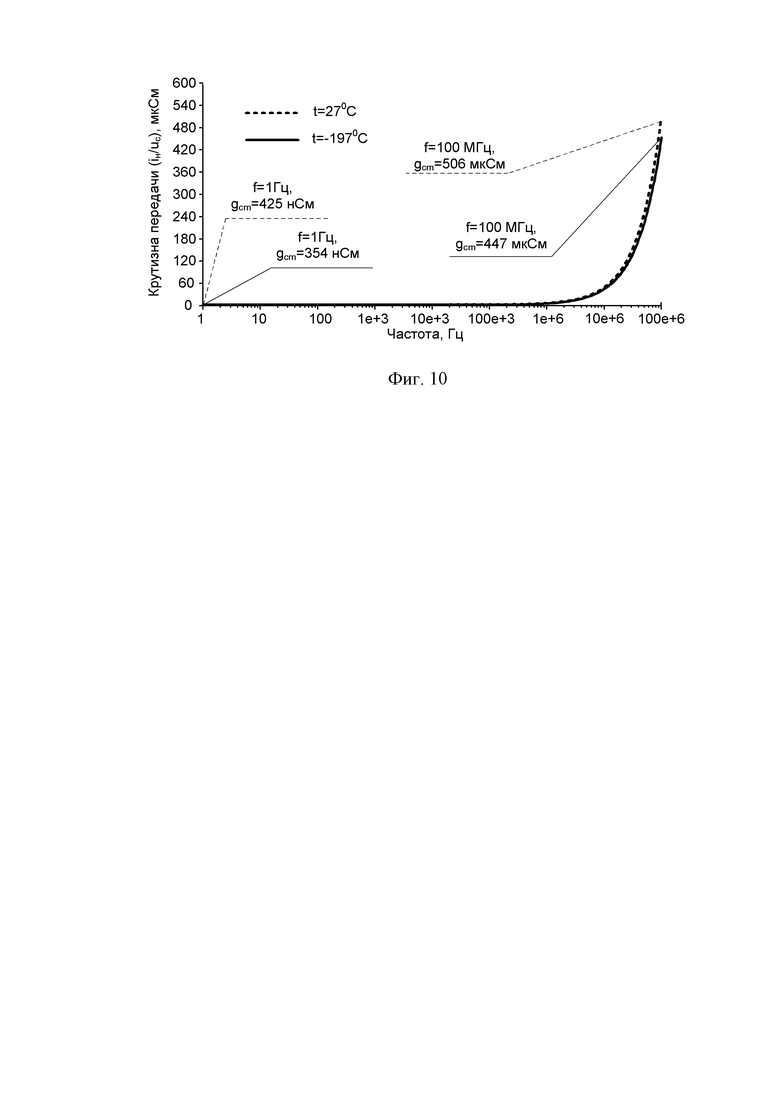

На чертеже фиг. 10 показана частотная зависимость крутизны gcm=iн/uc передачи входного синфазного сигнала uc=uc1=uc2 в типовом ОУ с входным каскадом-прототипом фиг. 8 при температурах 27°С и -197°С.

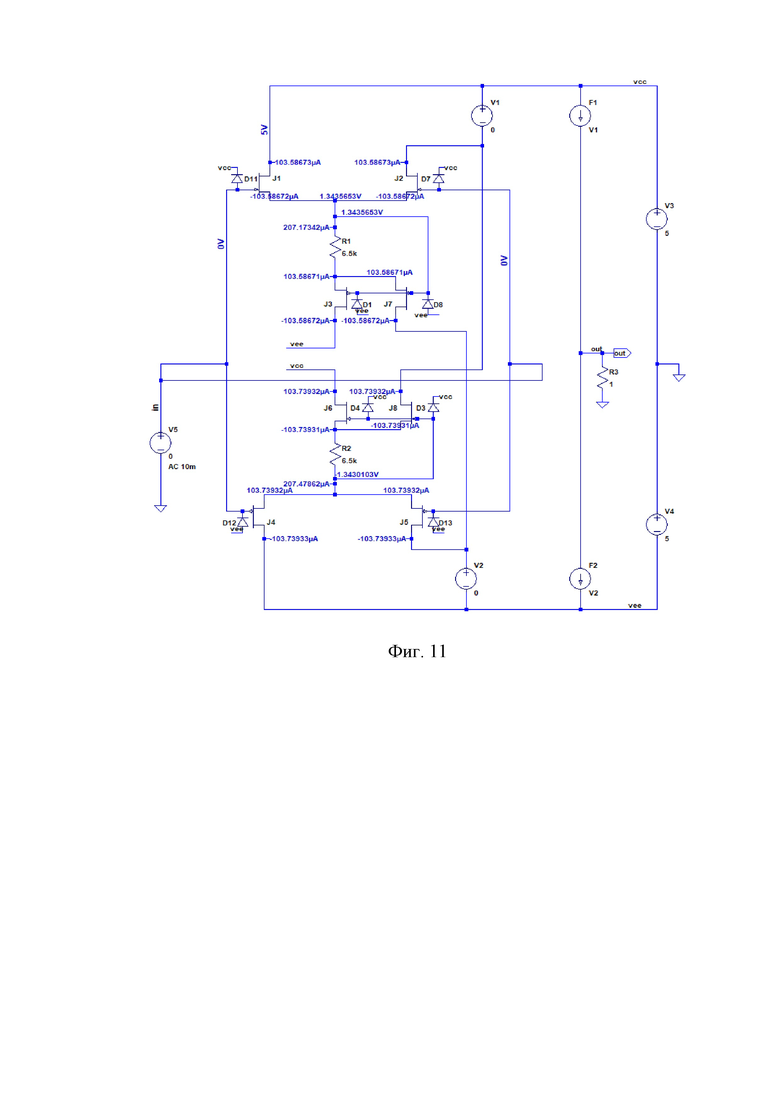

На чертеже фиг. 11 приведен статический режим заявляемого входного каскада фиг. 4 в структуре ОУ на токовых зеркалах в среде моделирования LTSpice на моделях интегральных транзисторов ОАО «Интеграл» (г.Минск) при t=27°С.

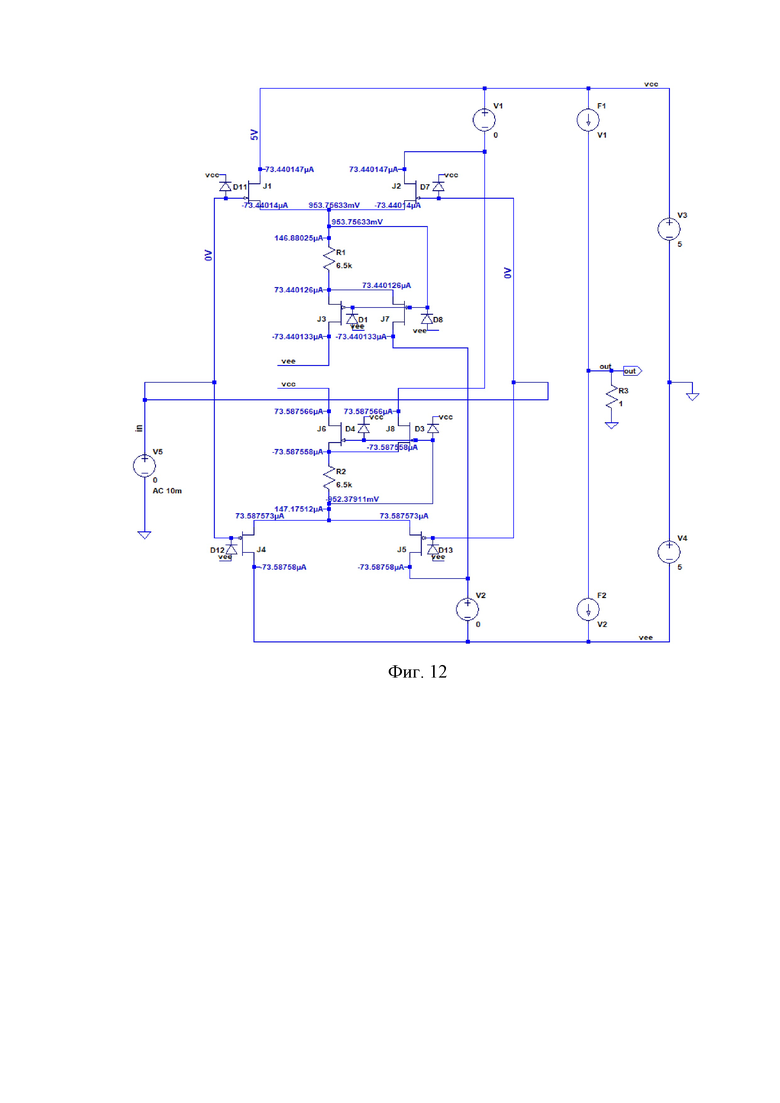

На чертеже фиг. 12 представлен статический режим заявляемого входного каскада фиг. 4 в структуре ОУ на токовых зеркалах в среде моделирования LTSpice на моделях интегральных транзисторов ОАО «Интеграл» (г.Минск) при t=-197°С.

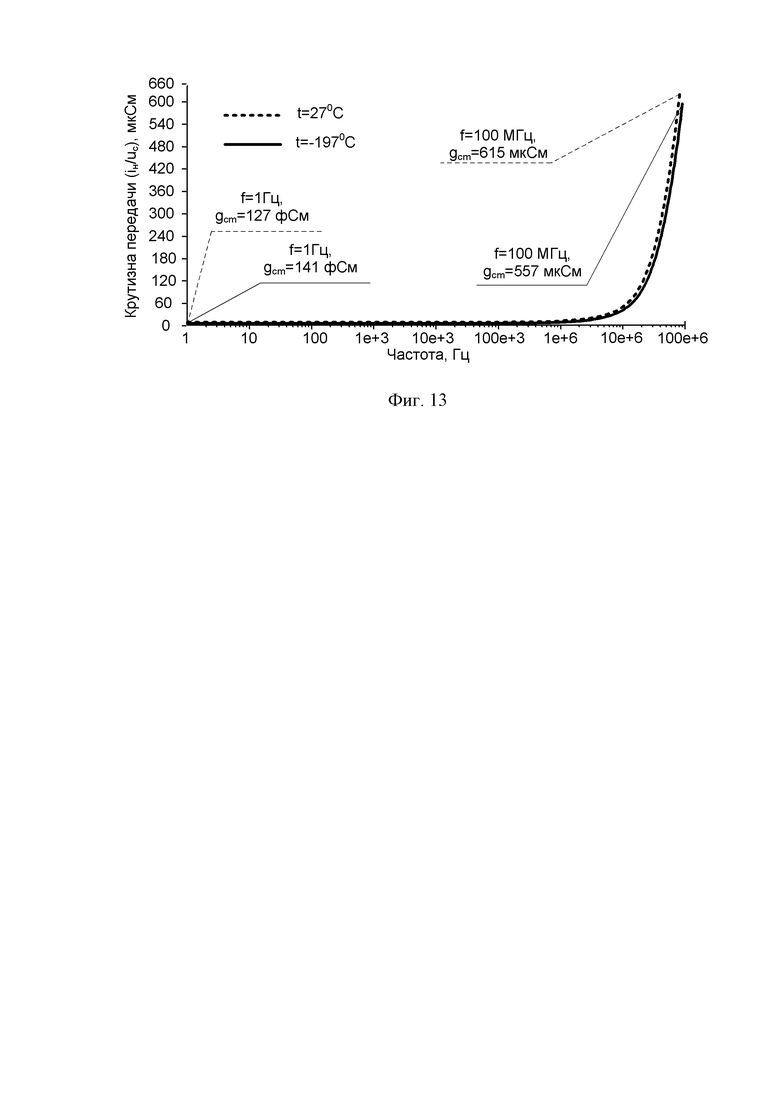

На чертеже фиг. 13 показана частотная зависимость крутизны gcm передачи входного синфазного сигнала uc=uc1=uc2 в типовом ОУ с заявляемым входным каскадом фиг. 11 при при температурах 27°С и -197°С.

Низкотемпературный входной каскад операционного усилителя с повышенным ослаблением входного синфазного сигнала на комплементарных полевых транзисторах с управляющим p-n переходом фиг. 2 содержит первый 1 и второй 2 входы устройства, первый 3 токовый выход устройства, согласованный с первой 4 шиной источника питания, второй 5 токовый выход устройства, согласованный со второй 6 шиной источника питания, первый 7 и второй 8 входные полевые транзисторы с объединенными истоками, третий 9 и четвертый 10 входные полевые транзисторы с объединенными истоками, первый 11 источник опорного тока, связанный с объединенными истоками первого 7 и второго 8 входных полевых транзисторов с объединенными истоками, второй 12 источник опорного тока, связанный с объединенными истоками третьего 9 и четвертого 10 входных полевых транзисторов с объединенными истоками, причем первый 1 вход устройства соединён с затворами первого 7 и третьего 9 входных полевых транзисторов, второй 2 вход устройства соединен с затворами второго 8 и четвертого 10 входных полевых транзисторов, сток второго 8 входного полевого транзистора подключен к первому 3 токовому выходу устройства, сток четвертого 10 входного полевого транзистора связан со вторым 5 токовым выходом устройства, сток первого 7 входного полевого транзистора соединен с третьим 13 токовым выходом устройства, согласованным с первой 4 шиной источника питания, а сток третьего 9 входного полевого транзистора соединен с четвертым 14 токовым выходом устройства, согласованным со второй 6 шиной источника питания. Первый 11 источник опорного тока выполнен на основе первого 15 и второго 16 дополнительных полевых транзисторах, затворы которых подключены к объединенным истокам первого 7 и второго 8 входных полевых транзисторов, а истоки связаны с объединенными истоками первого 7 и второго 8 входных полевых транзисторов, причем сток первого 15 дополнительного полевого транзистора соединен со вторым 5 токовым выходом устройства, а сток второго 16 дополнительного полевого транзистора согласован со второй 6 шиной источника питания, второй 12 источник опорного тока выполнен на основе третьего 17 и четвертого 18 дополнительных полевых транзисторов, затворы которых подключены к объединенным истокам третьего 9 и четвертого 10 входных полевых транзисторов, а истоки связаны с объединенными истоками третьего 9 и четвертого 10 входных полевых транзисторов, причем, сток третьего 17 дополнительного полевого транзистора соединен с первым 3 токовым выходом устройства, а сток четвертого 18 дополнительного полевого транзистора согласован с первой 4 шиной источника питания, причем в качестве упомянутых выше полевых транзисторов применены полевые транзисторы с управляющим p-n переходом.

На чертеже фиг. 3, в соответствии с п. 2 формулы изобретения, истоки первого 15 и второго 16 дополнительных полевых транзисторов связаны с объединенными истоками первого 7 и второго 8 входных полевых транзисторов через первый 19 дополнительный резистор, а истоки третьего 17 и четвертого 18 дополнительных полевых транзисторов связаны с объединенными истоками третьего 9 и четвертого 10 входных полевых транзисторов через второй 20 дополнительный резистор.

На чертеже фиг. 4 заявляемый входной каскад фиг. 3 используется в структуре операционного усилителя на токовых зеркалах 21 и 22, выходы которых подключены к выходу устройства 23. Двухполюсник 24 моделирует свойства нагрузки ОУ.

На чертеже фиг. 5 заявляемый входной каскад фиг. 3 используется в структуре операционного усилителя, выходной каскад которого реализован на «перегнутых» каскодах и включает вспомогательные резисторы 25, 26 и выходные полевые транзисторы 27, 28, стоки которых соединены с выходом устройства 29. Двухполюсник 30 моделирует свойства нагрузки ОУ.

На чертеже фиг. 6 представлена схема включения заявляемого входного каскада фиг. 3 в структуре ОУ с парафазным выходом, первый выходной каскад которого реализован на «перегнутых» каскодах и включает вспомогательные резисторы 25, 26, выходные полевые транзисторы 27, 28, стоки которых соединены с первым 29 выходом устройства. Двухполюсник 30 здесь моделирует свойства нагрузки ОУ, подключаемой к выходу первого выходного каскада (элементы 25-28). Второй выходной каскад в схеме фиг. 6 реализован на «перегнутых» каскодах и включает вспомогательные резисторы 31, 34, выходные полевые транзисторы 32, 33, стоки которых соединены со вторым 35 выходом устройства. Двухполюсник 36 здесь моделирует свойства нагрузки ОУ, подключаемой к выходу 35 второго выходного каскада (элементы 31,32,33,34).

На чертеже фиг. 7, в соответствии с п. 3 формулы изобретения, исток первого 15 дополнительного полевого транзистора связан с объединенными истоками первого 7 и второго 8 входных полевых транзисторов через третий 37 дополнительный резистор, исток второго 16 дополнительного полевого транзистора связан с объединенными истоками первого 7 и второго 8 входных полевых транзисторов через четвертый 38 дополнительный резистор, исток третьего 17 дополнительного полевого транзистора связан с объединенными истоками третьего 9 и четвертого 10 входных полевых транзисторов через пятый 39 дополнительный резистор, а исток четвертого 18 дополнительного полевого транзистора связан с объединенными истоками третьего 9 и четвертого 10 входных полевых транзисторов через шестой 40 дополнительный резистор. При этом на чертеже фиг. 7 заявляемый входной каскад по п. 3 подключен к выходному каскаду на «перегнутых» каскодах, который реализован на элементах 25, 26, 27, 28 и имеет первый выход устройства 29, к которому подключается двухполюсник нагрузки 30.

Рассмотрим работу заявляемого устройства фиг. 3.

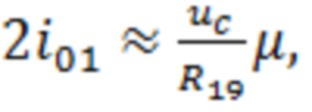

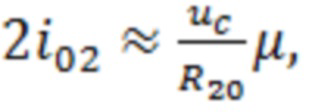

Изменения входного синфазного сигнала uc=uc1=uc2 на первом 1 и втором 2 входах устройства приводят к появлению приращений токов через первый 19 и второй 20 дополнительные резисторы

(1)

(1)

(2)

(2)

где R19, R20 – сопротивления первого 19 и второго 20 дополнительных резисторов,

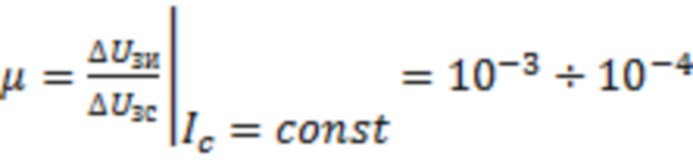

μ - коэффициент внутренней обратной связи полевых транзисторов 15 (16) и 17 (18), учитывающий влияние изменений напряжений на стоках этих транзисторов на смещение их стоко-затворных характеристик при постоянном токе стока:

. (3)

. (3)

Приращение токов 2i01, 2i02 через первый 19 и второй 20 дополнительные резисторы передаются соответственно на первый 3 и второй 5 токовые выходы. В результате в эквивалентных сопротивлениях нагрузки (Rн1, Rн2) токи i01 и i02 вычитаются, что уменьшает проводимость передачи входного синфазного сигнала gcm = iвых/uc на эти выходы.

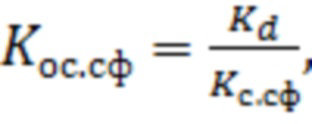

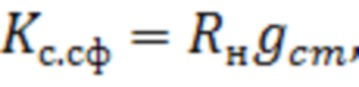

Если в качестве нагрузки, подключаемой к первому 3 и второму 5 токовым выходам, используются токовые зеркала 21 и 22, как это сделано в схеме фиг. 4, то в двухполюснике нагрузки 24 обеспечивается взаимная компенсация ошибок, обусловленных «пролезанием» входного синфазного сигнала на выход устройства 23. В конечном итоге, это улучшает Кос.сф. Действительно, Кос.сф в схеме ОУ фиг. 4 определяется формулами

(4)

(4)

(5)

(5)

(6)

(6)

(7)

(7)

где Kd – коэффициент усиления входного дифференциального сигнала ОУ (uвх=uc1-uc2);

Кс.сф – коэффициент преобразования входного синфазного сигнала uс=uc1=uc2 в выходное напряжение ОУ;

Sd – крутизна передачи входного дифференциального напряжения с первого 1 и второго 2 входов устройства на выход ОУ 23;

gcm<<Sd – крутизна передачи входного синфазного сигнала uc=uc1=uc2 на выход 23.

Как следует из графиков фиг. 10 и фиг. 13, заявляемый ВК, в отличие от ВК-прототипа фиг. 1, обеспечивает пренебрежимо малые значения gcm, что способствует повышению Кос.сф (формулы 4-7).

Указанные выше эффекты компенсации ошибок от синфазного сигнала работают также в схемах фиг. 5, фиг. 6 и фиг. 7, в которых используется заявляемый входной каскад (фиг. 3), а также выходные каскады на «перегнутых» каскодах.

Таким образом, предлагаемый входной каскад ОУ обеспечивает повышение Кос.сф в ОУ с разными вариантами построения выходных каскадов (фиг.4, фиг. 5, фиг. 6, фиг. 7).

Результаты компьютерного моделирования ОУ с предлагаемым входным каскадом фиг. 3, представленные на чертеже фиг. 10 и фиг. 13, показывают, что проводимости передачи синфазного сигнала на выход такого ОУ уменьшаются на низких частотах в широком диапазоне температур на несколько порядков. Причем этот выигрыш (N-раз) определяется отношением проводимостей передачи синфазного сигнала ОУ с входным каскадом без компенсации (прототип фиг. 1) к проводимости передачи синфазного сигнала ОУ с заявляемым ВК фиг. 3.

Таким образом, предлагаемый входной каскад обладает существенными преимуществами в сравнении с ВК-прототипом. Благодаря применению полевых транзисторов с управляющим p-n переходом схема заявляемого ВК и ОУ на его основе устойчиво работают в диапазоне криогенных температур и в условиях проникающей радиации [32], а также обеспечивает экстремально малый уровень низкочастотных шумов.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Заявка на патент US 2006/0125522, fig.1a, fig.3, 2006 г.

2. Заявка на патент US 2005/0024140, fig.12, 2005 г.

3. Патент US 5.714.906, fig. 1a, 1998 г.

4. Патент US 7.915.948, fig. 6, fig. 10, 2011 г.

5. Патент US 4.783.637, fig. 1, 1988 г.

6. Патент US 5.515.005, fig.1, fig. 2, 1996 г.

7. Патент SU № 1220105, 1984 г.

8. Патент US 3.968.451, fig.7, 1976 г.

9. Патент US 5.374.897, fig. 3, 1994 г.

10. Патент US 6.504.419, fig. 2, 2003 г.

11. Патент US 5.512.859, fig. 1, 1996 г.

12. Патент US 4.636.743, fig. 1,1987 г.

13. Патент US 6.268.769, fig. 3, 2001 г.

14. Патент US 3.974.455, fig. 7, 1976 г.

15. Патент US 5.291.149, 1994 г.

16. Авт. свид. СССР № 530425

17. Патент US 5.814.953, 1998 г.

18. Патент US 5.225.791, 1993 г.

19. Авт. свид. СССР № 611288

20. Патент US 6.794.940, fig. 1, 2004 г.

21. Патентная заявка US 2006/0226908, fig. 4, 2006 г.

22. Патентная заявка US 2001/0052818, fig. 1, 2001 г.

23. Заявка на патент US 2004/0174216, fig. 1, fig. 2, 2004 г.

24. Патент EP 1150423, fig.2, 2001 г.

25. Патентная заявка US 2003/0206060, fig. 1, 2003 г.

26. Патент US 6.642.789, fig. 1, 2003 г.

27. Патент US 4.377.789, fig. 1, 1983 г.

28. Патент US 6.100.762, fig. 1, 2000 г.

29. Патент US 5.909.146, fig. 5, 1999 г.

30. Патент US 5.621.357, fig. 4, 1997 г.

31. Патент US 6.844.781, fig.2, 2005 г.

32. O. V. Dvornikov, V. L. Dziatlau, N. N. Prokopenko, K. O. Petrosiants, N. V. Kozhukhov and V. A. Tchekhovski, "The accounting of the simultaneous exposure of the low temperatures and the penetrating radiation at the circuit simulation of the BiJFET analog interfaces of the sensors," 2017 International Siberian Conference on Control and Communications (SIBCON), Astana, 2017, pp. 1-6. DOI: 10.1109/SIBCON.2017.7998507

| название | год | авторы | номер документа |

|---|---|---|---|

| ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ ДВУХТАКТНОГО "ПЕРЕГНУТОГО" КАСКОДА И КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРОВ С УПРАВЛЯЮЩИМ PN-ПЕРЕХОДОМ | 2022 |

|

RU2780220C1 |

| Операционный усилитель с промежуточным двухтактным «перегнутым» каскодом на комплементарных полевых транзисторах | 2024 |

|

RU2837569C1 |

| Операционный усилитель на основе широкозонных полупроводников | 2023 |

|

RU2822157C1 |

| ПРОМЕЖУТОЧНЫЙ КАСКАД ОПЕРАЦИОННОГО УСИЛИТЕЛЯ С ПАРАФАЗНЫМ ВЫХОДОМ НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ С УПРАВЛЯЮЩИМ P-N ПЕРЕХОДОМ | 2019 |

|

RU2720555C1 |

| Арсенид-галлиевый операционный усилитель на основе "перегнутого" каскода | 2023 |

|

RU2820341C1 |

| Арсенид-галлиевый операционный усилитель с малым напряжением смещения нуля | 2023 |

|

RU2812914C1 |

| ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ «ПЕРЕГНУТОГО» КАСКОДА И КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРОВ | 2022 |

|

RU2773907C1 |

| Прецизионный арсенид-галлиевый операционный усилитель с малым уровнем систематической составляющей напряжения смещения нуля и повышенным коэффициентом усиления | 2023 |

|

RU2813370C1 |

| Арсенид-галлиевый операционный усилитель на p-n-p биполярных и полевых транзисторах с управляющим p-n переходом | 2023 |

|

RU2813281C1 |

| Арсенид-галлиевый операционный усилитель для работы в широком диапазоне температур | 2023 |

|

RU2814685C1 |

Изобретение относится к области радиотехники и аналоговой микроэлектроники. Технический результат заключается в повышении коэффициента ослабления входных синфазных сигналов, оказывающего существенное влияние на погрешности различных аналоговых интерфейсов с заявляемым устройством. Низкотемпературный входной каскад содержит шины источника питания, входные полевые транзисторы с объединенными истоками, источники опорного тока, дополнительные полевые транзисторы, причем в качестве упомянутых выше полевых транзисторов применены полевые транзисторы с управляющим p-n переходом. 2 з.п. ф-лы, 13 ил.

1. Низкотемпературный входной каскад операционного усилителя с повышенным ослаблением входного синфазного сигнала на комплементарных полевых транзисторах с управляющим p-n переходом, содержащий первый (1) и второй (2) входы устройства, первый (3) токовый выход устройства, согласованный с первой (4) шиной источника питания, второй (5) токовый выход устройства, согласованный со второй (6) шиной источника питания, первый (7) и второй (8) входные полевые транзисторы с объединенными истоками, третий (9) и четвертый (10) входные полевые транзисторы с объединенными истоками, первый (11) источник опорного тока, связанный с объединенными истоками первого (7) и второго (8) входных полевых транзисторов с объединенными истоками, второй (12) источник опорного тока, связанный с объединенными истоками третьего (9) и четвертого (10) входных полевых транзисторов с объединенными истоками, причем первый (1) вход устройства соединён с затворами первого (7) и третьего (9) входных полевых транзисторов, второй (2) вход устройства соединен с затворами второго (8) и четвертого (10) входных полевых транзисторов, сток второго (8) входного полевого транзистора подключен к первому (3) токовому выходу устройства, сток четвертого (10) входного полевого транзистора связан со вторым (5) токовым выходом устройства, сток первого (7) входного полевого транзистора соединен с третьим (13) токовым выходом устройства, согласованным с первой (4) шиной источника питания, а сток третьего (9) входного полевого транзистора соединен с четвертым (14) токовым выходом устройства, согласованным со второй (6) шиной источника питания, отличающийся тем, что первый (11) источник опорного тока выполнен на основе первого (15) и второго (16) дополнительных полевых транзисторах, затворы которых подключены к объединенным истокам первого (7) и второго (8) входных полевых транзисторов, а истоки связаны с объединенными истоками первого (7) и второго (8) входных полевых транзисторов, причем сток первого (15) дополнительного полевого транзистора соединен со вторым (5) токовым выходом устройства, а сток второго (16) дополнительного полевого транзистора согласован со второй (6) шиной источника питания, второй (12) источник опорного тока выполнен на основе третьего (17) и четвертого (18) дополнительных полевых транзисторов, затворы которых подключены к объединенным истокам третьего (9) и четвертого (10) входных полевых транзисторов, а истоки связаны с объединенными истоками третьего (9) и четвертого (10) входных полевых транзисторов, причем сток третьего (17) дополнительного полевого транзистора соединен с первым (3) токовым выходом устройства, а сток четвертого (18) дополнительного полевого транзистора согласован с первой (4) шиной источника питания, причем в качестве упомянутых выше полевых транзисторов применены полевые транзисторы с управляющим p-n переходом.

2. Низкотемпературный входной каскад операционного усилителя с повышенным ослаблением входного синфазного сигнала на комплементарных полевых транзисторах с управляющим p-n переходом по п. 1, отличающийся тем, что истоки первого (15) и второго (16) дополнительных полевых транзисторов связаны с объединенными истоками первого (7) и второго (8) входных полевых транзисторов через первый (19) дополнительный резистор, а истоки третьего (17) и четвертого (18) дополнительных полевых транзисторов связаны с объединенными истоками третьего (9) и четвертого (10) входных полевых транзисторов через второй (20) дополнительный резистор.

3. Низкотемпературный входной каскад операционного усилителя с повышенным ослаблением входного синфазного сигнала на комплементарных полевых транзисторах с управляющим p-n переходом по п. 1, отличающийся тем, что исток первого (15) дополнительного полевого транзистора связан с объединенными истоками первого (7) и второго (8) входных полевых транзисторов через третий (37) дополнительный резистор, исток второго (16) дополнительного полевого транзистора связан с объединенными истоками первого (7) и второго (8) входных полевых транзисторов через четвертый (38) дополнительный резистор, исток третьего (17) дополнительного полевого транзистора связан с объединенными истоками третьего (9) и четвертого (10) входных полевых транзисторов через пятый (39) дополнительный резистор, а исток четвертого (18) дополнительного полевого транзистора связан с объединенными истоками третьего (9) и четвертого (10) входных полевых транзисторов через шестой (40) дополнительный резистор.

| Пломбировальные щипцы | 1923 |

|

SU2006A1 |

| ТОКОВОЕ ЗЕРКАЛО | 2008 |

|

RU2365969C1 |

| US 7463013 B2, 09.12.2008 | |||

| Повторитель тока | 1987 |

|

SU1529410A1 |

Авторы

Даты

2020-05-25—Публикация

2020-01-31—Подача