Предлагаемое изобретение относится к области радиотехники и аналоговой микроэлектроники и может быть использовано в различных аналоговых и аналого-цифровых интерфейсах (активных RC-фильтрах, нормирующих преобразователях и т.п.), работающих в условиях низких температур и воздействия радиации.

В современной микроэлектронике достаточно популярны архитектуры двухкаскадных КМОП ОУ с симметричной активной нагрузкой (АН) в цепи противофазных токовых выходов входного дифференциального каскада. Причем в качестве входных КМОП транзисторов могут использоваться КМОП с n– и p–каналами [1-8].

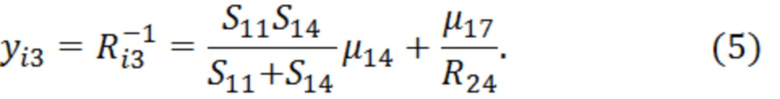

Ближайшим прототипом заявляемого устройства является операционный усилитель, представленный в патентной заявке фирмы Texas Instruments Incorporated US 2011/0012678, fig.4c,2011г.Он содержитпервый 1 и второй 2 входы устройства, основной токовый выход устройства 3, первый 4 и второй 5 входные полевые транзисторы, истоки которых объединены и подключены к первой 6 шине источника питания через источник опорного тока 7, затвор первого 4 входного полевого транзистора соединен с первым 1 входом устройства, затвор второго 5 входного полевого транзистора соединен со вторым 2 входом устройства, сток первого 4 входного полевого транзистора связан с первым 8 токовым выходом входного дифференциального каскада 9 на первом 4 и втором 5 входныхполевых транзисторах, а также соединен со стоком первого 10 выходного полевого транзистора и затвором второго 11 выходного полевого транзистора, сток второго 5 входного полевого транзистора связан со вторым 12 токовым выходом входного дифференциального каскада 9 на первом 4 и втором 5 входныхполевых транзисторах, а также соединен со стоком третьего 13 выходного полевого транзистора и затвором четвертого 14 выходного полевого транзистора, первый 15 и второй 16 вспомогательные резисторы, пятый 17 выходной полевой транзистор, причем сток четвертого 14 выходного полевого транзистора связан с основным токовым выходом устройства 3, а затворы первого 10 и третьего 13 выходных полевых транзисторов соединены друг с другом, причем истоки первого 10 и третьего 13 выходных полевых транзисторов согласованы со второй 18 шиной источника питания.

Существенный недостаток ОУ-прототипа фиг. 1, который относится к числу классических КМОП-схем современной микроэлектроники, состоит в том, что при его практической реализации по JFET (не КМОП) технологиям (Si, SiC, GaN, GaAs и др.) он оказывается неработоспособным. Это связано с тем, что полярность напряжения исток-затвор JFET противоположна полярности его напряжения исток-сток. Для построения JFET ОУ необходимы специальные схемотехнические решения, которые сегодня отсутствуют.

Основная задача предполагаемого изобретения состоит в создании для различных JFET техпроцессов (Si, SiC, GaN, GaAs и др.)работоспособного (при воздействии радиации и криогенных температур)операционного усилителя, который обеспечивает малые значения систематической составляющей напряжения смещения нуля (Uсм), а также повышенный коэффициент усиления (Ку) по напряжению.

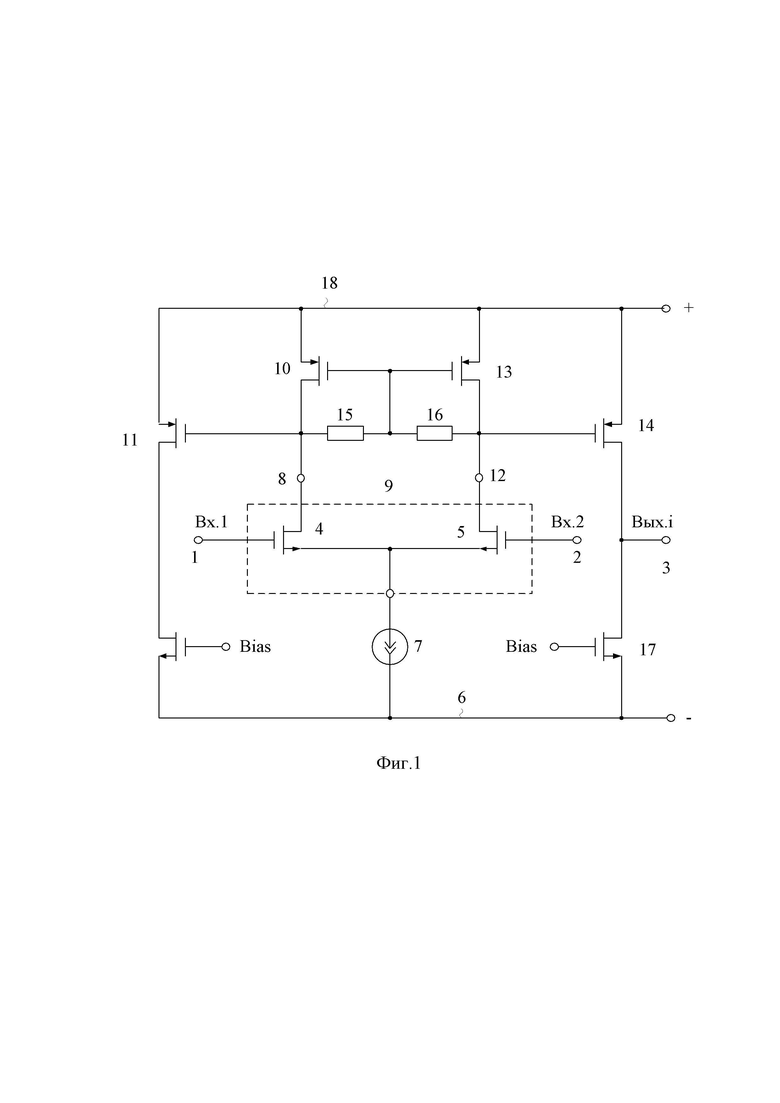

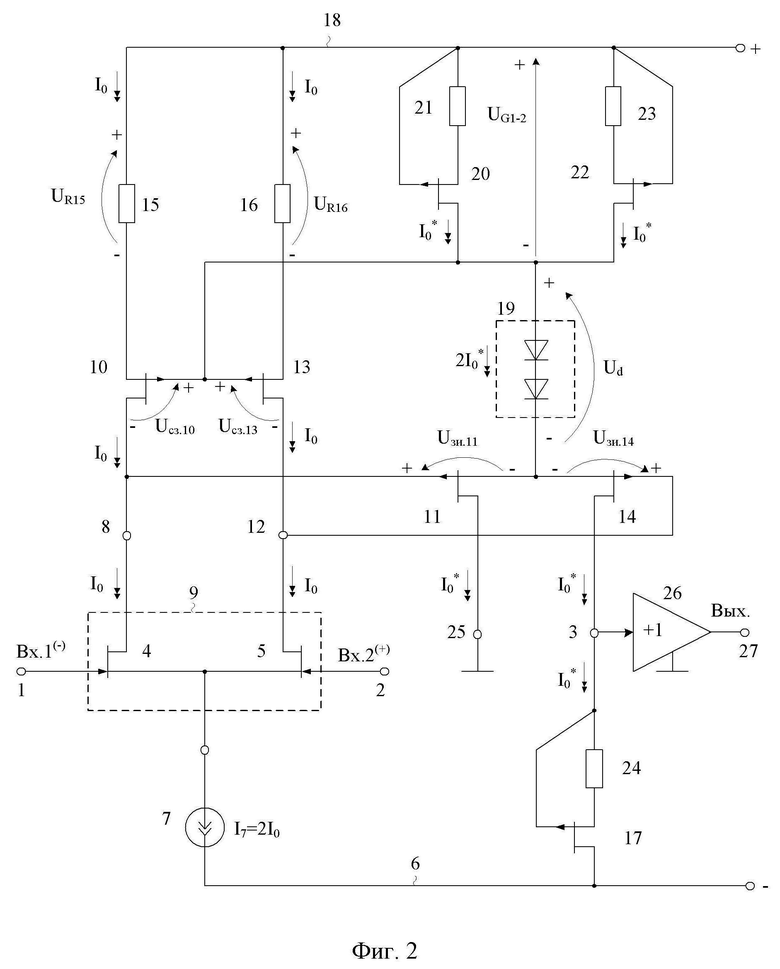

Поставленная задача достигается тем, что в ОУ фиг. 1, содержащемпервый 1 и второй 2 входы устройства, основной токовый выход устройства 3, первый 4 и второй 5 входные полевые транзисторы, истоки которых объединены и подключены к первой 6 шине источника питания через источник опорного тока 7, затвор первого 4 входного полевого транзистора соединен с первым 1 входом устройства, затвор второго 5 входного полевого транзистора соединен со вторым 2 входом устройства, сток первого 4 входного полевого транзистора связан с первым 8 токовым выходом входного дифференциального каскада 9 на первом 4 и втором 5 входныхполевых транзисторах, а также соединен со стоком первого 10 выходного полевого транзистора и затвором второго 11 выходного полевого транзистора, сток второго 5 входного полевого транзистора связан со вторым 12 токовым выходом входного дифференциального каскада 9 на первом 4 и втором 5 входныхполевых транзисторах, а также соединен со стоком третьего 13 выходного полевого транзистора и затвором четвертого 14 выходного полевого транзистора, первый 15 и второй 16 вспомогательные резисторы, пятый 17 выходной полевой транзистор, причем сток четвертого 14 выходного полевого транзистора связан с основным токовым выходом устройства 3, а затворы первого 10 и третьего 13 выходных полевых транзисторов соединены друг с другом, причем истоки первого 10 и третьего 13 выходных полевых транзисторов согласованы со второй 18 шиной источника питания, предусмотрены новые элементы и связи – в качестве всех полевых транзисторов используются полевые транзисторы с управляющим p-n переходом,исток первого 10 выходного полевого транзистора связан со второй 18 шиной источника питания через первый 15 вспомогательный резистор, исток третьего 13 выходного полевого транзистора связан со второй 18 шиной источника питания через второй 16 вспомогательный резистор, между объединенными затворами первого 10 и третьего 13 выходных полевых транзисторов и объединенными истоками второго 11 и четвертого 14 выходных полевых транзисторов включена цепь согласования потенциалов 19, к объединенным затворам первого 10 и третьего 13 выходных полевых транзисторовподключен сток первого 20 дополнительного полевого транзистора, затвор которого соединен со второй 18 шиной источника питания, а исток подключен ко второй 18 шине источника питания через первый 21 дополнительный резистор, к объединенным затворам первого 10 и третьего 13 выходных полевых транзисторовподключен сток второго 22 дополнительного полевого транзистора, затвор которого соединен со второй 18 шиной источника питания, а исток подключен ко второй 18 шине источника питания через второй 23 дополнительный резистор, сток пятого 17 выходного полевого транзистора соединен с первой 6 шиной источника питания, его затвор связан с основным токовым выходом устройства 3, а исток связан с основным токовым выходом устройства 3 через третий 24 дополнительный резистор, причем сток второго 11 выходного полевого транзистора согласован с общей шиной источника питания 25.

На чертеже фиг. 1 представлена схема ОУ-прототипа в структуре заявки на патент US фирмы Texas Instruments Incorporated 2011/0012678, 2011г., а на чертеже фиг. 2 –схема заявляемого JFet ОУ в соответствии с п. 1 и п.2 формулы изобретения.

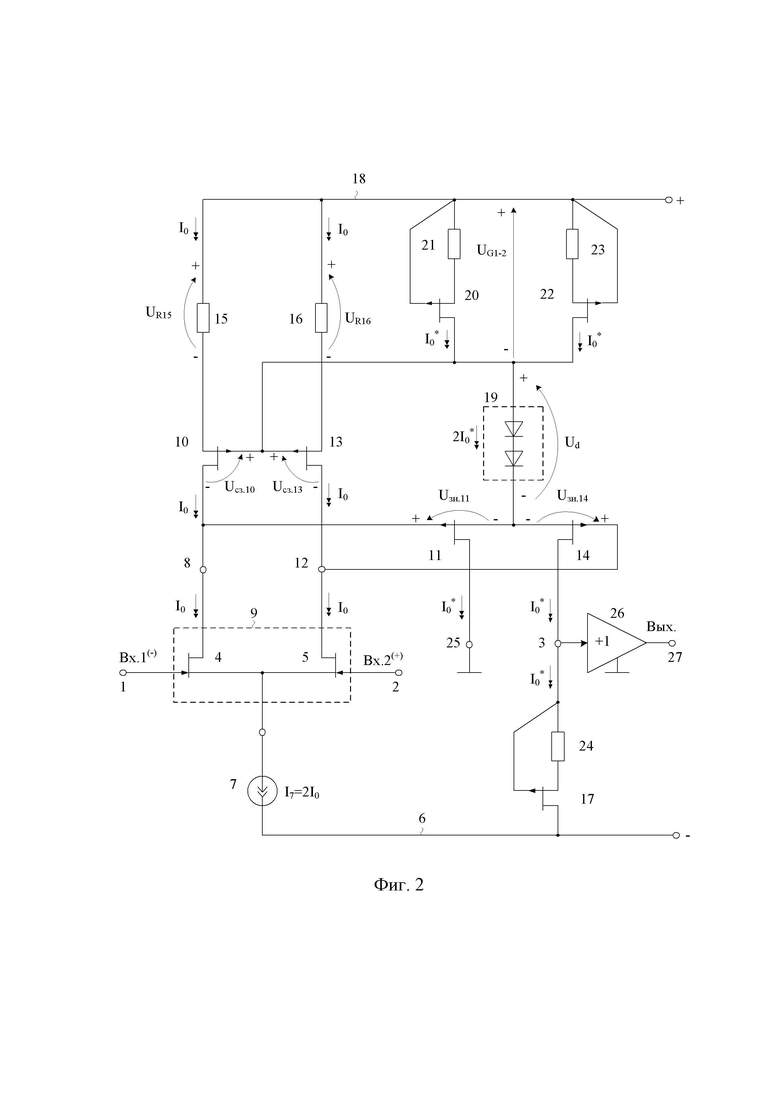

На чертеже фиг. 3 показан статический режим заявляемой схемы ОУ фиг. 2 при t=-197°C в среде LTSpice на моделях JFET транзисторов АО «Интеграл» (г. Минск).

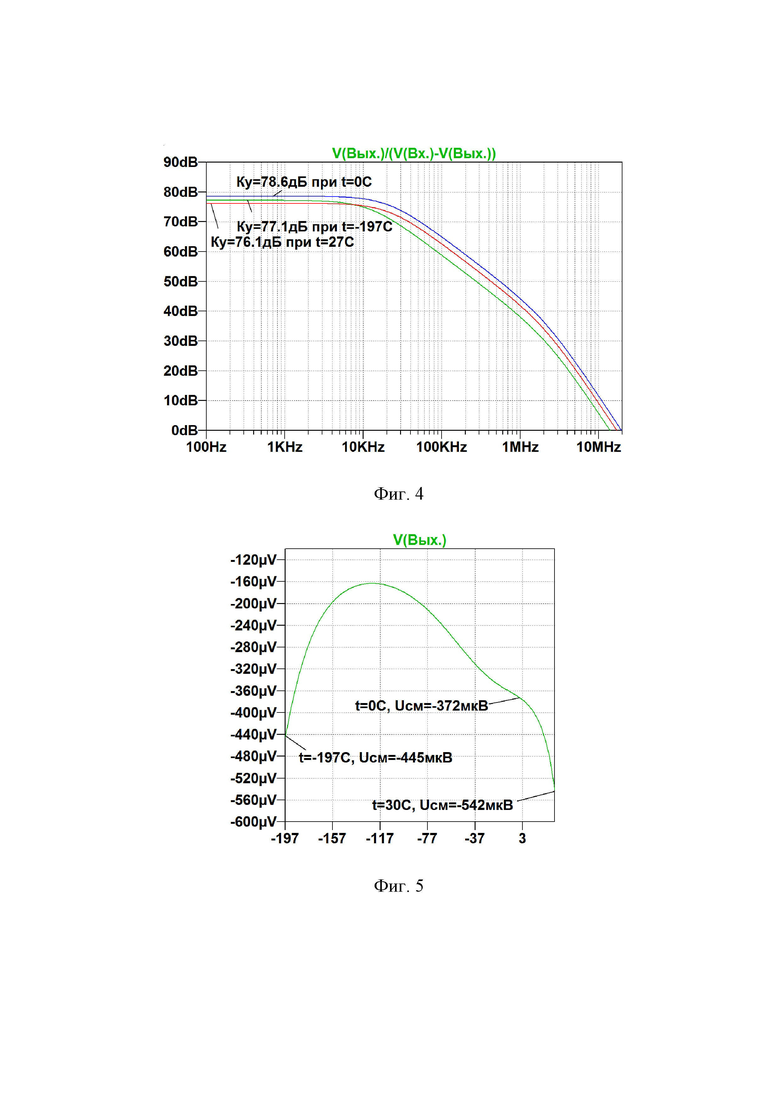

На чертеже фиг. 4 приведены амплитудно-частотные характеристикикоэффициента усиления по напряжению ОУ фиг. 3 при разных температурных режимах (t=0°C, t=27°C, t=-197°C).

На чертеже фиг. 5 представлена зависимость систематической составляющей напряжения смещения нуля (Uсм) ОУ фиг. 3 в диапазоне температур от -197°С до 30°С.

На чертеже фиг. 6 показано влияние на систематическую составляющую напряжения смещения нуля (Uсм) схемы ОУ фиг. 3 потока нейтронов (Fn=1÷1015 н/см2).

Дифференциальный операционный усилитель на полевых транзисторах с управляющим p-n переходом фиг. 2 содержит первый 1 и второй 2 входы устройства, основной токовый выход устройства 3, первый 4 и второй 5 входные полевые транзисторы, истоки которых объединены и подключены к первой 6 шине источника питания через источник опорного тока 7, затвор первого 4 входного полевого транзистора соединен с первым 1 входом устройства, затвор второго 5 входного полевого транзистора соединен со вторым 2 входом устройства, сток первого 4 входного полевого транзистора связан с первым 8 токовым выходом входного дифференциального каскада 9 на первом 4 и втором 5 входныхполевых транзисторах, а также соединен со стоком первого 10 выходного полевого транзистора и затвором второго 11 выходного полевого транзистора, сток второго 5 входного полевого транзистора связан со вторым 12 токовым выходом входного дифференциального каскада 9 на первом 4 и втором 5 входныхполевых транзисторах, а также соединен со стоком третьего 13 выходного полевого транзистора и затвором четвертого 14 выходного полевого транзистора, первый 15 и второй 16 вспомогательные резисторы, пятый 17 выходной полевой транзистор, причем сток четвертого 14 выходного полевого транзистора связан с основным токовым выходом устройства 3, а затворы первого 10 и третьего 13 выходных полевых транзисторов соединены друг с другом, причем истоки первого 10 и третьего 13 выходных полевых транзисторов согласованы со второй 18 шиной источника питания. Вкачестве всех полевых транзисторов используются полевые транзисторы с управляющим p-n переходом,исток первого 10 выходного полевого транзистора связан со второй 18 шиной источника питания через первый 15 вспомогательный резистор, исток третьего 13 выходного полевого транзистора связан со второй 18 шиной источника питания через второй 16 вспомогательный резистор, между объединенными затворами первого 10 и третьего 13 выходных полевых транзисторов и объединенными истоками второго 11 и четвертого 14 выходных полевых транзисторов включена цепь согласования потенциалов 19, к объединенным затворам первого 10 и третьего 13 выходных полевых транзисторовподключен сток первого 20 дополнительного полевого транзистора, затвор которого соединен со второй 18 шиной источника питания, а исток подключен ко второй 18 шине источника питания через первый 21 дополнительный резистор, к объединенным затворам первого 10 и третьего 13 выходных полевыхтранзисторовподключен сток второго 22 дополнительного полевого транзистора, затвор которого соединен со второй 18 шиной источника питания, а исток подключен ко второй 18 шине источника питания через второй 23 дополнительный резистор, сток пятого 17 выходного полевого транзистора соединен с первой 6 шиной источника питания, его затвор связан с основным токовым выходом устройства 3, а исток связан с основным токовым выходом устройства 3 через третий 24 дополнительный резистор, причем сток второго 11 выходного полевого транзистора согласован с общей шиной источника питания 25.

Кроме того, на чертеже фиг. 2, в соответствии с п. 2 формулы изобретения,основной токовый выход устройства 3 подключен ко входу дополнительного буферного усилителя 26, выход которого 27 является дополнительным потенциальным выходом устройства.

Рассмотрим работу предлагаемого ОУ фиг. 2.

Операционный усилитель фиг. 2 содержит два основных каскада усиления. Первый из них выполнен на входном дифференциальном каскаде 9 с симметричной активной нагрузкой (АН) на первом 10 и третьем 13 выходных полевых транзисторах. Применение такой АН позволяет исключить из схемы ОУ типовые токовые зеркала, которые в базисе JFET элементов характеризуются крайне неудовлетворительными параметрами, существенно ухудшающими основные статические и динамические характеристики ОУ.

Статический режим по току входного дифференциального каскада 9 устанавливается источником опорного тока 7:I7=2I0, где I0 - заданное разработчиком значение статических токов первого 10 и третьего 13 выходных полевых транзисторов, а также токов первого 15 и второго 16 вспомогательных резисторов.

За счет отрицательной обратной связи по выходному синфазному напряжению входного дифференциального каскада 9, которая организуется через второй каскад усиления (второй 11 и четвертый 14 выходные полевые транзисторы), в схеме фиг. 2 выполняются равенства:

IR15=IR16=I0=0,5I7, (1)

Iс10=Iс13=I0=0,5I7, (2)

где Ici – ток стока i-го транзистора.

При этом напряжения сток-затвор первого 10 и третьего 13 выходных полевых транзисторов определяются формулой

Uзс.10=Uзс.13=Ud-Uзи.11(14), (3)

где Uзи.11(14) – напряжение затвор-исток второго 11 и четвертого 14 выходных полевых транзисторов при выбранном статическом токе I0*.

Таким образом, для обеспечения заданного значения Uзс.10=Uзс.13 необходимо соответствующим образом выбирать напряжение Udна цепи согласования потенциалов 19. В частном случае в качестве данного элемента 19 могут использоваться резисторы, стабилитроны или последовательно включенные p-n переходы.

Второй каскад усиления выполнен на втором 11, четвертом 14 выходных полевых транзисторах, первом 20, втором 22 дополнительных полевых транзисторах и пятом 17 выходном полевом транзисторе. Его заданный статический режим по току I0*устанавливается первым 20 и вторым 22 дополнительными полевыми транзисторами, а также первым 21 и вторым 23 дополнительными резисторами.

Динамической нагрузкой второго каскада усиления является источник опорного тока I0*, выполненной на пятом 17 полевом транзисторе и третьем 24 дополнительном резисторе по точно такой же схеме, что и источники опорного тока на первом 20 и втором 22 дополнительных полевых транзисторах. Такое схемотехническое решение позволяет минимизировать напряжение смещения нуля второго каскада усиления, которое приводится ко входу ОУ через коэффициент усиления первого каскада К01. При больших К01 в схеме ОУ фиг. 2 минимизируется общее напряжение смещения нуля, обусловленное Ucмвторого каскада. При этом коэффициент усиления по напряжению второго каскада

K02=Ri3S11-14, (4)

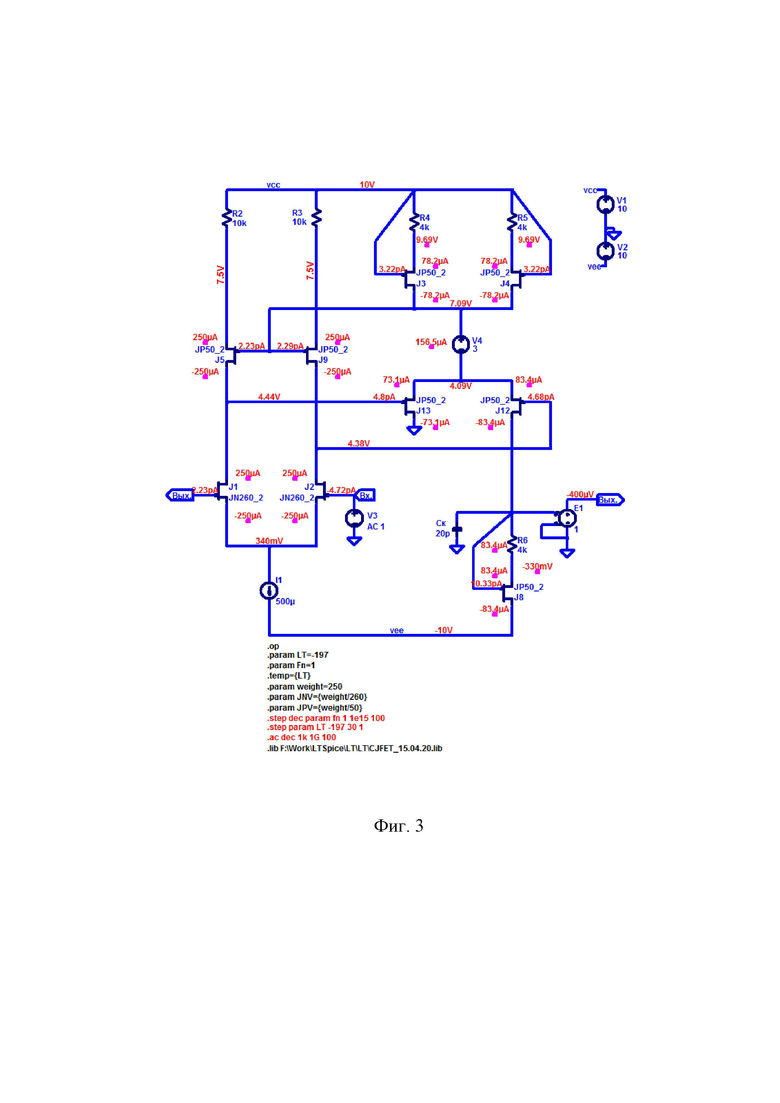

где Ri3 - эквивалентное сопротивление основного токового выхода устройства 3, S11-14 – эквивалентная крутизна дифференциального каскада на втором 11 и четвертом 14 выходных полевых транзисторах.Причем эквивалентная выходная проводимость в цепи основного токового выхода устройства 3

Таким образом, второй каскад усиления обеспечивает повышенные значения К02 (4) без применения токовых зеркал.

Для получения низкоомного потенциального выхода 27 в схеме фиг. 2 предусмотрен дополнительный буферный усилитель 26.

Результаты компьютерного моделирования (фиг. 3 – фиг. 6) показывают, что заявляемый ОУ работоспособен в диапазоне криогенных температур и воздействии потока нейтронов.

Таким образом, предлагаемый ОУ имеет ряд вышеназванных преимуществ в сравнении с ОУ-прототипом, позволяет получить малые значения систематической составляющей напряжения смещения нуля Uсм, приемлемые для многих применений значения Ку. За счет использования JFet обеспечивается высокая радиационная стойкость ОУ и его работоспособность в диапазоне криогенных температур. Предлагаемый ОУ может быть рекомендован для практического использования в космическом приборостроении и физике высоких энергий.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент US 2011/0012678, 2011 г.

2. Патент US 8169263, 2012г., fig. 5

3. Патент US 7741911, 2010г., fig. 3

4. Патент US 6388522, 2002г., fig. 1

5. Патент RU 2651221, 2018 г., fig. 2

6. Патент US 7154335, 2006г., fig. 3

7. Патент US 6426676, 2002г., fig. 3

8. Патент US 2003/0075163, 2003 г., fig. 6

Изобретение относится к области радиотехники. Технический результат: создание для различных JFET техпроцессов работоспособного операционного усилителя, который обеспечивает малые значения систематической составляющей напряжения смещения нуля (Uсм), а также повышенный коэффициент усиления (Ку) по напряжению. Для этого предложен дифференциальный операционный усилитель на полевых транзисторах с управляющим p-n переходом, в отличие от прототипа в качестве всех полевых транзисторов используются полевые транзисторы с управляющим p-n переходом, при этом исток первого (10) выходного полевого транзистора связан со второй (18) шиной источника питания через первый (15) вспомогательный резистор, исток третьего (13) выходного полевого транзистора связан со второй (18) шиной источника питания через второй (16) вспомогательный резистор, между объединенными затворами первого (10) и третьего (13) выходных полевых транзисторов и объединенными истоками второго (11) и четвертого (14) выходных полевых транзисторов включена цепь согласования потенциалов (19), а также предусмотрены другие новые элементы и связи. 1 з.п. ф-лы, 6 ил.

1. Дифференциальный операционный усилитель на полевых транзисторах с управляющим p-n переходом, содержащий первый (1) и второй (2) входы устройства, основной токовый выход устройства (3), первый (4) и второй (5) входные полевые транзисторы, истоки которых объединены и подключены к первой (6) шине источника питания через источник опорного тока (7), затвор первого (4) входного полевого транзистора соединен с первым (1) входом устройства, затвор второго (5) входного полевого транзистора соединен со вторым (2) входом устройства, сток первого (4) входного полевого транзистора связан с первым (8) токовым выходом входного дифференциального каскада (9) на первом (4) и втором (5) входных полевых транзисторах, а также соединен со стоком первого (10) выходного полевого транзистора и затвором второго (11) выходного полевого транзистора, сток второго (5) входного полевого транзистора связан со вторым (12) токовым выходом входного дифференциального каскада (9) на первом (4) и втором (5) входных полевых транзисторах, а также соединен со стоком третьего (13) выходного полевого транзистора и затвором четвертого (14) выходного полевого транзистора, первый (15) и второй (16) вспомогательные резисторы, пятый (17) выходной полевой транзистор, причем сток четвертого (14) выходного полевого транзистора связан с основным токовым выходом устройства (3), а затворы первого (10) и третьего (13) выходных полевых транзисторов соединены друг с другом, причем истоки первого (10) и третьего (13) выходных полевых транзисторов согласованы со второй (18) шиной источника питания, отличающийся тем, что в качестве всех полевых транзисторов используются полевые транзисторы с управляющим p-n переходом, исток первого (10) выходного полевого транзистора связан со второй (18) шиной источника питания через первый (15) вспомогательный резистор, исток третьего (13) выходного полевого транзистора связан со второй (18) шиной источника питания через второй (16) вспомогательный резистор, между объединенными затворами первого (10) и третьего (13) выходных полевых транзисторов и объединенными истоками второго (11) и четвертого (14) выходных полевых транзисторов включена цепь согласования потенциалов (19), к объединенным затворам первого (10) и третьего (13) выходных полевых транзисторов подключен сток первого (20) дополнительного полевого транзистора, затвор которого соединен со второй (18) шиной источника питания, а исток подключен ко второй (18) шине источника питания через первый (21) дополнительный резистор, к объединенным затворам первого (10) и третьего (13) выходных полевых транзисторов подключен сток второго (22) дополнительного полевого транзистора, затвор которого соединен со второй (18) шиной источника питания, а исток подключен ко второй (18) шине источника питания через второй (23) дополнительный резистор, сток пятого (17) выходного полевого транзистора соединен с первой (6) шиной источника питания, его затвор связан с основным токовым выходом устройства (3), а исток связан с основным токовым выходом устройства (3) через третий (24) дополнительный резистор, причем сток второго (11) выходного полевого транзистора согласован с общей шиной источника питания (25).

2. Дифференциальный операционный усилитель на полевых транзисторах с управляющим p-n переходом по п.1, отличающийся тем, что основной токовый выход устройства (3) подключен ко входу дополнительного буферного усилителя (26), выход которого (27) является дополнительным потенциальным выходом устройства.

| Способ приготовления лака | 1924 |

|

SU2011A1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С РАСШИРЕННЫМ ДИАПАЗОНОМ АКТИВНОЙ РАБОТЫ | 2007 |

|

RU2331971C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 1991 |

|

RU2060578C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С НЕСИММЕТРИЧНЫМ ВХОДОМ | 2002 |

|

RU2309529C2 |

Авторы

Даты

2020-12-28—Публикация

2020-08-31—Подача