Область техники, к которой относится изобретение

Настоящее раскрытие относится к технологиям источников питания, в частности, к схемам питания для вычислительных плат, блокам источника питания и вычислительным платам.

Уровень техники

Майнинг (добыча) криптовалюты представляет собой процесс, в котором транзакции для различных форм криптовалюты верифицируются и добавляются в цифровой регистрационный журнал блокчейна. В последние годы майнинг криптовалюты рос в геометрической прогрессии при более широком использовании криптовалюты. Каждый раз, когда выполняется транзакция криптовалюты, майнер криптовалюты отвечает за обеспечение подлинности информации и обновление блокчейна с помощью транзакции. Сам процесс майнинга включает в себя конкуренцию с другими майнерами криптовалюты для решения сложных математических задач с криптографическими хеш-функциями, которые связаны с блоком, содержащим данные транзакции. Первый майнер криптовалюты, взломавший код, получает вознаграждение за возможность авторизации транзакции, а взамен предоставленной услуги майнер криптовалюты зарабатывает небольшие суммы криптовалюты. Чтобы быть конкурентоспособным с другими майнерами криптовалюты, майнеру криптовалюты необходим компьютер для решения криптографических хеш-функций.

Для эффективного майнинга криптовалюты использовались специализированные аппаратные средства, такие как майнинговые машины криптовалюты. Эти майнинговые машины потребляют значительное количество электрической энергии и требуют стабилизированных источников питания, когда они работают непрерывно. Центральным компонентом майнинговой машины является вычислительная плата, также известная как хэш-плата, которая содержит схемы и чипы интегральной схемы и выполняет вычисления хэш-функций. В настоящее время горные машины в основном используют источники питания с преобразованием постоянного тока в постоянный. Однако эти источники энергии часто недоступны из-за высокого спроса и низкого предложения. Поэтому вместо источников питания постоянного тока иногда используются альтернативные чипы интегральной схемы источника питания. Когда вместо источников питания постоянного тока используется чип источника питания с альтернативным источником питания, периферийная схема питания часто несовместима с источником питания. Для каждой замененной интегральной микросхемы источника питания периферийная схема может нуждаться в доработке, что приводит к чрезмерному количеству различных версий вычислительной платы, сложностям в обслуживании и увеличению стоимости.

Сущность изобретения

Некоторые варианты осуществления настоящего раскрытия предусматривают вспомогательную схему и блок источника питания для вычислительных плат машин для майнинга криптовалюты.

Один аспект настоящего раскрытия предусматривает схему силового каскада вычислительной платы. Схема силового каскада вычислительной платы включает в себя входную цепь и выходную цепь. Входная цепь и выходная цепь электрически соединены друг с другом. Схема силового каскада вычислительной платы дополнительно включает в себя множество выводов корпуса. Множество выводов корпуса подключено, соответственно, к входной цепи, выходной цепи и блоку источника питания.

В некоторых вариантах осуществления выводы корпуса содержат набор из восьми выводов корпуса, и по меньшей мере один вывод из набора из восьми выводов корпуса подключен к входной цепи, и по меньшей мере один вывод из набора из восьми выводов корпуса соединен с выходной цепью.

В некоторых вариантах осуществления набор из восьми выводов корпуса включает в себя: первый вывод для подачи сигнала управления переключателем верхней лампы; второй вывод для подачи сигнала управления переключателем нижней лампы; третий вывод для подключения узла переключения силового каскада и схемы возбуждения верхней лампы; четвертый вывод для подачи напряжения и обеспечения рабочего напряжения смещения для чипа интегральной схемы на вычислительной плате; пятый вывод для подачи опорного нулевого потенциала; шестой вывод управления преобразователем постоянного тока в постоянный; седьмой вывод для подачи выходного напряжения постоянного тока; и восьмой вывод для управления с обратной связью и регулировки выходного напряжения.

В некоторых вариантах осуществления входная схема содержит по меньшей мере два полупроводниковых полевых транзистора, соединенных последовательно, и полупроводниковые полевые транзисторы электрически соединены с выводами корпуса.

В некоторых вариантах осуществления выходная цепь представляет собой схему стабилизации напряжения для подачи тока и стабилизированного напряжения на один или более чипов интегральной схемы, которые должны быть запитаны на вычислительной плате.

В некоторых вариантах осуществления блок источника питания содержит интегральную схему источника питания, вспомогательную схему и один или несколько выводов управления. Интегральная схема источника питания электрически соединена со вспомогательной схемой; вспомогательная схема выводит сигнал по меньшей мере на один из выводов управления; и один или несколько выводов управления выполнены с возможностью подключения к одному или нескольким выводам корпуса схемы силового каскада вычислительной платы.

В некоторых вариантах осуществления каждый из выводов управления выполнен с возможностью электрического соединения с соответствующим выводом корпуса в пределах множества выводов корпуса схемы силового каскада вычислительной платы.

Вариант осуществления настоящего раскрытия предусматривает вычислительную плату. Вычислительная плата включает в себя схему силового каскада, причем схема силового каскада содержит входную цепь и выходную цепь, которые электрически соединены друг с другом, и множество выводов корпуса, которые подключены, соответственно, к входной цепи и выходной цепи; блок источника питания, содержащий интегральную схему источника питания, вспомогательную схему и один или несколько выводов управления; и интегральную микросхему, которая должна быть запитана. Блок источника питания выполнен в корпусе для соединения с множеством выводов корпуса схемы силового каскада; и интегральная микросхема запитана от схемы силового каскада.

В некоторых вариантах осуществления по меньшей мере одна интегральная микросхема, которая должна быть запитана, соединена последовательно.

В некоторых вариантах осуществления выводы корпуса схемы силового каскада содержат набор из восьми выводов корпуса, и по меньшей мере один вывод из набора из восьми выводов корпуса подключен к входной цепи, и по меньшей мере один вывод из набора из восьми выводов корпуса подключен к выходной цепи.

В некоторых вариантах осуществления набор из восьми выводов корпуса схемы силового каскада включает в себя первый вывод для подачи сигнала управления переключателем верхней лампы; второй вывод для подачи сигнала управления переключателем нижней лампы; третий вывод для подключения узла переключения силового каскада и схемы возбуждения верхней лампы; четвертый вывод для подачи напряжения и обеспечения рабочего напряжения смещения для чипа интегральной схемы на вычислительной плате; пятый вывод для подачи опорного нулевого потенциала; шестой вывод управления преобразователем постоянного тока в постоянный; седьмой вывод для подачи выходного напряжения постоянного тока; и восьмой вывод для управления с обратной связью и регулировки выходного напряжения.

В некоторых вариантах осуществления входная цепь включает в себя по меньшей мере два полупроводниковых полевых транзистора, соединенных последовательно, и транзисторы полупроводникового поля электрически соединены с выводами корпуса.

В некоторых вариантах осуществления, схема силового каскада выходной цепи схемы силового каскада представляет собой схему стабилизации напряжения для подачи тока и стабилизированного напряжения на один или более чипов интегральной схемы, которые должны быть запитаны на вычислительной плате.

В некоторых вариантах осуществления вспомогательной схема блока источника питания подает сигнал на один из выводов управления корпуса источника питания; и один или несколько выводов управления соединены с одним или несколькими выводами корпуса схемы силового каскада вычислительной платы.

В некоторых вариантах осуществления каждый из выводов управления блока источника питания соединен с соответствующим выводом корпуса в множестве выводов корпуса схемы силового каскада.

Другой аспект настоящего раскрытия предусматривает вычислительную плату. Вычислительная плата включает в себя схему силового каскада, причем схема силового каскада содержит входную цепь и выходную цепь, которые электрически соединены друг с другом, и множество выводов корпуса, которые подключены, соответственно, к входной цепи и выходной цепи; блок источника питания; и интегральную микросхему, которая должна быть запитана. Блок источника питания выполнен в корпусе для соединения с множеством выводов корпуса схемы силового каскада; и интегральная микросхема запитана от схемы силового каскада.

В некоторых вариантах осуществления блок источника питания включает в себя первую интегральную схему источника питания и первую вспомогательную схему, соответствующую интегральной схеме источника питания.

В некоторых вариантах осуществления блок источника питания включает в себя вторую интегральную схему источника питания и вторую вспомогательную схему, соответствующую интегральной схеме источника питания, причем вторая интегральная схема источника питания и вторая вспомогательная схема заменяет первую интегральную схему источника питания и первую вспомогательную схему.

В другом варианте осуществления силовой схемы согласно настоящему раскрытию выводы корпуса включают в себя набор из восьми выводов корпуса; где по меньшей мере один из восьми выводов корпуса подключен к входной цепи, и по меньшей мере один из восьми выводов корпуса подключен к выходной цепи.

Некоторые варианты осуществления настоящего раскрытия предусматривают схему силового каскада вычислительной платы, блок источника питания и вычислительную плату, а также входную цепь и выходную цепь, размещенные на вычислительной плате. Входная цепь и выходная цепь электрически соединены друг с другом и подключены к выводам корпуса. При размещении чипа интегральной схемы источника питания и ее схему силового каскада в блоке источника питания и при подключении выводов общего управления к выводам блока, различные источники питания с преобразованием постоянного тока в постоянный можно выполнить совместимыми с входной цепью и выходной цепью. При размещении компонентов высокой мощности на вычислительной плате, блок источника питания можно выполнить небольшим, с меньшими трудностями при проектировании и с улучшенной способностью рассеивания тепла, при этом может поддерживаться стабильность источника питания.

Техническое решение согласно настоящему изобретению будет подробно описано ниже с помощью прилагаемых чертежей и вариантов осуществления изобретения.

Краткое описание чертежей

Настоящее раскрытие может стать более понятным из следующих чертежей, на которых:

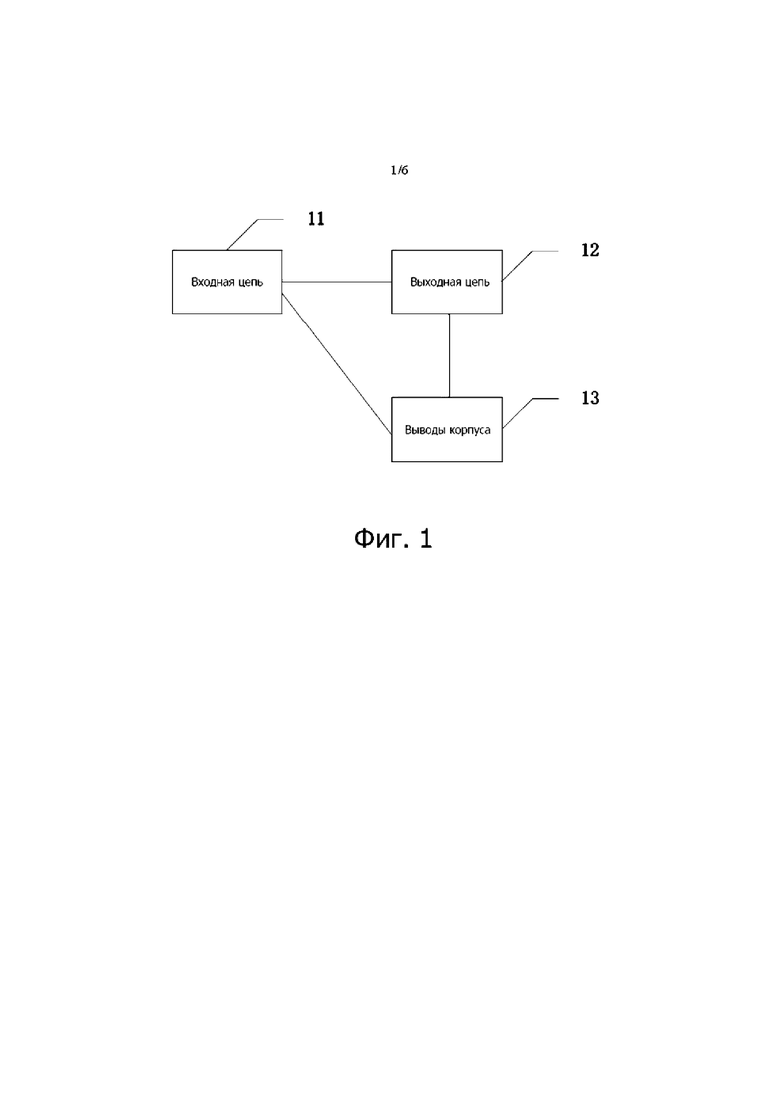

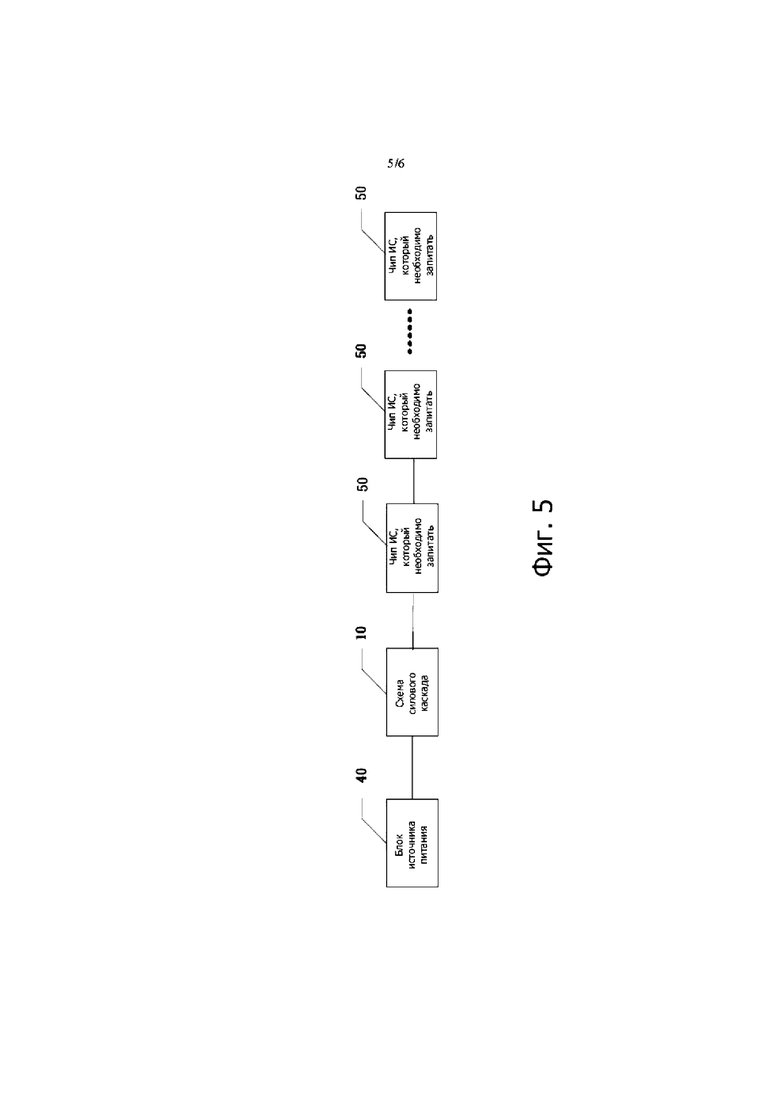

фиг. 1 – блок-схема варианта осуществления схемы силового каскада вычислительной платы согласно настоящему раскрытию;

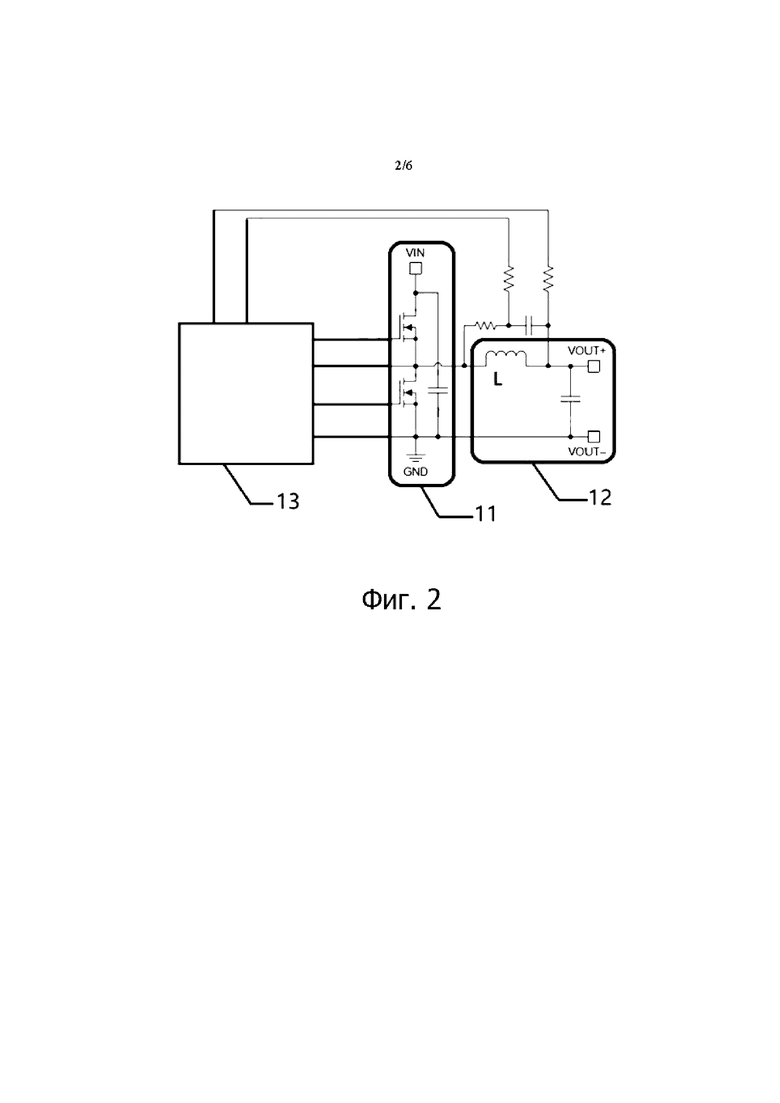

фиг. 2 – принципиальная схема конкретного примера вышеприведенного варианта осуществления схемы силового каскада вычислительной платы согласно настоящему раскрытию;

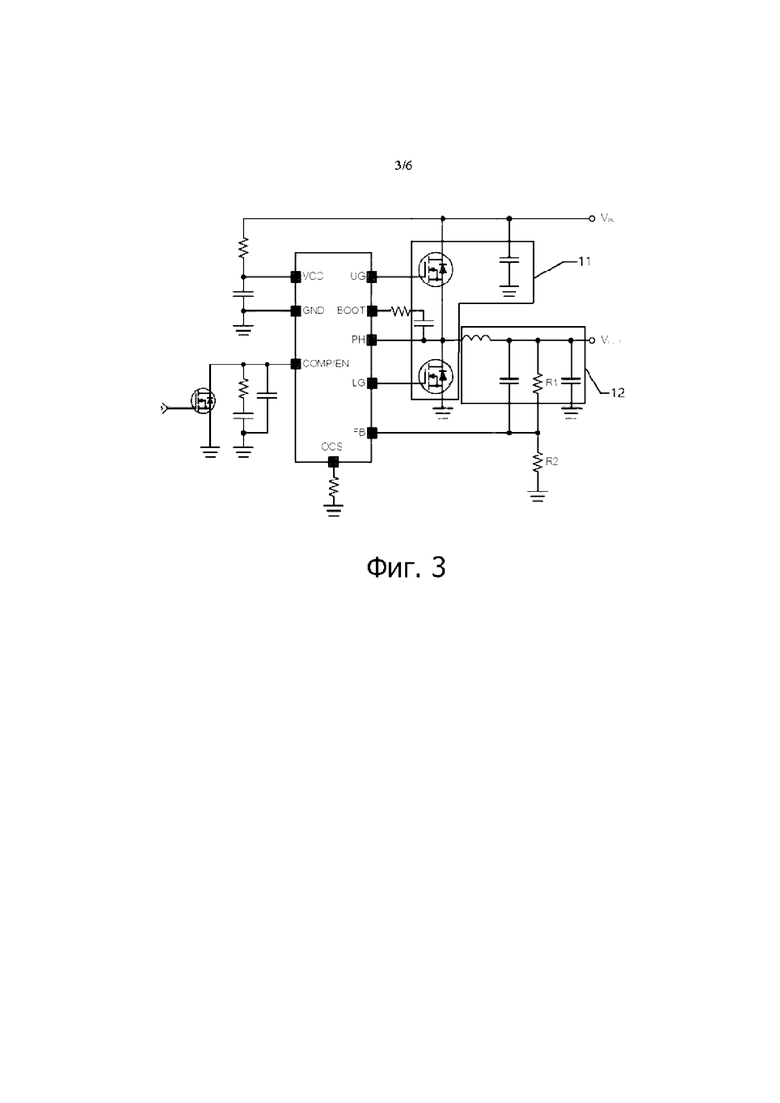

фиг. 3 – принципиальная схема другого конкретного примера вышеупомянутого варианта осуществления схемы силового каскада вычислительной платы настоящего раскрытия;

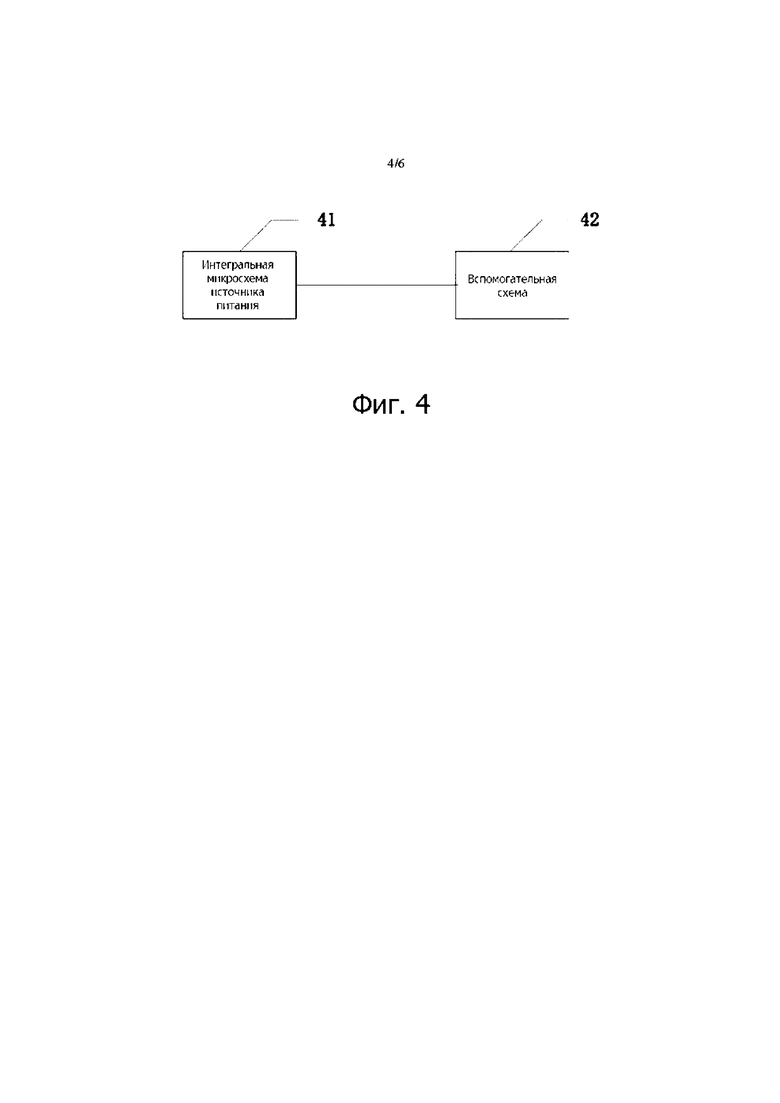

фиг. 4 – блок-схема варианта осуществления блока источника питания согласно настоящему раскрытию;

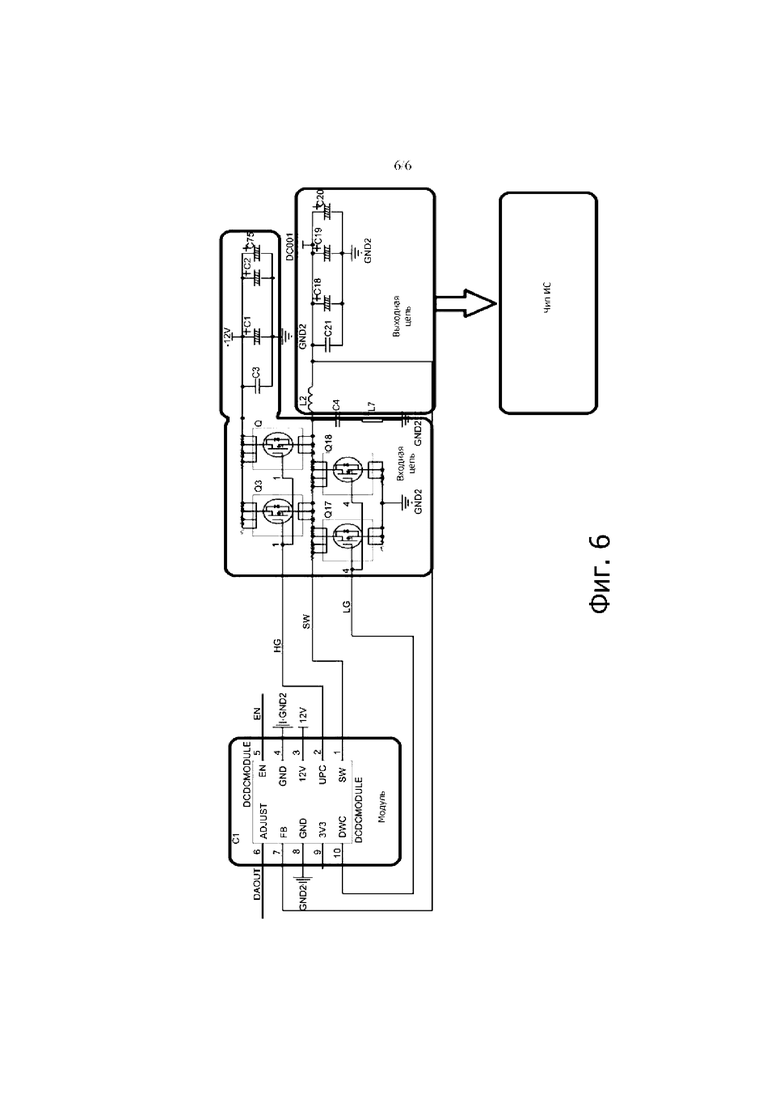

фиг. 5 – блок-схема варианта осуществления вычислительной платы согласно настоящему раскрытию; и

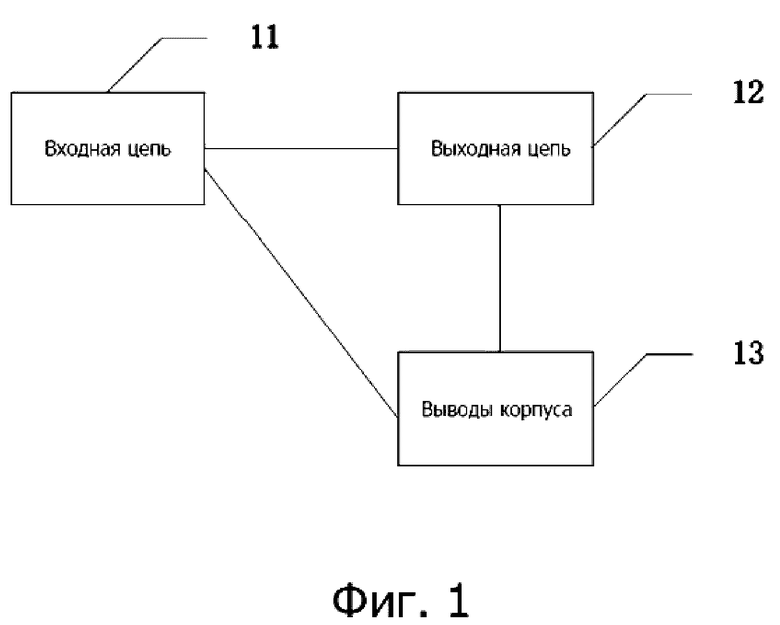

фиг. 6 – принципиальная схема другого конкретного примера вышеупомянутого варианта осуществления вычислительной платы согласно настоящему раскрытию.

Подробное описание изобретения

Технические решения настоящего раскрытия будут описаны со ссылкой на чертежи. Следует понимать, что описанные варианты осуществления являются некоторыми, а не всеми вариантами осуществления настоящего раскрытия. Другие варианты осуществления, представленные специалистами в данной области техники на основе описанных вариантов осуществления без изобретательских усилий, должны находиться в пределах объема настоящего раскрытия.

Примерные варианты осуществления будут описаны со ссылкой на прилагаемые чертежи, на которых одинаковые ссылочные позиции относятся к одинаковым или аналогичным элементам, если не указано иное.

Если не указано иное, все технические и научные термины, используемые в данном документе, имеют такие же или аналогичные значения, которые обычно понимает специалист в данной области техники. Как описано в данном документе, термины, используемые в описании настоящего раскрытия, предназначены для описания примерных вариантов осуществления вместо ограничения настоящего раскрытия. Используемый в данном документе термин «и/или» включает любую подходящую комбинацию одного или нескольких перечисленных связанных элементов.

Следует также понимать, что для удобства описания размер различных частей показан не в масштабе.

На фиг. 1 показана блок-схема варианта осуществления схемы силового каскада вычислительной платы согласно варианту осуществления настоящего раскрытия. Как показано на фиг. 1, схема может включать в себя: входную цепь 11 и выходную цепь 12 на вычислительной плате. Входная цепь 11 и выходная цепь 12 электрически соединены друг с другом. Выводы 13 корпуса соединены с входной цепью 11 и выходной цепью 12, соответственно. Выводы 13 корпуса используются для монтажа корпусированного блока источника питания.

При размещении интегральной микросхемы источника питания и ее вспомогательной схемы в блоке источника питания и подключении выводов общего управления к выводам корпуса можно выполнить различные источники питания с преобразованием постоянного тока в постоянный совместимыми с входной цепью 11 и выходной цепью 12. При размещении компонентов высокой мощности на вычислительной плате блок источника питания может быть выполнен небольшим с уменьшенной сложностью проектирования и повышенной способностью рассеивания тепла, при этом может поддерживаться стабильность работы источника питания.

В одном примере вышеупомянутого варианта осуществления схемы силового каскада вычислительной платы выводы 13 корпуса включают в себя набор из восьми выводов корпуса. Блок источника питания подключен к входной цепи 11 по меньшей мере с помощью одного из восьми выводов корпуса. Он также подключен к выходной цепи 12 по меньшей мере с помощью одного из восьми выводов корпуса.

В данном варианте осуществления корпус может иметь восемь выводов корпуса. Блок источника питания может включать в себя по меньшей мере один вывод управления. Он может быть выполнен в корпусе на вычислительной плате путем подсоединения выводов управления к выводам корпуса. Чип интегральной схемы источника питания может быть смонтирован на вычислительной плате с использованием простого корпуса, и блок источника питания может быть легко заменен, поэтому блок источника питания вычислительной платы не ограничивается интегральной микросхемой источника питания конкретного типа.

В одном примере вышеупомянутого варианта осуществления схемы силового каскада вычислительной платы восемь выводов корпуса могут включать в себя: первый вывод для подачи сигнала управления переключателем верхней лампы; второй вывод для подачи сигнала управления переключателем нижней лампы; третий вывод для подключения узла переключения силового каскада и схемы возбуждения верхней лампы; четвертый вывод для подачи напряжения и обеспечения рабочего напряжения смещения для чипа интегральной схемы; пятый вывод для подачи опорного нулевого потенциала; шестой вывод управления включением преобразователя постоянного тока в постоянный; седьмой вывод для подачи выходного напряжения преобразователя постоянного тока в постоянный; и восьмой вывод для управления с обратной связью и регулировки выходного напряжения.

В данном варианте осуществление первый вывод представляет собой вывод HG, второй вывод – вывод LG, третий вывод – вывод SW, и четвертый вывод – вывод VIN, пятый вывод – вывод GND, шестой вывод – вывод EN, седьмой вывод – вывод DCOUT, и восьмой вывод – вывод DAOUT.

Согласно варианту осуществления схемы силового каскада вычислительной платы настоящего раскрытия, входная цепь 11 может включать в себя по меньшей мере два полупроводниковых полевых транзистора, соединенных последовательно. Два полупроводниковых полевых транзистора могут быть электрически соединены с выводами корпуса.

Вышеупомянутый вариант осуществления предоставляет только пример схемы ввода. В общем, до тех пор, пока входная цепь 11 может использоваться для подачи тока и пути разряда для индуктора, она может использоваться в схеме силового каскада вычислительной платы.

Согласно еще одному варианту осуществления схемы силового каскада вычислительной платы настоящего раскрытия выходная цепь 12 может быть схемой стабилизации напряжения для подачи тока и стабилизированного напряжения на чипы интегральной схемы, которые должны быть запитаны на вычислительной плате.

Вышеупомянутый вариант осуществления предусматривает выходную цепь, которая функционирует для подачи тока и стабилизированного напряжения на нагрузку. В частности, он обеспечивает подачу тока питания и стабилизированного напряжения для чипов интегральных схем, которые должны быть запитаны на вычислительной плате.

На фиг. 2 показана принципиальная схема конкретного примера приведенного выше варианта осуществления схемы силового каскада вычислительной платы согласно настоящему раскрытию. Как показано на фиг. 2, входная цепь 11 и выходная цепь 12 могут быть смонтированы на вычислительной плате. Входная цепь 11 и выходная цепь 12 могут быть электрически соединены друг с другом. Входная цепь 11 может включать в себя два полупроводниковых полевых транзистора, соединенных последовательно. Полупроводниковые полевые транзисторы могут быть электрически соединены с выводами 13 корпуса. Выводы 13 корпуса могут использоваться для установки корпусированного блока источника питания.

На фиг. 3 показана принципиальная схема другого конкретного примера вышеупомянутого варианта осуществления схемы силового каскада вычислительной платы настоящего раскрытия. Как показано на фиг. 3, входная цепь 11 и выходная цепь 12 на вычислительной плате могут быть электрически соединены друг с другом. Схема силового каскада также может включать в себя блок источника питания, подключенный к входной цепи 11 и выходной цепи 12, соответственно.

На фиг. 4 показана блок-схема варианта осуществления блока источника питания согласно настоящему раскрытию. Как показано на фиг. 4, устройство данного варианта осуществления может включать в себя чип 41 силовой интегральной схемы питания и вспомогательную схему 42, которые соединены друг с другом. Вспомогательная схема 42 может выводить сигналы по меньшей мере на один вывод управления, и она подключена к выводам корпуса схемы силового каскада вычислительной платы через каждый из выводов управления.

Вышеупомянутый вариант осуществления настоящего раскрытия предусматривает блок источника питания. При размещении любого чипа 41 интегральной схемы источника питания в блоке источника питания, блок источника питания может быть небольшим, что снижает сложность проектирования. В то же время, вариант осуществления может использовать различные чипы 41 интегральной схемы источника питания с использованием надлежащей соответствующей вспомогательной схемы 42, которая преодолевает трудности совместимости в системах подачи питания на вычислительные платы. Вспомогательная схема 42 может быть выполнена с учетом требований заказчика для размещения различных чипов 41 интегральной схемы источника питания. Для каждого чипа 41 интегральной схемы источника питания в технических условиях часто содержатся процедуры проектирования для разработки вспомогательной схемы 42, а также необходимая информация и порядок расчета значений компонентов вспомогательной схемы 42. Таким образом, различные чипы 41 интегральной схемы источника питания могут быть сделаны совместимыми для питания вычислительной платы.

В одном примере вышеупомянутого варианта осуществления блока источника питания настоящего раскрытия каждый вывод управления может иметь соответствующий вывод корпуса при наличии восьми выводов корпуса в схеме силового каскада вычислительной платы.

Так как блок источника питания должен быть смонтирован на вычислительной плате, выводы управления блока источника питания могут иметь соответствующие выводы корпуса в схеме силового каскада вычислительной платы для обеспечения правильного монтажа источника питания на вычислительной плате.

В одном примере вышеупомянутого варианта осуществления блока источника питания настоящего раскрытия блок источника питания может быть подключен к выводам корпуса схемы силового каскада вычислительной платы. Блок источника питания может быть подключен к выводам корпуса схемы силового каскада вычислительной платы путем соединения выводов управления с соответствующими выводами корпуса в схеме силового каскада вычислительной платы. При правильном подсоединении выводов управления к соответствующим выводам корпуса корпусированный блок источника питания может быть подключен к вычислительной плате для подачи питания на чипы интегральной схемы, которые должны быть запитаны на вычислительной плате.

На фиг. 5 показана блок-схема варианта осуществления вычислительной платы согласно настоящему раскрытию. Как показано на фиг. 5, вычислительная плата данного варианта осуществления может включать в себя схему 10 силового каскада вычислительной платы любого из вышеупомянутых вариантов осуществления настоящего раскрытия, блок 40 источника питания любого из вышеупомянутых вариантов осуществления настоящего раскрытия и по меньшей мере один чип 50 интегральной схемы, который должен быть запитан.

Блок 40 источника питания может быть выполнен в корпусе в пределах корпуса выводов схемы 10 силового каскада вычислительной платы и может подавать питание по меньшей мере на один чип 50 интегральной схемы в схеме 10 силового каскада вычислительной платы.

Вышеупомянутый вариант осуществления настоящего раскрытия предусматривает вычислительную плату. За счет модульного исполнения чипа интегральной схемы источника питания может быть достигнута совместимость множества чипов интегральной схемы источника питания. В то же время, сложности, связанные с использованием модульного корпуса, уменьшаются, и упрощается обслуживание вычислительной платы. Поместив компоненты высокой мощности в схему силового каскада вычислительной платы и установив радиатор на вычислительную плату, система может лучше рассеивать тепло, поддерживая стабильность функции источника питания и уменьшая сложность проектирования вычислительной платы. При замене чипа силовой интегральной схемы нет необходимости повторно проектировать вычислительную плату. В результате может быть достигнута большая гибкость при проектировании оборудования и может быть уменьшена стоимость замены.

В одном примере вышеупомянутого варианта осуществления вычислительной платы согласно настоящему раскрытию по меньшей мере одна из интегральных микросхем, которая должна быть запитана, может быть соединена последовательно.

На фиг. 6 показана принципиальная схема другого примера вышеупомянутого варианта осуществления вычислительной платы согласно настоящему раскрытию. Как показано на фиг. 6, «модуль» на фигуре является блоком источника питания. Входная цепь и выходная цепь образуют схему силового каскада вычислительной платы. «Чип ИС» на чертеже обозначает чипы интегральной схемы, которые должны быть запитаны от схемы силового каскада.

Различные варианты осуществления в настоящем раскрытии описаны поэтапно. Каждый вариант осуществления фокусируется на некоторых различных аспектах из других вариантов осуществления, и одни и те же или аналогичные аспекты между различными вариантами осуществления могут быть связаны друг с другом. Воплощенная система в основном соответствует варианту осуществления способа, и соответствующие компоненты могут быть отнесены к частичному описанию варианта осуществления способа.

Описание настоящего раскрытия было представлено в целях иллюстрации и описания. Специалистам в данной области техники будут очевидны многие модификации и вариации. Вариант осуществления был выбран и описан для того, чтобы наилучшим образом объяснить принципы и варианты осуществления раскрытия. Специалистам в данной области техники будет также понятно, что признаки, описанные в соответствующих вариантах осуществления и/или формуле изобретения настоящего раскрытия, могут быть объединены различными способами, даже если такие комбинации явно не описаны в настоящем раскрытии. В частности, не отклоняясь от сущности и идеи настоящего раскрытия, признаки, описанные в соответствующих вариантах осуществления и/или формуле изобретения, могут быть объединены различными способами. Все эти комбинации входят в объем настоящего раскрытия.

Хотя настоящее раскрытие было показано и описано со ссылкой на различные варианты его осуществления, специалистам в данной области техники должно быть понятно, что в него могут быть внесены различные модификации в форме и деталях без отклонения от сущности и объема настоящего раскрытия, как это определено прилагаемой формулой изобретения и ее эквивалентами. Таким образом, объем настоящего раскрытия не должен быть ограничен вышеописанными вариантами осуществления, а должен определяться не только прилагаемой формулой изобретения, но также ее эквивалентами.

Следует отметить, что описание вышеупомянутых вариантов осуществления электронного устройства может быть аналогичным описанию вышеупомянутых вариантов осуществления способа, и варианты осуществления устройства имеют те же полезные эффекты, что и варианты осуществления способа. Следовательно, подробности не могут быть описаны здесь снова. Технические детали, не раскрытые в вариантах осуществления электронного устройства настоящего раскрытия, специалисты в данной области техники могут понять согласно вариантам осуществления способа настоящего раскрытия.

В некоторых вариантах осуществления, представленных в настоящем раскрытии, следует понимать, что описанные устройство и способ могут быть реализованы другими способами. Варианты осуществления устройства, описанные выше, являются просто примерными. Все функциональные модули или блоки в вариантах осуществления настоящего раскрытия могут быть интегрированы в один блок обработки, или каждый блок может использоваться как один блок. Два или более блоков могут быть объединены в один. Вышеупомянутый интегральный блок может быть реализован в виде аппаратных средств или в виде аппаратных средств в сочетании с функциональными блоками программного обеспечения.

Другие варианты осуществления раскрытия будут очевидны для специалистов в данной области техники из рассмотрения спецификации и практики раскрытия, представленной в данном документе. Предполагается, что описание и примеры будут рассматриваться только как примерные, с истинным объемом и сущностью раскрытия, указанными в формуле изобретения.

| название | год | авторы | номер документа |

|---|---|---|---|

| СИСТЕМНАЯ ВЫЧИСЛИТЕЛЬНАЯ ПЛАТА | 2024 |

|

RU2828793C1 |

| Управляющая система для квантовых вычислительных устройств | 2023 |

|

RU2814936C1 |

| Плата системная вычислительного модуля | 2024 |

|

RU2822305C1 |

| Плата системная вычислительного модуля | 2024 |

|

RU2840229C1 |

| МОДУЛЬНЫЙ ИСТОЧНИК ТОКА | 2023 |

|

RU2812960C1 |

| СВЕТОДИОДНАЯ ПЛАТА И ЭКРАН С ЕЕ ИСПОЛЬЗОВАНИЕМ | 2022 |

|

RU2837508C2 |

| СПОСОБ ДЛЯ УПРАВЛЕНИЯ ПИТАНИЕМ СИСТЕМЫ И ЕГО ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2018 |

|

RU2690750C1 |

| ПЛАТА РАСШИРЕНИЯ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ | 1990 |

|

RU2009539C1 |

| ТЕСТИРОВАНИЕ JTAG ТРАКТОВ ПЕРЕДАЧИ ДИСКРЕТНЫХ ДАННЫХ ПРИ ИСПОЛЬЗОВАНИИ СМЕННЫХ ПЕЧАТНЫХ ПЛАТ С УСТАНОВЛЕННЫМИ НА НИХ ЛОГИЧЕСКИМИ СХЕМАМИ JTAG | 1996 |

|

RU2182711C2 |

| СПЕЦИАЛИЗИРОВАННАЯ ИНТЕГРАЛЬНАЯ СХЕМА ДЛЯ УСТРОЙСТВА ДОСТАВКИ АЭРОЗОЛЯ | 2016 |

|

RU2711465C2 |

Изобретение относится к электротехнике. Технический результат заключается в уменьшении габаритов, улучшении рассеивания тепла. Схема силового каскада включает в себя входную цепь и выходную цепь. Входная и выходная цепи электрически соединены друг с другом. Схема силового каскада также включает в себя множество выводов корпуса. Множество выводов корпуса подключено, соответственно, к входной цепи, выходной цепи и блоку источника питания. 2 н. и 13 з.п. ф-лы, 6 ил.

1. Схема силового каскада вычислительной платы, содержащая:

входную цепь (11) и выходную цепь (12), причем входная (11) цепь и выходная цепь (12) электрически соединены друг с другом; и

множество выводов (13) корпуса, причем множество выводов корпуса подключено, соответственно, к входной цепи (11), выходной цепи (12) и блоку (40) источника питания.

2. Схема силового каскада вычислительной платы по п. 1, в которой выводы (13) корпуса содержат набор из восьми выводов корпуса, и по меньшей мере один вывод из набора из восьми выводов корпуса подключен к входной цепи (11), и по меньшей мере один вывод из набора из восьми выводов корпуса подключен к выходной цепи (12).

3. Схема силового каскада вычислительной платы по п. 2, в которой набор из восьми выводов (13) корпуса содержит: первый вывод для подачи сигнала управления переключателем верхней лампы; второй вывод для подачи сигнала управления переключателем нижней лампы; третий вывод для подключения узла переключения силового каскада и схемы возбуждения верхней лампы; четвертый вывод для подачи напряжения и обеспечения рабочего напряжения смещения для чипа интегральной схемы на вычислительной плате; пятый вывод для подачи опорного нулевого потенциала; шестой вывод управления включением преобразователя постоянного тока; седьмой вывод для подачи выходного напряжения постоянного тока; и восьмой вывод для управления с обратной связью и регулировки выходного напряжения.

4. Схема силового каскада вычислительной платы по п. 1, в которой входная цепь (11) содержит по меньшей мере два полупроводниковых полевых транзистора, соединенных последовательно, и полупроводниковые полевые транзисторы электрически соединены с выводами корпуса и/или;

выходная цепь (12) является схемой стабилизации напряжения для подачи тока и стабилизированного напряжения на один или несколько чипов интегральной схемы, которые должны быть запитаны на вычислительной плате.

5. Схема силового каскада вычислительной платы по п. 1, в которой блок (40) источника питания содержит интегральную схему (41) источника питания, вспомогательную схему (42) и один или несколько выводов управления;

где интегральная схема (41) источника питания электрически соединена со вспомогательной схемой (42); вспомогательная схема (42) выводит сигнал по меньшей мере на один из выводов управления; и один или несколько выводов управления выполнены с возможностью подключения к одному или нескольким выводам (13) корпуса схемы силового каскада вычислительной платы.

6. Схема силового каскада вычислительной платы по п. 1, в которой каждый из выводов (13) управления выполнен с возможностью электрического соединения с соответствующим выводом корпуса в пределах множества выводов (13) корпуса схемы силового каскада вычислительной платы.

7. Вычислительная плата, содержащая:

схему (10) силового каскада, причем схема (10) силового каскада содержит входную цепь (11) и выходную цепь (12), которые электрически соединены друг с другом, и множество выводов (13) корпуса, которые подключены, соответственно, к входной цепи (11) и выходной цепи (12);

блок (40) источника питания; и

интегральную микросхему, которая должна быть запитана;

где блок (40) источника питания выполнен в корпусе для соединения с множеством выводов (13) корпуса схемы (10) силового каскада; и интегральная микросхема запитана от схемы (10) силового каскада.

8. Вычислительная плата по п. 7, в которой блок (40) источника питания содержит интегральную схему (41) источника питания, вспомогательную схему (42) и один или несколько выводов управления.

9. Вычислительная плата по п. 8, в которой блок (40) источника питания содержит первую интегральную схему (41) источника питания и соответствующую первую вспомогательную схему (42).

10. Вычислительная плата по п. 9, в которой блок (40) источника питания содержит вторую интегральную схему (41) источника питания и соответствующую вторую вспомогательную схему (42), причем вторая интегральная схема (41) источника питания и вторая вспомогательная схема (42) заменяют первую интегральную схему (41) источника питания и первую вспомогательную схему (42).

11. Вычислительная плата по любому из пп. 7-10, в которой при наличии двух или более чипов, которые должны быть запитаны, по меньшей мере два из чипов, которые должны быть запитаны, соединены последовательно.

12. Вычислительная плата по любому из пп. 7-10, в которой выводы (13) корпуса схемы (10) силового каскада содержат набор из восьми выводов корпуса, и по меньшей мере один вывод из набора из восьми выводов корпуса подключен к входной цепи (11), и по меньшей мере один вывод из набора из восьми выводов корпуса подключен к выходной цепи (12).

13. Вычислительная плата по п. 12, в которой набор из восьми выводов (13) корпуса схемы (10) силового каскада содержит: первый вывод для вывода сигнала управления переключателем верхней лампы; второй вывод для подачи сигнала управления переключателем нижней лампы; третий вывод для подключения узла переключения силового каскада и схемы возбуждения верхней лампы; четвертый вывод для подачи напряжения и обеспечения рабочего напряжения смещения для чипа интегральной схемы на вычислительной плате; пятый вывод для подачи опорного нулевого потенциала; шестой вывод управления включением преобразователя постоянного тока; седьмой вывод для подачи выходного напряжения постоянного тока; и восьмой вывод для управления с обратной связью и регулировки выходного напряжения.

14. Вычислительная плата по любому из пп. 7-10, в которой входная цепь (11) содержит по меньшей мере два полупроводниковых полевых транзистора, соединенных последовательно, и полупроводниковые полевые транзисторы электрически соединены с выводами корпуса и/или;

схема силового каскада выходной цепи схемы (10) силового каскада является схемой стабилизации напряжения для подачи тока и стабилизированного напряжения на один или несколько чипов интегральной схемы, которые должны быть запитаны на вычислительной плате и/или;

вспомогательная схема (42) блока (40) источника питания подает сигнал на один из выводов управления корпуса источника питания; и один или несколько выводов управления соединены с одним или несколькими выводами (13) корпуса схемы силового каскада вычислительной платы.

15. Вычислительная плата по п. 14, в которой каждый из выводов управления блока (40) источника питания подключен к соответствующему выводу корпуса в пределах множества выводов (13) корпуса схемы (10) силового каскада.

| CN 104283406 A, 14.01.2015 | |||

| CN 106407008 A, 15.02.2017 | |||

| CN 203691210 U, 02.07.2014 | |||

| ДРАЙВЕРНОЕ УСТРОЙСТВО ПОСТОЯННОГО ТОКА, ИМЕЮЩЕЕ ВХОДНОЙ И ВЫХОДНОЙ ФИЛЬТРЫ, ДЛЯ ПРИВЕДЕНИЯ В ДЕЙСТВИЕ НАГРУЗКИ, В ЧАСТНОСТИ, БЛОКА СВЕТОДИОДОВ | 2012 |

|

RU2588580C2 |

Авторы

Даты

2020-08-11—Публикация

2018-09-21—Подача