ОБЛАСТЬ ТЕХНИКИ

Настоящее изобретение относится к устройству отображения и к схеме возбуждения для устройства отображения, а более конкретно - к схеме возбуждения линий сигнала сканирования, которая включает в себя множество сдвиговых регистров для возбуждения линий сигнала сканирования, которые размещены в блоке отображения устройства отображения.

ПРЕДШЕСТВУЮЩИЙ УРОВЕНЬ ТЕХНИКИ

В последние годы прогрессирующим образом развиваются монолитные структуры формирователя сигналов управления затвором (схем возбуждения линий сигнала сканирования), которые возбуждают линии затворной шины (линии сигнала сканирования) в жидкокристаллическом устройстве отображения. Традиционно формирователь сигналов управления затвором часто устанавливают на периферийной части подложки, которая составляет жидкокристаллическую панель, в качестве кристалла ИС (интегральной микросхемы). Однако в последние годы постепенно все чаще формируют формирователь сигналов управления затвором непосредственно на подложке. Такой формирователь сигналов управления затвором называют, например, «монолитным формирователем сигналов управления затвором». В жидкокристаллическом устройстве отображения, которое включает в себя монолитный формирователь сигналов управления затвором, в качестве элемента возбуждения традиционно используют тонкопленочный транзистор, в котором используют аморфный кремний (a-Si) (в дальнейшем называют «a-SiTFT»). Однако в последние годы в качестве эксперимента используют тонкопленочный транзистор, в котором используют микрокристаллический кремний (μc-Si) (в дальнейшем называют «μc-SiTFT»). Подвижность микрокристаллического кремния больше подвижности аморфного кремния, и дополнительно, μc-SiTFT формируют с помощью процесса, аналогичного процессу для a-SiTFT. Поэтому, основываясь на применении μc-SiTFT для элемента возбуждения, ожидается обеспечение уменьшения стоимости путем уменьшения площади рамки изображения и уменьшения количества кристаллов ИС формирователя, усовершенствование сборки готовых изделий, увеличение размера устройства отображения и тому подобное.

Блок отображения жидкокристаллического устройства отображения с активной матрицей включает в себя множество линий истоковой шины (линий видеосигнала), множество линий затворной шины и множество участков формирования пикселя, которые обеспечивают на соответствующих пересечениях множества линий истоковой шины и множества линий затворной шины. Участки формирования пикселя составляют массив пикселей с помощью размещения в форме матрицы. Каждый участок формирования пикселя включает в себя тонкопленочный транзистор, который является переключающим элементом, соединяющим вывод затвора с линией затворной шины, проходящей через соответствующее пересечение, и соединяющим вывод истока с линией истоковой шины, проходящей через данное пересечение, и включает в себя конденсатор пикселя, предназначенный для хранения значения напряжения пикселя. Дополнительно, жидкокристаллическое устройство отображения с активной матрицей снабжают формирователем сигналов управления затвором и формирователем сигналов управления истоком (схемой возбуждения линий видеосигнала) для возбуждения линии истоковой шины.

Видеосигнал, который указывает значение напряжения пикселя, передают с помощью линий истоковой шины, но по каждой из линий истоковой шины нельзя одновременно передавать видеосигнал, который указывает значения напряжения пикселей множества строк. Поэтому запись (заряд) видеосигналов в конденсатор пикселя в участках формирования пикселя, которые размещены в форме матрицы, выполняют последовательно строка за строкой. Следовательно, формирователь сигналов управления затвором формируют с помощью сдвигового регистра, который включает в себя множество каскадов, так что множество линий затворной шины последовательно выбирают в течение каждого предопределенного периода. Каждый каскад сдвигового регистра является схемой с двумя устойчивыми состояниями, которая находится в одном из двух состояний (в первом состоянии и во втором состоянии) в каждый момент времени и которая выводит сигнал, указывающий это состояние (в дальнейшем называют «сигнал состояния») в качестве сигнала сканирования. Активные сигналы сканирования последовательно выводят из множества схем с двумя устойчивыми состояниями в сдвиговом регистре, таким образом запись видеосигналов в конденсаторы пикселей выполняют последовательно строка за строкой, как описано выше.

Известна следующая относящаяся к настоящему изобретению информация о предшествующем уровне техники. Публикация выложенной японской патентной заявки № 2005-94335 раскрывает конфигурацию для устранения изменения пороговой характеристики транзистора, относящуюся к сдвиговому регистру, который обеспечивают в электронном устройстве, таком как устройство считывания изображения. Публикация выложенной японской патентной заявки № 2003-16794 раскрывает конфигурацию для предотвращения неправильной работы транзистора из-за паразитной емкости транзистора, относящуюся к сдвиговому регистру, который обеспечивают в электронном устройстве. Публикация выложенной японской патентной заявки № 2006-106394 раскрывает конфигурацию для работы двух формирователей сигналов управления затвором при использовании многофазных синхроимпульсов, относящуюся к жидкокристаллическому устройству отображения. Публикация выложенной японской патентной заявки № 2006-107692 раскрывает конфигурацию для предотвращения неправильной работы из-за изменения порогового напряжения транзистора, относящуюся к сдвиговому регистру, который обеспечивают на панели отображения. Публикация выложенной японской патентной заявки № 2006-127630 раскрывает конфигурацию для работы сдвигового регистра при использовании множества синхроимпульсов, относящуюся к сдвиговому регистру, который используют в жидкокристаллическом устройстве отображения. Публикация выложенной японской патентной заявки № 2001-52494 раскрывает конфигурацию для предотвращения уменьшения уровня выходного сигнала и изменения пороговой характеристики напряжения транзистора, относящуюся к сдвиговому регистру, который обеспечивают в электронном устройстве.

ДОКУМЕНТЫ ПРЕДШЕСТВУЮЩЕГО УРОВНЯ ТЕХНИКИ

ПАТЕНТНЫЕ ДОКУМЕНТЫ

[Патентный документ 1] Публикация выложенной японской патентной заявки № 2005-94335

[Патентный документ 2] Публикация выложенной японской патентной заявки № 2003-16794

[Патентный документ 3] Публикация выложенной японской патентной заявки № 2006-106394

[Патентный документ 4] Публикация выложенной японской патентной заявки № 2006-107692

[Патентный документ 5] Публикация выложенной японской патентной заявки № 2006-127630

[Патентный документ 6] Публикация выложенной японской патентной заявки № 2001-52494

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

ПРОБЛЕМЫ, КОТОРЫЕ БУДУТ РЕШЕНЫ С ПОМОЩЬЮ ИЗОБРЕТЕНИЯ

Между прочим, в последние годы жидкокристаллического устройства отображения, которые включают в себя монолитный формирователь сигналов управления затвором, развиваются в сторону большого размера и более высокой разрешающей способности панели. Когда размер панели становится большим, нагрузочная емкость линии затворной шины соответственно увеличивается. В результате время, требуемое для снижения уровня сигнала сканирования (сигнала состояния), становится продолжительным. Следовательно, существует вероятность, что сигнал сканирования в определенной строке не снизится до низкого уровня (уровня, при котором тонкопленочный транзистор в участке формирования пикселя перейдет в состояние «выключено») до тех пор, когда начнется период заряда конденсатора пикселя следующей строки после завершения периода заряда конденсатора пикселя этой строки. В результате произойдет неверное отображение из-за смешивания цветов между цветом, который будут отображать в определенной строке, и цветом, который будут отображать в следующей строке. Дополнительно, время заряда одной линии становится коротким в соответствии с более высокой разрешающей способностью панели и поэтому происходит неверное отображение, относящееся к смешиванию цветов, которое описано выше. Возникновение неверного отображения, относящегося к смешиванию цветов, описано, основываясь на конфигурации схемы с двумя устойчивыми состояниями, которую включает в себя сдвиговый регистр, и на временной диаграмме сигналов ввода-вывода схемы с двумя устойчивыми состояниями. Последующее описание основано на предположении, что все тонкопленочные транзисторы, которые обеспечивают в схеме с двумя устойчивыми состояниями, являются транзисторами с каналом n-типа.

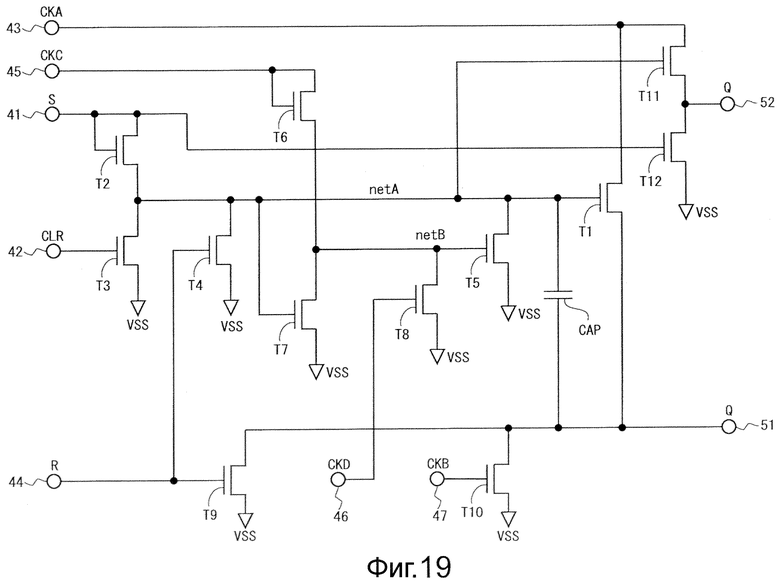

Фиг. 19 - принципиальная электрическая схема, на которой показан пример конфигурации схемы с двумя устойчивыми состояниями, которую включает в себя сдвиговый регистр формирователя сигналов управления затвором. Как показано на фиг. 19, схема с двумя устойчивыми состояниями включает в себя 12 тонкопленочных транзисторов T1-T12 и конденсатор CAP. Дополнительно, у схемы с двумя устойчивыми состояниями есть семь входных выводов 41-47 и два выходных вывода 51, 52 для вывода сигналов Q состояния в дополнение к входному выводу для напряжения VSS низкого уровня источника питания. Сигнал Q состояния, который выводят с выходного вывода 51, обеспечивают на линию затворной шины, соответствующую этой схеме с двумя устойчивыми состояниями, в качестве сигнала GOUT сканирования. Сигнал Q состояния, который выводят с выходного вывода 52, обеспечивают к схеме с двумя устойчивыми состояниями каскада, отличающегося от каскада этой схемы с двумя устойчивыми состояниями, в качестве сигнала Z для управления работой схемы с двумя устойчивыми состояниями другого каскада (в дальнейшем называют «управляющий сигнал другого каскада»).

Вывод затвора тонкопленочного транзистора T1, вывод истока тонкопленочного транзистора T2, вывод стока тонкопленочного транзистора T3, вывод стока тонкопленочного транзистора T4, вывод стока тонкопленочного транзистора T5, вывод затвора тонкопленочного транзистора T7 и вывод затвора тонкопленочного транзистора T11 соединяют друг с другом. Область (соединения), в которой эти выводы соединяют друг с другом, для удобства называют «netA». Вывод затвора тонкопленочного транзистора T5, вывод истока тонкопленочного транзистора T6, вывод стока тонкопленочного транзистора T7 и вывод стока тонкопленочного транзистора T8 соединяют друг с другом. Область (соединения), в которой эти выводы соединяют друг с другом, для удобства называют «netB».

Описанный формирователь сигналов управления затвором, как предполагают, включает в себя два сдвиговых регистра. Сигнал GOUT сканирования, который выводят из схемы с двумя устойчивыми состояниями в одном сдвиговом регистре, обеспечивают на линии затворной шины нечетных строк, а сигнал GOUT сканирования, который выводят из схемы с двумя устойчивыми состояниями в другом сдвиговом регистре, обеспечивают на линии затворной шины четных строк. То есть можно полагать, что «эти два сдвиговых регистра реализуют один сдвиговый регистр, который последовательно выбирает каждую из множества линий затворной шины в блоке отображения». Поэтому в последующем описании конфигурацию, в которой объединяют множество (два в данном примере) сдвиговых регистров, которые обеспечивают для последовательного выбора каждой из множества линий затворной шины, называют «весь сдвиговый регистр».

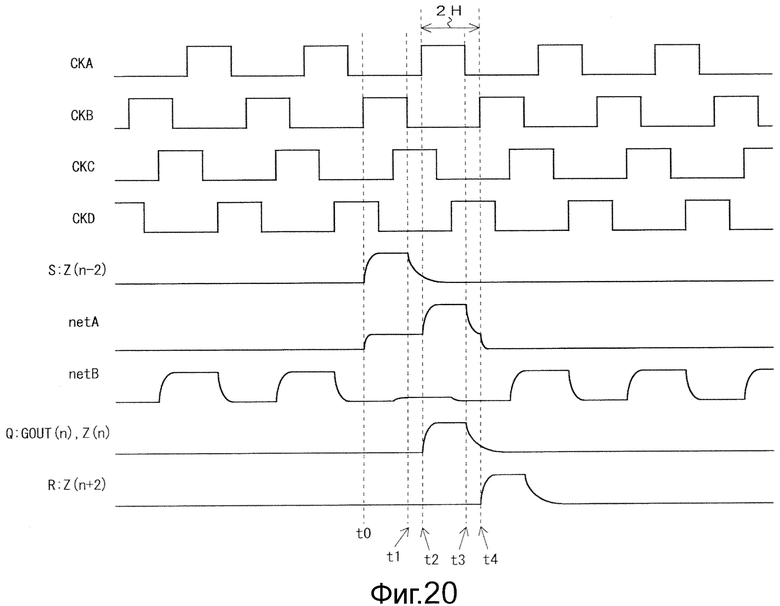

В вышеупомянутой конфигурации n-й каскад схемы с двумя устойчивыми состояниями всего сдвигового регистра работает следующим образом (см. фиг. 20). Первый синхроимпульс CKA, второй синхроимпульс CKB, третий синхроимпульс CKC и четвертый синхроимпульс CKD обеспечивают к входным выводам 43, 47, 45 и 46, соответственно. Управляющий сигнал Z(n-2) другого каскада, который выводят из схемы с двумя устойчивыми состояниями (n-2)-го каскада, обеспечивают к входному выводу 41 в качестве сигнала S установки. Управляющий сигнал Z(n+2) другого каскада, который выводят из схемы с двумя устойчивыми состояниями (n+2)-го каскада, обеспечивают к входному выводу 44 в качестве сигнала R сброса. Период с момента времени t1 до момента времени t2 и период с момента времени t3 до момента времени t4 не обеспечивают в общем случае или устанавливают как очень короткие периоды. На фиг. 20 период с момента времени t1 до момента времени t2 и период с момента времени t3 до момента времени t4 показаны как более продолжительные периоды, чем подлинные периоды. Для удобства момент времени t1 и момент времени t2 описаны отдельно, и момент времени t3 и момент времени t4 описаны отдельно. Это так же применяют к фиг. 3, фиг. 11 и фиг. 18 и к их описаниям.

Достигая момента времени t0, уровень сигнала S установки меняется с низкого уровня на высокий уровень. Соответственно, тонкопленочный транзистор T2 переходит в состояние «включено», конденсатор CAP заряжается, и уровень потенциала netA меняется с низкого уровня на высокий уровень. В результате тонкопленочные транзисторы T1, T11 переходят в состояние «включено». Достигая момента времени t1, уровень сигнала S установки меняется с высокого уровня на низкий уровень. Соответственно, тонкопленочный транзистор T2 переходит в состояние «выключено». В это время потенциал netA поддерживают с помощью конденсатора CAP, и поэтому его поддерживают на высоком уровне.

Достигая момента времени t2, уровень первого синхроимпульса CKA меняется с низкого уровня на высокий уровень. В это время, из-за того, что тонкопленочные транзисторы T1, T11 находятся в состоянии «включено», потенциалы сигналов Q состояния (потенциалы выходных выводов 51, 52) увеличиваются с увеличением потенциала входного вывода 43. Когда потенциал выходного вывода 51 увеличивается, потенциал netA также увеличивается через конденсатор CAP. В результате большое напряжение прикладывают к выводам затвора тонкопленочных транзисторов T1, T11, и потенциалы сигналов Q состояния увеличиваются до уровня, достаточного для того, чтобы линия затворной шины, соединенная с выходным выводом 51 схемы с двумя устойчивыми состояниями, перешла в выбранное состояние.

Достигая момента времени t3, уровень первого синхроимпульса CKA меняется с высокого уровня на низкий уровень. В это время, из-за того, что тонкопленочные транзисторы T1, T11 находятся в состоянии «включено», электрический ток между истоком и стоком тонкопленочных транзисторов T1, T11 постепенно уменьшается, основываясь на уменьшении потенциала входного вывода 43 и потенциалов сигналов Q состояния (потенциалов выходных выводов 51, 52). Поскольку конденсатор CAP обеспечивают между выходным выводом 51 и netA, как показано на фиг. 19, потенциал netA также уменьшается в соответствии с уменьшением потенциала выходного вывода 51. Однако из-за того, что потенциал netA уменьшается ориентировочно в соответствии с уменьшением потенциала выходного вывода 51, потенциал netA не уменьшается до низкого уровня, а поддерживается на высоком уровне.

Достигая момента времени t4, сигнал R сброса и второй синхроимпульс CKB изменяются с низкого уровня до высокого уровня, соответственно. Соответственно, тонкопленочные транзисторы T4, T9 и T10 переходят в состояние «включено». С помощью перехода тонкопленочного транзистора T4 в состояние «включено» потенциал netA уменьшается до низкого уровня. В это время потенциал выходного вывода 51 также уменьшается с помощью перехода тонкопленочных транзисторов T9, T10 в состояние «включено», данное уменьшение потенциала становится незначительным. Это происходит по следующей причине. Достигая момента времени t4, потенциал netA имеет низкий уровень и тонкопленочный транзистор T1 переходит в состояние «выключено». Поскольку в общем случае период с момента времени t3 до момента времени t4 не обеспечивают или устанавливают очень коротким, результат уменьшения потенциала выходного вывода 51, основанного на токе между истоком и стоком тонкопленочного транзистора T1, не получают.

Как описано выше, потенциал выходного вывода 51 уменьшается постепенно. То есть снижение уровня сигнала GOUT сканирования после того, как заканчивается период заряда в каждой строке, становится незначительным. Поэтому при тенденции к увеличению размера и повышению разрешающей способности панели увеличивается риск возникновения неверного отображения, относящегося к смешиванию цветов, которое описано выше.

Задачей настоящего изобретения является реализация формирователя сигналов управления затвором, который может вызывать быстрое снижение уровня сигнала сканирования после того, как период заряда в каждой строке заканчивается, для предотвращения возникновение неверного отображения, относящегося к смешиванию цветов.

СРЕДСТВО ДЛЯ РЕШЕНИЯ ПРОБЛЕМЫ

Первый аспект настоящего изобретения направлен на схему возбуждения линий сигнала сканирования устройства отображения, которая возбуждает множество линий сигнала сканирования, которые упорядочены в блоке отображения, причем упомянутая схема содержит:

множество сдвиговых регистров, причем каждый сдвиговый регистр включает в себя множество схем с двумя устойчивыми состояниями, имеющих первое состояние и второе состояние и соединенных последовательно друг с другом, и каждый сдвиговый регистр работает, основываясь на множестве синхросигналов, которые циклически повторяют первое изменение уровня для изменения со второго уровня на первый уровень и второе изменение уровня для изменения с первого уровня на второй уровень, и в каждом сдвиговом регистре данное множество схем с двумя устойчивыми состояниями последовательно переходят в первое состояние с помощью одного из множества синхросигналов, обеспечиваемых для каждой схемы с двумя устойчивыми состояниями в качестве синхросигнала возбуждения линии сигнала сканирования, причем

синхросигнал, тактирование изменения уровня которого отличается, обеспечен в каждый сдвиговый регистр в качестве синхросигнала возбуждения линии сигнала сканирования,

каждая схема с двумя устойчивыми состояниями включает в себя

выходной узел, который соединен с линией сигнала сканирования и который выводит сигнал состояния, который указывает либо первое состояние, либо второе состояние,

переключающий элемент управления выходом, имеющий второй электрод, на который обеспечен синхросигнал возбуждения линии сигнала сканирования, и третий электрод, соединенный с выходным узлом,

блок включения первого узла, который изменяет уровень первого узла, который соединен с первым электродом переключающего элемента управления выходом, на уровень «включено», основываясь на сигнале состояния, который выведен из схемы с двумя устойчивыми состояниями предшествующего каскада рассматриваемой схемы с двумя устойчивыми состояниями, и

блок выключения первого узла, который принимает сигнал состояния, который выведен из схемы с двумя устойчивыми состояниями последующего каскада рассматриваемой схемы с двумя устойчивыми состояниями в качестве сигнала выключения первого узла, и который изменяет уровень первого узла на уровень «выключено», основываясь на сигнале выключения первого узла, и

в каждой схеме с двумя устойчивыми состояниями после того, как рассматриваемая схема с двумя устойчивыми состояниями переходит в первое состояние, и после того, как синхросигнал возбуждения линии сигнала сканирования выполняет второе изменение уровня, уровень сигнала выключения первого узла меняется таким образом, что выполняется выключение первого узла, в течение периода с момента времени после того, как схема с двумя устойчивыми состояниями следующего каскада рассматриваемой схемы с двумя устойчивыми состояниями в сдвиговом регистре, который включает в себя рассматриваемую схему с двумя устойчивыми состояниями, переходит в первое состояние, до момента времени, когда синхросигнал возбуждения линии сигнала сканирования выполняет первое изменение уровня.

Согласно второму аспекту настоящего изобретения, в первом аспекте настоящего изобретения

каждая схема с двумя устойчивыми состояниями дополнительно включает в себя блок выключения выходного узла, который принимает сигнал состояния, который выведен из схемы с двумя устойчивыми состояниями последующего каскада рассматриваемой схемы с двумя устойчивыми состояниями в качестве сигнала выключения выходного узла, и который выключает выходной узел, основываясь на сигнале выключения выходного узла, и

в каждой схеме с двумя устойчивыми состояниями после того, как рассматриваемая схема с двумя устойчивыми состояниями переходит в первое состояние, уровень сигнала выключения первого узла меняется таким образом, что выполняется выключение первого узла в течение периода с момента времени после момента времени, когда уровень сигнала выключения выходного узла меняется таким образом, что выполняется выключение выходного узла, до момента времени, когда синхросигнал возбуждения линии сигнала сканирования выполняет первое изменение уровня.

Согласно третьему аспекту настоящего изобретения, в первом аспекте настоящего изобретения

каждая схема с двумя устойчивыми состояниями дополнительно включает в себя

переключающий элемент управления первым узлом, имеющий второй электрод, соединенный с первым узлом, и третий электрод, к которому приложен потенциал уровня «выключено», и

блок управления вторым узлом, который управляет потенциалом второго узла, который соединен с первым электродом переключающего элемента управления первым узлом, основываясь на другом синхросигнале, чем синхросигнал возбуждения линии сигнала сканирования из множества синхросигналов, и на потенциале первого узла.

Согласно четвертому аспекту настоящего изобретения, в первом аспекте настоящего изобретения

схема возбуждения линий сигнала сканирования содержит два сдвиговых регистра, каждый из которых идентичен упомянутому сдвиговому регистру,

упомянутые два сдвиговых регистра поочередно выводят сигнал состояния в первом состоянии для каждой из множества линий сигнала сканирования, и

сигнал состояния, который выведен из схемы с двумя устойчивыми состояниями третьего каскада после рассматриваемой схемы с двумя устойчивыми состояниями, обеспечен для каждой схемы с двумя устойчивыми состояниями во всем сдвиговом регистре, который включает в себя упомянутые два сдвиговых регистра, в качестве сигнала выключения первого узла.

Согласно пятому аспекту настоящего изобретения, в четвертом аспекте настоящего изобретения

тактирования, когда выполняется вывод сигнала состояния в первом состоянии из упомянутых двух сдвиговых регистров, сдвинуты на период, приблизительно равный одному периоду горизонтального сканирования, и

период от того, когда синхросигнал возбуждения линии сигнала сканирования выполняет первое изменение уровня, до того, когда упомянутый сигнал выполняет второе изменение уровня, и период от того, когда упомянутый сигнал выполняет второе изменение уровня, до того, когда упомянутый сигнал выполняет первое изменение уровня, являются периодами, которые приблизительно равны двум периодам горизонтального сканирования.

Согласно шестому аспекту настоящего изобретения, в четвертом аспекте настоящего изобретения

упомянутые два сдвиговых регистра работают, основываясь на первом синхросигнале, который обеспечен для схемы с двумя устойчивыми состояниями первого каскада одного из сдвиговых регистров в качестве синхросигнала возбуждения сигнала сканирования, втором синхросигнале, имеющем фазу, сдвинутую относительно фазы первого синхросигнала на 180 градусов, третьем синхросигнале, имеющем фазу, задержанную относительно фазы первого синхросигнала на 90 градусов, и четвертом синхросигнале, имеющем фазу, сдвинутую относительно фазы третьего синхросигнала на 180 градусов.

Согласно седьмому аспекту настоящего изобретения, в первом аспекте настоящего изобретения

схема возбуждения линий сигнала сканирования содержит m сдвиговых регистров, каждый из которых идентичен упомянутому сдвиговому регистру,

m сдвиговых регистров последовательно выводят сигнал состояния в первом состоянии для каждой из множества линий сигнала сканирования,

сигнал состояния, который выведен из схемы с двумя устойчивыми состояниями k-го каскада после рассматриваемой схемы с двумя устойчивыми состояниями, обеспечен для каждой схемы с двумя устойчивыми состояниями во всем сдвиговом регистре, который включает в себя m сдвиговых регистров, в качестве сигнала выключения первого узла, и

зависимость между m и k соответствует следующему уравнению: m+1≤k≤2m-1, где m является целым числом, которое равно или больше двух.

Согласно восьмому аспекту настоящего изобретения, в седьмом аспекте настоящего изобретения

тактирования, когда выполняется вывод сигнала состояния в первом состоянии из m сдвиговых регистров, сдвинуты на период, приблизительно равный одному периоду горизонтального сканирования, и

период от того, когда синхросигнал возбуждения линии сигнала сканирования выполняет первое изменение уровня, до того, когда упомянутый сигнал выполняет второе изменение уровня, и период от того, когда упомянутый сигнал выполняет второе изменение уровня, до того, когда упомянутый сигнал выполняет первое изменение уровня, являются периодами, которые приблизительно равны m периодам горизонтального сканирования.

Согласно девятому аспекту настоящего изобретения, в седьмом аспекте настоящего изобретения

соединение для сигнала, который будет обеспечен для каждой схемы с двумя устойчивыми состояниями в качестве сигнала выключения первого узла, сформировано так, чтобы оно ответвлялось от соединения для сигнала, который будет обеспечен для схемы с двумя устойчивыми состояниями (k-m)-го каскада после рассматриваемой схемы с двумя устойчивыми состояниями в качестве сигнала выключения выходного узла.

Согласно десятому аспекту настоящего изобретения, в первом аспекте настоящего изобретения

соединение для передачи множества сигналов возбуждения для работы множества сдвиговых регистров обеспечены вместе для множества сдвиговых регистров, причем множество сигналов возбуждения включает в себя множество синхросигналов.

Согласно одиннадцатому аспекту настоящего изобретения, в первом аспекте настоящего изобретения

переключающие элементы, которые включены в каждую схему с двумя устойчивыми состояниями, являются тонкопленочными транзисторами, которые все имеют канал того же самого типа.

Согласно двенадцатому аспекту настоящего изобретения, в первом аспекте настоящего изобретения

переключающие элементы, которые включены в каждую схему с двумя устойчивыми состояниями, являются тонкопленочными транзисторами, которые выполнены из аморфного кремния.

Согласно тринадцатому аспекту настоящего изобретения, в первом аспекте настоящего изобретения

переключающие элементы, которые включены в каждую схему с двумя устойчивыми состояниями, являются тонкопленочными транзисторами, которые выполнены из микрокристаллического кремния.

Согласно четырнадцатому аспекту настоящего изобретения, в первом аспекте настоящего изобретения

переключающие элементы, которые включены в каждую схему с двумя устойчивыми состояниями, являются тонкопленочными транзисторами, которые выполнены из поликристаллического кремния.

Согласно пятнадцатому аспекту настоящего изобретения, в первом аспекте настоящего изобретения

переключающие элементы, которые включены в каждую схему с двумя устойчивыми состояниями, являются тонкопленочными транзисторами, которые выполнены из оксидных полупроводников.

Шестнадцатый аспект настоящего изобретения направлен на устройство отображения, которое включает в себя блок отображения и содержит схему возбуждения линий сигнала сканирования согласно первому аспекту настоящего изобретения.

Семнадцатый аспект настоящего изобретения направлен на способ возбуждения для возбуждения множества линий сигнала сканирования, упорядоченных в блоке отображения, с помощью схемы возбуждения линий сигнала сканирования, включающей в себя множество сдвиговых регистров, причем каждый сдвиговый регистр включает в себя множество схем с двумя устойчивыми состояниями, имеющих первое состояние и второе состояние и соединенных последовательно друг с другом, и каждый сдвиговый регистр работает, основываясь на множестве синхросигналов, которые циклически повторяют первое изменение уровня для изменения со второго уровня на первый уровень и второе изменение уровня для изменения с первого уровня на второй уровень, и в каждом сдвиговом регистре множество схем с двумя устойчивыми состояниями последовательно переходят в первое состояние с помощью одного из множества синхросигналов, обеспечиваемых для каждой схемы с двумя устойчивыми состояниями в качестве синхросигнала возбуждения линии сигнала сканирования, при этом упомянутый способ содержит:

первый этап возбуждения, на котором изменяют состояние каждой схемы с двумя устойчивыми состояниями со второго состояния на первое состояние; и

второй этап возбуждения, на котором изменяют состояние каждой схемы с двумя устойчивыми состояниями с первого состояния на второе состояние, причем

синхросигналы, тактирование изменения уровня которых отличается, обеспечивают в каждый сдвиговый регистр в качестве синхросигнала возбуждения линии сигнала сканирования,

каждая схема с двумя устойчивыми состояниями включает в себя

выходной узел, который соединяют с линией сигнала сканирования, и который выводит сигнал состояния, который указывает или первое состояние как уровень «включено», или второе состояние как уровень «выключено»,

переключающий элемент управления выходом, имеющий второй электрод, на который обеспечивают синхросигнал возбуждения линии сигнала сканирования, и третий электрод, соединенный с выходным узлом, и

первый узел, соединенный с первым электродом переключающего элемента управления выходом, и

в каждой схеме с двумя устойчивыми состояниями

первый этап возбуждения включает в себя

этап включения первого узла, на котором изменяют уровень первого узла до уровня «включено», основываясь на сигнале состояния, который выводят из схемы с двумя устойчивыми состояниями предшествующего каскада рассматриваемой схемы с двумя устойчивыми состояниями, и

этап включения сигнала состояния, на котором изменяют уровень сигнала состояния до уровня «включено», основываясь на первом изменении уровня синхросигнала возбуждения линии сигнала сканирования,

второй этап возбуждения включает в себя

этап выключения сигнала состояния, на котором изменяют уровень сигнала состояния до уровня «выключено», основываясь на втором изменении уровня синхросигнала возбуждения линии сигнала сканирования, и

этап выключения первого узла, на котором принимают сигнал состояния, который выводят из схемы с двумя устойчивыми состояниями последующего каскада рассматриваемой схемы с двумя устойчивыми состояниями в качестве сигнала выключения первого узла, и изменяют уровень первого узла до уровня «выключено», основываясь на сигнале выключения первого узла, и

после того, как этап включения сигнала состояния заканчивают, и после того, как начинают этап выключения сигнала состояния, начинают этап выключения первого узла в течение периода с момента времени после того, как схема с двумя устойчивыми состояниями следующего каскада рассматриваемой схемы с двумя устойчивыми состояниями в сдвиговом регистре, который включает в себя рассматриваемую схему с двумя устойчивыми состояниями, завершает этап включения сигнала состояния, до момента времени, когда синхросигнал возбуждения линии сигнала сканирования выполняет первое изменение уровня.

Согласно восемнадцатому аспекту настоящего изобретения, в семнадцатом аспекте настоящего изобретения

схема возбуждения линий сигнала сканирования содержит два сдвиговых регистра, каждый из которых идентичен упомянутому сдвиговому регистру,

упомянутые два сдвиговых регистра поочередно выводят сигнал состояния в первом состоянии для каждой из множества линий сигнала сканирования, и

сигнал состояния, который выводят из схемы с двумя устойчивыми состояниями третьего каскада после рассматриваемой схемы с двумя устойчивыми состояниями, обеспечивают для каждой схемы с двумя устойчивыми состояниями во всем сдвиговом регистре, который включает в себя упомянутые два сдвиговых регистра, в качестве сигнала выключения первого узла.

Согласно девятнадцатому аспекту настоящего изобретения, в восемнадцатом аспекте настоящего изобретения

тактирования, когда выполняют вывод сигнала состояния в первом состоянии из упомянутых двух сдвиговых регистров, сдвинуты на период, приблизительно равный одному периоду горизонтального сканирования, и

период от того, когда синхросигнал возбуждения линии сигнала сканирования выполняет первое изменение уровня, до того, когда упомянутый сигнал выполняет второе изменение уровня, и период от того, когда упомянутый сигнал выполняет второе изменение уровня, до того, когда упомянутый сигнал выполняет первое изменение уровня, являются периодами, которые приблизительно равны двум периодам горизонтального сканирования.

Согласно двадцатому аспекту настоящего изобретения, в семнадцатом аспекте настоящего изобретения

схема возбуждения линий сигнала сканирования содержит m сдвиговых регистров, каждый из которых идентичен упомянутому сдвиговому регистру,

m сдвиговых регистров последовательно выводят сигнал состояния в первом состоянии для каждой из множества линий сигнала сканирования,

сигнал состояния, который выводят из схемы с двумя устойчивыми состояниями k-го каскада после рассматриваемой схемы с двумя устойчивыми состояниями, обеспечивают для каждой схемы с двумя устойчивыми состояниями во всем сдвиговом регистре, который включает в себя m сдвиговых регистров, в качестве сигнала выключения первого узла, и

зависимость между m и k соответствует следующему уравнению:

m+1≤k≤2m-1,

где m является целым числом, которое равно или больше двух.

Согласно двадцать первому аспекту настоящего изобретения, в двадцатом аспекте настоящего изобретения

тактирования, когда выполняют вывод сигнала состояния в первом состоянии из m сдвиговых регистров, сдвинуты на период, приблизительно равный одному периоду горизонтального сканирования, и

период от того, когда синхросигнал возбуждения линии сигнала сканирования выполняет первое изменение уровня, до того, когда упомянутый сигнал выполняет второе изменение уровня, и период от того, когда упомянутый сигнал выполняет второе изменение уровня, до того, когда упомянутый сигнал выполняет первое изменение уровня, являются периодами, которые приблизительно равны m периодам горизонтального сканирования.

РЕЗУЛЬТАТ ИЗОБРЕТЕНИЯ

Согласно первому аспекту настоящего изобретения, в каждой схеме с двумя устойчивыми состояниями множества сдвиговых регистров, которые составляют схему возбуждения линий сигнала сканирования, первый узел поддерживают в состоянии уровня «включено» в течение периода, который соответствует сдвигу по фазе между каждым из сдвиговых регистров, после того, как потенциал выходного узла начинает уменьшаться, основываясь на изменении синхросигнала возбуждения линии сигнала сканирования с первого уровня до второго уровня. Поэтому переключающий элемент управления выходом поддерживают в состоянии «включено» в течение периода, который соответствует сдвигу по фазе между каждым из сдвиговых регистров, после того, как потенциал выходного узла начинает уменьшаться. Соответственно, результат уменьшения потенциала выходного узла, основанного на изменении уровня синхросигнала возбуждения линии сигнала сканирования, получают в достаточной степени. Поэтому потенциал сигнала сканирования, который выводят из каждого выходного узла, быстро уменьшается до уровня «выключено», после того, как выбранный период соответствующей линии сигнала сканирования заканчивается. В результате можно предотвращать возникновение неверного отображения, относящегося, например, к смешиванию цветов между цветом, который будут отображать в определенной строке, и цветом, который будут отображать в следующей строке. Дополнительно, из-за того, что период, в течение которого переключающий элемент управления выходом поддерживают в состоянии «включено», становится продолжительным, можно предотвращать возникновение неверного отображения, относящегося к волновому искажению сигнала сканирования, даже когда нагрузочная емкость линии сигнала сканирования увеличивается, основываясь на увеличении размера панели, и тому подобное.

Согласно второму аспекту настоящего изобретения, выключение выходного узла с помощью блока выключения выходного узла начинают до того, как начинают выключение первого узла с помощью блока выключения первого узла. Поэтому потенциал выходного узла уменьшается быстрее. В результате эффективно предотвращают возникновение неверного отображения.

Согласно третьему аспекту настоящего изобретения, потенциал второго узла можно устанавливать на уровень «включено» в каждом предопределенном периоде с помощью использования синхросигнала в течение периода, когда потенциал первого узла находится в уровне «выключено». Соответственно, переключающий элемент управления первым узлом переходит в состояние «включено» в каждом предопределенном периоде в течение периода, когда потенциал первого узла находится на уровне «выключено». Поэтому, например, даже когда происходит изменение порогового напряжения переключающего элемента управления выходом и ток утечки переключающего элемента становится большим, потенциал первого узла можно надежно устанавливать на уровень «выключено» в каждом предопределенном периоде, и можно устранить вывод неправильного импульса из выходного узла.

Согласно четвертому аспекту настоящего изобретения, период, в течение которого каждая схема с двумя устойчивыми состояниями будет поддерживаться в первом состоянии, становится периодом в состоянии «включено» выхода сдвигового регистра. Выключение первого узла начинают после периода, равного сдвигу по фазе между двумя сдвиговыми регистрами, добавленному к периоду в состоянии «включено» выхода сдвигового регистра, после каждого переключения схемы с двумя устойчивыми состояниями из второго состояния в первое состояние. Поэтому первый узел поддерживают в состоянии уровня «включено» в течение относительно продолжительного периода, и результат уменьшения потенциала выходного узла, основанного на изменении уровня синхросигнала возбуждения линии сигнала сканирования, получают в достаточной степени, аналогичным образом, как в первом аспекте настоящего изобретения.

Согласно пятому аспекту настоящего изобретения, результат уменьшения потенциала выходного узла, основанного на изменении уровня синхросигнала возбуждения линии сигнала сканирования, получают в достаточной степени, аналогичным образом, как в четвертом аспекте настоящего изобретения, основываясь на соглашении, что периоды горизонтального сканирования четных каскадов и нечетных каскадов сдвигового регистра равны.

Согласно шестому аспекту настоящего изобретения, результат, аналогичный результату четвертого аспекта настоящего изобретения, получают в схеме возбуждения линий сигнала сканирования, которая включает в себя множество сдвиговых регистров, которые работают, основываясь на синхросигналах с четырьмя фазами, фазы которых сдвинуты относительно друг друга на 90 градусов.

Согласно седьмому аспекту настоящего изобретения, период, в течение которого каждая схема с двумя устойчивыми состояниями будет поддерживаться в первом состоянии, становится периодом в состоянии «включено» сдвигового регистра. Выключение первого узла начинают после периода, равного сдвигу по фазе между соответствующими сдвиговыми регистрами, добавленному к периоду в состоянии «включено» выхода сдвигового регистра, после изменения состояния всех схем с двумя устойчивыми состояниями из второго состояния в первое состояние. Поэтому первый узел поддерживают в состоянии уровня «включено» в течение относительно продолжительного периода, и результат уменьшения потенциала выходного узла, основанного на изменении уровня синхросигнала возбуждения линии сигнала сканирования, получают в достаточной степени, аналогичным образом, как в первом аспекте настоящего изобретения.

Согласно восьмому аспекту настоящего изобретения, результат уменьшения потенциала выходного узла, основанного на изменении уровня синхросигнала возбуждения линии сигнала сканирования, получают в достаточной степени, аналогичным образом, как в седьмом аспекте настоящего изобретения, основываясь на соглашении, что периоды горизонтального сканирования каждого каскада сдвигового регистра равны.

Согласно девятому аспекту настоящего изобретения, можно уменьшать площадь соединений для передачи сигнала выключения первого узла, и можно миниатюризировать размер устройства отображения, которое включает в себя схему возбуждения линий сигнала сканирования согласно седьмому аспекту настоящего изобретения.

Согласно десятому аспекту настоящего изобретения, можно уменьшать площадь соединений для передачи сигнала возбуждения сдвигового регистра, и можно миниатюризировать размер устройства отображения, которое включает в себя схему возбуждения линий сигнала сканирования согласно первому аспекту настоящего изобретения.

Согласно одиннадцатому аспекту настоящего изобретения можно уменьшать стоимость производства схемы возбуждения линий сигнала сканирования.

Согласно двенадцатому аспекту настоящего изобретения, результат, аналогичный результату первого аспекта настоящего изобретения, получают в схеме возбуждения линий сигнала сканирования, которая использует в качестве переключающего элемента тонкопленочный транзистор, изготовленный из аморфного кремния.

Согласно тринадцатому аспекту настоящего изобретения, результат, аналогичный результату первого аспекта настоящего изобретения, получают в схеме возбуждения линий сигнала сканирования, которая использует в качестве переключающего элемента тонкопленочный транзистор, изготовленный из микрокристаллического кремния.

Согласно четырнадцатому аспекту настоящего изобретения, результат, аналогичный результату первого аспекта настоящего изобретения, получают в схеме возбуждения линий сигнала сканирования, которая использует в качестве переключающего элемента тонкопленочный транзистор, изготовленный из поликристаллического кремния.

Согласно пятнадцатому аспекту настоящего изобретения, результат, аналогичный результату первого аспекта настоящего изобретения, получают в схеме возбуждения линий сигнала сканирования, которая использует в качестве переключающего элемента тонкопленочный транзистор, изготовленный из оксидных полупроводников.

Согласно шестнадцатому аспекту настоящего изобретения, можно реализовать устройство отображения, которое включает в себя схему возбуждения линий сигнала сканирования, которая получает результат, аналогичный результату первого аспекта настоящего изобретения.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

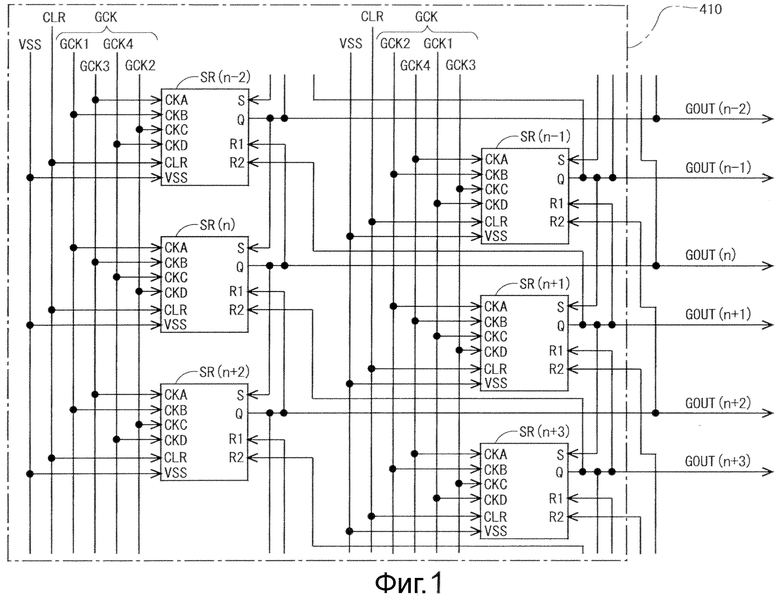

Фиг. 1 является структурной схемой для описания «всего сдвигового регистра» в жидкокристаллическом устройстве отображения с активной матрицей согласно первому варианту осуществления настоящего изобретения.

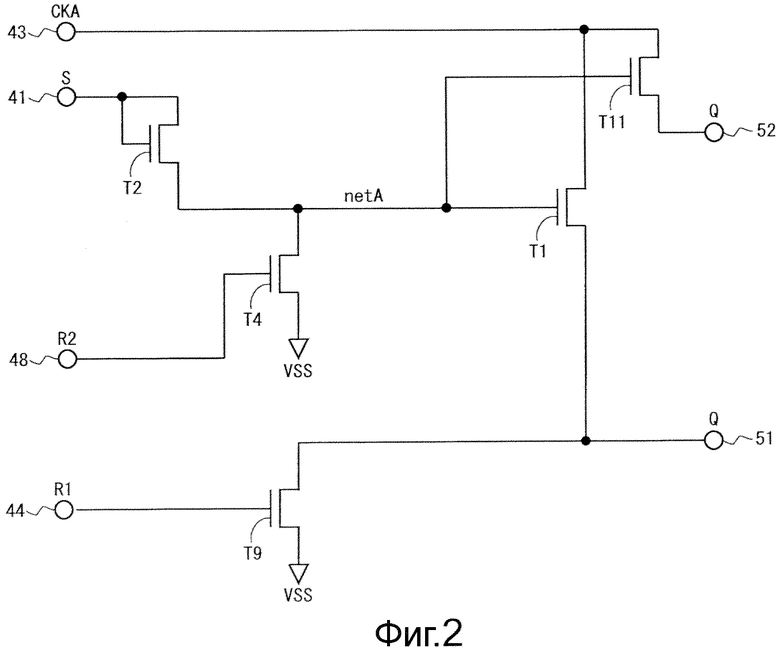

Фиг. 2 является принципиальной электрической схемой, показывающей основную часть конфигурации схемы с двумя устойчивыми состояниями в каждом варианте осуществления.

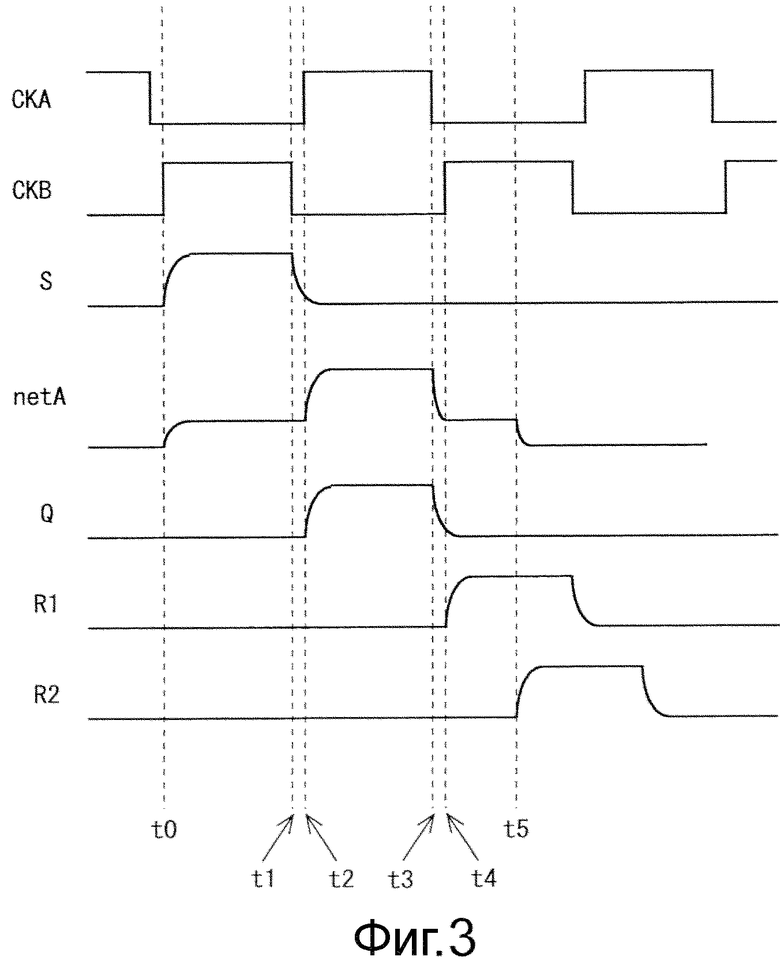

Фиг. 3 является диаграммой формы сигналов для описания основного принципа работы схемы с двумя устойчивыми состояниями в каждом варианте осуществления.

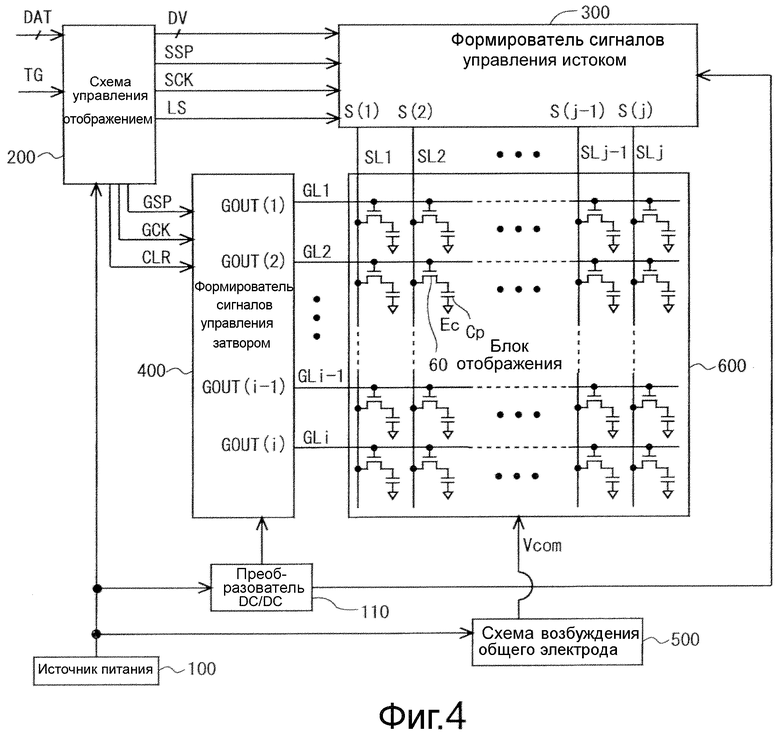

Фиг. 4 является структурной схемой, показывающей полную конфигурацию жидкокристаллического устройства отображения в первом варианте осуществления.

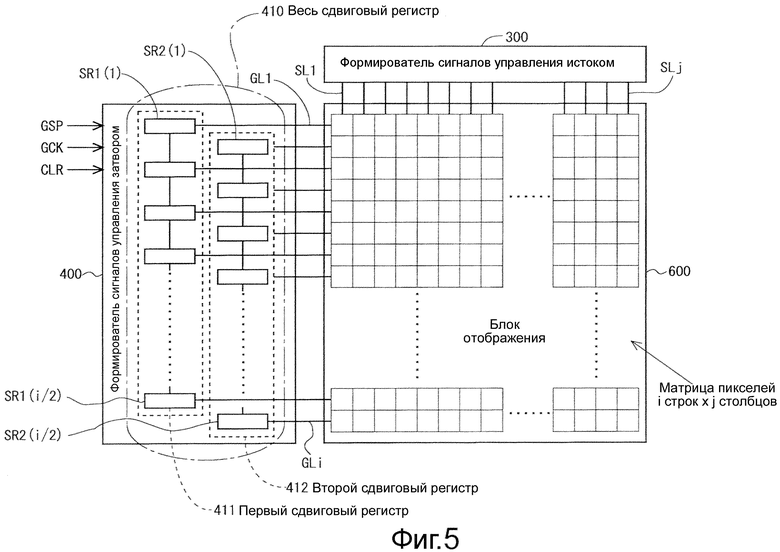

Фиг. 5 является структурной схемой для описания конфигурации формирователя сигналов управления затвором в первом варианте осуществления.

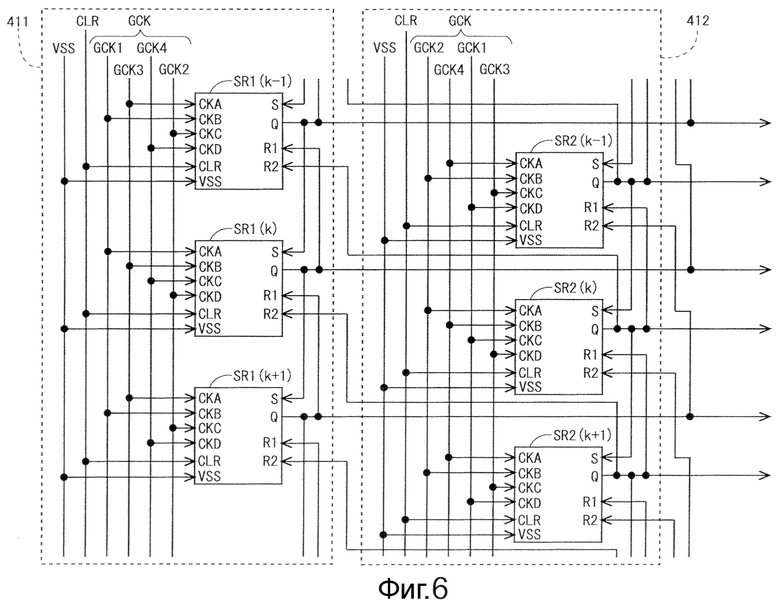

Фиг. 6 является структурной схемой, показывающей конфигурацию сдвиговых регистров в формирователе сигналов управления затвором в первом варианте осуществления.

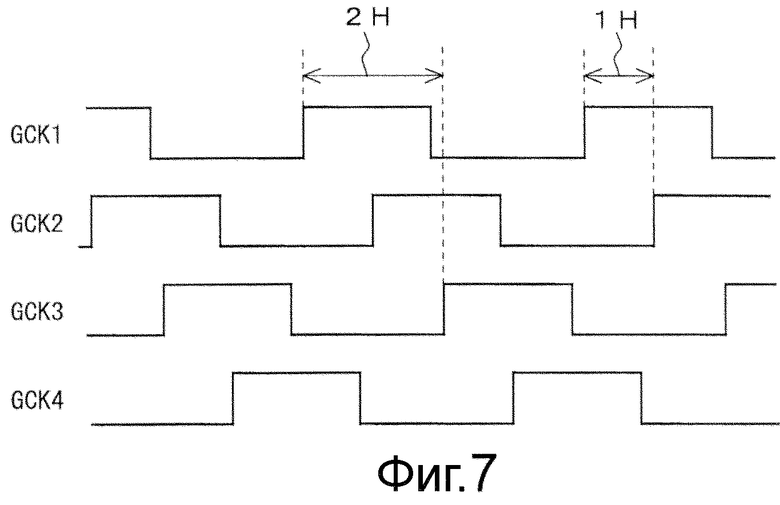

Фиг. 7 является диаграммой формы синхросигналов затвора с первого по четвертый в первом варианте осуществления.

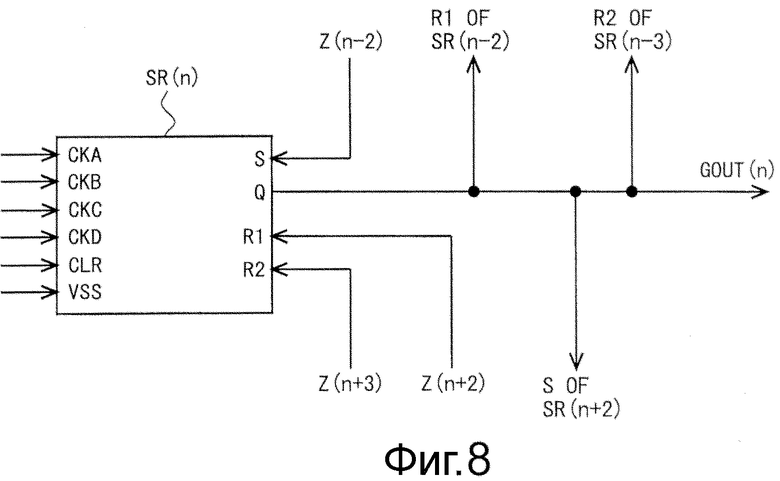

Фиг. 8 является объяснительной схемой сигналов ввода-вывода схемы с двумя устойчивыми состояниями n-го каскада всего сдвигового регистра в первом варианте осуществления.

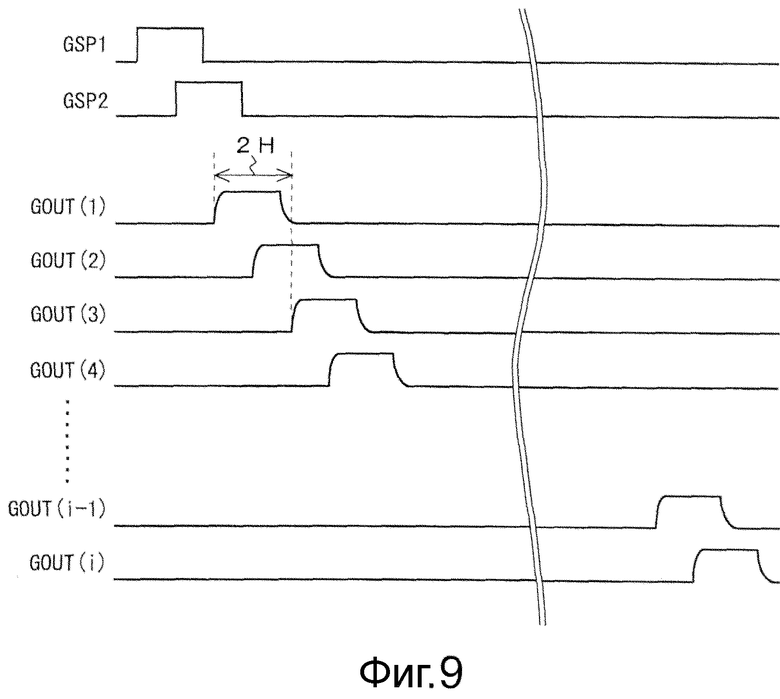

Фиг. 9 является диаграммой формы сигналов для описания работы формирователя сигналов управления затвором в первом варианте осуществления.

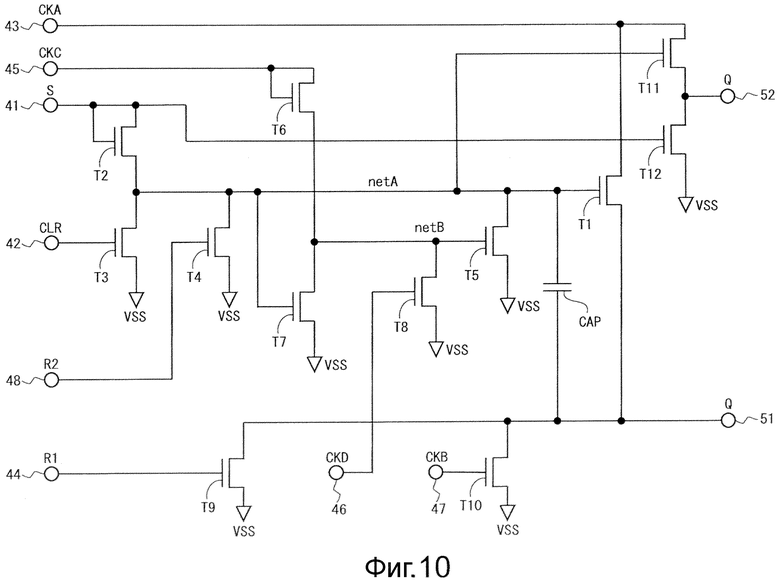

Фиг. 10 является принципиальной электрической схемой, показывающей конфигурацию схемы с двумя устойчивыми состояниями, которую включает в себя сдвиговый регистр в первом варианте осуществления.

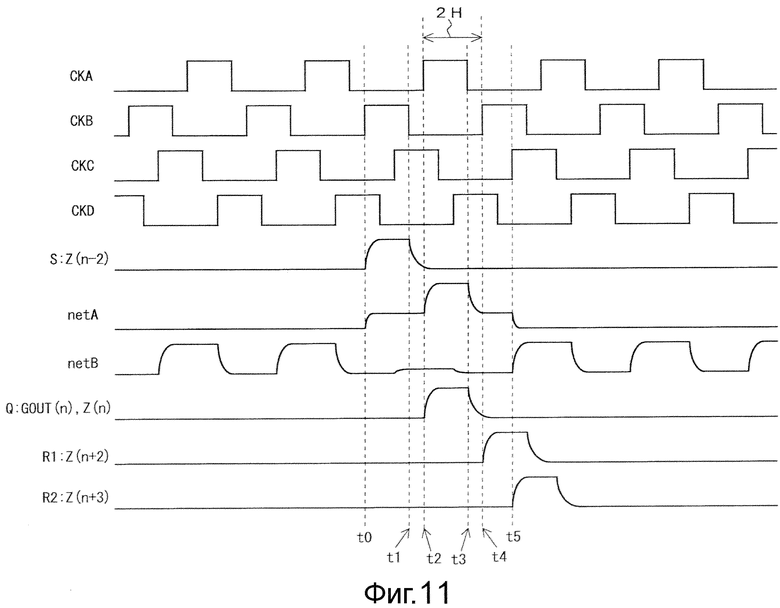

Фиг. 11 является диаграммой формы сигналов для описания работы каждого каскада сдвигового регистра в первом варианте осуществления.

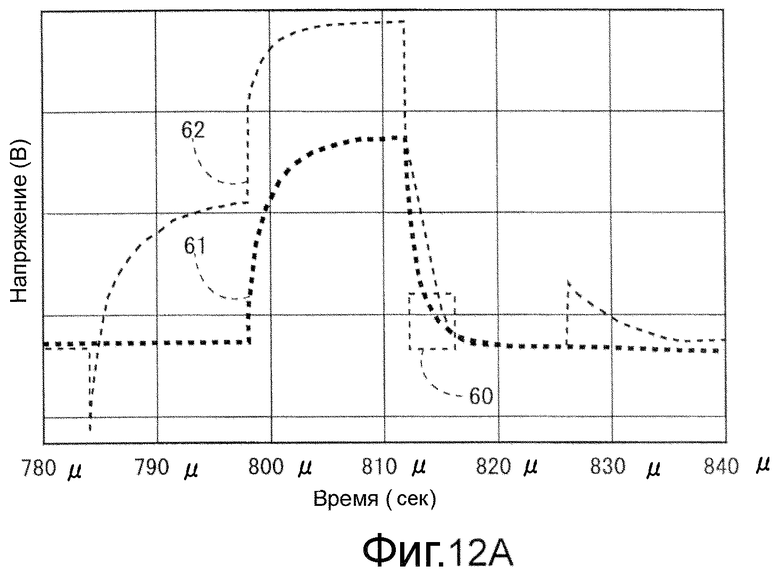

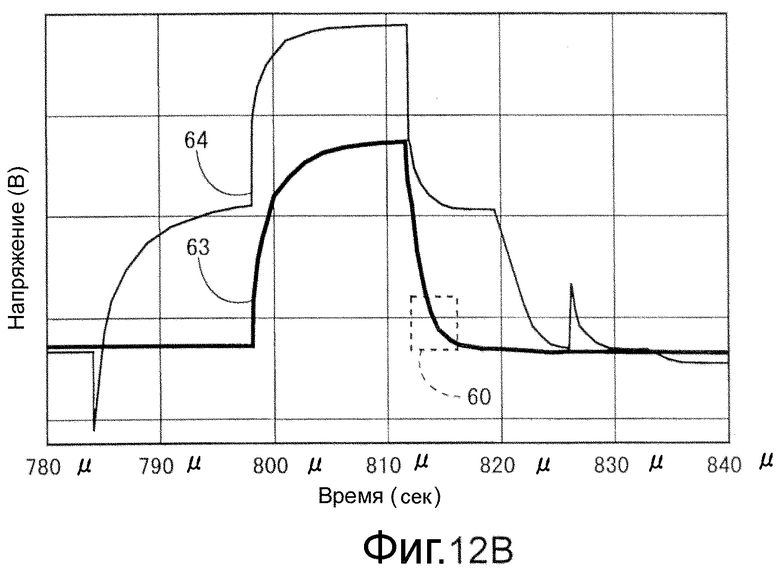

Фиг. 12A и 12B являются схемами, которые объясняют результат первого варианта осуществления.

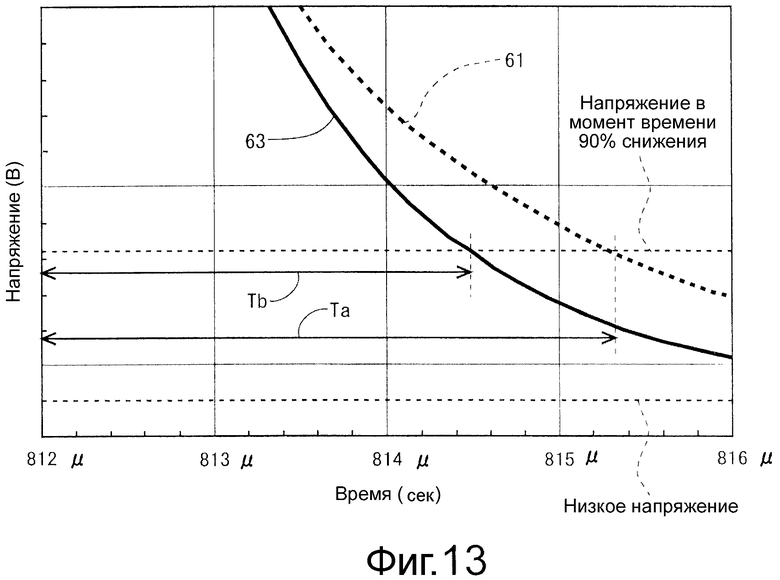

Фиг. 13 является схемой, которая объясняет результат первого варианта осуществления.

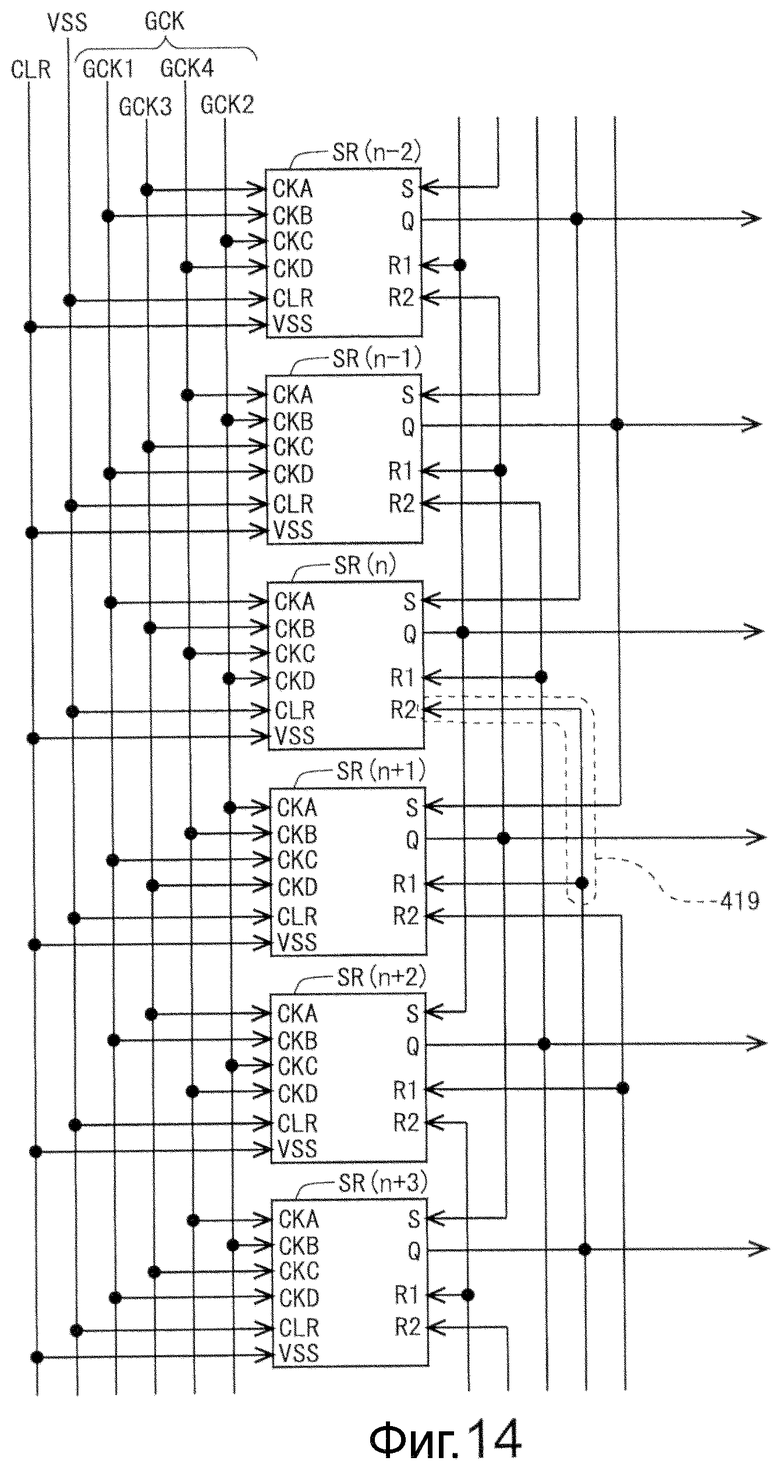

Фиг. 14 является структурной схемой, показывающей конфигурацию сдвигового регистра в формирователе сигналов управления затвором в модификации первого варианта осуществления.

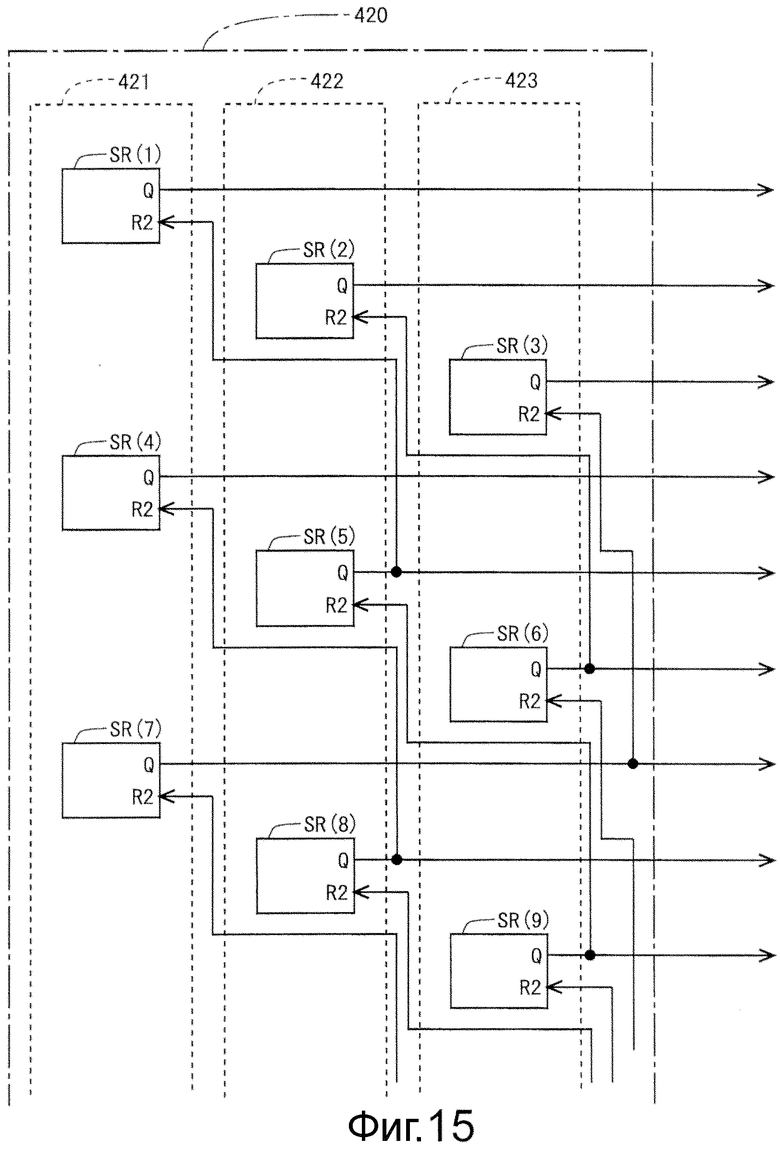

Фиг. 15 является структурной схемой, показывающей принципиальную схему сдвигового регистра в формирователе сигналов управления затвором жидкокристаллического устройства отображения с активной матрицей согласно второму варианту осуществления настоящего изобретения.

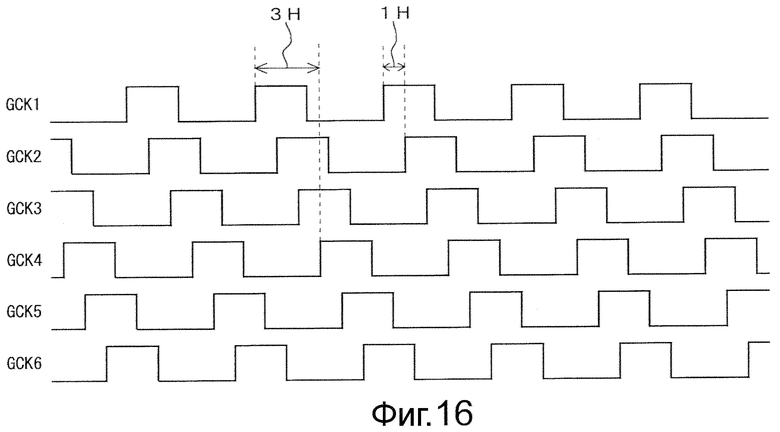

Фиг. 16 является диаграммой формы синхросигналов затвора с первого по шестой во втором варианте осуществления.

Фиг. 17 является схемой, показывающей пример зависимости между синхросигналами затвора с первого по шестой и синхроимпульсами с первого по четвертый в каждом сдвиговом регистре во втором варианте осуществления.

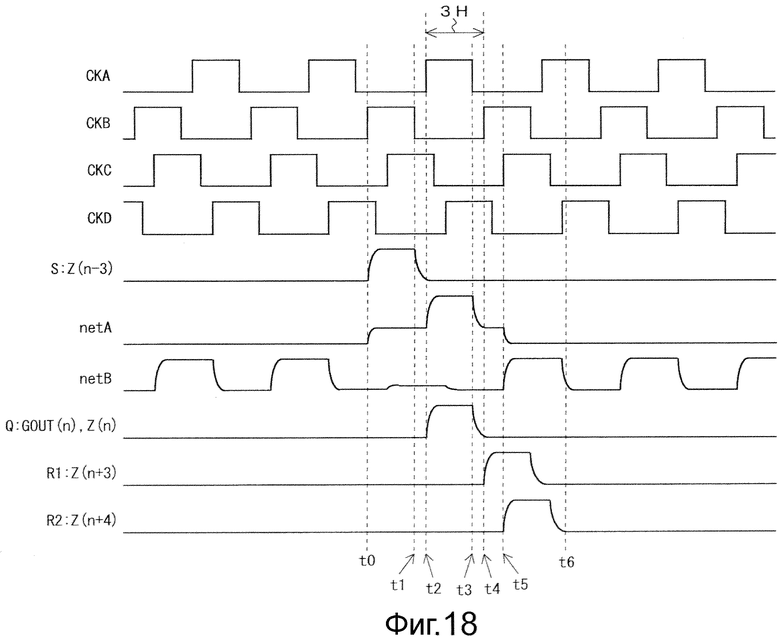

Фиг. 18 является диаграммой формы сигналов для описания работы схемы с двумя устойчивыми состояниями во втором варианте осуществления.

Фиг. 19 является принципиальной электрической схемой, показывающей пример конфигурации схемы с двумя устойчивыми состояниями, которую включает в себя сдвиговый регистр в формирователе сигналов управления затвором.

Фиг. 20 является диаграммой формы сигналов для описания работы каждого каскада сдвигового регистра.

ВАРИАНТЫ ОСУЩЕСТВЛЕНИЯ ИЗОБРЕТЕНИЯ

Варианты осуществления настоящего изобретения описаны ниже со ссылкой на сопроводительные чертежи. В последующем описании вывод затвора (электрод затвора) тонкопленочного транзистора соответствует первому электроду, вывод стока (электрод стока) соответствует второму электроду, а вывод истока (электрод истока) соответствует третьему электроду. Все тонкопленочные транзисторы, которые обеспечивают в схеме с двумя устойчивыми состояниями, описаны как тонкопленочные транзисторы с каналом n-типа.

<1. Концепция вариантов осуществления>

Сначала концепция описанных ниже вариантов осуществления описана со ссылкой на фиг. 2 и 3. Фиг. 2 является принципиальной электрической схемой, показывающей основную часть конфигурации одного каскада (конфигурации схемы с двумя устойчивыми состояниями) сдвигового регистра в каждом варианте осуществления. Фиг. 3 является диаграммой формы сигналов для описания принципа работы схемы с двумя устойчивыми состояниями.

Как показано на фиг. 2, схема с двумя устойчивыми состояниями включает в себя пять тонкопленочных транзисторов T1, T2, T4, T9 и T11. У схемы с двумя устойчивыми состояниями также есть четыре входных вывода 41, 43, 44 и 48 и два выходного вывода 51, 52 в дополнение к входному выводу для напряжения VSS низкого уровня источника питания. Вывод затвора тонкопленочного транзистора T1, вывод затвора тонкопленочного транзистора T11, вывод истока тонкопленочного транзистора T2 и вывод стока тонкопленочного транзистора T4 соединяют друг с другом. Область (соединения), в которой эти выводы соединяют друг с другом, для удобства называют «netA» (первым узлом).

Что касается тонкопленочного транзистора T1, вывод затвора соединяют с netA, вывод стока соединяют с входным выводом 43, а вывод истока соединяют с выходным выводом 51. Что касается тонкопленочного транзистора T2, вывод затвора и вывод стока соединяют с входным выводом 41 (т.е. в диодном включении), а вывод истока соединяют с netA. Что касается тонкопленочного транзистора T4, вывод затвора соединяют с входным выводом 48, вывод стока соединяют с netA, а вывод истока соединяют с напряжением VSS источника питания. Что касается тонкопленочного транзистора T9, вывод затвора соединяют с входным выводом 44, вывод стока соединяют с выходным выводом 51, а вывод истока соединяют с напряжением VSS источника питания. Что касается тонкопленочного транзистора T11, вывод затвора соединяют с netA, вывод стока соединяют с входным выводом 43, а вывод истока соединяют с выходным выводом 52. В последующих вариантах осуществления два выходных вывода 51, 52 обеспечивают в качестве выводов для вывода сигналов Q состояния. Однако настоящее изобретение не ограничено этим, и конфигурация может быть такой, что обеспечивают один выходной вывод 51.

В вышеупомянутой конфигурации схема с двумя устойчивыми состояниями работает следующим образом (см. фиг. 3). Достигая момента времени t0, уровень сигнала S установки меняется с низкого уровня на высокий уровень. Соответственно, тонкопленочный транзистор T2 переходит в состояние «включено», уровень потенциала netA меняется с низкого уровня на высокий уровень. В результате тонкопленочные транзисторы T1, T11 переходят в состояние «включено». Однако в течение периода с момента времени t0 до момента времени t2 первый синхроимпульс CKA имеет низкий уровень, и поэтому сигнал Q состояния поддерживают на низком уровне.

После того как уровень второго синхроимпульса CKB меняется с высокого уровня на низкий уровень в момент времени t1, когда достигают момент времени t2, уровень первого синхроимпульса CKA меняется с низкого уровня на высокий уровень. В это время, из-за того, что тонкопленочные транзисторы T1, T11 находятся в состоянии «включено», потенциалы сигналов Q состояния (потенциалы выходных выводов 51, 52) увеличиваются с увеличением потенциала входного вывода 43. Соответственно, линия затворной шины, которая соединена с выходным выводом 51 этой схемы с двумя устойчивыми состояниями, переходит в выбранное состояние. Когда достигают момент времени t3, уровень первого синхроимпульса CKA меняется с высокого уровня на низкий уровень. В это время, из-за того, что тонкопленочные транзисторы T1, T11 находятся в состоянии «включено», электрический ток между истоком и стоком тонкопленочных транзисторов T1, T11 зависит от уменьшения потенциала входного вывода 43, и потенциал сигналов Q состояния (потенциалы выходных выводов 51, 52) уменьшается.

Достигая момента времени t4, уровень первого сигнала R1 сброса меняется с низкого уровня на высокий уровень. Соответственно, тонкопленочный транзистор T9 переходит в состояние «включено», и потенциал выходного вывода 51 уменьшается. В это время из-за того, что второй сигнал R2 сброса поддерживают на низком уровне, тонкопленочный транзистор T4 находится в состоянии «выключено». Поэтому в течение периода, когда уровень сигнала Q состояния меняется с высокого уровня на низкий уровень, потенциал netA поддерживают на высоком уровне. Поэтому тонкопленочный транзистор T1 поддерживают в состоянии «включено» в и после момента времени t4, и результат уменьшения потенциала сигнала Q состояния, основанного на изменении первого синхроимпульса CKA с высокого уровня на низкий уровень, получают в достаточной степени. В результате потенциал выходного вывода 51 быстро уменьшается до низкого уровня.

Достигая момента времени t5, уровень второго сигнала R2 сброса меняется с низкого уровня на высокий уровень. Соответственно, тонкопленочный транзистор T4 переходит в состояние «включено», и уровень потенциала netA меняется с высокого уровня на низкий уровень.

Как описано выше, в каждом варианте осуществления в качестве сигнала для уменьшения потенциала выходного вывода 51 и сигнала для уменьшения потенциала netA используют различные сигналы, и тактирование, когда уровень потенциала netA меняется с высокого уровня на низкий уровень, устанавливают позже, чем тактирование, когда уровень потенциала выходного вывода 51 меняется с высокого уровня на низкий уровень. В частности, в каждом из последующих вариантов осуществления сигнал Q состояния (сигнал сканирования) для возбуждения последующей строки относительно строки, возбуждаемой сигналом Q состояния (сигналом сканирования), соответствующим первому сигналу R1 сброса каждой схемы с двумя устойчивыми состояниями, обеспечивают к схеме с двумя устойчивыми состояниями в качестве второго сигнала R2 сброса, так что потенциал netA уменьшается, основываясь на втором сигнале R2 сброса, уровень которого меняется с низкого уровня на высокий уровень при более позднем тактировании, чем тактирование первого сигнала R1 сброса для уменьшения потенциала выходного вывода 51. Согласно этой конфигурации период, когда потенциал netA поддерживают на высоком уровне, становится более продолжительным, чем обычный период, и результат уменьшения потенциала сигнала Q состояния, основанного на изменении уровня первого синхроимпульса CKA с высокого уровня на низкий уровень, получают в достаточной степени. Поэтому, после того, как период заряда в каждой строке заканчивается, потенциал сигнала сканирования для возбуждения каждой строки быстро уменьшается до низкого уровня.

<2. Первый вариант осуществления>

<2.1 Полная конфигурация и работа>

Фиг. 4 является структурной схемой, показывающей полную конфигурацию жидкокристаллического устройства отображения с активной матрицей согласно первому варианту осуществления настоящего изобретения. Как показано на фиг. 4, жидкокристаллическое устройство отображения включает в себя источник 100 питания, преобразователь 110 DC/DC (преобразования напряжения постоянного тока), схему 200 управления отображением, формирователь 300 сигналов управления истоком (схему возбуждения линий видеосигнала), формирователь 400 сигналов управления затвором (схему возбуждения линий сигнала сканирования), схему 500 возбуждения общего электрода и блок 600 отображения. Формирователь 400 сигналов управления затвором сформирован на панели отображения, которая включает в себя блок 600 отображения, при использовании аморфных кремниевых, или поликристаллических кремниевых, или микрокристаллических кремниевых, или оксидных полупроводников (например, на основе оксида индия, галлия и цинка (IGZO)) и т.д. То есть в настоящем варианте осуществления формирователь 400 сигналов управления затвором имеет монолитную конфигурацию.

Блок 600 отображения включает в себя множество (j) линий SL1 - SLj истоковой шины (линий видеосигнала), множество (i) линий GL1-GLi затворной шины (линий сигнала сканирования) и множество (i×j) участков формирования пикселя, которые обеспечивают на соответствующих пересечениях линий SL1 - SLj истоковой шины и линий GL1-GLi затворной шины. Участки формирования пикселя составляют массив пикселей, размещенных в форме матрицы. Каждый участок формирования пикселя включает в себя тонкопленочный транзистор (TFT) 60, который является переключающим элементом, соединяющим вывод затвора с линией затворной шины, проходящей через соответствующее пересечение, и соединяющим вывод истока с линией истоковой шины, проходящей через это пересечение, пиксельный электрод, который соединяют с выводом стока тонкопленочного транзистора 60, общий электрод Ec, который является противоположным электродом, который обеспечивают вместе ко множеству участков формирования пикселя, и жидкокристаллический слой, который обеспечивают вместе ко множеству участков формирования пикселя и который расположен между пиксельным электродом и общим электродом Ec. Конденсатор пикселя Cp формируют с помощью жидкокристаллического конденсатора, который формируют с помощью пиксельного электрода и общего электрода Ec. Обычно, вспомогательный конденсатор обеспечивают параллельно с жидкокристаллическим конденсатором для надежного поддержания напряжения в конденсаторе пикселя Cp. Однако, так как вспомогательный конденсатор непосредственно не относится к настоящему изобретению, описание и чертеж вспомогательного конденсатора опущены.

Источник 100 питания подает предопределенное напряжение источника питания на преобразователь 110 DC/DC, схему 200 управления отображением и схему 500 возбуждения общего электрода. Преобразователь 110 DC/DC генерирует предопределенное напряжение постоянного тока из напряжения источника питания для работы формирователя 300 сигналов управления истоком и формирователя 400 сигналов управления затвором и подает напряжение постоянного тока на формирователь 300 сигналов управления истоком и на формирователь 400 сигналов управления затвором. Схема 500 возбуждения общего электрода прикладывает предопределенное напряжение Vcom к общему электроду Ec.

Схема 200 управления отображением принимает сигнал DAT изображения и группу TG сигналов тактирования, таких как сигнал горизонтальной синхронизации и сигнал вертикальной синхронизации, которые передают извне, и выводит цифровой видеосигнал DV и сигнал SSP запускающего импульса истока, синхросигнал SCK истока, стробирующий сигнал LS фиксации, сигнал GSP запускающего импульса затвора, синхросигнал GCK затвора и сигнал CLR очистки, которые предназначены для управления отображением изображения блока 600 отображения. Синхросигнал GCK затвора сформирован с помощью синхросигналов GCK1, GCK2, GCK3 и GCK4 с четырьмя фазами, как будет описано позже. Сигнал GSP запускающего импульса затвора сформирован с помощью первого сигнала GSP1 запускающего импульса затвора и второго сигнала GSP2 запускающего импульса затвора.

Формирователь 300 сигналов управления истоком принимает цифровой видеосигнал DV, сигнал SSP запускающего импульса истока, синхросигнал SCK истока и стробирующий сигнал LS фиксации, которые выводят из схемы 200 управления отображением, и подает видеосигналы S(1)-S(j) возбуждения в линии SL1 - SLj истоковой шины.

Формирователь 400 сигналов управления затвором применяет повторение активных сигналов GOUT(1)-GOUT(i) сканирования к линиям GL1-GLi затворной шины в циклах из одного периода вертикального сканирования, основываясь на сигнале GSP запускающего импульса затвора, синхросигнале GCK затвора и сигнале CLR очистки, которые выводят из схемы 200 управления отображением. формирователь 400 сигналов управления затвором подробно описан позже.

Как описано выше, с помощью видеосигналов S(1)-S(j) возбуждения, поданных на линии SL1-SLj истоковой шины, и сигналов GOUT(1) - GOUT(i) сканирования, поданных на линии GL1-GLi затворной шины, изображение, основанное на сигнале DAT изображения, передаваемом извне, отображают в блоке 600 отображения.

<2.2 Конфигурации и работа формирователя сигналов управления затвором>

Конфигурация формирователя 400 сигналов управления затвором в настоящем варианте осуществления описана далее со ссылкой на фиг. 1, 5 и 6. Как показано на фиг. 5, формирователь 400 сигналов управления затвором включает в себя два сдвиговых регистра (первый сдвиговый регистр 411 и второй сдвиговый регистр 412). Матрица пикселей i строк × j столбцов сформирована в блоке 600 отображения. Каскады первого сдвигового регистра 411 обеспечивают так, чтобы они имели взаимно-однозначное соответствие нечетным строкам матрицы пикселей, а каскады второго сдвигового регистра 412 обеспечивают так, чтобы они имели взаимно-однозначное соответствие четным строкам матрицы пикселей. Поэтому каждый из первого сдвигового регистра 411 и второго сдвигового регистра 412 сформирован с помощью (i/2) каскадов. Дополнительно, каждый каскад первого сдвигового регистра 411 и второго сдвигового регистра 412 является схемой с двумя устойчивыми состояниями, которая находится в одном из двух состояний (в первом состоянии и во втором состоянии) в каждый момент времени и которая выводит в качестве сигнала сканирования сигнал (сигнал состояния), который указывает это состояние. Таким образом, первый сдвиговый регистр 411 сформирован с помощью (i/2) схем SR1(1)-SR1(i/2) с двумя устойчивыми состояниями, а второй сдвиговый регистр 412 сформирован с помощью (i/2) схем SR2(1)-SR2(i/2) с двумя устойчивыми состояниями. В настоящем варианте осуществления, когда схема с двумя устойчивыми состояниями находится в первом состоянии, эта схема с двумя устойчивыми состояниями выводит сигнал состояния высокого уровня (H уровня) в качестве сигнала сканирования, а когда схема с двумя устойчивыми состояниями находится во втором состоянии, эта схема с двумя устойчивыми состояниями выводит сигнал состояния низкого уровня (L уровня) в качестве сигнала сканирования. Сигнал состояния, который также выводят из каждой схемы с двумя устойчивыми состояниями, функционирует в качестве управляющего сигнала другого каскада, который управляет работой схемы с двумя устойчивыми состояниями каскада, отличающегося от каскада рассматриваемой схемы с двумя устойчивыми состояниями.

Фиг. 6 - структурная схема, показывающая конфигурацию первого сдвигового регистра 411 и второго сдвигового регистра 412 в формирователе 400 сигналов управления затвором. Как показано на фиг. 6, в каждой схеме с двумя устойчивыми состояниями входные выводы для приема каждого из четырехфазных синхросигналов CKA (в дальнейшем называют «первый синхроимпульс»), CKB (в дальнейшем называют «второй синхроимпульс»), CKC (в дальнейшем называют «третий синхроимпульс») и CKD (в дальнейшем называют «четвертый синхроимпульс»), входной вывод для приема сигнала CLR очистки, входной вывод для приема напряжения VSS низкого уровня источника питания, входной вывод для приема сигнала S установки в качестве сигнала запуска сканирования, входные выводы для приема каждого из первого сигнала R1 сброса и второго сигнала R2 сброса в качестве сигнала окончания сканирования, и выходной вывод для вывода сигнала Q состояния. Выходной вывод схемы с двумя устойчивыми состояниями в первом сдвиговом регистре 411 соединяют с линией затворной шины нечетных строк, а выходной вывод схемы с двумя устойчивыми состояниями во втором сдвиговом регистре 412 соединяют с линией затворной шины четных строк.

Согласно вышеупомянутой конфигурации линиями затворной шины нечетных строк возбуждают с помощью первого сдвигового регистра 411, а линиями затворной шины четных строк возбуждают с помощью второго сдвигового регистра 412. С помощью первого сигнала GSP1 запускающего импульса затвора, обеспечиваемого к первому каскаду SR1(1) первого сдвигового регистра 411, и второго сигнала GSP2 запускающего импульса затвора, обеспечиваемого к первому каскаду SR2(1) второго сдвигового регистра 412, линии затворной шины в блоке 600 отображения последовательно выбирают одну за другой. С вышеупомянутой точки зрения можно полагать, что «первый сдвиговый регистр 411 и второй сдвиговый регистр 412 реализуют один сдвиговый регистр, который последовательно выбирает каждую из i линий GL1-GLi затворной шины». Поэтому в последующем конфигурацию, в которой существуют объединенные вместе первый сдвиговый регистр 411 и второй сдвиговый регистр 412, называют «весь сдвиговый регистр», и всему сдвиговому регистру назначено позиционное обозначение 410. Следует отметить, что, как показано на фиг. 1, ссылочный символ SR(n) назначен схеме с двумя устойчивыми состояниями n-го каскада всего сдвигового регистра 410.

В качестве синхросигнала GCK затвора, синхросигналы с четырьмя фазами GCK1 (в дальнейшем называют «первый синхросигнал затвора»), GCK2 (в дальнейшем называют «второй синхросигнал затвора»), GCK3 (в дальнейшем называют «третий синхросигнал затвора») и GCK4 (в дальнейшем называют «четвертый синхросигнал затвора»), обеспечивают на первый сдвиговый регистр 411 и второй сдвиговый регистр 412. Как показано на фиг. 7, для каждого из синхросигналов затвора с первого по четвертый GCK1 - GCK4 период состояния «включено» (период, в течение которого сигнал поддерживают в состоянии высокого уровня) составляет приблизительно два периода горизонтального сканирования (2H). Для каждого сигнала высокий уровень соответствует первому уровню, а низкий уровень соответствует второму уровню.

Фаза первого синхросигнала GCK1 затвора и фаза третьего синхросигнала GCK3 затвора сдвинуты относительно друг друга на 180 градусов. Фаза второго синхросигнала GCK2 затвора и фаза четвертого синхросигнала GCK4 затвора сдвинуты относительно друг друга на 180 градусов. Фаза первого синхросигнала GCK1 затвора сдвинута вперед на 90 градусов от фазы второго синхросигнала GCK2 затвора. Сдвиг по фазе на 90 градусов соответствует приблизительно одному периоду горизонтального сканирования (1H).

Сигналы обеспечивают к входным выводам (каждого каскада (каждой схемы с двумя устойчивыми состояниями) следующим образом (см. фиг. 6). В первом сдвиговом регистре 411 один из первого синхросигнала GCK1 затвора и третьего синхросигнала GCK3 затвора обеспечивают в качестве первого синхроимпульса CKA, а другой обеспечивают в качестве второго синхроимпульса CKB. Когда третий синхросигнал GCK3 затвора обеспечивают, например, в качестве первого синхроимпульса CKA в нечетном каскаде, первый синхросигнал GCK1 затвора обеспечивают в качестве первого синхроимпульса CKA в четном каскаде. В первом сдвиговом регистре 411 один из второго синхросигнала GCK2 затвора и четвертого синхросигнала GCK4 затвора обеспечивают в качестве третьего синхроимпульса CKC, а другой обеспечивают в качестве четвертого синхроимпульса CKD. Во втором сдвиговом регистре 412 один из второго синхросигнала GCK2 затвора и четвертого синхросигнала GCK4 затвора обеспечивают в качестве первого синхроимпульса CKA, а другой обеспечивают в качестве второго синхроимпульса CKB. Во втором сдвиговом регистре 412 один из первого синхросигнала GCK1 затвора и третьего синхросигнала GCK3 затвора обеспечивают в качестве третьего синхроимпульса CKC, а другой обеспечивают в качестве четвертого синхроимпульса CKD. Сигнал CLR очистки и напряжение VSS низкого уровня источника питания обычно обеспечивается ко всем схемам с двумя устойчивыми состояниями.

Сигнал S установки, первый сигнал R1 сброса и второй сигнал R2 сброса обеспечивают следующим образом (см. фиг. 8). Когда обращают внимание на n-ный каскад SR(n) всего сдвигового регистра 410, управляющий сигнал Z(n-2) другого каскада, который выводят из второго предыдущего каскада, обеспечивают в качестве сигнала S установки, управляющий сигнал Z(n+2) другого каскада, который выводят из второго последующего каскада, обеспечивают в качестве первого сигнала R1 сброса, и управляющий сигнал Z(n+3) другого каскада, который выводят из третьего последующего каскада, обеспечивают в качестве второго сигнала R2 сброса. Например, когда обращают внимание на седьмой каскад SR(7) всего сдвигового регистра 410, управляющий сигнал Z(5) другого каскада, который выводят из пятого каскада SR(5), обеспечивают в качестве сигнала S установки, управляющий сигнал Z(9) другого каскада, который выводят из девятого каскада SR(9), обеспечивают в качестве первого сигнала R1 сброса, и управляющий сигнал Z(10) другого каскада, который выводят из десятого каскада SR(10), обеспечивают в качестве второго сигнала R2 сброса. Другими словами, когда обращают внимание на четвертый каскад SR1(4) первого сдвигового регистра 411, сигнал Q состояния, который выводят из третьего каскада SR1(3) первого сдвигового регистра 411, обеспечивают в качестве сигнала S установки, сигнал Q состояния, который выводят из пятого каскада SR1(5) первого сдвигового регистра 411, обеспечивают в качестве первого сигнала R1 сброса, и сигнал Q состояния, который выводят из пятого каскада SR2(5) второго сдвигового регистра 412, обеспечивают в качестве второго сигнала R2 сброса.

Далее описывают сигналы, которые выводят от выходного вывода каждого каскада (каждой схемы с двумя устойчивыми состояниями). Как показано на фиг. 8, сигнал Q состояния, который становится возбуждающим сигналом GOUT(n) сканирования линии GLn затворной шины n-ной строки, выводят от выходного вывода n-го каскада SR(n) всего сдвигового регистра 410. Сигнал Q состояния обеспечивают к (n-2)-му каскаду SR(n-2) в качестве первого сигнала R1 сброса, обеспечивают к (n-3)-му каскаду SR(n-3) в качестве второго сигнала R2 сброса, и обеспечивают к (n+2)-му каскаду SR(n+2) в качестве сигнала S установки.

В вышеупомянутой конфигурации, когда первый сигнал GSP1 запускающего импульса затвора в качестве сигнала S установки обеспечивают к первому каскаду SR1(1) первого сдвигового регистра 411, и когда второй сигнал GSP2 запускающего импульса затвора в качестве сигнала S установки обеспечивают к первому каскаду SR2(1) второго сдвигового регистра 412, первый сигнал GSP1 запускающего импульса затвора последовательно перемещают к каждому каскаду в первом сдвиговом регистре 411, а второй сигнал GSP2 запускающего импульса затвора последовательно перемещают к каждому каскаду во втором сдвиговом регистре 412, основываясь на синхросигналах затвора с первого по четвертый GCK1-GCK4. В соответствии с перемещением этих импульсов сигнал Q состояния, который последовательно выводят из каждого каскада всего сдвигового регистра 410, имеет высокий уровень. Соответственно, как показано на фиг. 9, сигналы GOUT(1) - GOUT(i) сканирования, состояние высокого уровня которых поддерживают в течение приблизительно двух периодов горизонтального сканирования, последовательно обеспечивают на линии GL1-GLi затворной шины в блоке 600 отображения приблизительно каждый период горизонтального сканирования.

В настоящем варианте осуществления первый синхроимпульс CKA соответствует синхросигналу возбуждения линии сигнала сканирования, первый сигнал R1 сброса соответствует сигналу выключения выходного узла, и второй сигнал R2 сброса соответствует сигналу выключения первого узла.

<2.3 Конфигурации схемы с двумя устойчивыми состояниями>

Фиг. 10 является принципиальной электрической схемой, показывающей конфигурацию схемы с двумя устойчивыми состояниями (конфигурацию одного каскада первого сдвигового регистра 411 и второго сдвигового регистра 412) в настоящем варианте осуществления. Как показано на фиг. 10, схема с двумя устойчивыми состояниями включает в себя двенадцать тонкопленочных транзисторов T1-T12 и конденсатор CAP. У схемы с двумя устойчивыми состояниями есть восемь входных выводов 41-48 и два выходных вывода 51, 52 в дополнение к входному выводу для напряжения VSS низкого уровня источника питания. Входному выводу, который принимает сигнал S установки, назначают позиционное обозначение 41, входному выводу, который принимает сигнал CLR очистки, назначают позиционное обозначение 42, входному выводу, который принимает первый синхроимпульс CKA, назначают позиционное обозначение 43, входному выводу, который принимает первый сигнал R1 сброса, назначают позиционное обозначение 44, входному выводу, который принимает третий синхроимпульс CKC, назначают позиционное обозначение 45, входному выводу, который принимает четвертый синхроимпульс CKD, назначают позиционное обозначение 46, входному выводу, который принимает второй синхроимпульс CKB, назначают позиционное обозначение 47, и входному выводу, который принимает второй сигнал R2 сброса, назначают позиционное обозначение 48. Выходному выводу, который выводит сигнал Q состояния в качестве сигнала GOUT сканирования, назначают позиционное обозначение 51, а выходному выводу, который выводит сигнал Q состояния в качестве управляющего сигнала Z другого каскада, назначают позиционное обозначение 52.

Далее описывают зависимости соединений между составными частями в схеме с двумя устойчивыми состояниями. Вывод затвора тонкопленочного транзистора T1, вывод истока тонкопленочного транзистора T2, вывод стока тонкопленочного транзистора T3, вывод стока тонкопленочного транзистора T4, вывод стока тонкопленочного транзистора T5, вывод затвора тонкопленочного транзистора T7 и вывод затвора тонкопленочного транзистора T11 соединяют друг с другом. Область (соединения), в которой эти выводы соединяют друг с другом, для удобства называют «netA» (первым узлом). Вывод затвора тонкопленочного транзистора T5, вывод истока тонкопленочного транзистора T6, вывод стока тонкопленочного транзистора T7 и вывод стока тонкопленочного транзистора T8 соединяют друг с другом. Область (соединения), в которой эти выводы соединяют друг с другом, для удобства называют «netB» (вторым узлом).

Что касается тонкопленочного транзистора T1, вывод затвора соединяют с netA, вывод стока соединяют с входным выводом 43, а вывод истока соединяют с выходным выводом 51. Что касается тонкопленочного транзистора T2, вывод затвора и вывод стока соединяют с входным выводом 41 (т.е. в диодном включении), а вывод истока соединяют с netA. Что касается тонкопленочного транзистора T3, вывод затвора соединяют с входным выводом 42, вывод стока соединяют с netA, а вывод истока соединяют с напряжением VSS источника питания. Что касается тонкопленочного транзистора T4, вывод затвора соединяют с входным выводом 48, вывод стока соединяют с netA, а вывод истока соединяют с напряжением VSS источника питания. Что касается тонкопленочного транзистора T5, вывод затвора соединяют с netB, вывод стока соединяют с netA, а вывод истока соединяют с напряжением VSS источника питания.

Что касается тонкопленочного транзистора T6, вывод затвора и вывод стока соединяют с входным выводом 45 (т.е. в диодном включении), а вывод истока соединяют с netB. Что касается тонкопленочного транзистора T7, вывод затвора соединяют с netA, вывод стока соединяют с netB, а вывод истока соединяют с напряжением VSS источника питания. Что касается тонкопленочного транзистора T8, вывод затвора соединяют с входным выводом 46, вывод стока соединяют с netB, а вывод истока соединяют с напряжением VSS источника питания. Что касается тонкопленочного транзистора T9, вывод затвора соединяют с входным выводом 44, вывод стока соединяют с выходным выводом 51, а вывод истока соединяют с напряжением VSS источника питания. Что касается тонкопленочного транзистора T10, вывод затвора соединяют с входным выводом 47, вывод стока соединяют с входным выводом 51, а вывод истока соединяют с напряжением VSS источника питания.

Что касается тонкопленочного транзистора T11, вывод затвора соединяют с netA, вывод стока соединяют с входным выводом 43, а вывод истока соединяют с выходным выводом 52. Что касается тонкопленочного транзистора T12, вывод затвора соединяют с входным выводом 41, вывод стока соединяют с выходным выводом 52, а вывод истока соединяют с напряжением VSS источника питания. Что касается конденсатора CAP, один конец соединяют с netA, а другой конец соединяют с выходным выводом 51.

Далее описывают функционирование каждого составляющего элемента в данной схеме с двумя устойчивыми состояниями. Тонкопленочный транзистор T1 обеспечивает потенциал первого синхроимпульса CKA к выходному выводу 51, когда потенциал netA имеет высокий уровень. Тонкопленочный транзистор T2 устанавливает потенциал netA в высокий уровень, когда сигнал S установки имеет высокий уровень. Тонкопленочный транзистор T3 устанавливает потенциал netA в низкий уровень, когда сигнал CLR очистки имеет высокий уровень. Тонкопленочный транзистор T4 устанавливает потенциал netA в низкий уровень, когда второй сигнал R2 сброса имеет высокий уровень. Тонкопленочный транзистор T5 устанавливает потенциал netA в низкий уровень, когда потенциал netB имеет высокий уровень. Тонкопленочный транзистор T6 устанавливает потенциал netB в высокий уровень, когда третий синхроимпульс CKC имеет высокий уровень. Тонкопленочный транзистор T7 устанавливает потенциал netB в низкий уровень, когда потенциал netA имеет высокий уровень. Тонкопленочный транзистор T8 устанавливает потенциал netB в низкий уровень, когда четвертый синхроимпульс CKD имеет высокий уровень. Тонкопленочный транзистор T9 устанавливает потенциал выходного вывода 51 в низкий уровень, когда первый сигнал R1 сброса имеет высокий уровень. Тонкопленочный транзистор T10 устанавливает потенциал выходного вывода 51 в низкий уровень, когда второй синхроимпульс CKB имеет высокий уровень. Тонкопленочный транзистор T11 обеспечивает потенциал первого синхроимпульса CKA к выходному выводу 52, когда потенциал netA имеет высокий уровень. Тонкопленочный транзистор T12 устанавливает потенциал выходного вывода 52 в низкий уровень, когда сигнал S установки имеет высокий уровень. Конденсатор CAP функционирует в качестве компенсирующего конденсатора для поддержания потенциала netA на высоком уровне в течение периода, когда линия затворной шины, соединенная с этой схемой с двумя устойчивыми состояниями, находится в выбранном состоянии.

В настоящем варианте осуществления тонкопленочный транзистор T1 реализует переключающий элемент управления выходом, а тонкопленочный транзистор T5 реализует переключающий элемент управления первым узлом. Тонкопленочный транзистор T2 реализует блок включения первого узла, тонкопленочный транзистор T4 реализует блок выключения первого узла, тонкопленочный транзистор T9 реализует блок выключения выходного узла, а тонкопленочные транзисторы T6-T8 реализуют блок управления вторым узлом.

<2.4 Работа схемы с двумя устойчивыми состояниями>

Работа схемы с двумя устойчивыми состояниями в настоящем варианте осуществления описана со ссылкой на фиг. 10 и 11. Во время работы жидкокристаллического устройства отображения первый синхроимпульс CKA, второй синхроимпульс CKB, третий синхроимпульс CKC и четвертый синхроимпульс CKD, временные диаграммы которых показаны на фиг. 11, обеспечивают к схеме с двумя устойчивыми состояниями. Сигнал CLR очистки переходит в высокий уровень в течение предопределенного периода каждый период кадра, и таким образом потенциал netA устанавливают в низкий уровень каждый период кадра во всех схемах с двумя устойчивыми состояниями.

В течение периода до момента времени t0 потенциал netA и потенциал сигнала Q состояния (потенциалы выходных выводов 51, 52) имеют низкий уровень. В течение периода до момента времени t0, когда уровень третьего синхроимпульса CKC меняется с низкого уровня на высокий уровень, уровень потенциала netB меняется с низкого уровня на высокий уровень, и когда уровень четвертого синхроимпульса CKD меняется с низкого уровня на высокий уровень, уровень потенциала netB меняется с высокого уровня на низкий уровень. Таким образом, каждый предопределенный период потенциал netB переходит на высокий уровень, и тонкопленочный транзистор T5 переходит в состояние «включено», и поэтому, в течение периода до момента времени t0 потенциал netA будет поддерживаться на низком уровне.

Достигая момента времени t0, уровень сигнала S установки меняется с низкого уровня на высокий уровень. Поскольку тонкопленочный транзистор T2 находится в диодном включении, как показано на фиг. 10, тонкопленочный транзистор T2 переходит в состояние «включено» с помощью сигнала S установки, который переходит на высокий уровень, и конденсатор CAP заряжается. Соответственно, уровень потенциала netA меняется с низкого уровня на высокий уровень, и тонкопленочные транзисторы T1, T11 переходят в состояние «включено». Достигая момента времени t1, уровень сигнала S установки меняется с высокого уровня на низкий уровень. Следовательно, тонкопленочный транзистор T2 переходит в состояние «выключено». В это время, из-за того, что потенциал netA поддерживают с помощью конденсатора CAP, потенциал netA не меняется из-за перехода тонкопленочного транзистора T2 в состояние «выключено».