ПЕРЕКРЕСТНЫЕ ССЫЛКИ НА РОДСТВЕННЫЕ ЗАЯВКИ

[0001] По данной заявке испрашивается приоритет китайской патентной заявки 201710687764.6 поданной 11 августа 2017 г., раскрытие которой в полном объеме включено в настоящее описание изобретения посредством ссылки.

ОБЛАСТЬ ТЕХНИКИ, К КОТОРОЙ ОТНОСИТСЯ ИЗОБРЕТЕНИЕ

[0002] Настоящее изобретение относится к области связи и, в частности, к способу и устройству кодирования данных, носителю данных и процессору.

УРОВЕНЬ ТЕХНИКИ

[0003] Для решения проблемы, присущей уровню техники, состоящей в снижении эффективности кодирования или декодирования кода LDPC в процессе кодирования с квазициклической проверкой на четность низкой плотности (LDPC), когда появляется больше битов заполнения, предусмотрено правило построения таблицы размера транспортного блока (TBS), чтобы при осуществлении кодирования с LDPC возникало как можно меньше битов заполнения или вообще не возникало битов заполнения. Для решения проблемы узких мест, обусловленной тем, что число кодовых блоков в каждой группе кодовых блоков в транспортном блоке может различаться, предусмотрен способ прогнозирования Kmax в способе разбиения кодового блока, благодаря чему, число кодовых блоков в каждой группе кодовых блоков позволяет избегать снижения общей производительности, обусловленной, когда некоторые группы кодовых блоков имеют больше кодовых блоков; и для решения проблемы низкой производительности кодирования с квазициклической LDPC в модуляции высокого порядка или канала с замираниями, производительность кодирования с квазициклической LDPC повышается согласно способу перемежения кодовых слов.

[0004] В фактической системе связи, поскольку число битов транспортного блока, которые фактически необходимо передавать, не обязательно равно битовой длине системы, поддерживаемой базисной матрицей кодирования с квазициклической LDPC, разбиение кодового блока необходимо осуществлять на транспортном блоке и необходимо заполнять биты. Однако разбиение кодового блока, осуществляемое на транспортном блоке, и биты заполнения порождают проблему неустойчивости передачи, например, снижения скорости кодирования и декодирования, высокого энергопотребления и влияния на устойчивость передачи данных.

[0005] В уровне техники не существует эффективного решения проблемы неустойчивой передачи после осуществления кодирования с квазициклической LDPC в отношении данных, подлежащих передаче.

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

[0006] Варианты осуществления настоящего изобретения предусматривают способ и устройство кодирования данных, носитель данных и процессор, для решения по меньшей мере проблемы, присущей уровню техники, неустойчивой передачи после осуществления кодирования с квазициклической LDPC в отношении данных, подлежащих передаче.

[0007] Согласно варианту осуществления настоящего изобретения, предусмотрен способ кодирования данных. Способ включает в себя: осуществление кодирования с квазициклической LDPC в отношении битовой последовательности информационного пакета для получения последовательности кодовых слов LDPC, и определение размера одномерного кольцевого буфера конечной длины согласно последовательности кодовых слов LDPC; выбор значения версии избыточности из множества заранее определенных значений версии избыточности, и определение начальной позиции для считывания битовой последовательности, подлежащей передаче, в одномерном кольцевом буфере конечной длины согласно выбранному значению версии избыточности и заранее заданному параметру, где заранее заданный параметр включает в себя по меньшей мере один из: размера поднятия, полного числа столбцов матрицы базисного графа, полного числа строк матрицы базисного графа, числа системных столбцов матрицы базисного графа или длины битовой последовательности информационного пакета; и последовательное считывание битов данных с конкретной длиной от начальной позиции для формирования битовой последовательности, подлежащей передаче, и отправку битовой последовательности, подлежащей передаче.

[0008] Согласно другому варианту осуществления настоящего изобретения, дополнительно предусмотрено устройство кодирования данных. Устройство включает в себя: модуль получения, выполненный с возможностью получения данных, подлежащих отправке; модуль перемежения, выполненный с возможностью осуществления кодирования с квазициклической LDPC в отношении данных, подлежащих отправке, для получения последовательности кодовых слов LDPC, и перемежения последовательности кодовых слов LDPC для получения перемеженной последовательности кодовых слов LDPC; модуль выбора, выполненный с возможностью осуществления циклического выбора битов на перемеженной последовательности кодовых слов LDPC от начальной позиции для получения согласованной по частоте последовательности кодовых слов, где начальная позиция определяется согласно заранее определенному параметру, где заранее определенный параметр включает в себя по меньшей мере один из: версии избыточности, размера поднятия, полного числа столбцов матрицы базисного графа, полного числа строк матрицы базисного графа, числа системных столбцов матрицы базисного графа или длины битовой последовательности информационного пакета; и модуль отправки, выполненный с возможностью отправки согласованной по частоте последовательности кодовых слов.

[0009] Согласно другому варианту осуществления настоящего изобретения, дополнительно предусмотрен носитель данных. На носителе данных хранятся программы, которые, при выполнении, выполняют вышеупомянутый способ кодирования данных.

[0010] Согласно другому варианту осуществления настоящего изобретения, дополнительно предусмотрен процессор. Процессор используется для выполнения программы, которая, при выполнении, выполняют вышеупомянутый способ кодирования данных в необязательных вышеописанных вариантах осуществления.

[0011] Согласно настоящее изобретение, получаются данные, подлежащие отправке; кодирование с квазициклической LDPC осуществляется в отношении данных, подлежащих отправке, для получения последовательности кодовых слов LDPC, и последовательность кодовых слов LDPC перемежается для получения перемеженной последовательности кодовых слов LDPC; циклический выбор битов осуществляется на перемеженной последовательности кодовых слов LDPC от начальной позиции для получения согласованной по частоте последовательности кодовых слов, где начальная позиция определяется согласно заранее определенному параметру; и отправляется согласованная по частоте последовательность кодовых слов. Предложенное выше решение устраняет присущую уровню техники проблему неустойчивой передачи после осуществления кодирования с квазициклической LDPC в отношении данных, подлежащих передаче, и позволяет добиться устойчивой передачи после кодирования с квазициклической LDPC.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

[0012] Описанные здесь чертежи используются для обеспечения дополнительного понимания настоящего изобретения и образуют часть настоящей заявки на изобретение. Иллюстративные варианты осуществления и их описания в настоящем изобретении используются для объяснения настоящего изобретения, но не для ограничения настоящего изобретения тем или иным образом. На чертежах:

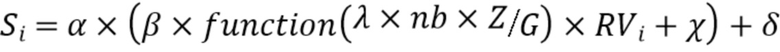

[0013] фиг. 1 - блок-схема операций способа кодирования данных согласно варианту осуществления настоящего изобретения; и

[0014] фиг. 2 - блок-схема операций способа обработки данных путем кодирования с LDPC согласно предпочтительному варианту осуществления настоящего изобретения.

ПОДРОБНОЕ ОПИСАНИЕ

[0015] Варианты осуществления настоящего изобретения предусматривают сеть мобильной связи (которая включает в себя, но без ограничения, сеть мобильной связи 5G). Сетевая архитектура сети может включать в себя устройство на стороне сети (например, базовую станцию) и терминал. Согласно варианту осуществления предусмотрен способ передачи информации, исполняемый в сетевой архитектуре. Следует отметить, что среда выполнения способа передачи информации, предусмотренного вариантами осуществления настоящего изобретения, не ограничивается сетевой архитектурой.

[0016] Уровень техники способа кодирования в цифровой системе связи будет кратко описан до подробного описания вариантов осуществления настоящего изобретения.

[0017] Цифровая система связи в уровне техники в общем случае включает в себя три части: передающую сторону, канал и принимающую сторону. Передающая сторона может осуществлять кодирование канала в отношении информационной последовательности для получения кодированного кодового слова, перемежать кодированное кодовое слово, и отображать перемеженные биты в символы модуляции, и затем обрабатывать и передавать символы модуляции согласно информации о канале связи. На канале, характеристика конкретного канала вследствие таких факторов, как многолучевое распространение, и перемещение приводит к искаженной передаче данных, и шум и помеха будут дополнительно ухудшать передачу данных. Принимающая сторона принимает данные символа модуляции после прохождения по каналу, где данные символа модуляции уже искажены в этот момент, и необходимо осуществлять конкретную обработку для восстановления исходной информационной последовательности.

[0018] Согласно способу кодирования, используемому передающей стороной для кодирования информационной последовательности, принимающая сторона может осуществлять соответствующую обработку принятых данных для надежного восстановления исходной информационной последовательности. В общем случае, способ кодирования базируется на кодировании с прямой коррекцией ошибок (FEC). Кодирование FEC добавляет некоторую избыточную информацию в информационную последовательность, и принимающая сторона может надежно восстанавливать исходную информационную последовательность с помощью избыточной информации.

[0019] Некоторое общее кодирование FEC включает в себя: сверточный код, турбо-код и код LDPC. В процессе кодирования FEC, кодирование FEC осуществляется в отношении информационной последовательности с числом k битов для получения FEC-кодированного кодового слова с n битами (включающими в себя n-k битов избыточности), и скорость кодирования FEC равна k/n. Код LDPC является линейным блочным кодом, заданным с помощью очень редкой матрицы проверки на четность или двустороннего графа. Разреженность проверочной матрицы кода LDPC помогает достичь кодирования и декодирования низкой сложности, что делает LDPC более практической. Различные практики и теории доказывают, что код LDPC имеет наилучшую производительность кодирования канала, очень близкую к пределу Шэннона в условиях аддитивного белого гауссова шума (AWGN). В матрице проверки на четность кода LDPC, каждая строка является кодом с проверкой на четность. Если элементное значение позиции некоторого индекса равно 1 в каждой строке, это означает, что бит в этой позиции участвует в коде с проверкой на четность; если элементное значение равно 0, это означает, что бит в этой позиции не участвует в коде с проверкой на четность.

[0020] Благодаря структурированным характеристикам, код квазициклической LDPC приобрел популярность. Например, код квазициклической LDPC широко применяется к IEEE802.11ac, IEEE802.11ad, IEEE802.11aj, IEEE802.16e, IEEE802.11n, СВЧ-связи и оптоволоконной связи, и применяется как схема кодирования канала данных в мобильной связи 5-го поколения (5G). Матрица H проверки на четность кода квазициклической LDPC является матрицей, имеющей M × Z строк и N× Z столбцов, которая состоит из M ×N подматриц. Каждая подматрица является той или иной степенью базисной матрицы перестановок размером Z × Z, то есть каждая подматрица получается циклическим сдвигом нескольких значений единичной матрицы размером Z × Z.

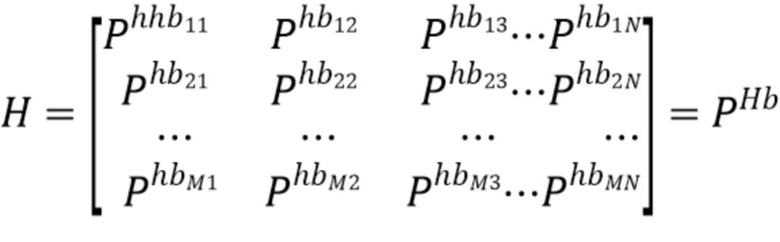

[0021] Для упрощения описания циклического сдвига единичной матрицы с математической точки зрения, матрица проверки на четность кода квазициклической LDPC можно записать в виде следующей математической формулы.

[0022]

[0023] Если  ,

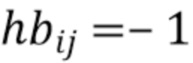

,  - нулевая матрица размером Z × Z; в противном случае, стандартная матрица P перестановок в неотрицательной целочисленной степени. Стандартная матрица P перестановок записывается следующим образом.

- нулевая матрица размером Z × Z; в противном случае, стандартная матрица P перестановок в неотрицательной целочисленной степени. Стандартная матрица P перестановок записывается следующим образом.

[0024]

[0025] Согласно этому определению, Z и степень  могут однозначно идентифицировать каждую блочную матрицу. Если некоторая блочная матрица является нулевой матрицей, блочная матрица может быть представлена значением “−1” или нуль или в других формах. Если блочная матрица получена s-кратным циклическим сдвигом единичной матрицы, блочная матрица равна s. Все

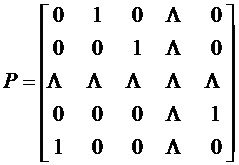

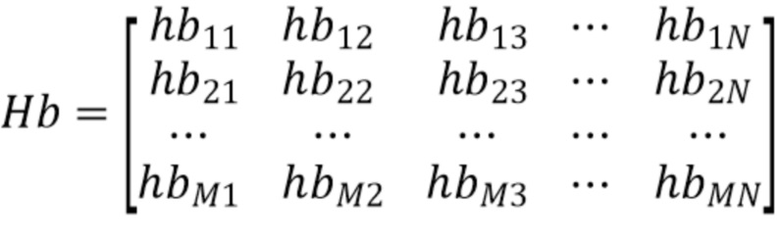

могут однозначно идентифицировать каждую блочную матрицу. Если некоторая блочная матрица является нулевой матрицей, блочная матрица может быть представлена значением “−1” или нуль или в других формах. Если блочная матрица получена s-кратным циклическим сдвигом единичной матрицы, блочная матрица равна s. Все  могут образовывать базисную матрицу Hb кода квазициклической LDPC, которую можно записать в следующем виде.

могут образовывать базисную матрицу Hb кода квазициклической LDPC, которую можно записать в следующем виде.

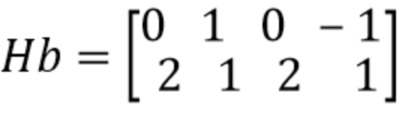

[0026]

[0027] Таким образом, базисная матрица Hb включает в себя два типа элементов: элемент, указывающий нулевую квадратную матрицу, и элемент, указывающий значение циклического сдвига единичной матрицы, которое в общем случае представлено целым числом в диапазоне от 0 до (Z −1). Базисная матрица Hb может именоваться базисной проверочной матрицей или базисной матрицей проверки на четность или матрицей проверки на четность. В базисной матрице Hb, если элемент, указывающий нулевую матрицу, заменяется элементом “0”, и другие элементы заменяются элементами “1”, можно получить матрицу базисного графа или матрицу шаблона кодирования с квазициклической LDPC. Матрицу базисного графа также можно описать в форме таблицы. Например, пары индексов строк и столбцов используются для указания позиций “1” матрицы базисного графа или позиций элементов, указывающих значение циклического сдвига единичной матрицы в базисной матрице. Таким образом, базисная матрица кода квазициклической LDPC может определяться согласно матрице шаблона кода квазициклической LDPC и группе значений сдвига (или коэффициентов). Размер Z базисной матрицы перестановок или нулевой квадратной матрицы может задаваться как размер сдвига/размер поднятия или коэффициент расширения или размер подматрицы.

[0028] Таким образом, структурированный код LDPC может однозначно определяться базисной проверочной матрицей Hb и размером Z поднятия. Например, базисная матрица Hb (из 2 строк и 4 столбцов) соответствует размеру Z поднятия 4 и записывается следующим образом.

[0029]

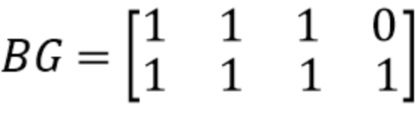

[0030] Матрица шаблона, соответствующая базисной матрице Hb, записывается следующим образом.

[0031]

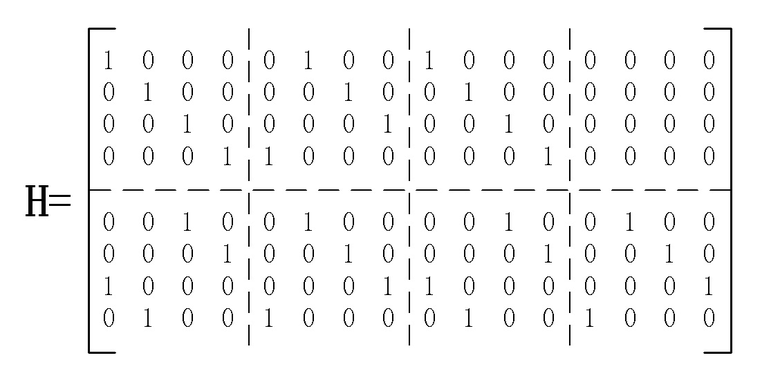

[0032] Матрица H проверки на четность, полученная согласно базисной матрице Hb и размеру Z поднятия, записывается следующим образом.

[0033]

[0034] Кодирование с квазициклической LDPC может непосредственно осуществляться согласно матрице проверки на четность, определяемой согласно базисной матрице Hb и размеру Z поднятия. Согласно определению кода LDPC, выполняется H×C=0; H включает в себя [Hs Hp], где Hs - матрица системной части столбцов матрицы проверки на четность, и Hp - матрица проверочной части столбцов матрицы проверки на четность; C может включать в себя [Cs Cp], где Cs - системная битовая последовательность (бит информации, известный бит) кода LDPC, и Cp - проверочная битовая последовательность (неизвестный бит) кода LDPC. Процесс кодирования с LDPC является процессом вычисления проверочной битовой последовательности. Таким образом, Hs×Cs=Hp×Cp, и затем можно вычислять проверочную битовую последовательность Cp, то есть Cp=inv(Hp)×Hs×Cs, где формула inv(x) представляет двоичную инверсию матрицы x. Таким образом, матрица проверочных столбцов матрицы проверки на четность должна быть квадратной матрицей и двоично обратимой, чтобы последовательность, кодированная с квазициклической LDPC, представляла собой [Cs Cp]. Конечно, последовательность, кодированную с квазициклической LDPC, также можно вычислять посредством циклического сдвига каждого Z-битового блока.

[0035] В процессе передачи данных, заявитель установил, что при осуществлении разбиения кодового блока на транспортном блоке и заполнении битов, для кода LDPC, биты заполнения используются для помощи в кодировании или декодировании и фактически не участвуют в передаче, но в процессе кодирования и декодирования, если появляется больше битов заполнения, кодер или декодер выполняет некоторые бесполезные операции, что приводит к снижению скорости кодирования и декодирования и повышает энергопотребление. При большой длине транспортного блока, число кодовых блоков в этот момент велико. Для облегчения обратной связи и повышения эффективности обработки, все кодовые блоки LDPC должны делиться на множество групп кодовых блоков, где каждая группа кодовых блоков включает в себя несколько кодовых блоков LDPC, и принимается обратная связь в виде квитирования или отрицательного квитирования (ACK/NACK), и повторная передача данных осуществляется на принимающей стороне группами кодовых блоков. Если конструкция групп кодовых блоков не учитывается в процессе разбиения кодового блока, число кодовых блоков в каждой группе кодовых блоков будет различаться при делении кодовых блоков на группы кодовых блоков, что буде приводить к появлению узких мест и влиять на устойчивость передачи данных. Поскольку кодирование с квазициклической LDPC имеет некоторые структурированные характеристики, в некоторых модуляциях высокого порядка или каналах с замиранием, код LDPC может сталкиваться с некоторыми проблемами, связанными с низкой производительностью. Таким образом, биты кодового слова необходимо перемежать для рандомизации импульсного шума и, таким образом, повышения производительности кодирования с квазициклической LDPC в условиях импульсного шума.

[0036] Вариант осуществления 1

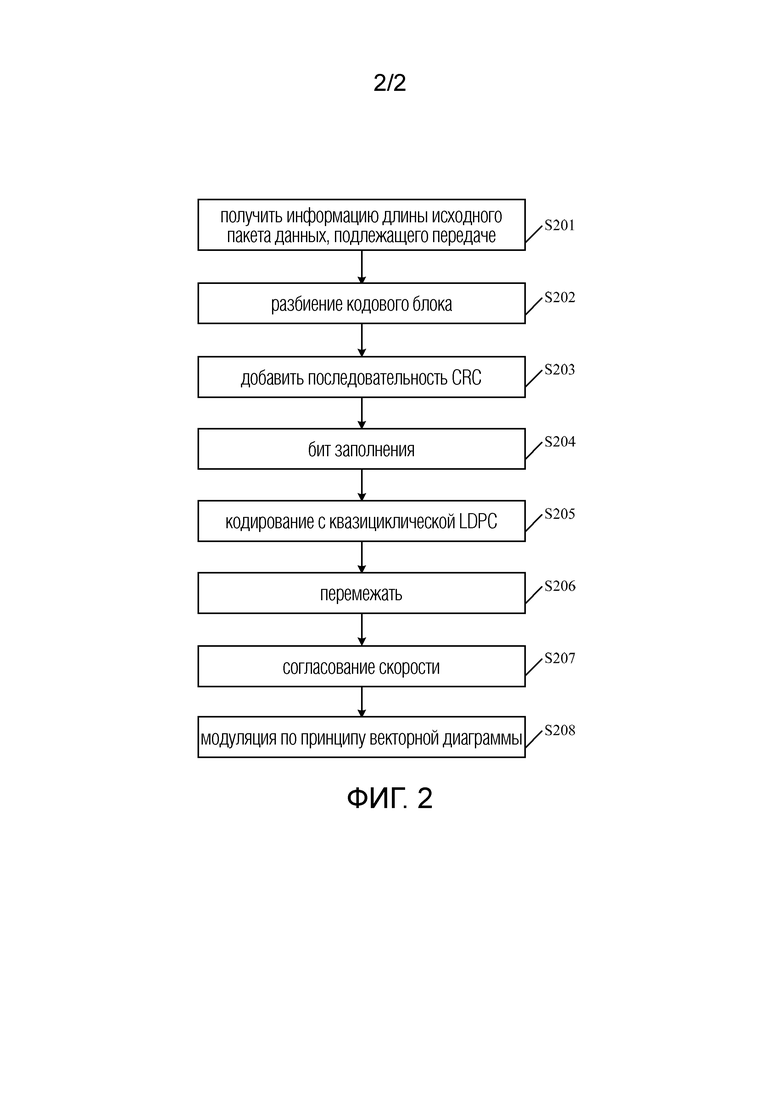

[0037] Вариант осуществления предусматривает способ кодирования данных. На фиг. 1 показана блок-схема операций способа кодирования данных согласно варианту осуществления настоящего изобретения. Как показано на фиг. 1, способ включает в себя описанные ниже этапы.

[0038] На этапе S102, кодирование с квазициклической LDPC осуществляется в отношении битовой последовательности информационного пакета для получения последовательности кодовых слов LDPC, и размер одномерного кольцевого буфера конечной длины определяется согласно последовательности кодовых слов LDPC.

[0039] На этапе S104, значение версии избыточности выбирается из множества заранее определенных значений версии избыточности, и начальная позиция для считывания битовой последовательности, подлежащей передаче, в одномерном кольцевом буфере конечной длины определяется согласно выбранному значению версии избыточности и заранее заданному параметру, где заранее заданный параметр включает в себя по меньшей мере один из: размера поднятия, полного числа столбцов матрицы базисного графа, полного числа строк матрицы базисного графа, числа системных столбцов матрицы базисного графа или длины битовой последовательности информационного пакета.

[0040] На этапе S106, биты данных с конкретной длиной последовательно считываются от начальной позиции для формирования битовой последовательности, подлежащей передаче, и битовая последовательность, подлежащая передаче, отправляется.

[0041] Посредством вышеописанных этапов, кодирование с квазициклической LDPC осуществляется в отношении битовой последовательности информационного пакета для получения последовательности кодовых слов LDPC, и размер одномерного кольцевого буфера конечной длины определяется согласно последовательности кодовых слов LDPC; значение версии избыточности выбирается из множества заранее определенных значений версии избыточности, и начальная позиция для считывания битовой последовательности, подлежащей передаче, в одномерном кольцевом буфере конечной длины определяется согласно выбранному значению версии избыточности и заранее заданному параметру, где заранее заданный параметр включает в себя по меньшей мере один из: размера поднятия, полного числа столбцов матрицы базисного графа, полного числа строк матрицы базисного графа, числа системных столбцов матрицы базисного графа или длины битовой последовательности информационного пакета; и биты данных с конкретной длиной последовательно считываются от начальной позиции для формирования битовой последовательности, подлежащей передаче, и битовая последовательность, подлежащая передаче, отправляется. Предложенное выше решение устраняет присущую уровню техники проблему неустойчивой передачи после осуществления кодирования с квазициклической LDPC в отношении данных, подлежащих передаче, и позволяет добиться устойчивой передачи после кодирования с квазициклической LDPC.

[0042] В одном варианте осуществления, вышеописанные этапы могут, но без ограничения, выполняться базовой станцией или терминалом.

[0043] В одном варианте осуществления, последовательность кодовых слов LDPC перемежается для получения перемеженной последовательности кодовых слов LDPC, и этот этап включает в себя: осуществление перемежения блоков в отношении последовательности кодовых слов LDPC, где число строк матрицы перемежения определяется согласно параметру кодирования с квазициклической LDPC, и параметр кодирования с квазициклической LDPC включает в себя по меньшей мере один из: размера поднятия, полного числа столбцов матрицы базисного графа, полного числа строк матрицы базисного графа и числа системных столбцов матрицы базисного графа. Матрица перемежения перемежается в соответствии с тем, как данные в матрице вводятся вдоль столбца и выводятся вдоль столбца.

[0044] В одном варианте осуществления, число строк матрицы перемежения равно положительному целочисленному коэффициенту размера поднятия квазициклической LDPC, или равно положительному целому числу, кратному размеру поднятия кодирования с квазициклической LDPC.

[0045] В одном варианте осуществления, число строк матрицы перемежения равно положительному целочисленному коэффициенту полного числа столбцов матрицы базисного графа кодирования с квазициклической LDPC, или равно положительному целому числу, кратному полного числа столбцов матрицы базисного графа кодирования с квазициклической LDPC.

[0046] В одном варианте осуществления, способ перемежения дополнительно включает в себя: осуществление вывода, соответственно, согласно заранее определенному порядку столбцов для получения перемеженной последовательности кодовых слов.

[0047] В одном варианте осуществления, способ перемежения внутри столбца определяется согласно порядку модуляции.

[0048] В необязательном порядке, при условии, что порядок модуляции больше M0, выполняется способ перемежения внутри столбца, где M0 - целое число, большее 1.

[0049] В одном варианте осуществления, начальная позиция определяется согласно версии избыточности, размеру поднятия и полному числу столбцов матрицы базисного графа.

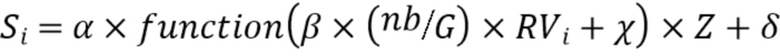

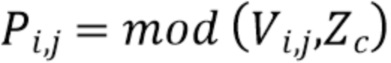

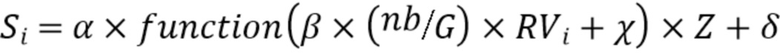

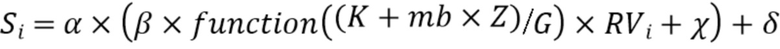

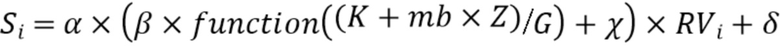

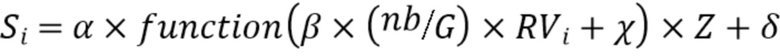

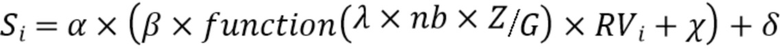

[0050] В одном варианте осуществления, начальная позиция, соответствующая версии избыточности, равной  , вычисляется по следующей формуле:

, вычисляется по следующей формуле:

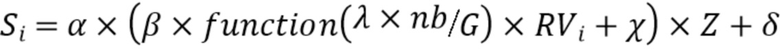

[0051] первая формула:  ;

;

[0052] причем в первой формуле, nb - полное число столбцов матрицы базисного графа, Z - размер поднятия, α - положительное целое число, G - действительное число, большее 0, β - положительное действительное число, χ - неотрицательное действительное число, и δ - целое число, где function(x) представляет округление действительного числа x в сторону увеличения, в сторону уменьшения или до ближайшего целого числа;

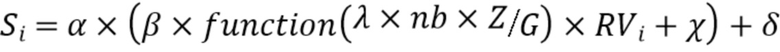

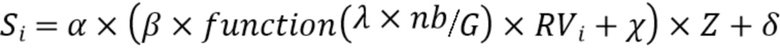

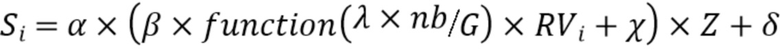

[0053] или второй формуле:  ;

;

[0054] причем во второй формуле, nb - полное число столбцов матрицы базисного графа, Z - размер поднятия, α - положительное целое число, G - действительное число, большее 0, β - положительное целое число, λ - положительное действительное число, χ - неотрицательное действительное число, и δ - целое число, где function(x) представляет округление действительного числа x в сторону увеличения, в сторону уменьшения или до ближайшего целого числа;

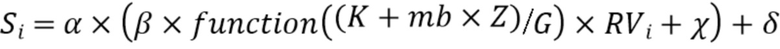

[0055] или третьей формуле:  ;

;

[0056] причем в третьей формуле, nb - полное число столбцов матрицы базисного графа, Z - размер поднятия, G - действительное число, большее 0, α - положительное целое число, β - положительное целое число, λ - положительное действительное число, χ - неотрицательное действительное число, и δ - целое число, где function(x) представляет округление действительного числа x в сторону увеличения, в сторону уменьшения или до ближайшего целого числа.

[0057] В одном варианте осуществления, начальная позиция определяется согласно версии избыточности, размеру поднятия, полному числу столбцов матрицы базисного графа и длине битовой последовательности информационного пакета.

[0058] В одном варианте осуществления, начальная позиция, соответствующая версии избыточности, равной  вычисляется по одной из следующих формул:

вычисляется по одной из следующих формул:

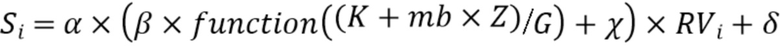

[0059]  ; и

; и

[0060]  ;

;

[0061] причем в двух вышеприведенных формулах, K - длина битовой последовательности информационного пакета, Z - размер поднятия, G - действительное число, большее 0, α - положительное целое число, β - положительное целое число, λ - положительное действительное число, χ - неотрицательное действительное число, и δ - целое число, где function(x) представляет округление действительного числа x в сторону увеличения, в сторону уменьшения или до ближайшего целого числа.

[0062] В одном варианте осуществления, этап, на котором последовательность кодовых слов LDPC перемежается для получения перемеженной последовательности кодовых слов LDPC, включает в себя: перемежение всех битов от S0-го бита до S1-го бита в последовательности кодовых слов LDPC, где S0 и S1 - положительные целые числа, и S1 больше S0.

[0063] В одном варианте осуществления, этап, на котором все биты от S0-го бита до S1-го бита в последовательности кодовых слов LDPC перемежаются, включает в себя: осуществление перемежения блоков для всех битов от S0-го бита до S1-го бита в последовательности кодовых слов LDPC согласно матрице перемежения, где число столбцов блочной матрицы перемежения равно Z0, и Z0 определяется параметром кодирования с квазициклической LDPC, где параметр кодирования с квазициклической LDPC включает в себя по меньшей мере один из: размера поднятия, полного числа столбцов матрицы базисного графа, полного числа строк матрицы базисного графа, числа системных столбцов матрицы базисного графа и длины битовой последовательности информационного пакета.

[0064] В одном варианте осуществления, Z0 равно положительному целочисленному коэффициенту размера поднятия кодирования с LDPC.

[0065] В одном варианте осуществления, Z0 равно Z, Z - размер поднятия кодирования с LDPC, S0 равно 2×Z, и S1 равно E ×Z−1, где E - целое число, большее 2.

[0066] В одном варианте осуществления, E равно kb, kb+1, kb+2, kb+3 или kb+4, где kb - число системных столбцов матрицы базисного графа кодирования с LDPC.

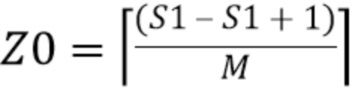

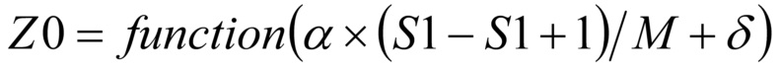

[0067] В одном варианте осуществления, Z0 определяется следующими параметрами: S0, S1 и порядком модуляции, где порядок модуляции представляет собой число битов, переносимых каждым символом модуляции.

[0068] В одном варианте осуществления, Z0 вычисляется по следующей формуле:  , где M - порядок модуляции и положительное целое число.

, где M - порядок модуляции и положительное целое число.

[0069] В одном варианте осуществления, значение S1 определяется по меньшей мере одним из следующих параметров: длины битовой последовательности информационного пакета, полученной после осуществления разбиения кодового блока в отношении данных, подлежащих отправке, и длины битовой последовательности, подлежащей передаче.

[0070] В одном варианте осуществления, когда скорость R кодирования с LDPC меньше или равна R0, все биты от S0-го бита до S1-го бита в последовательности кодовых слов LDPC перемежаются согласно матрице перемежения, где R0 - действительное число, большее или равное 3/4 и меньшее 1, и скорость R кодирования с LDPC равна частному от деления длины битовой последовательности информационного пакета на длину битовой последовательности, подлежащей передаче.

[0071] Настоящее изобретение будет подробно описано ниже в связи с предпочтительными вариантами осуществления.

[0072] Предпочтительный вариант осуществления 1

[0073] Вариант осуществления предусматривает способ обработки данных путем кодирования с квазициклической LDPC, который можно применять к системе связи на основе новой технологии радиодоступа (NR). Способ, предусмотренный в этом необязательном варианте осуществления, можно применять к системе мобильной связи "проект долгосрочного развития систем связи" (LTE) или перспективной системе мобильной связи 5G или другим беспроводным или проводным системам связи, и направление передачи данных является направлением, в котором базовая станция отправляет данные мобильному пользователю (передача служебных данных по нисходящей линии связи), или направление передачи данных является направлением, в котором мобильный пользователь отправляет данные на базовую станцию (передача служебных данных по восходящей линии связи). Мобильный пользователь включает в себя: мобильное устройство, терминал доступа, пользовательский терминал, пользовательскую станцию, пользовательский блок, мобильную станцию, удаленную станцию, удаленный терминал, пользовательский агент, пользовательское оборудование, пользовательское устройство или устройства под другими названиями. Базовая станция включает в себя: точку доступа (AP), которая может именоваться узлом B, контроллером радиосети (RNC), усовершенствованным узлом B (eNB), контроллером базовых станций (BSC), базовой приемопередающей станцией (BTS), базовой станцией (BS), функцией приемопередатчика (TF), радио-маршрутизатором, радио-приемопередатчиком, блоком основного обслуживания, блоком расширенного обслуживания, базовой станцией радиосвязи (RBS), или другие устройства под другими названиями.

[0074] Согласно одному аспекту этого необязательного варианта осуществления, этот необязательный вариант осуществления предусматривает способ обработки данных путем кодирования с квазициклической LDPC, который можно применять к сценарию улучшенной широкополосной мобильной связи (enhanced Mobile Broadband) (eMBB), сценарию сверхнадежной связи с низкой задержкой (Ultra-Reliable and Low Latency Communications) (URLLC) или сценарию массовой связи машинного типа (massive Machine Type Communications) (mMTC) в новой технологии радиодоступа (новой RAT).

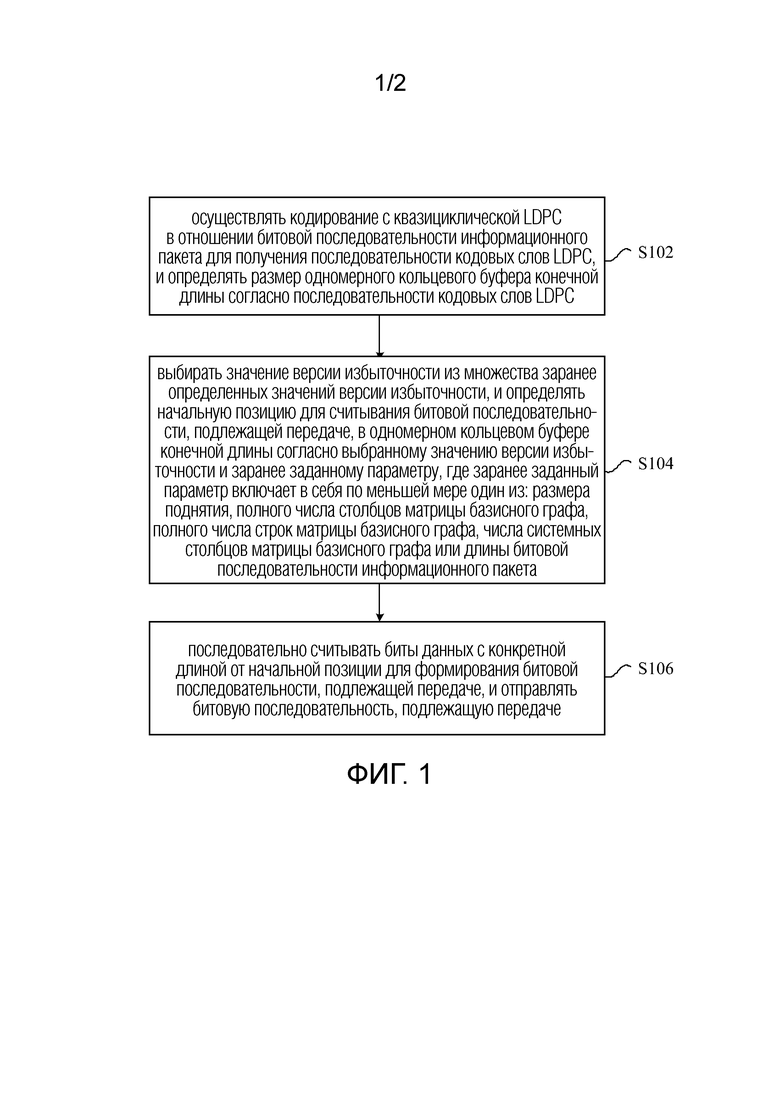

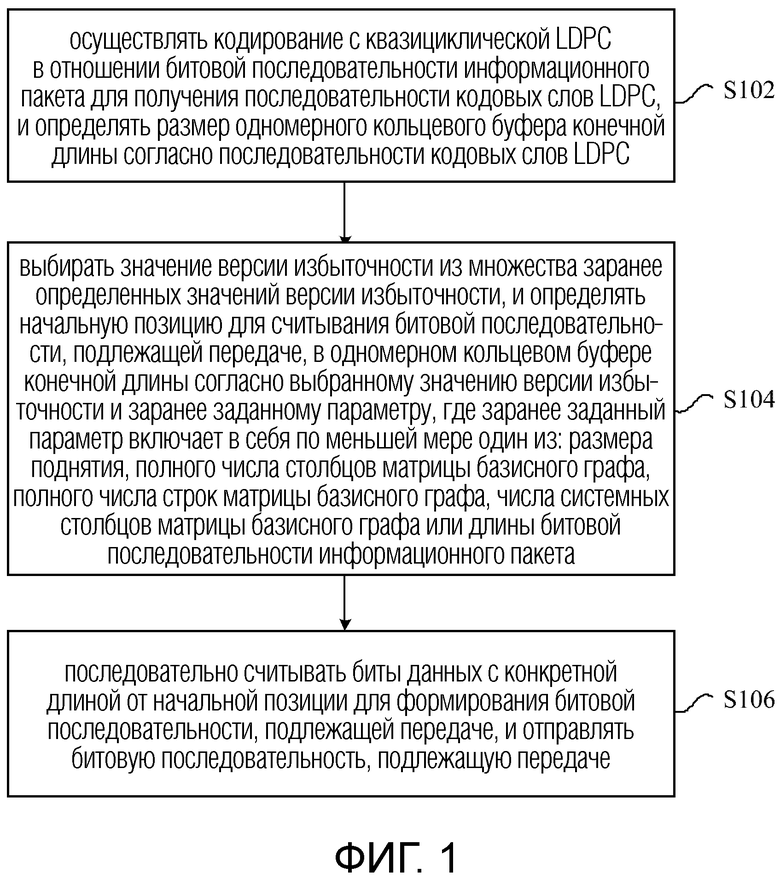

[0075] На фиг. 2 показана блок-схема операций способа обработки данных путем кодирования с LDPC согласно предпочтительному варианту осуществления настоящего изобретения. Как показано на фиг. 2, способ включает в себя описанные ниже этапы.

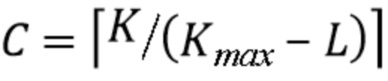

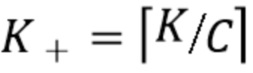

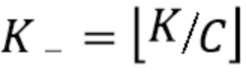

[0076] На этапе S201 получается информация длины исходного пакета данных, подлежащего передаче, и длина исходного пакета данных, подлежащего передаче, который нужно отправить в данный момент (также известная как TBS), определяется из таблицы TBS согласно информации управления, где информацию управления можно получить из информации управления нисходящей линии связи или восходящей линии связи или другой системной информации.

[0077] На этапе S202 осуществляется разбиение кодового блока. Исходный пакет данных, подлежащий передаче, делится согласно длине самого длинного информационного блока,  , где число битовых последовательностей информационного пакета, полученных после разделения, равно

, где число битовых последовательностей информационного пакета, полученных после разделения, равно  , и длина битовой последовательности информационного пакета, полученной после разбиения кодового блока, включает в себя

, и длина битовой последовательности информационного пакета, полученной после разбиения кодового блока, включает в себя  и

и  , где K - длина битовой последовательности информационного пакета и положительное целое число,

, где K - длина битовой последовательности информационного пакета и положительное целое число,  - положительное целое число, и L - длина последовательности циклической проверки избыточности (CRC), добавленной в каждую битовую последовательность информационного пакета.

- положительное целое число, и L - длина последовательности циклической проверки избыточности (CRC), добавленной в каждую битовую последовательность информационного пакета.

[0078] На этапе S203 добавляется последовательность CRC. Последовательность CRC с числом L битов добавляется в каждый блок битов информации, полученный после разбиения кодового блока, где L - целое число, большее 0.

[0079] На этапе S204 бит заполняется. Подбит заполняется в блоке битов информации, в который добавлена последовательность CRC, где подбит используется только для помощи в кодировании и не участвует в передаче.

[0080] На этапе S205 осуществляется кодирование с квазициклической LDPC. Размер поднятия, используемый кодированием с LDPC определяется согласно длине каждой битовой последовательности информационного пакета, полученной после разбиения кодового блока, проверочная матрица кодирования с LDPC определяется и вычисляется согласно полученной информации размера поднятия, и кодирование с квазициклической LDPC осуществляется на каждой битовой последовательности информационного пакета согласно проверочной матрице и размеру поднятия кодирования с LDPC для получения последовательности кодовых слов LDPC.

[0081] Матрица базисного графа кодирования с квазициклической LDPC включает в себя два типа матриц базисного графа: базисный граф 1 и базисный граф 2. Число строк и столбцов матрицы базисного графа, базисного графа 1, равны 46 и 68 соответственно, то есть полное число столбцов матрицы базисного графа равно 68, полное число строк матрицы базисного графа равно 46, и число системных столбцов матрицы базисного графа равно 68-46=22. Число строк и столбцов матрицы базисного графа, равно базисного графа 2, равны 42 и 52 соответственно, то есть полное число столбцов матрицы базисного графа равно 52, полное число строк матрицы базисного графа равно 42, и число системных столбцов матрицы базисного графа равно 52-42=10. В связи с тем, что полное число столбцов матрицы базисного графа равно 68 или полное число строк матрицы базисного графа равно 46 или число системных столбцов матрицы базисного графа равно 22, может определяться, что индекс, соответствующий матрице базисного графа, равен 1 (базисный граф 1). В связи с тем, что полное число столбцов матрицы базисного графа равно 52 или полное число строк матрицы базисного графа равно 42 или число системных столбцов матрицы базисного графа равно 10, может определяться, что индекс, соответствующий матрице базисного графа, равен 2 (базисный граф 2). Например, таблица 1 показывает позицию каждого элемента со значением 1 с индексом (i) строки в базисном графе 1 и базисном графе 2, то есть позиция может заменяться позицией циклической перестановки единичной матрицы. Таблица 2 показывает размеры поднятия, поддерживаемые базисным графом 1, включающим в себя 8 наборов размеров поднятия. Таблица 4 показывает размеры поднятия, поддерживаемые базисным графом 2, также включающим в себя 8 наборов размеров поднятия. Индекс  набора для набора размеров поднятия определяется согласно вышеупомянутой информации размера поднятия. Матрица значений сдвига каждого набора размеров поднятия, соответствующего базисному графу 1 получается из таблицы 3 согласно индексу

набора для набора размеров поднятия определяется согласно вышеупомянутой информации размера поднятия. Матрица значений сдвига каждого набора размеров поднятия, соответствующего базисному графу 1 получается из таблицы 3 согласно индексу  набора, матрица значений сдвига каждого набора размеров поднятия, соответствующего базисному графу 2 получается из таблицы 5 согласно индексу набора, и затем матрица базисного графа, соответствующая текущему размеру поднятия

набора, матрица значений сдвига каждого набора размеров поднятия, соответствующего базисному графу 2 получается из таблицы 5 согласно индексу набора, и затем матрица базисного графа, соответствующая текущему размеру поднятия  , можно получить согласно формуле:

, можно получить согласно формуле:  . Если размер битовой последовательности информационного пакета меньше или равен 2560, и кодовая скорость меньше или равна 2/3, выбирается базисный граф 2, в противном случае выбирается базисный граф 1. Заметим, что в таблице 1, первый столбец указывает индексы (i) строк базисного графа 1 и базисного графа 2, второй столбец указывает индексы (j) столбцов базисного графа 1, и [i, j] определяет позицию каждого элемента со значением 1 базисного графа 1; кроме того, третий столбец указывает индексы (j) столбцов базисного графа 2. Таблица 3 и таблица 4 соответственно показывают 8 матриц значений сдвига, соответствующих базисному графу 1 и базисному графу 2, где i указывает индекс строки, j указывает индекс столбца, и

. Если размер битовой последовательности информационного пакета меньше или равен 2560, и кодовая скорость меньше или равна 2/3, выбирается базисный граф 2, в противном случае выбирается базисный граф 1. Заметим, что в таблице 1, первый столбец указывает индексы (i) строк базисного графа 1 и базисного графа 2, второй столбец указывает индексы (j) столбцов базисного графа 1, и [i, j] определяет позицию каждого элемента со значением 1 базисного графа 1; кроме того, третий столбец указывает индексы (j) столбцов базисного графа 2. Таблица 3 и таблица 4 соответственно показывают 8 матриц значений сдвига, соответствующих базисному графу 1 и базисному графу 2, где i указывает индекс строки, j указывает индекс столбца, и  указывает индекс набора для набора размеров поднятия.

указывает индекс набора для набора размеров поднятия.

[0082] Таблица 1

В нижеследующей таблице 1 показаны базисный граф 1 и базисный граф 2.

[0083] Таблица 2

В нижеследующей таблице 2 показаны размеры поднятия базисного графа 1.

набора

набора

[0084] Таблица 3

В нижеследующей таблице 3 показаны значения сдвига базисного графа 1.

[0085] Таблица 4

В нижеследующей таблице 4 показаны размеры поднятия базисного графа 2.

набора

набора

[0086] Таблица 5 В нижеследующей таблице 5 показаны значения сдвига базисного графа 2.

[0087] На этапе S206 осуществляется перемежение. Перемежение служит для перемежения последовательности кодовых слов LDPC для получения перемеженной последовательности кодовых слов LDPC. Способ перемежения включает в себя: осуществление перемежения блоков в отношении последовательности кодовых слов LDPC, где число строк матрицы перемежения определяется согласно параметру кодирования с квазициклической LDPC, и параметр кодирования с квазициклической LDPC включает в себя по меньшей мере один из: размера поднятия, полного числа столбцов матрицы базисного графа, полного числа строк матрицы базисного графа и числа системных столбцов матрицы базисного графа.

[0088] В одном конкретном варианте осуществления, число строк матрицы перемежения равно положительному целочисленному коэффициенту размера поднятия квазициклической LDPC, или равно положительному целому числу, кратному размеру поднятия кодирования с квазициклической LDPC.

[0089] В одном конкретном варианте осуществления, число строк матрицы перемежения равно положительному целочисленному коэффициенту полного числа столбцов матрицы базисного графа кодирования с квазициклической LDPC, или равно положительному целому числу, кратному полного числа столбцов матрицы базисного графа кодирования с квазициклической LDPC.

[0090] В одном конкретном варианте осуществления, Матрица перемежения перемежается в соответствии с тем, как данные в матрице вводятся вдоль столбца и выводятся вдоль столбца.

[0091] В одном конкретном варианте осуществления, в способе перемежения, вывод осуществляется согласно заранее определенному порядку столбцов для получения перемеженной последовательности кодовых слов.

[0092] В одном конкретном варианте осуществления, в способе перемежения, перемежение внутри столбца осуществляется в отношении столбцов в матрице перемежения, где способ перемежения внутри столбца включает в себя: перемежение циклического сдвига и перемежение случайной последовательности. Предпочтительно, способ перемежения внутри столбца определяется согласно порядку модуляции. Предпочтительно, при условии, что порядок модуляции больше 2, выполняется способ перемежения внутри столбца.

[0093] Способ перемежения включает в себя: отображение всех битов от S0-го бита до S1-го бита в последовательности кодовых слов LDPC на биты от S0-го бита до S1-го бита перемеженной последовательности кодовых слов согласно заранее определенной последовательности индексов перемежения, где S0 - положительное целое число, и S1 - целое число, большее S0.

[0094] Заранее определенная последовательность индексов перемежения получается при перемежении блоков, число столбцов блочной матрицы перемежения равно Z0, и Z0 - положительное целое число.

[0095] В одном более конкретном варианте осуществления, Z0 равно положительному целочисленному коэффициенту размера поднятия кодирования с LDPC.

[0096] В одном более конкретном варианте осуществления, Z0 равно Z, Z - размер поднятия кодирования с LDPC, S0 равно 2×Z, и S1 равно E×Z−1, где E - целое число, большее 2. Кроме того, E равно kb, kb+1, kb+2, kb+3 или kb+4, где kb - число системных столбцов матрицы базисного графа кодирования с LDPC.

[0097] Предпочтительно, в одном более конкретном варианте осуществления, S0 равно kb×Z, и S1 равно E×Z−1, где Z - размер поднятия кодирования с LDPC, E равно kb+Δmb, Δmb - целое число, большее 0, и kb - число системных столбцов матрицы базисного графа кодирования с LDPC. Кроме того, Δmb определяется согласно одной из следующих комбинаций параметров: комбинации 1, состоящей из числа системных столбцов матрицы базисного графа кодирования с LDPC и скорости кодирования; комбинации 2, состоящей из длины битовой последовательности информационного пакета, длины битовой последовательности, подлежащей передаче и размера поднятия кодирования с LDPC; и комбинации 3, состоящей из числа битов проверки кода LDPC, содержащихся в битовой последовательности, подлежащей передаче, и размера поднятия кодирования с LDPC.

[0098] В одном более конкретном варианте осуществления, Z0 определяется следующими параметрами: S0, S1 и порядком модуляции, где порядок модуляции представляет собой число битов, переносимых каждым символом модуляции. Предпочтительно, Z0 вычисляется по следующей формуле:  , где M - порядок модуляции и положительное целое число.

, где M - порядок модуляции и положительное целое число.

[0099] В одном более конкретном варианте осуществления, конкретное значение S1 определяется следующими параметрами: длиной битовой последовательности информационного пакета и длиной битовой последовательности, подлежащей передаче.

[0100] В одном более конкретном варианте осуществления, когда кодовая скорость R меньше или равна R0, осуществляется перемежение блоков, где R0 - действительное число, большее или равное 3/4 и меньшее 1, и кодовая скорость R имеет значение, полученное делением длины битовой последовательности информационного пакета на длину битовой последовательности, подлежащей передаче.

[0101] Вышеупомянутый способ перемежения имеет следующие благоприятные эффекты: кодовое слово LDPC можно эффективно рандомизировать, код LDPC может получать преимущества повышенной производительности в модуляции высокого порядка (например, 64-ичная квадратурная амплитудная модуляция (QAM) или 256 QAM), и производительность кода LDPC на канале с замираниями можно эффективно повышать.

[0102] На этапе S207 осуществляется согласование скорости. Циклический выбор битов осуществляется на перемеженной последовательности кодовых слов LDPC от начальной позиции для получения согласованной по частоте последовательности кодовых слов. Начальная позиция определяется согласно заранее определенному параметру, где заранее определенный параметр включает в себя по меньшей мере один из: версии избыточности, размера поднятия, полного числа столбцов матрицы базисного графа, полного числа строк матрицы базисного графа, числа системных столбцов матрицы базисного графа или длины битовой последовательности информационного пакета.

[0103] В одном более конкретном варианте осуществления, начальная позиция определяется согласно версии избыточности, размеру поднятия и полному числу столбцов матрицы базисного графа. Кроме того, начальная позиция, соответствующая версии избыточности, равной  вычисляется по следующей формуле:

вычисляется по следующей формуле:

[0104]  ,

,

[0105] причем, в формуле, nb - полное число столбцов матрицы базисного графа, Z - размер поднятия, α - положительное целое число, G - действительное число, большее 0, β - положительное действительное число, χ - неотрицательное действительное число, и δ - целое число, где function(x) представляет округление действительного числа x в сторону увеличения, в сторону уменьшения или до ближайшего целого числа.

[0106] Кроме того, начальная позиция, соответствующая версии избыточности, равной  вычисляется по следующей формуле:

вычисляется по следующей формуле:  .

.

[0107] Причем, в формуле, nb - полное число столбцов матрицы базисного графа, Z - размер поднятия, α - положительное целое число, G - действительное число, большее 0, β - положительное целое число, λ - положительное действительное число, χ - неотрицательное действительное число, и δ - целое число, где function(x) представляет округление действительного числа x в сторону увеличения, в сторону уменьшения или до ближайшего целого числа.

[0108] Кроме того, начальная позиция, соответствующая версии избыточности, равной  вычисляется по следующей формуле:

вычисляется по следующей формуле:  .

.

[0109] Причем, в формуле, nb - полное число столбцов матрицы базисного графа, Z - размер поднятия, G - действительное число, большее 0, α - положительное целое число, β - положительное целое число, λ - положительное действительное число, χ - неотрицательное действительное число, и δ - целое число, где function(x) представляет округление действительного числа x в сторону увеличения, в сторону уменьшения или до ближайшего целого числа.

[0110] В одном более конкретном варианте осуществления, начальная позиция определяется согласно версии избыточности, размера поднятия, полного числа строк матрицы базисного графа и длины битовой последовательности информационного пакета. Кроме того, начальная позиция, соответствующая версии избыточности, равной  , вычисляется по одной из следующих формул:

, вычисляется по одной из следующих формул:  ; и

; и  ,

,

[0111] Причем, в вышеприведенных формулах, K - длина битовой последовательности информационного пакета, Z - размер поднятия, G - действительное число, большее 0, α - положительное целое число, β - положительное целое число, λ - положительное действительное число, χ - неотрицательное действительное число, и δ - целое число, где function(x) представляет округление действительного числа x в сторону увеличения, в сторону уменьшения или до ближайшего целого числа.

[0112] Циклический выбор битов осуществляется на перемеженной последовательности кодовых слов. Биты от 2×Z-го бита до концевого бита в перемеженной последовательности кодовых слов сохраняются в одном кольцевом буфере, и n битов получаются последовательно из кольцевого буфера согласно версии избыточности для формирования битовой последовательности, подлежащей передаче.

[0113] На этапе S208 осуществляется модуляция по принципу векторной диаграммы. Битовая последовательность, подлежащая передаче, делится на множество битовых пакетов, множество битовых пакетов отображается на символ модуляции векторной диаграммы, и символ модуляции векторной диаграммы отправляется. В предпочтительном варианте осуществления, до отображения множества битовых пакетов на символ модуляции векторной диаграммы, биты в битовом пакете перемежаются соответственно, и каждый перемеженный битовый пакет отображается на символ модуляции векторной диаграммы. Порядок модуляции символа модуляции векторной диаграммы равен M, и порядок модуляции представляет число битов, переносимых каждым символом модуляции векторной диаграммы. Модуляция по принципу векторной диаграммы включает в себя одну из следующих: двоичной фазовой манипуляции (BPSK), квадратурной фазовой манипуляции (QPSK), 16 QAM, 64 QAM или 256 QAM, и соответствующие порядки модуляции равны 1, 2, 4, 6 и 8 соответственно. Предпочтительно, в одном конкретном варианте осуществления, перемежение внутри битового пакета определяется согласно порядку модуляции. Например, при условии, что порядок модуляции больше M1, выполняется способ перемежения, где M1 равен 2, 3, 4, 5 или 6. Предпочтительно, перемежение внутри битового пакета включает в себя: перемежение циклического сдвига и перемежение случайной индексной последовательности. Предпочтительно, способы перемежения любых F соседних символов векторной диаграммы во всех символы модуляции векторной диаграммы отличаются, где F - положительное целое число. В другом варианте осуществления, существует G0 способов перемежения внутри битового пакета, и G0 способов отличаются. Перемежение внутри битового пакета выбирает G1 способов из G0 способов для последовательного перемежения битов в каждом битовом пакете в некотором порядке. В другом варианте осуществления, существует множество наборов способов перемежения внутри битового пакета, и способ перемежения внутри битового пакета определяется из множества наборов способов перемежения согласно порядку модуляции.

[0114] Из описания вышеупомянутых вариантов осуществления, специалистам в данной области техники будет очевидно, что способ в вышеописанных вариантах осуществления может быть реализован программным обеспечением совместно с необходимой аппаратной платформой общего назначения, или, конечно, может быть реализован оборудованием. Однако, во многих случаях, первый является предпочтительным вариантом реализации. На основании этого понимания, решения, предусмотренные настоящим изобретением по существу, или часть, отвечающая уровню техники, можно реализовать в форме программного продукта. Компьютерный программный продукт хранится на носителе данных (например, в постоянной памяти (ROM)/оперативной памяти (RAM), на магнитном диске или оптическом диске) и включает в себя несколько инструкций позволяющий оконечному устройству (которым может быть мобильный телефон, компьютер, сервер, сетевое устройство и т.п.) для выполнения способа согласно каждому варианту осуществления настоящего изобретения.

[0115] Вариант осуществления 2

[0116] Вариант осуществления дополнительно предусматривает устройство кодирования данных. Устройство используется для реализации вышеупомянутых вариантов осуществления и предпочтительных реализаций, и вышеприведенные описания не будут повторяться. Используемый ниже термин “модуль” может быть программным, аппаратным или комбинированным и осуществлять заранее определенные функции. Описанное ниже устройство согласно варианту осуществления предпочтительно реализовать программно, но также возможна и допустима аппаратная реализация или комбинированная программная и аппаратная реализация.

[0117] Согласно другому варианту осуществления настоящего изобретения, дополнительно предусмотрено устройство кодирования данных. Устройство включает в себя модуль получения, модуль перемежения, модуль выбора и модуль отправки.

[0118] Модуль получения выполнен с возможностью получения данных, подлежащих отправке.

[0119] Модуль перемежения подключен к модулю получения и выполнен с возможностью осуществления кодирования с квазициклической LDPC в отношении данных, подлежащих отправке, для получения последовательности кодовых слов LDPC, и перемежения последовательности кодовых слов LDPC для получения перемеженной последовательности кодовых слов LDPC.

[0120] Модуль выбора подключен к модулю перемежения и выполнен с возможностью осуществления циклического выбора битов на перемеженной последовательности кодовых слов LDPC от начальной позиции для получения согласованной по частоте последовательности кодовых слов, где начальная позиция определяется согласно заранее определенному параметру, где заранее определенный параметр включает в себя по меньшей мере один из: версии избыточности, размера поднятия, полного числа столбцов матрицы базисного графа, полного числа строк матрицы базисного графа, числа системных столбцов матрицы базисного графа или длины битовой последовательности информационного пакета.

[0121] Модуль отправки подключен к модулю выбора и выполнен с возможностью отправки согласованной по частоте последовательности кодовых слов.

[0122] Следует добавить, что этапы способа согласно варианту осуществления 1 могут выполняться устройством в этом варианте осуществления.

[0123] Следует отметить, что различные вышеописанные модули могут быть реализованы программно или аппаратно. Аппаратная реализация может, но не обязательно, осуществляться следующим образом: различные вышеописанные модули располагаются на одном и том же процессоре, или различные вышеописанные модули располагаются в своих соответствующих процессорах в любой комбинированной форме.

[0124] Вариант осуществления 3

[0125] Согласно другому варианту осуществления настоящего изобретения, дополнительно предусмотрен процессор. Процессор используется для выполнения программы, которая, при выполнении, выполняют способ любого из необязательные вышеописанных вариантов осуществления.

[0126] Вариант осуществления 4

[0127] Согласно другому варианту осуществления настоящего изобретения, дополнительно предусмотрен носитель данных. На носителе данных хранятся программы, которые, при выполнении, выполняют способ любого из необязательные вышеописанных вариантов осуществления.

[0128] Специалистам в данной области техники будет очевидно, что каждый из вышеупомянутых модулей или этапов настоящего изобретения может осуществляться вычислительным устройством общего назначения, модули или этапы могут быть сконцентрированы на едином вычислительном устройстве или распределены в сети, состоящей из многочисленных вычислительных устройств, и альтернативно, модули или этапы могут осуществляться программными кодами, исполняемыми вычислительными устройствами, благодаря чему, модули или этапы могут храниться в устройстве хранения и выполняться вычислительным устройством. В ряде случаев, проиллюстрированные или описанные этапы могут выполняться в другом порядке, чем описано здесь, или модули или этапы могут быть воплощены в различных модулях интегральной схемы, или несколько модулей или этапов могут быть воплощены в едином модуле интегральной схемы. Таким образом, настоящее изобретение не ограничивается никакой конкретной комбинацией оборудования и программного обеспечения.

[0129] Выше приведены только предпочтительные варианты осуществления настоящего изобретения, не призванные ограничивать настоящее изобретение. Специалисты в данной области техники могут предложить различные модификации и вариации настоящего изобретения. Любые модификации, эквивалентные замены, усовершенствования и пр., отвечающие сущности и принципу настоящего изобретения, должны укладываться в объем настоящего изобретения.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ОБРАБОТКИ ДАННЫХ И СПОСОБ ОБРАБОТКИ ДАННЫХ | 2014 |

|

RU2656830C2 |

| УСТРОЙСТВО ОБРАБОТКИ ДАННЫХ И СПОСОБ ОБРАБОТКИ ДАННЫХ | 2012 |

|

RU2595579C2 |

| УСТРОЙСТВО ОБРАБОТКИ ДАННЫХ И СПОСОБ ОБРАБОТКИ ДАННЫХ | 2014 |

|

RU2654132C2 |

| УСТРОЙСТВО ОБРАБОТКИ ДАННЫХ И СПОСОБ ОБРАБОТКИ ДАННЫХ | 2011 |

|

RU2574822C2 |

| УСТРОЙСТВО ОБРАБОТКИ ДАННЫХ И СПОСОБ ОБРАБОТКИ ДАННЫХ | 2014 |

|

RU2656723C2 |

| УСТРОЙСТВО ОБРАБОТКИ ДАННЫХ И СПОСОБ ОБРАБОТКИ ДАННЫХ | 2011 |

|

RU2574828C2 |

| КОДИРОВАНИЕ И ДЕКОДИРОВАНИЕ LDPC ПАКЕТОВ ПЕРЕМЕННЫХ РАЗМЕРОВ | 2008 |

|

RU2443053C2 |

| УЛУЧШЕННОЕ ВЫКАЛЫВАНИЕ И СТРУКТУРА КОДА С МАЛОЙ ПЛОТНОСТЬЮ ПРОВЕРОК НА ЧЕТНОСТЬ (LDPC) | 2017 |

|

RU2718171C1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ КАНАЛА В СИСТЕМЕ СВЯЗИ С ИСПОЛЬЗОВАНИЕМ КОДОВ С НИЗКОЙ ПЛОТНОСТЬЮ ПРОВЕРОК НА ЧЕТНОСТЬ | 2009 |

|

RU2450442C2 |

| СПОСОБ ОБРАБОТКИ ИНФОРМАЦИИ И УСТРОЙСТВО СВЯЗИ | 2017 |

|

RU2740154C1 |

Изобретение относится к средствам для кодирования данных. Технический результат заключается в повышении эффективности кодирования. Получают последовательность кодовых слов LDPC, осуществляя кодирование с LDPC в отношении битовой последовательности информационного пакета. Определяют размер одномерного кольцевого буфера конечной длины согласно последовательности кодовых слов LDPC. Выбирают значение версии избыточности из множества заранее определенных значений версии избыточности. Определяют начальную позицию для считывания битовой последовательности, подлежащей передаче, в одномерном кольцевом буфере конечной длины согласно выбранному значению версии избыточности, размеру поднятия и полному числу столбцов матрицы базисного графа. Причем размер поднятия описывает размер базисной матрицы перестановок или нулевой квадратной матрицы. Формируют битовую последовательность, подлежащую передаче, последовательно считывая биты данных с конкретной длиной от начальной позиции, причем биты данных базируются на последовательности кодовых слов LDPC. Отправляют битовую последовательность, подлежащую передаче. 3 н. и 8 з.п. ф-лы, 2 ил., 5 табл.

1. Способ кодирования данных с проверкой на четность низкой плотности (LDPC), содержащий этапы, на которых:

получают последовательность кодовых слов LDPC, осуществляя кодирование с LDPC в отношении битовой последовательности информационного пакета;

определяют размер одномерного кольцевого буфера конечной длины согласно последовательности кодовых слов LDPC;

выбирают значение версии избыточности из множества заранее определенных значений версии избыточности;

определяют начальную позицию для считывания битовой последовательности, подлежащей передаче, в одномерном кольцевом буфере конечной длины согласно выбранному значению версии избыточности, размеру поднятия и полному числу столбцов матрицы базисного графа,

причем размер поднятия описывает размер базисной матрицы перестановок или нулевой квадратной матрицы;

формируют битовую последовательность, подлежащую передаче, последовательно считывая биты данных с конкретной длиной от начальной позиции, причем биты данных базируются на последовательности кодовых слов LDPC; и

отправляют битовую последовательность, подлежащую передаче.

2. Способ по п. 1, в котором определение размера одномерного кольцевого буфера конечной длины согласно последовательности кодовых слов LDPC содержит этапы, на которых:

перемежают последовательность кодовых слов LDPC для получения перемеженной последовательности кодовых слов LDPC и получают данные одномерного кольцевого буфера конечной длины.

3. Способ по п. 2, в котором перемежение последовательности кодовых слов LDPC для получения перемеженной последовательности кодовых слов LDPC содержит этап, на котором:

осуществляют перемежение блоков в отношении последовательности кодовых слов LDPC, причем число строк матрицы перемежения определяется согласно параметру кодирования с LDPC, и при этом параметр кодирования с LDPC содержит по меньшей мере один из размера поднятия, полного числа столбцов матрицы базисного графа, полного числа строк матрицы базисного графа или числа системных столбцов матрицы базисного графа.

4. Способ по п. 1, в котором начальная позиция, соответствующая версии избыточности, равной  , вычисляется по следующей формуле:

, вычисляется по следующей формуле:

первой формуле:  ;

;

причем в первой формуле nb - полное число столбцов матрицы базисного графа, Z - размер поднятия, α - положительное целое число, G - действительное число, большее 0, β - положительное действительное число, χ - неотрицательное действительное число и δ - целое число,

где function(x) представляет округление действительного числа x в сторону увеличения, в сторону уменьшения или до ближайшего целого числа; или

второй формуле:  ;

;

причем во второй формуле nb - полное число столбцов матрицы базисного графа, Z - размер поднятия, α - положительное целое число, G - действительное число, большее 0, β - положительное целое число, λ - положительное действительное число,  - неотрицательное действительное число и δ - целое число,

- неотрицательное действительное число и δ - целое число,

где function(x) представляет округление действительного числа x в сторону увеличения, в сторону уменьшения или до ближайшего целого числа; или

третьей формуле:  ;

;

причем в третьей формуле nb - полное число столбцов матрицы базисного графа, Z - размер поднятия, G - действительное число, большее 0, α - положительное целое число, β - положительное целое число, λ - положительное действительное число, χ - неотрицательное действительное число и δ - целое число,

где function(x) представляет округление действительного числа x в сторону увеличения, в сторону уменьшения или до ближайшего целого числа.

5. Способ по п. 2, в котором перемежение последовательности кодовых слов LDPC для получения перемеженной последовательности кодовых слов LDPC содержит этап, на котором:

перемежают все биты от S0-го бита до S1-го бита в последовательности кодовых слов LDPC, где S0 и S1 - положительные целые числа, и S1 больше S0.

6. Способ по п. 5, в котором перемежение всех битов от S0-го бита до S1-го бита в последовательности кодовых слов LDPC содержит этап, на котором:

осуществляют перемежение блоков для всех битов от S0-го бита до S1-го бита в последовательности кодовых слов LDPC согласно матрице перемежения, причем полное число столбцов блочной матрицы перемежения равно Z0, причем Z0 определяется параметром кодирования с LDPC, причем параметр кодирования с квазициклической LDPC содержит по меньшей мере одно из размера поднятия, полного числа столбцов матрицы базисного графа, полного числа строк матрицы базисного графа, числа системных столбцов матрицы базисного графа или длины битовой последовательности информационного пакета.

7. Способ по п. 6, в котором Z0 определяется следующими параметрами: S0, S1 и порядком модуляции, где порядок модуляции определяется как число битов, переносимых каждым символом модуляции.

8. Способ по п. 7, в котором Z0 вычисляется по следующей формуле:

9. Способ по п. 1, в котором отправка битовой последовательности, подлежащей передаче, содержит этапы, на которых: делят битовую последовательность, подлежащую передаче, на множество битовых пакетов, перемежают биты в каждом битовом пакете из множества битовых пакетов соответственно, и отображают каждый перемеженный битовый пакет в символ модуляции векторной диаграммы.

10. Носитель данных, содержащий хранимые на нем программы, при этом, при выполнении, программы выполняют способ по любому из пп. 1-9.

11. Процессор, выполненный с возможностью выполнения программ, при этом, при выполнении, программы выполняют способ по любому из пп. 1-9.

| CN 101188428 A, 28.05.2008 | |||

| Токарный резец | 1924 |

|

SU2016A1 |

| CN 107026654 A, 08.08.2017 | |||

| CN 102075196 A, 25.05.2011 | |||

| Способ приготовления лака | 1924 |

|

SU2011A1 |

| УСТРОЙСТВО И СПОСОБ ПЕРЕДАЧИ И ПРИЕМА ЗАКОДИРОВАННЫХ ДАННЫХ ПОСРЕДСТВОМ КОДЕРА, ИМЕЮЩЕГО НЕРАВНУЮ ВЕРОЯТНОСТЬ ОШИБОК, В СИСТЕМЕ МОБИЛЬНОЙ СВЯЗИ | 2004 |

|

RU2340092C2 |

Авторы

Даты

2021-02-11—Публикация

2018-07-09—Подача