Область техники, к которой относится изобретение

Варианты осуществления настоящего изобретения относятся к области связи и, в частности, к способу обработки информации и устройству связи.

Уровень техники

Код с низкой плотностью проверок на четность (low density parity check, LDPC) представляет собой тип линейного блочного кода с разреженной матрицей проверки на четность и характеризуется гибкой структурой и низкой сложностью декодирования. Поскольку при декодировании LDPC кода используют частично параллельный алгоритм итеративного декодирования, LDPC код имеет более высокую производительность, чем обычный турбокод. Для повышения надежности передачи канала и эффективного использования мощности в системе связи LDPC код может быть использован в качестве кода с исправлением ошибок в системе связи. LDPC код может также широко применяться для космической связи, волоконно-оптической связи, систем персональной связи, ADSL, устройств магнитной записи и тому подобного. В настоящее время LDPC схема кода рассматривается как одна из схем канального кодирования в мобильной связи 5-го поколения.

В практических применениях могут быть использованы LDPC матрицы, характеризующиеся различными специальными структурами. LDPC матрица Н, имеющая специальную структуру, может быть получена путем расширения LDPC базовой матрицы, имеющей квазициклическую (quasi cycle, QC) структуру. Схема кодирования с использованием QC-LDPC матриц подходит для аппаратных средств с высокой степенью параллелизма и обеспечивает более высокую производительность.

QC-LDPC подходит для аппаратных средств с высокой степенью параллелизма и обеспечивает более высокую производительность. LDPC матрица может быть разработана для применения в канальном кодировании.

Сущность изобретения

Варианты осуществления настоящего изобретения предоставляют способ обработки информации и устройство и систему связи для поддержки кодирования и декодирования последовательностей информационных бит множества длин.

Согласно первому аспекту предоставлены способ кодирования и кодер. Кодер кодирует входную последовательность, используя матрицу кода с низкой плотностью проверок на четность, LDPC.

Согласно второму аспекту предоставлены способ декодирования и декодер. Декодер декодирует входную последовательность, используя матрицу кода с низкой плотностью проверок на четность, LDPC.

В первой реализации первого аспекта или второго аспекта LDPC матрицу получают на основании коэффициента Z поднятия и базовой матрицы.

На основании вышеизложенной реализации базовая матрица базового графа 30a может включать в себя от строки 0 до строки 4 и от столбца 0 до столбца 26 в одной из матриц 30b-10, 30b-11, 30b-20, 30b-21, 30b-30, 30b-40, 30b-50, 30b-60, 30b-70 и 30b-80, или базовая матрица включает в себя от строки 0 до строки 4 и некоторые из столбцов от 0 до столбца 26 в одной из матриц 30b-10 30b-11, 30b-20, 30b-21, 30b-30, 30b-40, 30b-50, 30b-60, 30b-70 и 30b-80 или базовая матрица может быть матрицей, полученной путем выполнения перестановки строка/столбец в матрице, включающей в себя строки от 0 до строки 4 и от столбца 0 до столбца 26 в одной из матриц с 30b-10 по 30b-80, или базовая матрица может быть матрицей, полученной путем выполнения перестановки строка/столбец для матрицы, включающей в себя от строки 0 до строки 4 и некоторые их столбцов от 0 до столбца 26 в одной из матриц 30b-10, 30b-11, 30b-20, 30b-21, 30b-30, 30b-40, 30b-50, 30b-60, 30b-70 и 30b-80.

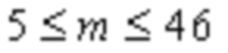

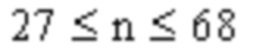

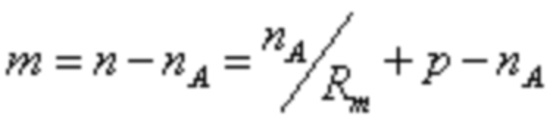

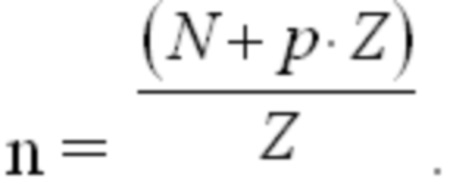

Кроме того, базовая матрица базового графа 30a может дополнительно включать в себя строку 0 до строки (m-1) и столбец 0 до столбца (n-1) в одной из матриц 30b-10, 30b-11, 30b-20, 30b-21, 30b-30, 30b-40, 30b-50, 30b-60, 30b-70 и 30b-80 или базовая матрица может быть матрицей, полученной путем выполнения перестановки строка/столбец на матрице включающей в себя строки от 0 до строки (m-1) и от 0 до столбца (n-1) в одной из матриц 30b-10, 30b-11, 30b-20, 30b-21, 30b-30, 30b-40, 30b-50, 30b-60, 30b-70 и 30b-80, где  и

и  .

.

Чтобы поддерживать разные длины кодовых блоков, для LDPC кода требуются разные коэффициенты Z поднятия. На основании вышеизложенной реализации в возможной реализации, основанной на различных коэффициентах Z поднятия, используются базовые матрицы, соответствующие различным коэффициентам Z поднятия. Например,  и

и  .

.

Если a = 2, базовая матрица может включать в себя строки от 0 до строки 4 и от столбца 0 до столбца 26 в матрице 30b-10 или 30b-11, или базовая матрица включает в себя строки от 0 до строки 4 и некоторые из столбца 0 до столбца 26 в матрице 30b-10 или 30b-11. Кроме того, базовая матрица дополнительно включает в себя строки от 0 до строки (m-1) и от столбца 0 до столбца (n-1) в матрице 30b-10 или 30b-11.

Если a = 3, базовая матрица может включать в себя строки от 0 до строки 4 и от столбца 0 до столбца 26 в матрице 30b-20 или 30b-21, или базовая матрица включает в себя строки от 0 до строки 4 и некоторые из столбца 0 до столбца 26 в матрице 30b-20 или 30b-21. Кроме того, базовая матрица дополнительно включает в себя строки от 0 до строки (m-1) и от столбца 0 до столбца (n-1) в матрице 30b-20 или 30b-21.

Если a = 5, базовая матрица может включать в себя строки от 0 до строки 4 и столбцы от 0 до столбца 26 в матрице 30b-30, или базовая матрица включает в себя строки от 0 до строки 4 и некоторые из столбцов от 0 до столбца 26 в матрица 30b-30. Кроме того, базовая матрица дополнительно включает в себя строку от 0 до строки (m-1) и от столбца 0 до столбца (n-1) в матрице 30b-30.

Если a = 7, базовая матрица может включать в себя строку 0 до строки 4 и столбец 0 до столбца 26 в матрице 30b-40, или базовая матрица включает строку 0 по строку 4 и некоторые столбцы 0 по столбец 26 в матрице 30b-40. Кроме того, базовая матрица дополнительно включает в себя строку 0 по строку (m-1) и столбец от 0 до столбца (n-1) в матрице 30b-40.

Если a = 9, базовая матрица может включать в себя строку от 0 по строку 4 и столбец 0 по столбец 26 в матрице 30b-50, или базовая матрица включает в себя строку 0 - строку 4 и некоторые столбцы 0 - столбец 26 в матрица 30b-50. Кроме того, базовая матрица дополнительно включает в себя строку от 0 по строки (m-1) и столбец от 0 до столбца (n-1) в матрице 30b-50.

Если a = 11, базовая матрица может включать в себя строки от 0 до строки 4 и от столбца 0 до столбца 26 в матрице 30b-60, или базовая матрица включает в себя строки от 0 до строки 4 и некоторые из столбцов от 0 до столбца 26 в матрица 30b-60. Кроме того, базовая матрица дополнительно включает в себя строку от 0 до строки (m-1) и столбец от 0 до столбца (n-1) в матрице 30b-60.

Если a = 13, базовая матрица может включать в себя строки от 0 до строки 4 и столбцы от 0 до столбца 26 в матрице 30b-70, или базовая матрица включает в себя строки от 0 до строки 4 и некоторые из столбцов от 0 до столбца 26 в матрица 30b-70. Кроме того, базовая матрица дополнительно включает в себя строку от 0 до строки (m-1) и столбец от 0 до столбца (n-1) в матрице 30b-70.

Если a = 15, базовая матрица может включать в себя строку от 0 до строки 4 и столбец 0 до столбца 26 в матрице 30b-80, или базовая матрица включает строку от 0 до строки 4 и некоторые столбцы от 0 до столбца 26 в матрице 30b-80. Кроме того, базовая матрица дополнительно включает в себя строку от 0 до строки (m-1) и столбец от 0 до столбца (n-1) в матрице 30b-80.

Базовая матрица может быть матрицей, полученной путем выполнения перестановки строка/столбец над вышеупомянутыми базовыми матрицами.

Кроме того, альтернативно, на основании вышеупомянутых реализаций, LDPC матрица может быть получена на основании коэффициента Z поднятия и матрицы Hs, полученной посредством смещения каждой из вышеупомянутых базовых матриц, или может быть получена на основании коэффициента Z поднятия и матрица, полученная путем выполнения перестановки строка/столбец для матрицы Hs, полученной путем смещения каждой из вышеупомянутых базовых матриц. Смещение каждой из вышеупомянутых базовых матриц может содержать: увеличение или уменьшение значений сдвига, больших или равных 0, в одном или нескольких столбцах на величину смещения.

Базовый граф и базовые матрицы LDPC матрицы в вышеприведенных реализациях могут удовлетворять требованиям к производительности кодовых блоков множества длин блоков.

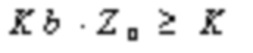

На основании любого из вышеупомянутых аспектов или возможных реализаций аспектов, в другой возможной реализации, способ дополнительно включает в себя: определение коэффициента Z поднятия. Например, значение коэффициента Z поднятия определяют на основании длины K входной последовательности. Минимальное значение Z0, которое удовлетворяет  , может быть определено из поддерживаемого коэффициента поднятия, установленного в качестве значения коэффициента Z поднятия. В возможной реализации Kb может быть количеством столбцов, соответствующих информационным битам в базовой матрице LDPC кода. Например, для базового графа 30a, Kb = 22. В другой возможной реализации значение Kb может варьироваться в зависимости от значения K, но не превышает количество столбцов, соответствующих информационным битам в базовой матрице LDPC кода. Например, когда K больше первого порогового значения, Kb = 22; когда K меньше или равно первому пороговому значению, Kb = 21. В качестве альтернативы, когда K превышает первое пороговое значение, Kb = 22; когда K меньше или равен первому пороговому значению и больше второго порогового значения, Kb = 21; когда K меньше или равен второму пороговому значению, Kb = 20.

, может быть определено из поддерживаемого коэффициента поднятия, установленного в качестве значения коэффициента Z поднятия. В возможной реализации Kb может быть количеством столбцов, соответствующих информационным битам в базовой матрице LDPC кода. Например, для базового графа 30a, Kb = 22. В другой возможной реализации значение Kb может варьироваться в зависимости от значения K, но не превышает количество столбцов, соответствующих информационным битам в базовой матрице LDPC кода. Например, когда K больше первого порогового значения, Kb = 22; когда K меньше или равно первому пороговому значению, Kb = 21. В качестве альтернативы, когда K превышает первое пороговое значение, Kb = 22; когда K меньше или равен первому пороговому значению и больше второго порогового значения, Kb = 21; когда K меньше или равен второму пороговому значению, Kb = 20.

Коэффициент Z поднятия может быть определен кодером или декодером на основании длины K входной последовательности или может быть определен другим компонентом и предоставлен кодеру или декодеру в качестве входного параметра.

Возможно, LDPC матрица может быть получена на основании полученного коэффициента Z поднятия и базовой матрицы, соответствующей коэффициенту Z поднятия.

Во второй реализации первого аспекта или второго аспекта LDPC матрицу получают на основании коэффициента Z поднятия и параметров LDPC матрицы.

Параметры LDPC матрицы могут включать в себя индекс строки, позицию столбца, в котором расположен ненулевой элемент, и значение сдвига ненулевого элемента, и хранят в соответствии с таблицей 3- 10, таблицей 3-11, таблицей 3-20, таблицей 3-21, таблицей 3-30, таблицей 3-40, таблицей 3-50, таблицей 3-60, таблицей 3-70 и таблицей 3-80. Параметры могут дополнительно включать в себя вес строки. Позиции столбцов, в которых расположен ненулевой элемент, находятся во взаимно однозначном соответствии со значениями сдвига ненулевого элемента.

Следовательно, кодер кодирует входную последовательность на основании коэффициента Z поднятия и параметров LDPC матрицы. Параметры, сохраненные на основании таблицы 3-10, соответствуют матрице 30b-10, параметры, сохраненные на основании таблицы 3-11, соответствуют матрице 30b-11, параметры, сохраненные на основании таблицы 3-20, соответствуют матрице 30b-20, параметры, сохраненные на основании таблицы 3-21, соответствуют матрице 30b-21, параметры, сохраненные на основании таблицы 3-30, соответствуют матрице 30b-30, параметры, сохраненные на основании таблицы 3-40, соответствуют матрице 30b-40, параметры, сохраненные на основании таблицы 3-50, соответствуют матрице 30b-50, параметры, сохраненные на основании таблицы 3-60, соответствуют матрице 30b-60, параметры, сохраненные на основе таблицы 3-70, соответствуют матрице 30b-70, и параметры, сохраненные на основании таблицы 3-80, соответствуют матрице 30b-80.

Для устройства связи на передающей стороне кодирование входной последовательности с использованием LDPC матрицы может включать в себя:

кодирование входной последовательности с использованием LDPC матрицы, соответствующей коэффициенту Z поднятия; или кодирование входной последовательности с использованием матрицы, причем матрицу получают путем выполнения перестановки строк/столбцов на LDPC матрице, соответствующей коэффициенту Z поднятия. В настоящем изобретении перестановка строк/столбцов относится к перестановке строк, перестановок столбцов или перестановке строк и перестановок столбцов.

Для устройства связи на принимающей стороне декодирование входной последовательности с использованием LDPC матрицы включает в себя:

декодирование входной последовательности с использованием LDPC матрицы, соответствующей коэффициенту Z поднятия; или декодирование входной последовательности с использованием матрицы, в котором матрицу получают путем выполнения перестановки строк/столбцов на LDPC матрице, соответствующей коэффициенту Z поднятия. В настоящем изобретении перестановка строк/столбцов относится к перестановке строк, перестановок столбцов или перестановке строк и перестановок столбцов.

В возможной реализации LDPC матрица может быть сохранена в памяти, и входную последовательность кодируют с использованием LDPC матрицы, или перестановку (перестановка строк/столбцов) или поднятие выполняют на основании LDPC матрицы, чтобы получить LDPC матрицу, которую можно использовать для кодирования.

В другой возможной реализации может быть сохранен один или несколько параметров, LDPC матрица, используемая для кодирования или декодирования, может быть получена на основании одного или нескольких параметров, и поэтому входная последовательность может быть кодирована или декодирована на основании LDPC матрицы. Один или несколько параметров включают в себя, по меньшей мере, одно из следующего: базовый граф, базовую матрицу, переставленную матрицу, полученную путем выполнения перестановки строк/столбцов на основании базового графа или базовой матрицы, поднятую матрицу на основании базового графа или базовой матрицы, значение сдвига ненулевого элемента в базовой матрице или любой параметр, относящийся к получению LDPC матрицы.

В еще одном возможном варианте осуществления базовая матрица LDPC матрицы может храниться в памяти.

В еще одной возможной реализации базовый граф LDPC матрицы может быть сохранен в памяти, и значения смещения ненулевых элементов в базовой матрице LDPC матрицы могут быть сохранены в памяти.

В еще одной возможной реализации параметры LDPC матрицы сохраняют в памяти в соответствии с таблицами с 3-10 по 3-80.

На основании вышеизложенных возможных реализаций, в возможной реализации, по меньшей мере, один из базовый граф и базовая матрица, которые используют для LDPC кодирования или декодирования, получают путем выполнения перестановки строк, или перестановки столбцов, или перестановки строк и столбцов, перестановкой, по меньшей мере, на одном из базовом графе и базовой матрицы вышеупомянутой LDPC матрицы.

Согласно третьему аспекту предоставлено устройство связи. Устройство связи может включать в себя соответствующий модуль, выполненный с возможностью выполнять вышеизложенные способы реализаций. Модуль может быть программным и/или аппаратным.

В возможной реализации устройство связи, предусмотренное в третьем аспекте, включает в себя процессор и компонент приемопередатчика. Процессор и компонент приемопередатчика могут быть выполнены с возможностью реализации функций описанного выше способа кодирования или декодирования. В реализации, если устройство связи является терминалом, базовой станцией или другим сетевым устройством, компонент приемопередатчика устройства связи может быть приемопередатчиком; если устройство связи представляет собой микросхему основной полосы частот или схему обработки основной полосы частот, компонент приемопередатчика устройства связи может быть схемой ввода/вывода микросхемы основной полосы частот или схемы обработки основной полосы частот и выполнена с возможностью принимать/отправлять входной/выходной сигнал. Возможно, устройство связи может дополнительно включать в себя память, выполненную с возможностью хранить данные и/или инструкции.

В реализации процессор может включать в себя кодер согласно первому аспекту и блок определения. Блок определения выполнен с возможностью определять коэффициент Z поднятия, необходимого для кодирования входной последовательности. Кодер выполнен с возможностью кодировать входную последовательность с использованием LDPC матрицы, соответствующей коэффициенту Z поднятия.

В другой реализации процессор может включать в себя декодер согласно второму аспекту и модуль получения. Модуль получения выполнен с возможностью получения мягких значений кода LDPC и коэффициента подъема Z. Декодер выполнен с возможностью декодировать мягкие значения кода LDPC на основе базовой матрицы HB, соответствующей коэффициенту подъема Z, для получения информационного бита. последовательность.

В соответствии с четвертым аспектом предоставлено устройство связи, включающее в себя один или несколько процессоров.

В возможной реализации один или более процессоров могут реализовывать функции кодера в первом аспекте. В другом возможном варианте кодер в первом аспекте может быть частью процессора. Процессор может реализовывать другие функции в дополнение к функциям кодера в первом аспекте.

В возможной реализации один или несколько процессоров могут реализовывать функции декодера, описанные во втором аспекте. В другой возможной реализации декодер во втором аспекте может быть частью процессора.

Возможно, устройство связи может дополнительно включать в себя приемопередатчик и антенну.

Возможно, устройство связи может дополнительно включать в себя компонент, выполненный с возможностью генерировать CRC транспортный блок, компонент, выполненный с возможностью выполнять сегментацию кодового блока и CRC присоединение, перемежитель, выполненный с возможностью выполнять перемежение, модулятор, выполненный с возможностью выполнять обработку модуляции, или т.п..

Возможно, устройство связи может дополнительно включать в себя демодулятор, выполненный с возможностью выполнять демодуляцию, обращенный перемежитель, выполненный с возможностью выполнять обратное перемежение, компонент, выполненный с возможностью выполнять согласования с пониженной скоростью, или тому подобное. Функции этих компонентов могут быть реализованы с использованием одного или нескольких процессоров.

В возможной реализации функции этих компонентов могут быть реализованы с использованием одного или нескольких процессоров.

Согласно пятому аспекту вариант осуществления настоящего изобретения предоставляет систему связи. Система включает в себя устройство связи, описанное в третьем аспекте.

Согласно шестому аспекту вариант осуществления настоящего изобретения предоставляет систему связи. Система включает в себя одно или несколько устройств связи, описанных в четвертом аспекте.

Согласно другому аспекту вариант осуществления настоящего изобретения предоставляет компьютерный носитель данных. Компьютерный носитель данных хранит программу, и когда программа выполняется на компьютере, компьютер выполняет способ в соответствии с любым из вышеупомянутых аспектов.

Согласно еще одному аспекту настоящего изобретения предоставлен компьютерный программный продукт, включающий в себя инструкции. Когда компьютерный программный продукт выполняют на компьютере, компьютер выполняет способ в соответствии с любым из вышеупомянутых аспектов.

Согласно способу обработки информации, приспособлению, устройству связи и системе связи в вариантах осуществления настоящего изобретения могут быть удовлетворены требования гибкой длины кода и скорости кодирования системы с точки зрения производительности кодирования и минимального уровня ошибок.

Краткое описание чертежей

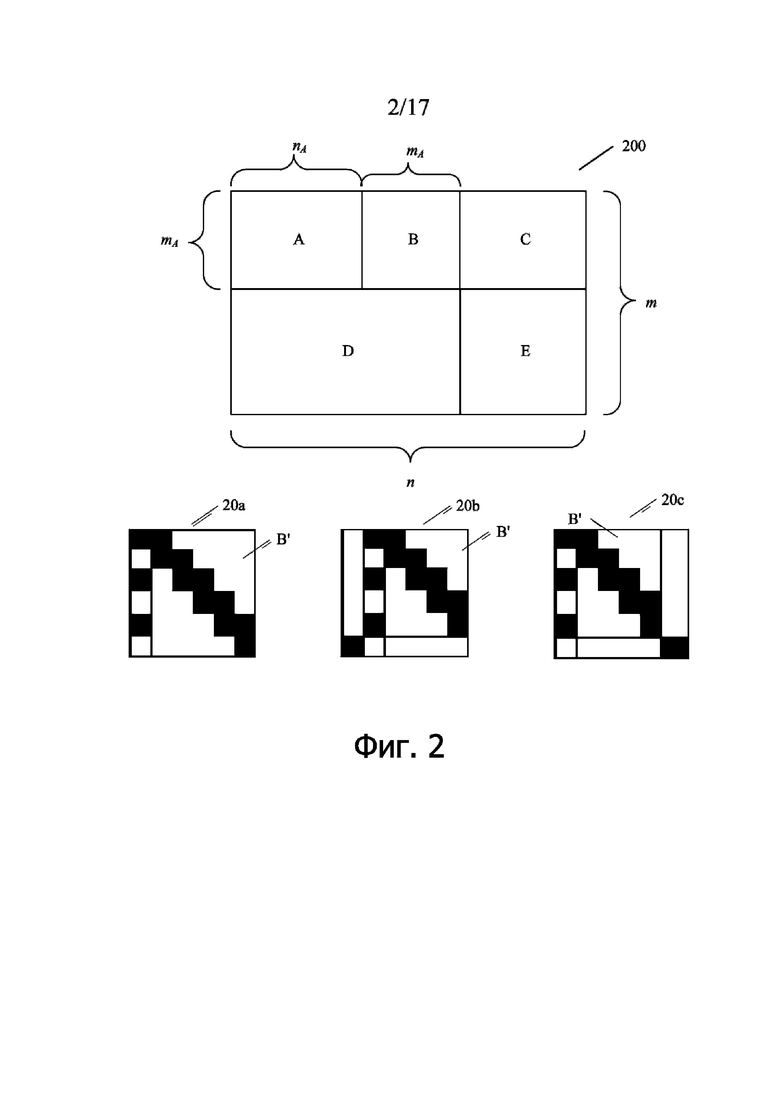

Фиг. 1 является схемой базового графа, базовой матрицы и матриц круговой перестановки базовой матрицы в схеме LDPC кода;

Фиг. 2 является схемой базового графа LDPC кода;

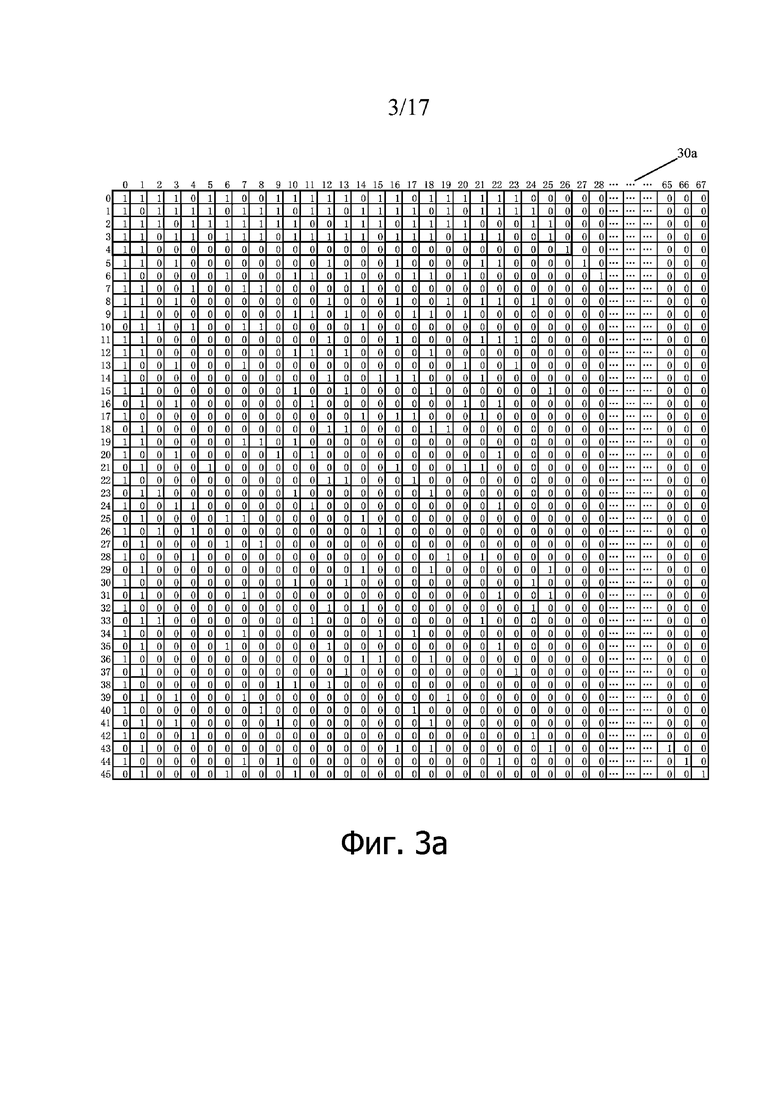

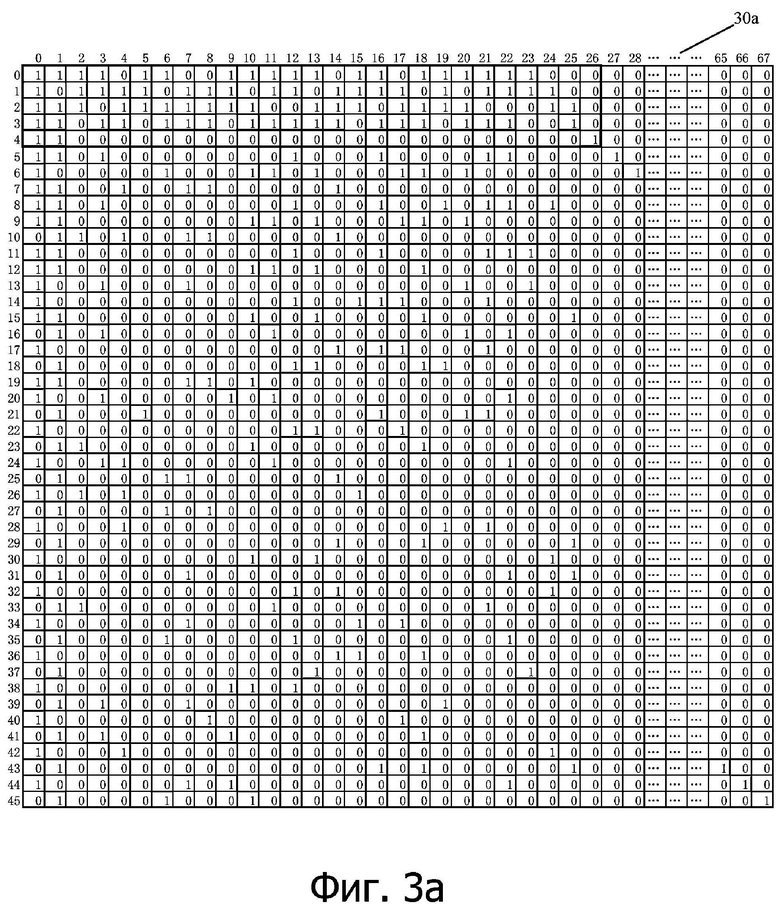

Фиг. 3a является схемой базового графа LDPC кода согласно варианту осуществления настоящего изобретения;

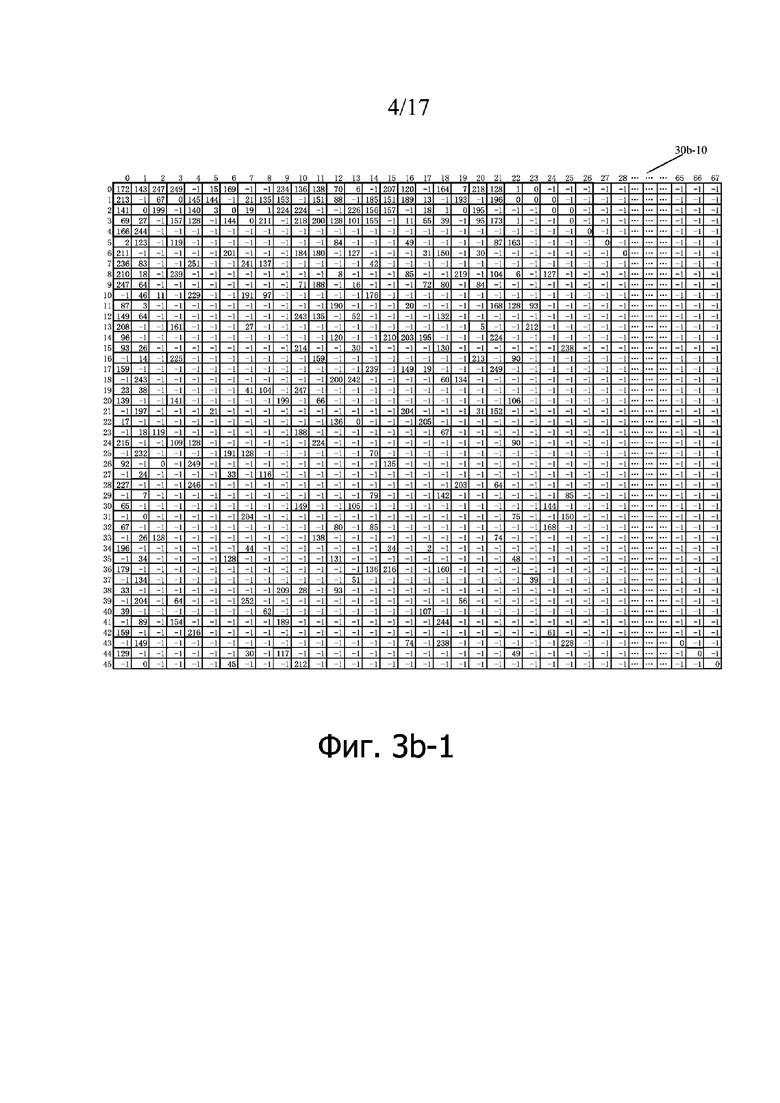

Фиг. 3b-1 является схемой базовой матрицы в соответствии с вариантом осуществления настоящего изобретения;

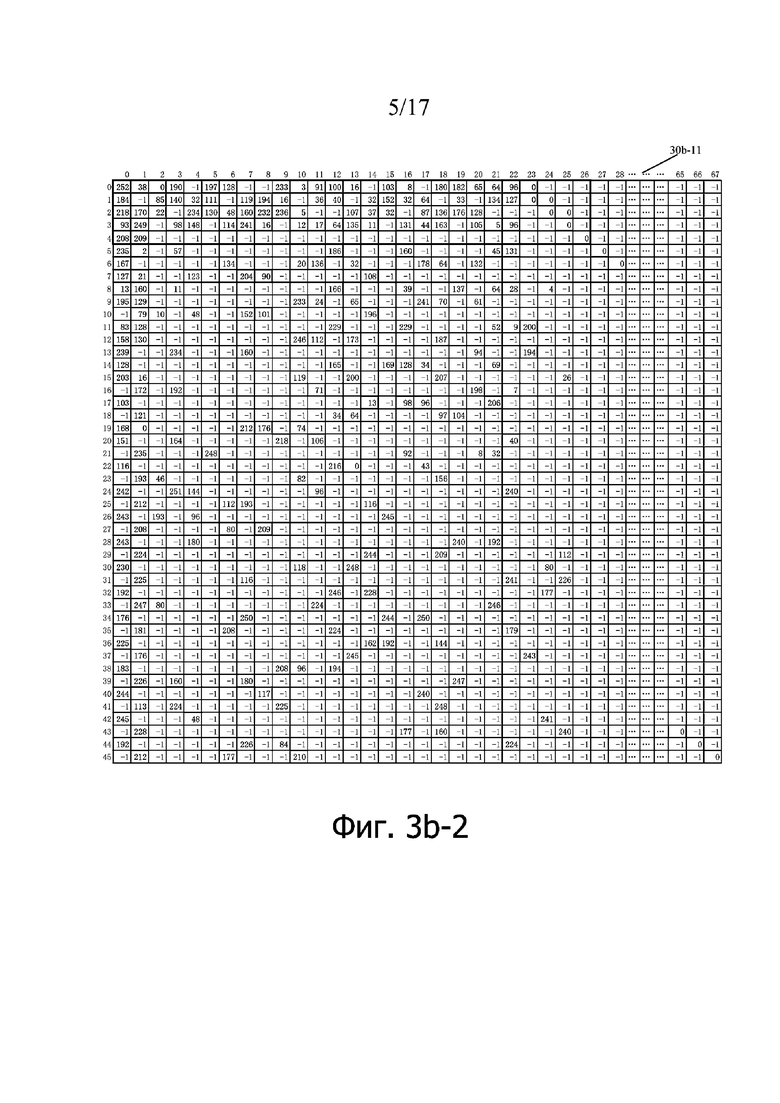

Фиг. 3b-2 является схемой другой базовой матрицы в соответствии с вариантом осуществления настоящего изобретения;

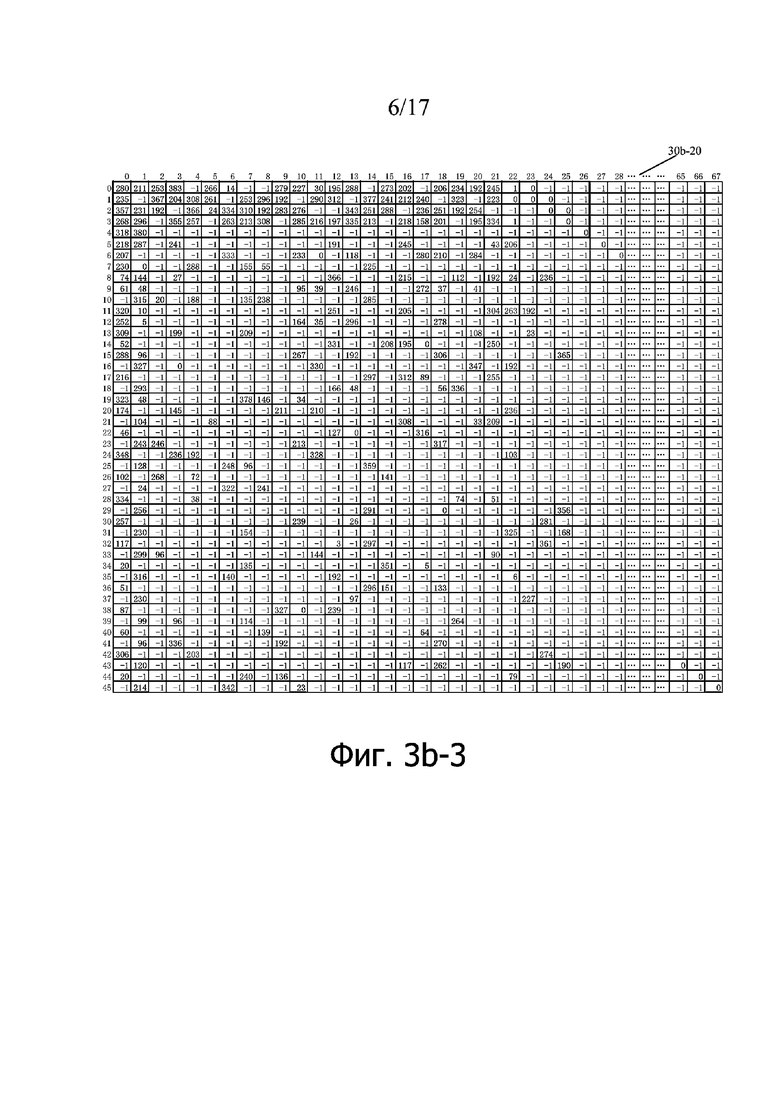

Фиг. 3b-3 является схемой другой базовой матрицы в соответствии с вариантом осуществления настоящего изобретения;

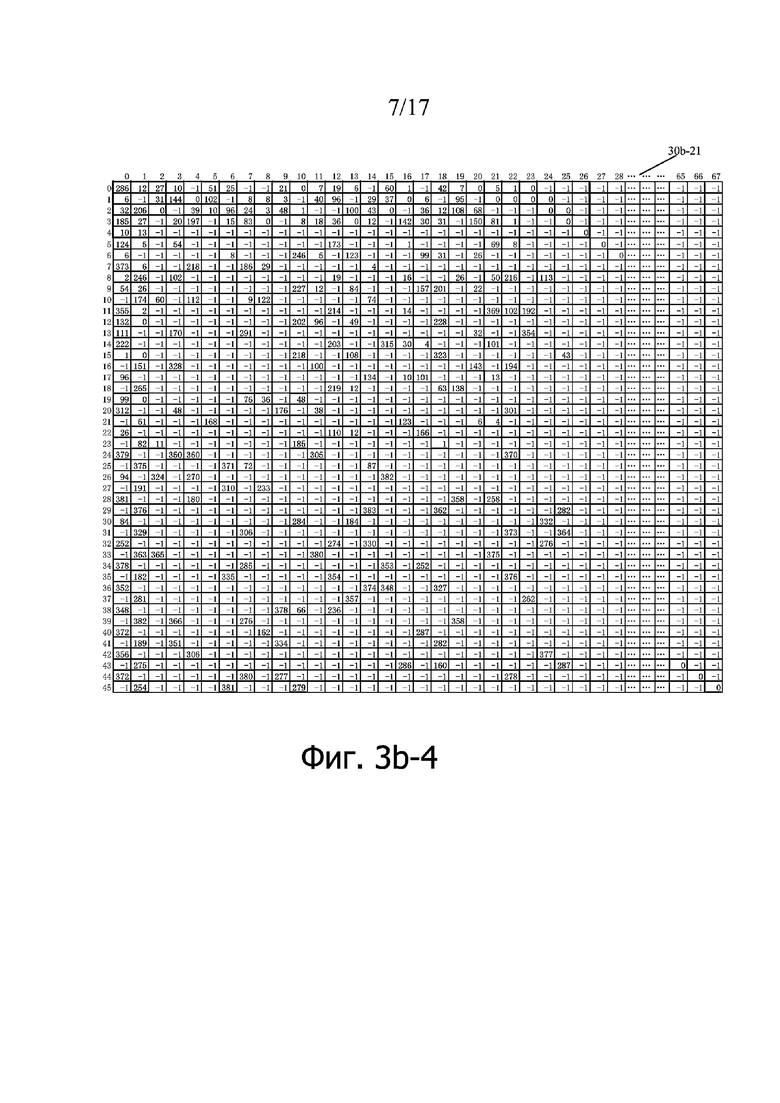

Фиг. 3b-4 является схемой другой базовой матрицы согласно варианту осуществления настоящего изобретения;

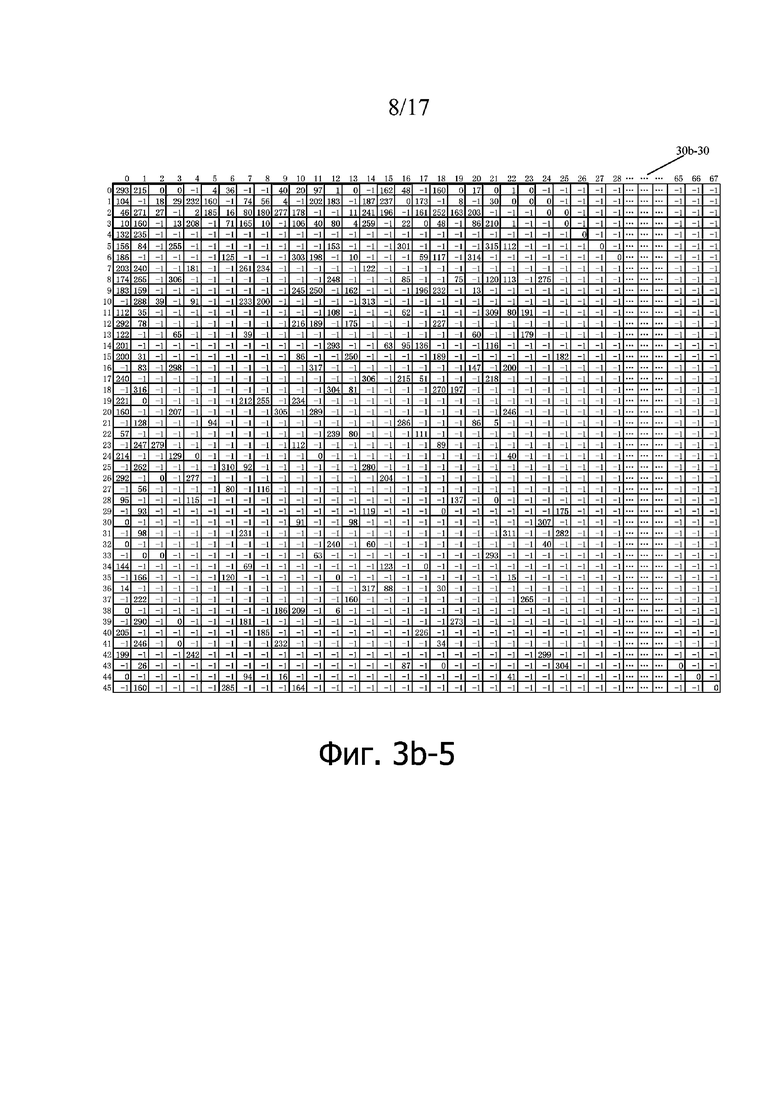

Фиг. 3b-5 является схемой другой базовой матрицы согласно варианту осуществления настоящего изобретения;

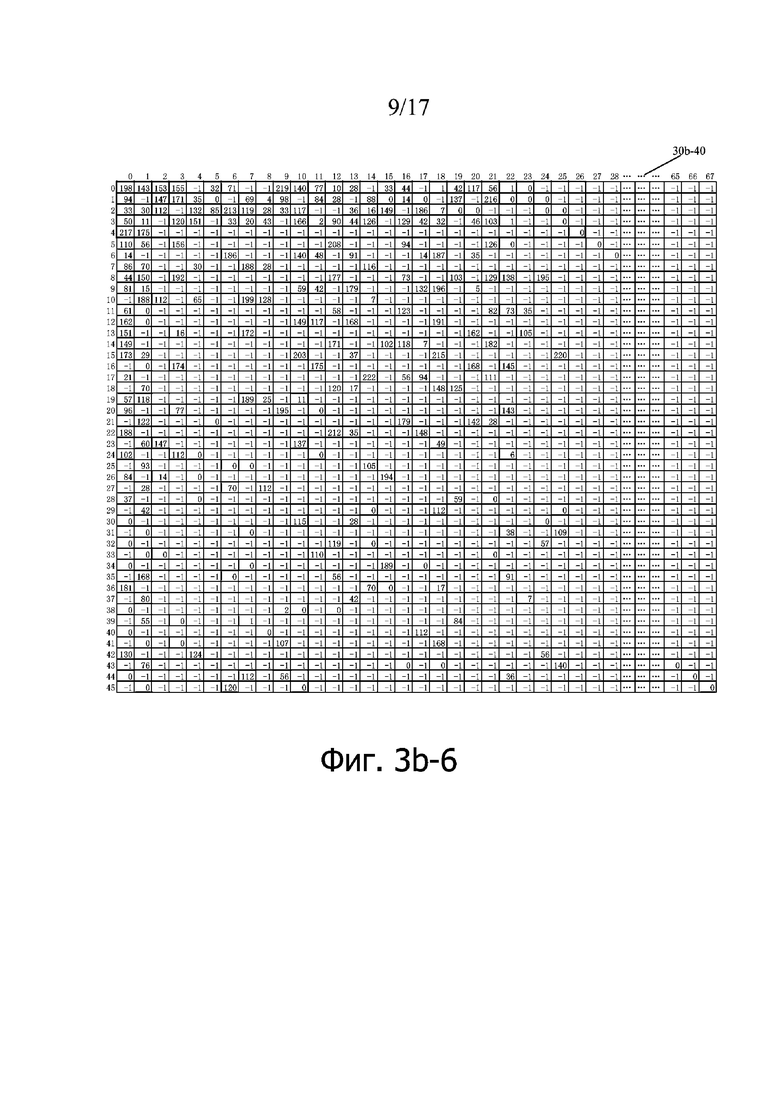

Фиг. 3b-6 является схемой другой базовой матрицы в соответствии с вариантом осуществления настоящего изобретения;

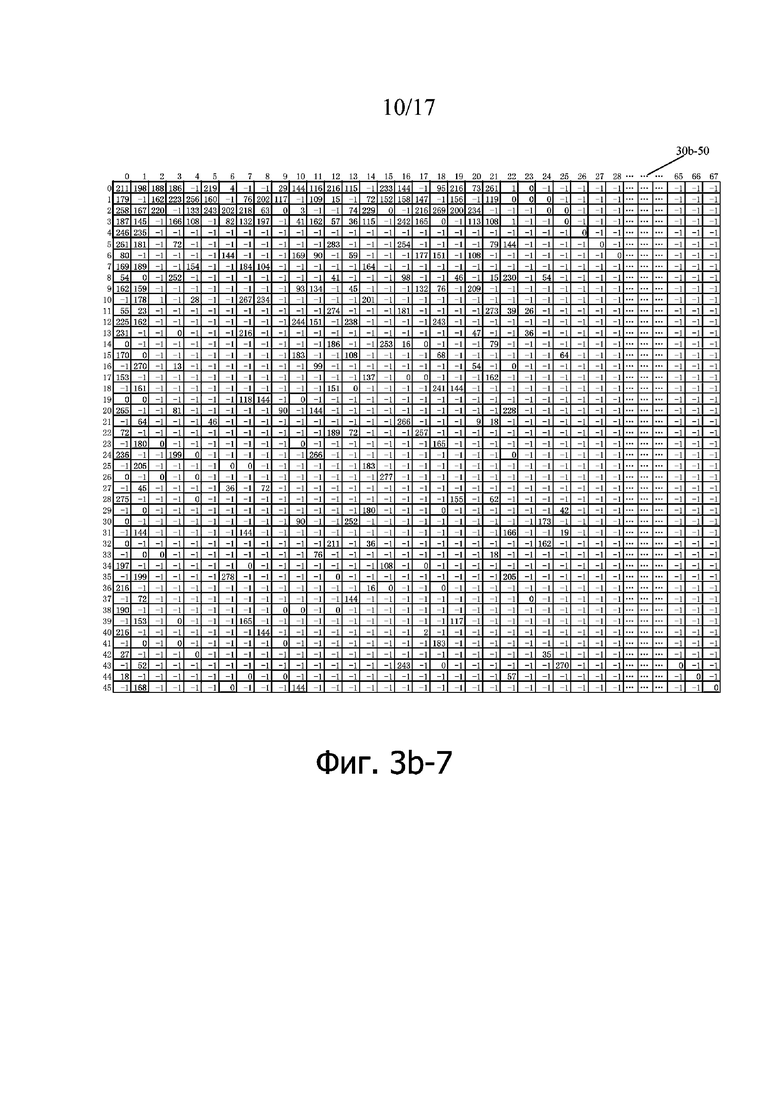

Фиг. 3b-7 является схемой другой базовой матрицы в соответствии с вариантом осуществления настоящего изобретения;

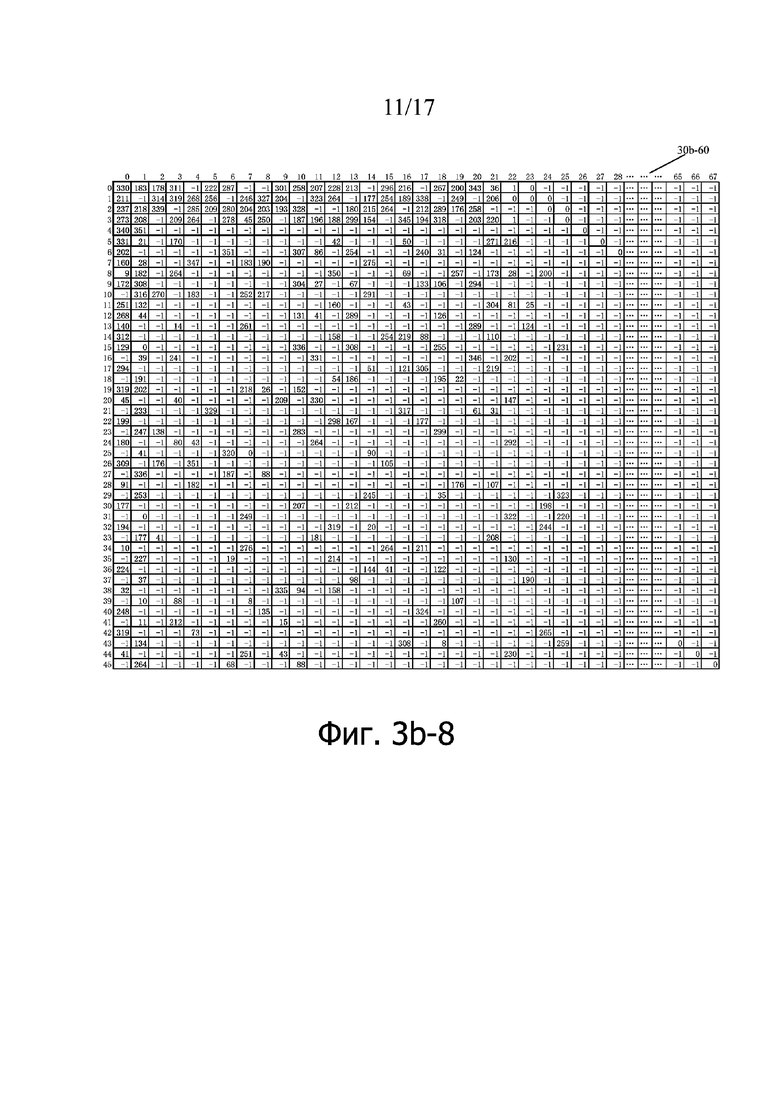

Фиг. 3b-8 является схемой другой базовой матрицы в соответствии с вариантом осуществления настоящего изобретения;

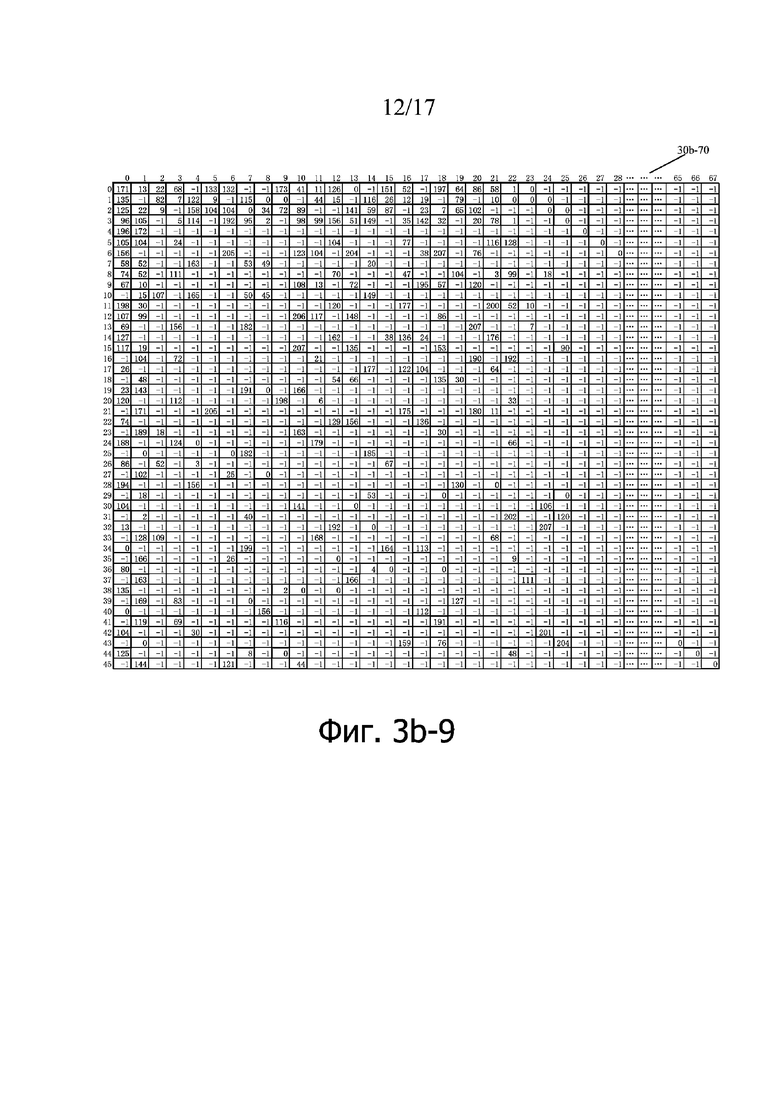

Фиг. 3b-9 является схемой другой базовой матрицы в соответствии с вариантом осуществления настоящего изобретения;

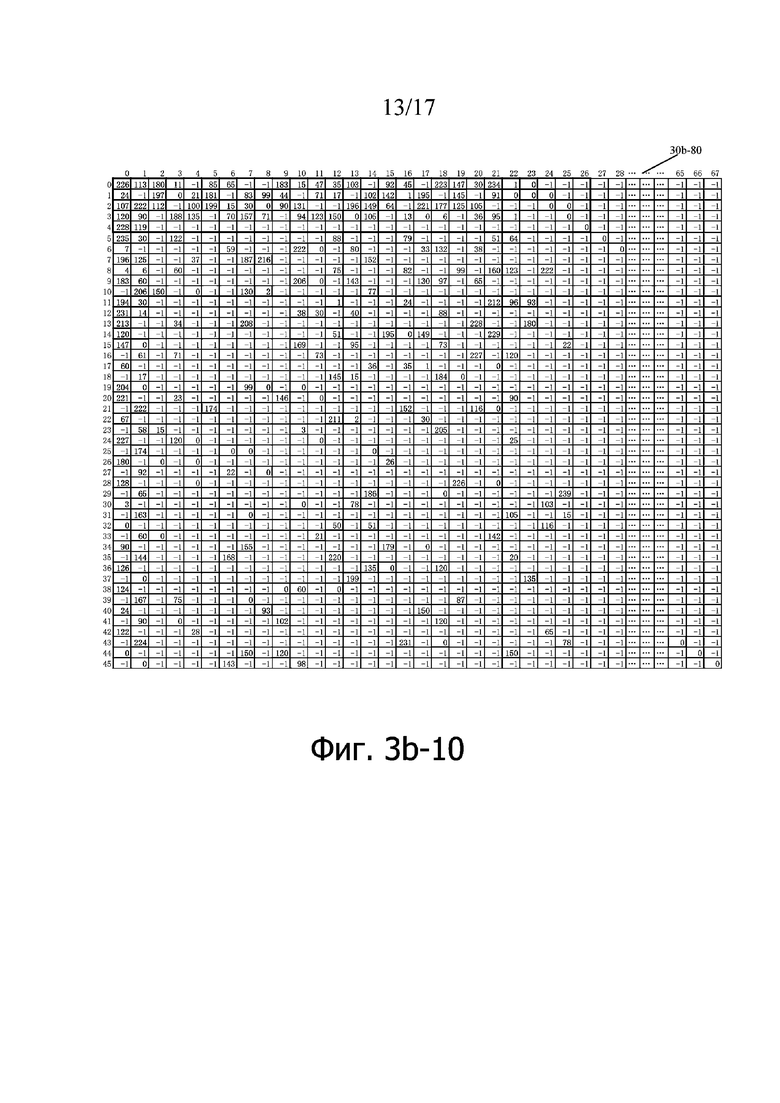

Фиг. 3b-10 является схемой другой базовой матрицы в соответствии с вариантом осуществления настоящего изобретения;

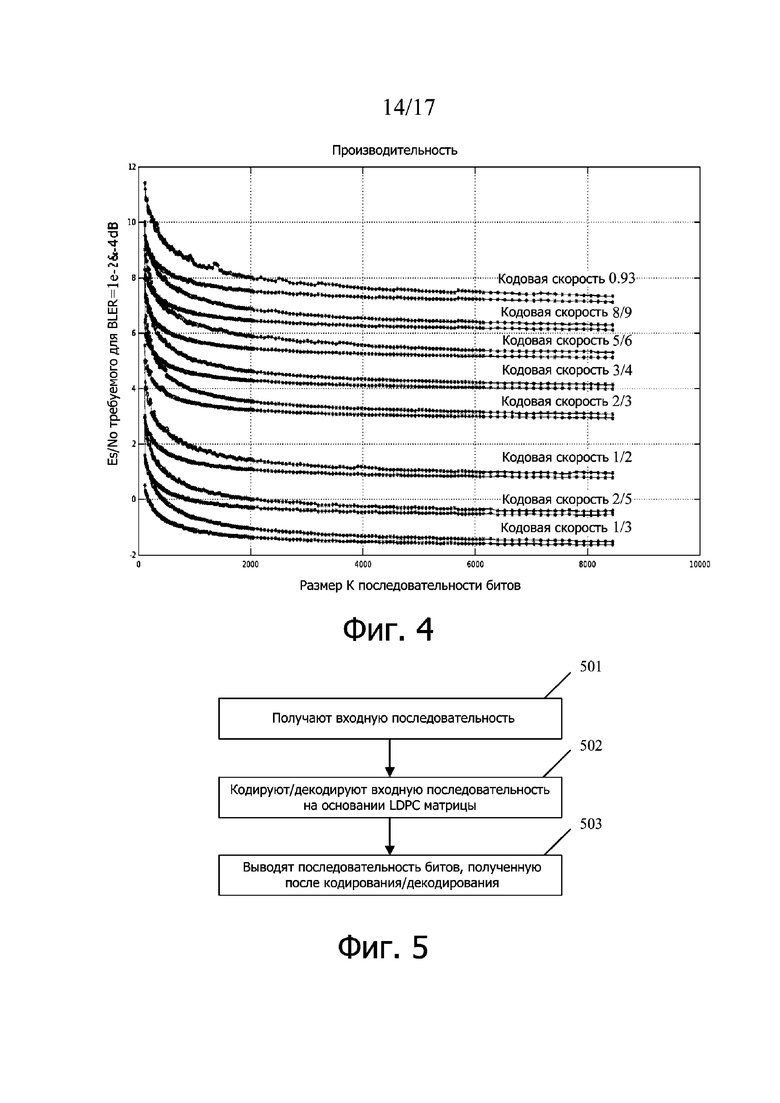

Фиг. 4 является схемой производительности в соответствии с вариантом осуществления настоящего изобретения;

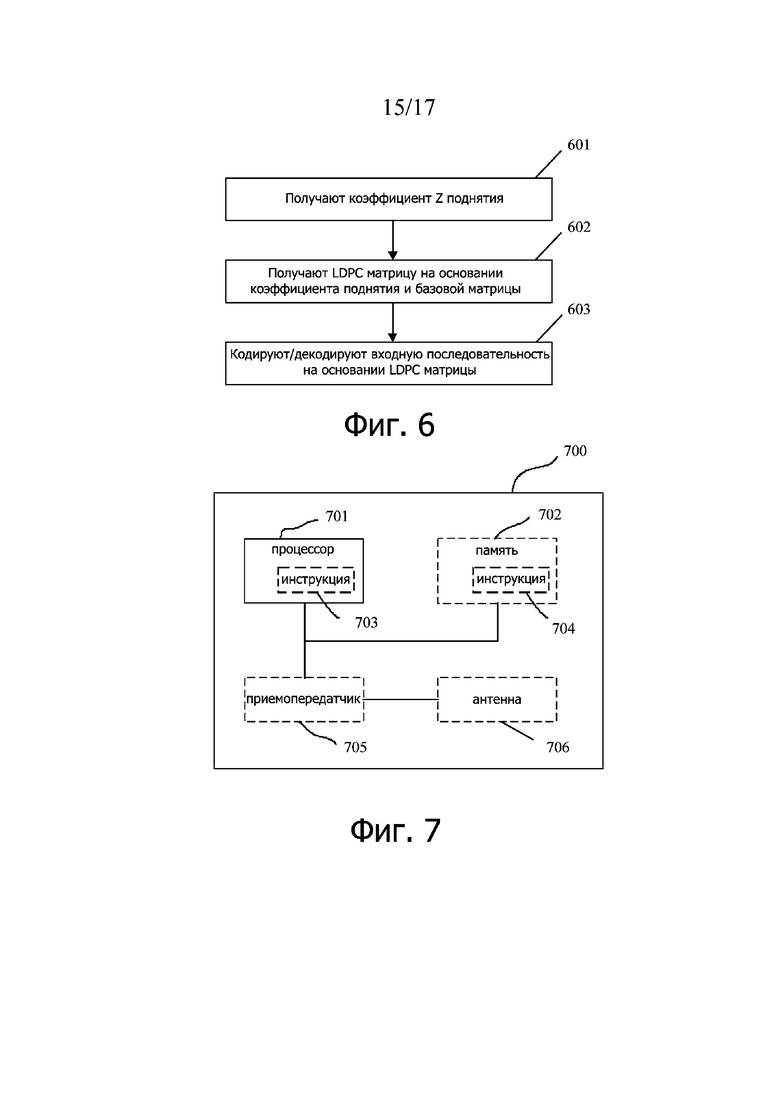

Фиг. 5 является блок-схемой последовательности операций способа обработки информации в соответствии с другим вариантом осуществления настоящего изобретения;

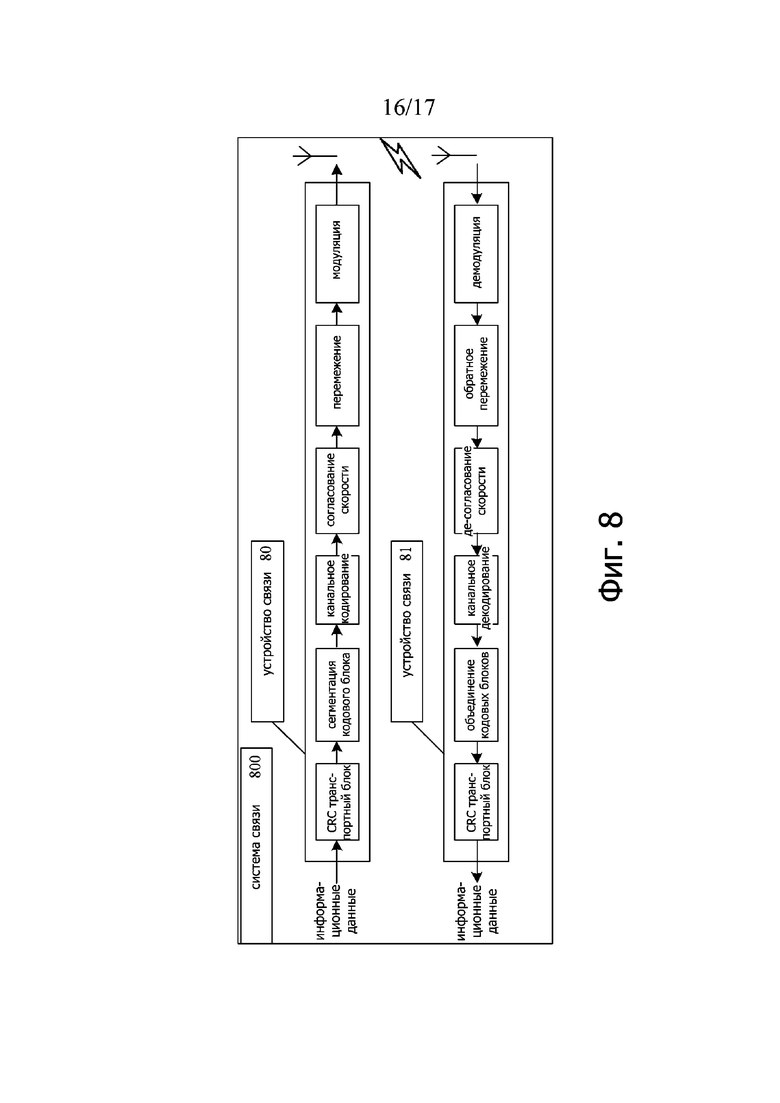

Фиг. 6 является блок-схемой последовательности операций способа обработки информации в соответствии с другим вариантом осуществления настоящего изобретения;

Фиг. 7 является схемой устройства обработки информации в соответствии с другим вариантом осуществления настоящего изобретения;

Фиг. 8 является схемой системы связи в соответствии с другим вариантом осуществления настоящего изобретения; и

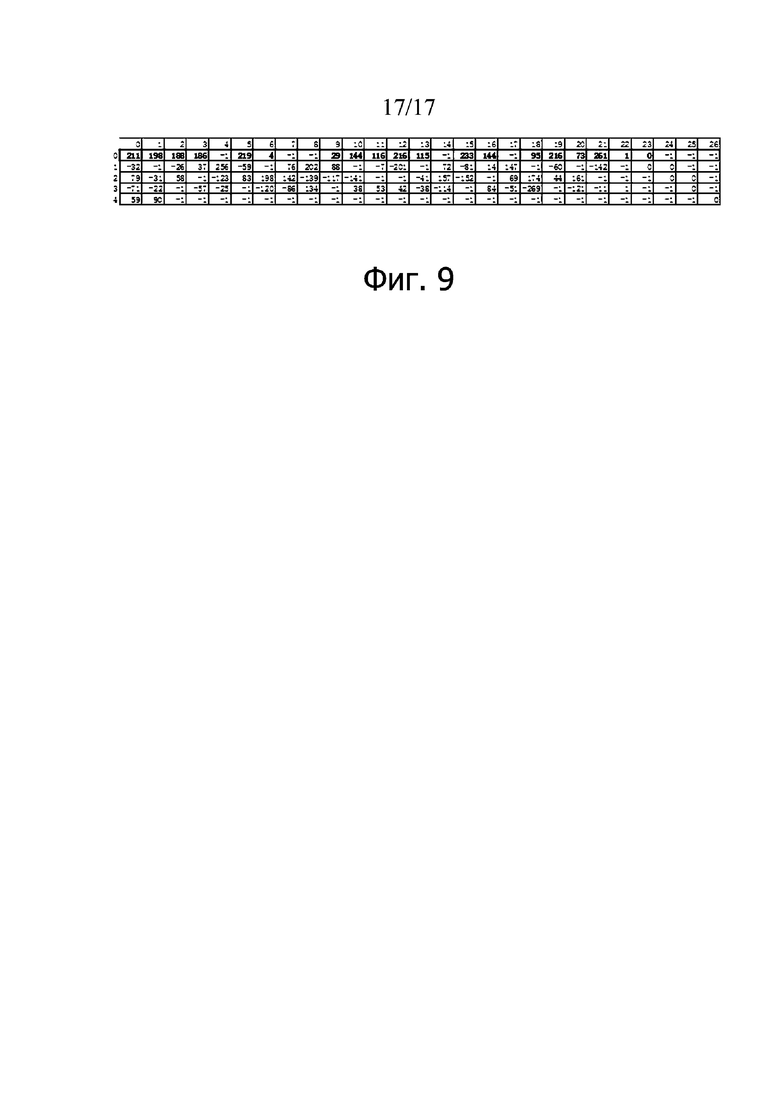

Фиг. 9 является схемой значений сдвига базовой матрицы в соответствии с другим вариантом осуществления настоящего изобретения.

Описание вариантов осуществления

С целью облегчения понимания, ниже приведены некоторые термины, используемые в настоящем изобретении.

В настоящем изобретении термины «сеть» и «система» обычно используют взаимозаменяемо, и термины «приспособление» и «устройство» также обычно используют взаимозаменяемо. Специалист в данной области может понять значения терминов. «Устройство связи» может быть микросхемой (такой как микросхема основной полосы частот, микросхема цифровой обработки сигналов или микросхема общего назначения), терминалом, базовой станцией или другим сетевым устройством. Терминал представляет собой устройство, имеющее функцию связи, и может включать в себя портативное устройство, автомобильное устройство, носимое устройство, вычислительное устройство, другое устройство обработки, подключенное к беспроводному модему, или тому подобное, которое имеет функцию беспроводной связи. Терминал может иметь разные названия в разных сетях, например, устройство пользователя, мобильная станция, абонентское устройство, станция, сотовый телефон, персональный цифровой помощник, беспроводной модем, устройство беспроводной связи, портативное устройство, портативный компьютер, беспроводной телефон и станция беспроводной локальной сети. Для простоты описания в настоящем изобретении эти устройства кратко упоминаются как терминал. Базовая станция (base station, BS) также может называться устройством базовой станции и представляет собой устройство, развернутое в сети радиодоступа для обеспечения функции беспроводной связи. Базовая станция может иметь разные названия в разных системах беспроводного доступа. Например, базовая станция в сети универсальной системы мобильной связи (Universal Mobile Telecommunications System, UMTS) упоминается как NodeB (NodeB), базовая станция в LTE сети упоминается как развитый NodeB (evolved NodeB, eNB или eNodeB), базовая станция в сети «Новое радио» (new radio, NR) упоминается как точка приема передачи (transmission reception point, TRP) или NodeB следующего поколения (generation nodeB, gNB) или базовая станция в другой усовершенствованной сети может иметь другое название. Данный аспект не ограничен в настоящем изобретении.

Далее приведено описание технических решений в вариантах осуществления настоящего изобретения со ссылкой на прилагаемые чертежи в вариантах осуществления настоящего изобретения.

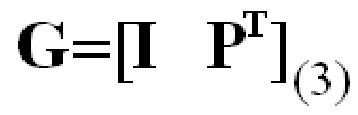

LDPC код может быть определен с использованием матрицы H проверки на четность. Матрица H проверки на четность для LDPC кода может быть получена с использованием базового графа (base graph) и значений сдвига. Базовый граф обычно может включать в себя m × n записей матрицы (entry) и может быть представлен с использованием матрицы из m строк и n столбцов. Значением матричного элемента является либо 0, либо 1. Элемент, значение которого равно 0, иногда называют нулевым элементом, который может быть заменен на нулевую матрицу (zero matrix) размера Z × Z. Элемент, значение которого равно 1, иногда называют ненулевым элементом, который может быть заменен матрицей круговой перестановки размера Z × Z. Другими словами, каждый элемент матрицы представляет собой одну нулевую матрицу или одну матрицу круговой перестановки. Фиг. 1 показывает пример 10a базового графа LDPC кода, в котором m = 5 и n = 27 и который имеет QC структуру. Следует отметить, что в этой спецификации просто для простоты описания индексы строк и индексов столбцов базового графа и матрицы нумеруются, начиная с 0. Например, столбец 0 представляет первый столбец базового графа и матрицы, и первый столбец представляет второй столбец базового графа и матрицы, строка 0 представляет первую строку базового графа и матрицы, строка 1 представляет вторую строку базового графа и матрицы и так далее. Следует понимать, что строки и столбцы базового графа или базовой матрицы нумеруют различными способами и настоящее изобретение не ограничено конкретным способом нумерации.

Следует понимать, что индексы строк и индексы столбцов могут альтернативно быть пронумерованы, начиная с 1, и в этом случае, индексы строк и индексов столбцов, показанные в этой спецификации, увеличиваются на 1, чтобы получить соответствующие индексы строк и индексов столбцов. Например, если номера строк или индексы столбцов нумеруют начиная с 1, то столбец 1 представляет первый столбец базового графа и матрицы, столбец 2 представляет второй столбец базового графа и матрицы, строка 1 представляет первую строку базовый граф и матрицы, строка 2 представляет вторую строку базового графа и матрицы и так далее.

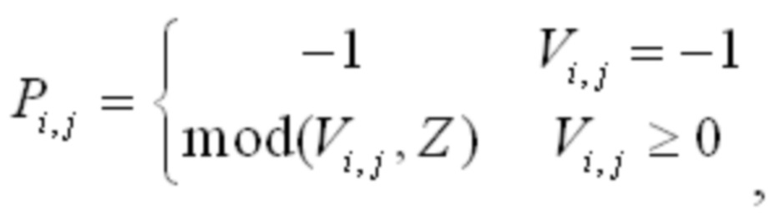

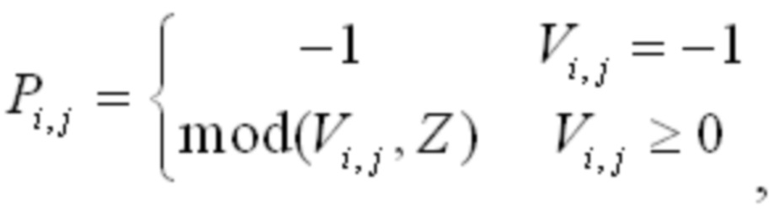

Если значение элемента в строке i и столбце j в базовом графе равно 1, и значение сдвига элемента равно Pi,j, где Pi,j, является целым числом, большим или равным 0, то указывает, что элемент может быть заменен матрицей круговой перестановки размером Z × Z, соответствующей Pi,j,. Матрица круговой перестановки может быть получена путем кругового сдвига единичной матрицы размера Z × Z вправо Pi,j, раз. Можно узнать, что каждый элемент, значение которого в базовом графе равно 0, заменяют нулевой матрицей размером Z × Z, и каждый элемент, значение которого равно 1, заменяют матрицей круговой перестановки размером Z × Z, соответствующей значению сдвига элемента, для получения матрицы проверки на четность LDPC кода. Базовый граф может использоваться для указания позиций значений сдвига, и каждый ненулевой элемент в базовом графе соответствует значению сдвига. Z является положительным целым числом и может также упоминаться как коэффициент поднятия, или иногда может упоминаться как размер поднятия, фактор поднятия или тому подобное. Z может быть определен на основании размера кодового блока, поддерживаемого системой, и размера информационных данных. Можно узнать, что матрица Н проверки на четность имеет размер (m × Z) * (n × Z). Например, если коэффициент Z поднятия равен 4, то каждый нулевой элемент заменяют нулевой матрицей размером 4 × 4 11a. Если P2,3 равно 2, ненулевой элемент в строке 2 и столбце 3 заменяют матрицей 11d круговой перестановки размером 4 × 4, и матрицу 11d получают путем кругового сдвига единичной матрицы 11b 4 × 4 вправо дважды. Если P2,4 равно 0, то ненулевой элемент в строке 2 и столбце 4 заменяют единичной матрицей 11b. Следует отметить, что в настоящем документе описаны только примеры, и примеры не являются ограничением.

Значение Pi,j может зависеть от коэффициента Z поднятия, для элемента 1 (ненулевого элемента) в строке i и столбце j базового графа, Pi,j может быть различным для разных коэффициентов Z поднятия. Для простоты реализации, базовая матрица (base matrix) m строк и n столбцов, которые иногда называют матрицей проверки на четность (PCM), могут быть определены в системе. Элементы в базовой матрице взаимно однозначно соответствуют элементам в базовом графе. Нулевой элемент в базовом графе имеет такую же позицию в базовой матрице. В матрице нулевой элемент представлен значением -1 или нулевым значением. Ненулевой элемент в строке i и столбце j, значение которого равно 1 в базовом графе, соответствует ненулевому элементу в той же позиции в базовой матрице. Ненулевой элемент представлен значением Pi,j, где Pi,j может быть значением сдвига, определенным относительно предустановки или конкретного коэффициента Z поднятия. В вариантах осуществления настоящего изобретения базовая матрица иногда также упоминается как матрица сдвига базового графа.

Как показано на фиг. 1, 10b является базовой матрице, соответствующей базовому графу 10a.

Как правило, базовый граф или базовая матрица LDPC кода могут дополнительно включать в себя p столбцов, соответствующие предопределенным выколотым битам (built-in puncture), и p может быть целым числом в диапазоне от 0 до 2. Эти столбцы могут использоваться при кодировании, но системные биты, соответствующие кодированию с использованием столбцов, соответствующих предопределенным выколотым битам, не отправляют. Кодовая скорость базовой матрицы LDPC кода удовлетворяет R=(n-m)/(n-p). Используя базовый граф 10a в качестве примера, если есть два столбца, соответствующих предопределенным выколотым битам, кодовая скорость составляет (27-5) / (27-2) = 0,88, что приблизительно равно 8/9.

LDPC код, используемый в системе беспроводной связи, представляет собой QC-LDPC код, и часть матрицы, которая соответствует битам четности QC-LDPC кода, имеет двухдиагональную структуру или структуру, похожую на структуру захвата. Это может упростить кодирование и поддерживать гибридное повторение с возрастающей избыточностью. В декодере для QC-LDPC кода QC-LDPC сдвига (QC-LDPC shift network, QSN), Баньян-сети или Бенеша-сети обычно используют для реализации циклического сдвига информации.

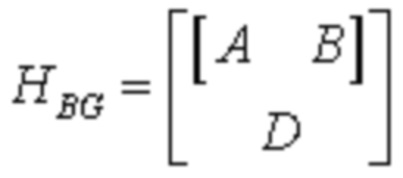

Базовый граф QC-LDPC кода с хищной структурой представляет собой матрицу из m строк и n столбцов. Базовый граф может включать в себя пять подматриц: A, B, C, D и E, где вес матрицы определяется количеством ненулевых элементов, вес строки (row weight) относится к количеству из ненулевых элементов в строке вес столбца (вес столбца) относится к количеству ненулевых элементов в столбце. Как показано в 200 на фиг. 2:

Подматрица A является матрицей, включающей в себя строки mA и столбцы nA, и размер подматрицы A равен mA × nA. Каждый столбец соответствует Z систематических битов в LDPC коде, и систематический бит иногда упоминается как информационный бит.

Подматрица B является матрицей, включающей в себя строки mA и столбцы mA, и размер подматрицы B равен mA × mA. Каждый столбец соответствует Z битам четности в LDPC коде. Подматрица B включает в себя подматрицу B' с двухдиагональной структурой и столбец матрицы, вес столбца которого равен 3 (для короткого столбца с весом 3), столбец веса 3 может быть расположен с левой стороны подматрицы B', как показано на 20а на фиг. 2. Подматрица B может дополнительно включать в себя один или несколько столбцов матрицы, вес столбца которых равен 1 (для короткого столбца веса 1). Например, возможная реализация показана на 20b или 20c на фиг. 2.

Обычно матрица, сгенерированная на основании подматрицы A и подматрицы B, может упоминаться как базовая матрица и может использоваться для поддержки кодирования с высокой скоростью кодирования.

Подматрица C является полностью нулевой матрицей и имеет размер mA × mD.

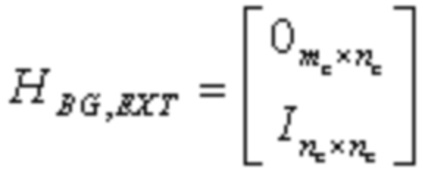

Подматрица E является единичной матрицей и имеет размер mD × mD.

Подматрица D имеет размер mD (nA + mA) и может обычно использоваться для генерирования битов четности для низкой кодовой скорости.

Понятно, что базовый граф описан выше с точки зрения математического определения. Поскольку подматрица C является нулевой матрицей и E является единичной матрицей, в возможной реализации может использоваться матрица, включающая в себя подматрицу A и подматрицу B, или матрица, включающая в себя подматрицу A, подматрицу B и подматрицу D просто представлять базовый граф матрицы при кодировании или декодировании.

Поскольку подматрица C и подматрица E имеют относительно определенные структуры, структуры подматрицы A, подматрицы B и подматрицы D являются одним из факторов, влияющих на производительность кодирования и декодирования LDPC кода.

Когда для кодирования используют LDPC матрицу с хищной структурой, в возможной реализации матрица, включающая в себя подматрицу A и подматрицу B, другими словами, базовую матрицу, могут сначала использовать для кодирования для получения одного или более битов четности, соответствующих подматрице B, и затем используют всю матрицу для кодирования для получения одного или нескольких битов четности, соответствующих подматрице E. Поскольку подматрица B может включать в себя подматрицу B' с двухдиагональной структурой и один или более столбцов веса 1, во время кодирования сначала могут быть получены биты четности, соответствующие двухдиагональной структуре, а затем могут быть получены биты четности, соответствующие столбцам веса 1.

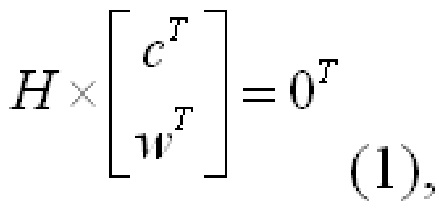

Нижеследующее обеспечивает примерную реализацию кодирования. Предполагают, что основной матрицей, включающей в себя подматрицу A и подматрицу B, является Hcore. Последняя строка и последний столбец в Hcore удаляют из Hcore, другими словами, столбец весом 1 и строка, в которой ненулевой элемент в столбце веса 1 расположен в Hcore, удалены из Hcore для получения матрицы Hcore-dual. Часть битов четности Hcore-dual представлена He = [He1 He2]. He1 является столбцом с весом 3, и He2 имеет двухдиагональную структуру. Согласно определению LDPC матрицы, Hcore-dual⋅[S Pe]T = 0, где S является входной последовательностью и представлена вектором информационных битов, Pe является вектором, включающим в себя биты четности, и [SPe]T представляет собой транспонированную матрицу, образованную входной последовательностью S и Pe. Следовательно, биты четности, соответствующие Hcore-dual, могут быть сначала вычислены на основании входной последовательности S и Hcore-dual, где входная последовательность S включает в себя все информационные биты. Затем биты четности, соответствующие одному или нескольким столбцам веса 1 в подматрице B, вычисляют на основании полученных битов четности, соответствующих Hcore-dual и входной последовательности S. В этом случае, могут быть получены все биты четности, соответствующие подматрице B, Затем, биты четности, соответствующие подматрице E, получают путем кодирования подматрицы D и на основании входной последовательности S и битов четности, соответствующих подматрице B. Таким образом, получают все информационные биты и все биты четности. Эти биты образуют кодированную последовательность, другими словами, LDPC кодовое слово (слова).

Возможно, кодирование LDPC кода может дополнительно включать в себя операцию укорочения (shortening) и операцию выкалывания (puncturing). Укороченные биты и выколотые биты не отправляют.

Укорочение обычно выполняется, начиная с последнего бита информационных битов, и может выполняться различными способами. Например, для количества укороченных битов, равного s0, последние s0 битов во входной последовательности S могут быть установлены как известные биты, например, установить на 0 или ноль, или другое значение, чтобы получить входную последовательность S', и затем кодируют входную последовательность S' с использованием LDPC матрицы. В другом примере, последние (s0 mod Z) биты во входной последовательности S могут быть установлены как известные биты, например, равны 0 или нулю, или другому значению для получения входной последовательности S', и последние  столбцы в подматрица A удаляют для получения LDPC матрицы H', и кодируют входную последовательность S' с использованием LDPC матрицы H', или последние

столбцы в подматрица A удаляют для получения LDPC матрицы H', и кодируют входную последовательность S' с использованием LDPC матрицы H', или последние  столбцы в подматрице A не участвуют в кодировании входной последовательности S'. После кодирования укороченные биты не отправляют.

столбцы в подматрице A не участвуют в кодировании входной последовательности S'. После кодирования укороченные биты не отправляют.

Выкалывание может быть выполнено на предопределенном выколотом бите (битах) или бите (битах) четности во входной последовательности. Выкалывание бита (битов) четности обычно выполняют, начиная с последнего бита в битах четности. Альтернативно, выкалывание бита (битов) четности может выполняться в соответствии с предварительно установленным порядком выкалывания системы. В возможной реализации сначала кодируют входную последовательность, а затем, на основании количества p битов, которые должны быть выколоты, выбирают последний бит (биты) в битах четности, или p бит (биты) выбирают на основании предустановленной последовательности выкалывания в системе, где p бит (биты) не отправляют. В другой возможной реализации могут быть определены p столбцов, соответствующих выколотым битам в матрице, и p строк, в которых расположены ненулевые элементы в этих столбцах, и строки и столбцы не участвуют в кодировании и, следовательно, не генерируют соответствующие биты четности.

Следует отметить, что реализации кодирования просто используется в качестве примера в данном документе, и другая реализация кодирования, известная специалисту в данной области техники, может быть использована на основании базового графа и/или базовых матриц, предоставленных в настоящем изобретении без ограничений. В настоящем изобретении выполняют декодирование с использованием множества способов декодирования, например, способа декодирования с минимальной суммой (MS) или способа декодирования с распространением степени уверенности. Способ декодирования MS иногда также упоминается как способ лавинного декодирования MS. Например, инициализируют входную последовательность и выполняют итерацию для инициализированной входной последовательности. После итерации выполняют жесткое обнаружение, и проверяют результат жесткого решения. Если результат декодирования соответствует уравнению проверки на четность, декодирование завершается успешно, итерационная обработка заканчивается, и выводят результат решения. Если результат декодирования не соответствует уравнению проверки на четность, итерация выполняется снова с максимальным количеством итераций. Если проверка по-прежнему не проходит, при достижении максимального количества итераций, декодирование завершается неудачно. Очевидно, что специалисту в данной области техники понятно, что принцип декодирования MS общеизвестен, и подробности в данном документе не описаны.

Следует отметить, что способ декодирования просто используется в качестве примера в данном документе, и другой известный способ декодирования для специалиста в данной области техники может использоваться на основании базового графа и/или базовой матрицы, предоставленной в настоящем изобретении без ограничений.

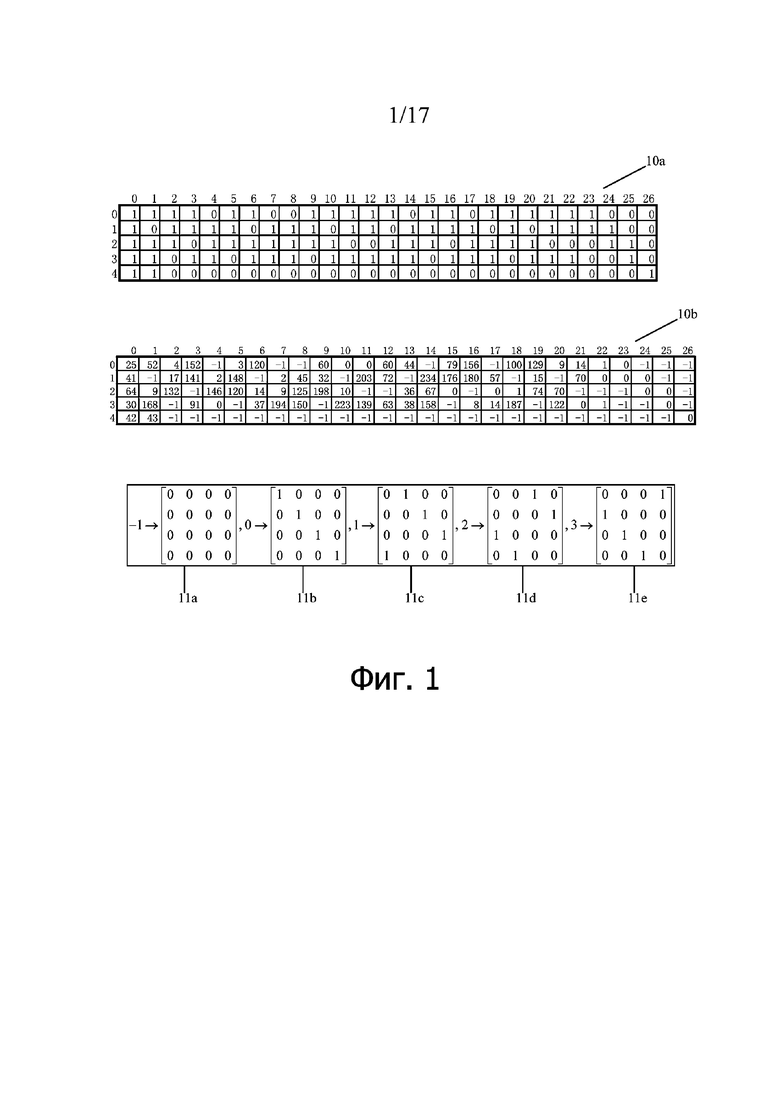

LDPC код обычно может быть получен на основании схемы базового графа или базовой матрицы. Например, верхний предел производительности LDPC кода может быть определен путем выполнения эволюции плотности на базовом графе или базовой матрице, и определяют минимальный уровень ошибки LDPC кода на основании значений сдвига в базовой матрице. Повышение производительности кодирования или декодирования и снижение минимального уровня ошибок являются одними из целей разработки базового графа и базовой матрицы. Длина кода широко варьируется в системе беспроводной связи. Например, длина кода может составлять 2560 бит, 38400 бит или тому подобное. На фиг.3а показан пример базового графа 30а LDPC кода. Фиг. с 3b-1 по фиг. 3b-10 являются примерами базовых матриц базового графа 30a, и могут быть удовлетворены требования к производительности для различных длин блоков. Для простоты описания и понимания индексы строк и столбцов отдельно показаны на самой верхней стороне и самой левой стороне на фиг. 3а и фиг. 3b-1 - 3b-10.

На фиг. 3а показан пример базового графа 30а LDPC кода. На чертеже от 0 до 67 (то есть, от столбца 0 до столбца 67) в самой верхней строке указывают индексы столбца, и от 0 до 45 (то есть, от строки 0 до строки 45) в крайнем левом столбце указывают индексы строки. То есть, базовый граф имеет размер 46 строк и 68 столбцов.

В реализации подматрица A и подматрица B могут рассматриваться как базовая матрица базового графа LDPC кода и могут использоваться для кодирования с высокой скоростью кодирования. Матрица, включающая в себя 5 строк и 27 столбцов, как показано на базовом графе 10a, может быть основной матрицей базового графа, которая представляет собой матрицу, включающую 5 строк и 27 столбцов.

В реализации подматрица A может включать в себя один или несколько столбцов, соответствующих встроенным выколотым битам, например, может включать в себя два столбца, соответствующих встроенным выколотым битам. После выкалывания кодовая скорость, которая может поддерживаться базовой матрицей, составляет 0,88.

Подматрица B может включать в себя столбец веса 3, то есть, вес столбца 0 подматрицы B (столбец 22 основной матрицы) равен 3. Подматрица B имеет двухдиагональную структуру, которая включает в себя столбец 1 - столбец 3 (столбец 23 - столбец 25 основной матрицы) и строки 0 - строка 3 подматрицы, и подматрица B дополнительно содержит столбец веса 1 (столбец 26 основной матрицы).

В реализации подматрица А может соответствовать систематическим битам. Систематические биты иногда называют информационными битами. Подматрица A имеет размер mA строк и 22 столбцов, если mA = 5, и подматрица A включает в себя элементы от строки 0 до строки 4 и от столбца 0 до столбца 21 в базовом графе 30a.

В реализации подматрица B может соответствовать битам четности, подматрица B имеет размер mA строк и столбцов mA и включает в себя элементы от строки 0 до строки 4 и от столбца 22 до столбца 26 в базовом графе 30a.

Для получения гибких кодовых скоростей, подматрица C, подматрица D и подматрица E соответствующих размеров могут быть добавлены на основании основной матрицы, чтобы получить разные кодовые скорости. Подматрица C является полностью нулевой матрицей. Подматрица Е является единичной матрицей, размеры матриц определяют в соответствии с кодовой скоростью, и структуры матриц являются относительно фиксированными. Следовательно, производительность кодирования и производительность декодирования, в основном, зависят от основной матрицы и подматрицы D. Строки и столбцы добавляют на основании основной матрицы для формирования соответствующих C, D и E, так что могут быть получены разные скорости кодирования.

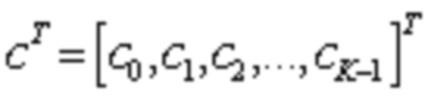

Число столбцов подматрицы D является суммой количества столбцов подматрицы A и количества столбцов подматрицы B, и количество строк подматрицы D, главным образом, связано с кодовой скоростью. Базовый граф 30a используется в качестве примера. Количество столбцов подматрицы D составляет 27 столбцов. Если кодовая скорость, поддерживаемая LDPC кодом, равна Rm, базовый граф или базовая матрица LDPC кода имеет размер m строк и n столбцов, где  и

и  . Если минимальная кодовая скорость Rm равна 1/3, и количество p столбцов, соответствующих встроенным выколотым битам, равно 2, в примере базового графа 30a, n = 68, m = 46, количество строк mD подматрицы D может составлять до m-mA = 46-5 = 41 и 0≤mD≤41.

. Если минимальная кодовая скорость Rm равна 1/3, и количество p столбцов, соответствующих встроенным выколотым битам, равно 2, в примере базового графа 30a, n = 68, m = 46, количество строк mD подматрицы D может составлять до m-mA = 46-5 = 41 и 0≤mD≤41.

Базовый граф 30a используется в качестве примера. Подматрица D может включать в себя mD строки в строке от 5 до 41 в базовом графе 30a.

В настоящем изобретении, при наличии не более одного ненулевого элемента в одном столбце для двух смежных строк в базовом графе, эти две строки взаимно ортогональны. В других столбцах, отличающихся от некоторых столбцов для двух смежных строк в базовом графе, если в одном и том же столбце других столбцов для двух смежных строк содержится не более одного ненулевого элемента, эти две строки являются квазиортогональными. Например, для двух смежных строк, если в столбце есть только один ненулевой элемент, отличный от столбцов, соответствующих встроенным выколотым битам, две соседние строки являются квазиортогональными.

Строка 5 - строка 41 в базовом графе 30a может включать в себя множество строк с квазиортогональной структурой и, по меньшей мере, две строки с ортогональной структурой. Например, строки от 5 до 41 в базовом графе 30a включают в себя, по меньшей мере, 15 строк, которые соответствуют квазиортогональной структуре. Существует не более одного ненулевого элемента в одном и том же столбце в столбцах, отличных от столбцов, соответствующих встроенным выколотым битам в любых двух смежных строках из 15 строк. Строка от 5 до строки 41 в базовом графе 30a может дополнительно включать в себя от 10 до 26 строк, которые соответствуют ортогональной структуре. Другими словами, в этих строках имеется не более одного ненулевого элемента в одном и том же столбце для любых двух соседних строк. Другими словами, в столбце также содержится не более одного ненулевого элемента, соответствующего встроенным выколотым битам.

Если mD = 15, подматрица D в базовом графе LDPC кода имеет размер 15 строк и 27 столбцов. Подматрица D может быть матрицей, состоящей из строки 5 - строки 19 и столбца 0 - столбца 26 в базовом графе 30a. Соответствующая кодовая скорость, поддерживаемая LDPC кодом, составляет 22/40 = 0,55. При этой кодовой скорости базовый граф LDPC кода соответствует матрице, состоящей из строки 0 - строки 19 и столбца 0 - столбца 41 в базовом графе 30a. Подматрица E является единичной матрицей из 15 строк и 15 столбцов, и подматрица C является полностью нулевой матрицей из 5 строк и 15 столбцов.

Если mD = 19, подматрица D в базовом графе LDPC кода имеет размер 19 строк и 27 столбцов. Подматрица D может быть матрицей, состоящей из строки 5 - строки 23 и столбца 0 - столбца 26 в базовом графе 30a. Соответствующая кодовая скорость, поддерживаемая LDPC кодом, составляет 22/44 = 1/2. При этой кодовой скорости базовый граф LDPC кода соответствует матрице, образованной строкой 0 - строкой 23 и столбцом 0 - столбцом 45 в базовом графе 30a. Подматрица E является единичной матрицей из 19 строк и 19 столбцов, и подматрица C является полностью нулевой матрицей из 5 строк и 19 столбцов.

То же самое верно, если mD является другим значением, и подробности не описаны.

В реализации перестановка строк/столбцов может выполняться на базовом графе и/или базовой матрице. Другими словами, может быть выполнена перестановка строк, или перестановка столбцов, или перестановка строк и перестановок столбцов. Операция перестановки строк/столбцов не изменяет вес строки или вес столбца, а также не меняет количество ненулевых элементов. Следовательно, базовый граф и/или базовая матрица, полученные с помощью перестановки строк/столбцов, оказывают ограниченное влияние на производительность системы. В целом, влияние на производительность системы из-за перестановки строк/столбцов является приемлемым и находится в допустимом диапазоне. Например, в некоторых сценариях или в некоторых диапазонах производительность снижается в допустимом диапазоне, в то время, как в некоторых сценариях или в некоторых диапазонах производительность улучшается. В целом, и на общую производительность это никак не сказывается.

Например, строка 34 и строка 36 в базовом графе 30a могут быть взаимозаменяемыми, и столбец 44 и столбец 45 могут быть взаимозаменяемыми. В другом примере подматрица D включает в себя строки mD в матрице F, перестановка строк может не выполняться в строках mD, или перестановка строк может выполняться в одной или нескольких строках строк mD; и подматрица E все еще имеет диагональную структуру, и перестановка строк или перестановка столбцов не выполняется на подматрице E. Например, строки 27 и строка 29 в матрице F взаимозаменяемы, подматрица D включает в себя строки mD в подматрице F, и подматрица E все еще имеет диагональную структуру. Понятно, что если базовый граф или базовая матрица включает в себя подматрицу D, то, когда обмен столбцами выполняется для столбцов в основной матрице, обмен столбцами должен выполняться соответственно на подматрице D.

Матрицы с 30b-10 по 30b-80, показанные на фиг. 3b-1 по фиг. 3b-10 являются соответственно структурами множества базовых матриц базового графа 30a. Положение ненулевого элемента в строке i и столбце j на базовом графе 30a в каждой из матриц с 30b-10 по 30b-80 не изменяется, и значение ненулевого элемента в строке i и столбец j в каждой из матриц являются значениями Vi,j смещения, и нулевой элемент представлен -1 или нулем в базовой матрице. Соответствующая часть подматрицы D в базовых матрицах может включать в себя строки mD в строках с 5 по 45 любой из базовых матриц, и значение mD может быть выбрано на основании разных кодовых скоростей. Понятно, что, если базовый граф является матрицей, полученной путем выполнения преобразования строки/столбца на базовом графе 30a, базовая матрица также является матрицей, полученной путем выполнения преобразования строки/столбца в любой из матриц 30b-10 - 30b-80.

В возможной реализации базовая матрица LDPC кода может включать в себя строки от 0 до строки 4 и от столбца 0 до столбца 26 в любой из матриц с 30b-10 по 30b-80, показанных на фиг. 3b-1 по фиг. 3б-10. В этом случае, матрица, включающая в себя строки от 0 до строки 4 и от 0 до столбца 26 матрицы, показанной на фиг. 3b-1 по фиг. 3b-10, может использоваться в качестве части основной матрицы базовой матрицы. В этой реализации структура другой части базовой матрицы LDPC кода, например, матрицы C, матрицы D или матрицы E, не ограничена. Например, любая структура, показанная на фиг. 3b-1 по фиг. 3b-10, или могут использоваться другие структуры матрицы.

В другом возможном варианте базовая матрица LDPC кода может включать в себя: матрицу, включающую в себя строки от 0 до строки (m-1) и от столбца 0 до столбца (n-1) в любой из матриц с 30b-10 по 30b-80 как показано на фиг. 3b-1 по фиг. 3b-10, где 5≤m≤46, m - целое число, 27≤n≤68, и n - целое число.

В этой реализации структура другой части базовой матрицы LDPC кода не ограничена. Например, могут использовать любую структуру, показанную на фиг. 3b-1 по фиг. 3b-10, могут использоваться и другие структуры матрицы.

В другой возможной реализации базовая матрица LDPC кода может включать в себя: строки от 0 до строки 4 и некоторые из столбцов от 0 до столбца 26 в любой из матриц с 30b-10 по 30b-80, показанных на фиг. 3b-1 по фиг. 3b-10. Например, укорочение (shortening) и/или выкалывание (puncturing) может выполняться на части основной матрицы (строка 0 - строка 4 и столбец 0 - колонка 26), показанной на фиг. 3b-1 по фиг. 3b-10. В реализации базовая матрица LDPC кода может не включать в себя столбец, соответствующий укороченным и/или выколотым битам.

В этой реализации другая часть базовой матрицы LDPC кода не ограничена. Например, могут быть сделаны ссылки на структуры, показанные на фиг. 3b-1 по фиг. 3b-10, или могут использоваться другие структуры.

В другой возможной реализации базовая матрица LDPC кода может включать в себя: матрицу, включающую в себя строки от 0 до строки (m-1) и некоторые из столбца от 0 до столбца (n-1) в любой из матриц с 30b-10 по 30b-80, показанные на фиг. 3b-1 по фиг. 3b-10, где 5≤m≤46, m - целое число, 27≤n≤68, и n - целое число. Например, могут выполнять укорочение (shortening) и/или выкалывание(puncturing) в строке от 0 до строки (m-1) и от столбца 0 до столбца (n-1) в любой из матриц с 30b-10 по 30b-80, как показано на фиг. 3b-1 по фиг. 3b-10. В реализации базовая матрица LDPC кода может не включать в себя столбец (столбцы), соответствующий укороченному и/или выколотому биту (битам). В этой реализации другая часть базовой матрицы LDPC кода не ограничена. Например, могут быть сделаны ссылки на структуры, показанные на фиг. 3b-1 по фиг. 3b-10, или использовать другую структуру.

В реализации операция укорочения может выполняться над информационными битами. Например, любая матрица, показанная на фиг. 3b-1 по фиг. 3b-10 используется в качестве примера. Если один или несколько столбцов от столбца 0 до столбца 21 укорочены, то базовая матрица LDPC кода может не включать в себя один или несколько укороченных столбцов матриц, показанных на фиг. 3b-1 по фиг. 3b-10. Например, если столбец 21 укорочен, базовая матрица LDPC кода может включать в себя: от столбца 0 до столбца 20 и от столбца 22 до столбца 26 в любой из матриц с 30b-10 по 30b-80. Для матрицы, включающей в себя строки от 0 до строки 4, от столбца 0 до столбца 20 и от столбца 22 до столбца 26 в любой из матриц с 30b-10 по 30b-80, кодовая скорость, поддерживаемая матрицей в этом случае, составляет 7/8,

В другой реализации выкалывание может выполняться над битами четности. Например, любая матрица, показанная на фиг. 3b-1 по фиг. 3b-10 используется в качестве примера, и один или несколько столбцов от столбца 22 до столбца 26 выколоты. Базовая матрица LDPC кода может не включать в себя выколотый один или несколько столбцов в матрицах, показанных на фиг. 3b-1 по фиг. 3b-10. Например, если столбец 26 выколот, то базовая матрица LDPC кода может включать в себя: от столбца 0 до столбца 25 в любой из матриц с 30b-10 по 30b-80.

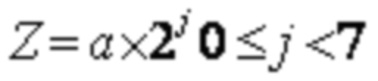

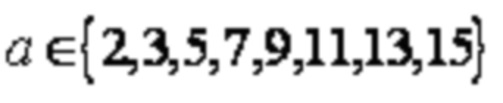

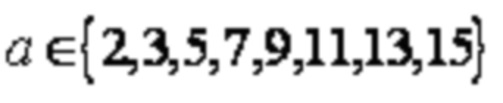

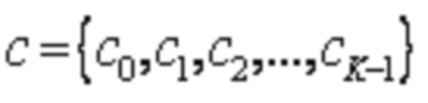

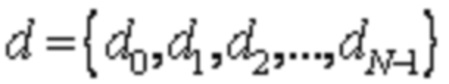

Для LDPC кода предназначены различные коэффициенты Z поднятия для поддержки последовательностей информационных битов различной длины. В возможной реализации могут использоваться разные базовые матрицы для разных коэффициентов поднятия для получения относительно высокой производительности. Например, коэффициенты Z = a × 2j поднятия, где 0 ≤ j <7, и  . Таблица 1 представляет собой возможно поддерживаемый набор коэффициентов поднятия {2, 3, 4, 5, 6, 7, 8, 9, 10, 11, 12, 13, 14, 15, 16, 18, 20, 22, 24, 26, 28, 30, 32, 36, 40, 44, 48, 52, 56, 60, 64, 72, 80, 88, 96, 104, 112, 120, 128, 144, 160, 176, 192, 208, 224, 240, 256, 288, 320, 352, 384}. Каждая из ячеек, за исключением самой верхней строки и самого левого столбца, представляет значение Z, соответствующее значениям соответствующих a и j. Например, для столбца, в котором a = 2, и строки, в которой j = 1, Z = 4. Для другого примера, для a = 11 и j = 3, Z = 88. По аналогии подробности не описаны.

. Таблица 1 представляет собой возможно поддерживаемый набор коэффициентов поднятия {2, 3, 4, 5, 6, 7, 8, 9, 10, 11, 12, 13, 14, 15, 16, 18, 20, 22, 24, 26, 28, 30, 32, 36, 40, 44, 48, 52, 56, 60, 64, 72, 80, 88, 96, 104, 112, 120, 128, 144, 160, 176, 192, 208, 224, 240, 256, 288, 320, 352, 384}. Каждая из ячеек, за исключением самой верхней строки и самого левого столбца, представляет значение Z, соответствующее значениям соответствующих a и j. Например, для столбца, в котором a = 2, и строки, в которой j = 1, Z = 4. Для другого примера, для a = 11 и j = 3, Z = 88. По аналогии подробности не описаны.

Таблица 1

Набор коэффициентов подъема, поддерживаемый базовым графом, может быть всеми или некоторыми из коэффициентов поднятия в таблице 1, например, может быть {24, 26, 28, 30, 32, 36, 40, 44, 48, 52, 56, 60, 64, 72, 80, 88, 96, 104, 112, 120, 128, 144, 160, 176, 192, 208, 224, 240, 256, 288, 320, 352, 384}, в которых Z больше чем или равно 24. Для другого примера, набор коэффициентов поднятия может быть набором объединения одного или нескольких из {2, 3, 4, 5, 6, 7, 8, 9, 10, 11, 12, 13, 14 , 15, 16, 18, 20, 22} и {24, 26, 28, 30, 32, 36, 40, 44, 48, 52, 56, 60, 64, 72, 80, 88, 96, 104, 112 120, 128, 144, 160, 176, 192, 208, 224, 240, 256, 288, 320, 352, 384}. Следует отметить, что здесь приведены только примеры. Набор коэффициентов поднятия, поддерживаемый базовым графом, может быть разделен на различные поднаборы на основе значения a. Например, если a = 2, подмножество коэффициента Z поднятия может включать в себя один или несколько из {2, 4, 8, 16, 32, 64, 128, 256}. В другом примере, если a = 3, подмножество коэффициента Z поднятия может включать в себя один или несколько из {3, 6, 12, 24, 48, 96, 192, 384} и так далее.

Набор коэффициентов поднятия, поддерживаемый базовым графом, может быть разделен на основании различных значений, и определена соответствующая базовая матрица.

Если a = 2 или значение коэффициента Z поднятия равно одному из {2, 4, 8, 16, 32, 64, 128, 256}, базовая матрица может включать в себя строки от 0 до строки 4 и от столбца 0 до столбца 26 в матрице 30b-10 или 30b-11; или базовая матрица включает в себя строки от 0 до строки (m-1) и от 0 до столбца (n-1) в матрице 30b-10 или 30b-11, где 5≤m≤46, m является целым числом, 27≤n≤68 и n является целым числом; или базовая матрица включает в себя строки от 0 до строки (m-1) и некоторые из столбцов от 0 до столбца (n-1) в матрице 30b-10 или 30b-11, где 5≤m≤46, m является целым числом, 27≤n≤68 и n является целым числом.

Если a = 3 или значение коэффициента Z поднятия равно одному из {3, 6, 12, 24, 48, 96, 192, 384}, базовая матрица может включать в себя строки от 0 до строки 4 и от столбца 0 до столбца 26 в матрице 30b-20 или 30b-21; или базовая матрица включает в себя строки от 0 до строки (m-1) и от 0 до столбца (n-1) в матрице 30b-20 или 30b-21, где 5≤m≤46, m является целым числом, 27≤n≤68 и n является целым числом; или базовая матрица включает в себя строки от 0 до строки (m-1) и некоторые из столбца от 0 до столбца (n-1) в матрице 30b-20 или 30b-21, где 5≤m≤46, m является целым числом, 27≤n≤68 и n является целым числом.

Если a = 5 или значение коэффициента Z поднятия равно одному из {5, 10, 20, 40, 80, 160, 320}, базовая матрица может включать в себя строки от 0 до 4 и от 0 до 26 в матрица 30b-30; или базовая матрица включает в себя строку от 0 до строки (m-1) и от 0 до столбца (n-1) в матрице 30b-30, где 5≤m≤46, m является целым числом, 27≤n≤68 и n является целым числом; или базовая матрица включает в себя строку от 0 до строки (m-1) и некоторые из столбца от 0 до столбца (n-1) в матрице 30b-30, где 5≤m≤46, m является целым числом, 27≤n≤68 и n является целым числом.

Если a = 7 или значение коэффициента Z поднятия равно одному из {7, 14, 28, 56, 112, 224}, базовая матрица может включать в себя строки от 0 до строки 4 и от столбца 0 до столбца 26 в матрице 30b-40; или базовая матрица включает в себя строку от 0 до строки (m-1) и от 0 до столбца (n-1) в матрице 30b-40, где 5≤m≤46, m является целым числом, 27≤n≤68 и n является целым числом; или базовая матрица включает в себя строку от 0 до строки (m-1) и некоторые из столбца от 0 до столбца (n-1) в матрице 30b-40, где 5≤m≤46 m является целым числом, 27≤n≤68 и n является целым числом.

Если a = 9 или значение коэффициента Z поднятия равно одному из {9, 18, 36, 72, 144, 288}, базовая матрица может включать в себя строки от 0 до строки 4 и от столбца 0 до столбца 26 в матрице 30b-50; или базовая матрица включает в себя строку от 0 до строки (m-1) и от 0 до столбца (n-1) в матрице 30b-50, где 5≤m≤46, m является целым числом, 27≤n≤68 и n является целым числом; или базовая матрица включает в себя строку от 0 до строки (m-1) и некоторые из столбца от 0 до столбца (n-1) в матрице 30b-50, где 5≤m≤46 m является целым числом, 27≤n≤68 и n является целым числом.

Если a = 11 или значение коэффициента Z поднятия равно одному из {11, 22, 44, 88, 176, 352}, базовая матрица может включать в себя строки от 0 до строки 4 и от столбца 0 до столбца 26 в матрице 30b-60; или базовая матрица включает в себя строку от 0 до строки (m-1) и от 0 до столбца (n-1) в матрице 30b-60, где 5≤m≤46 m является целым числом, 27≤n≤68 и n является целым числом; или базовая матрица включает в себя строку от 0 до строки (m-1) и некоторые столбцы от 0 до столбца (n-1) в матрице 30b-60, где 5≤m≤46 m является целым числом, 27≤n≤68 и n является целым числом.

Если a = 13 или значение коэффициента Z поднятия равно одному из {13, 26, 52, 104, 208}, базовая матрица может включать в себя строки от 0 до строки 4 и от столбца 0 до столбца 26 в матрице 30b-70; или базовая матрица включает в себя строку от 0 до строки (m-1) и от 0 до столбца (n-1) в матрице 30b-70, где 5≤m≤46 m является целым числом, 27≤n≤68 и n является целым числом; или базовая матрица включает в себя строку от 0 до строки (m-1) и некоторые из столбца от 0 до столбца (n-1) в матрице 30b-70, где 5≤m≤46 m является целым числом, 27≤n≤68 и n является целым числом.

Если a = 15 или значение коэффициента Z поднятия равно одному из {15, 30, 60, 120, 240}, базовая матрица может включать в себя строки от 0 до строки 4 и от столбца 0 до столбца 26 в матрице 30b-80; или базовая матрица включает в себя строку от 0 до строки (m-1) и от 0 до столбца (n-1) в матрице 30b-80, где 5≤m≤46 m является целым числом, 27≤n≤68 и n является целым числом; или базовая матрица включает в себя строку от 0 до строки (m-1) и некоторые столбцы от 0 до столбца (n-1) в матрице 30b-80, где 5≤m≤46 m является целым числом, 27≤n≤68 и n является целым числом.

Возможно, для базовой матрицы для LDPC кода значения смещения ненулевых элементов в одном или нескольких столбцах в матрице могут быть увеличены или уменьшены посредством смещений Offsets без существенного влияния на производительность системы. Смещения ненулевых элементов в разных столбцах могут быть одинаковыми или могут быть разными. Например, чтобы компенсировать один или несколько столбцов в матрице, значения компенсации для разных столбцов могут быть одинаковыми или могут отличаться. Это не ограничено в настоящем изобретении.

Незначительное влияние на производительность системы означает, что влияние на производительность системы является приемлемым и находится в допустимом диапазоне в целом. Например, производительность снижается в пределах допустимого диапазона в некоторых сценариях или в некоторых диапазонах. Однако в некоторых сценариях или в некоторых диапазонах производительность улучшается до некоторой степени. Влияние на общую производительность является не существенным.

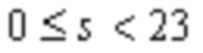

Например, каждое значение смещения, большее или равное 0 в столбце s в любой из матриц с 30b-10 по 30b-80, увеличивается или уменьшается посредством смещений Offsets так что может быть получена матрица Hs смещения матрицы, где Offsets является целым числом, большее или равное 0, и  . Смещения Offsets одного или нескольких столбцов могут быть одинаковыми или разными.

. Смещения Offsets одного или нескольких столбцов могут быть одинаковыми или разными.

На схеме производительности, показанной на фиг. 4, проиллюстрированы кривые производительности LDPC кодов, закодированных на основании матриц с 30b-10 по 30b-80. Горизонтальная координата представляет длину последовательности информационных битов, и единицей длины является бит. Вертикальная координата представляет отношение сигнал/шум символа (Es/N0), необходимое для достижения соответствующего значения BLER. Две строки каждой кодовой скорости соответственно соответствуют двум случаям, когда значения BLER равны 0,01 и 0,0001. При той же кодовой скорости случай, когда BLER равен 0,01, соответствует верхней кривой, а случай, когда BLER равен 0,0001, соответствует нижней кривой. Если каждая кривая является плавной, это указывает на то, что матрица имеет относительно хорошую производительность в случаях различной длины кода.

На фиг. 1 по фиг. 3а и фиг. 3b-1 по фиг. 3b-10 показывают структуры базового графа и базовой матрицы LDPC кода. Для описания структуры базового графа и/или базовых матриц в реализациях настоящего изобретения, структуры могут быть дополнительно описаны в таблице 2-10 и таблице 2-11.

В реализации базовый граф 10a на фиг. 1 представляет собой матрицу из 5 строк и 27 столбцов, и соответствующие параметры могут быть выражены в таблице 2-10.

Таблица 2-10

(row index)

(row degree/row weight)

В реализации базовая матрица, показанная на фиг. 10b на фиг. 1, представляет собой матрицу из 5 строк и 27 столбцов, и соответствующие параметры могут быть выражены в таблице 2-11.

Таблица 2-11

(row index)

(row degree/row weight)

(позиция столбца ненулевого элемента в строке)

(значение смещения ненулевого элемента в строке)

В реализации матрица 30b-10 на фиг. 3b-1 может быть выражена в таблице 3-10.

Таблица 3-10

В реализации матрица 30b-11 на фиг. 3b-2 может быть выражена в таблице 3-11.

Таблица 3-11

В реализации матрица 30b-20 на фиг. 3b-3 может быть выражена в таблице 3-20.

Таблица 3-20

В реализации матрица 30b-21 на фиг. 3b-4 может быть выражена в таблице 3-21.

Таблица 3-21

В реализации матрица 30b-30 на фиг. 3b-5 может быть выражена в таблице 3-30.

Таблица 3-30

В реализации матрица 30b-40 на фиг. 3b-6 может быть выражена в таблице 3-40.

Таблица 3-40

В реализации матрица 30b-50 на фиг. 3b-7 может быть выражена в таблице 3-50.

Таблица 3-50

В реализации матрица 30b-60 на фиг. 3b-8 может быть выражена в таблице 3-60.

Таблица 3-60

В реализации матрица 30b-70 на фиг. 3b-9 может быть выражена в таблице 3-70.

Таблица 3-70

В реализации матрица 30b-80 на фиг. 3b-10 может быть выражена в таблице 3-80.

Таблица 3-80

Очевидно, что фиг. 1 по фиг. 3а, фиг. 3b-1 по фиг. 3b-10, таблица 2-10, таблица 2-11 и таблицы с 3-10 по таблицу 3-80 должны помочь понять схемы базового графа и матрицы, и формы выражений структур не ограничиваются формами выражений в фиг. 1 по фиг. 3а, фиг. 3b-1 по фиг. 3b-10 или таблице 2-10, таблице 2-11 и таблице 3-10 по таблицу 3-80. Может быть использован другой возможный вариант.

В реализации параметр «вес строки» в таблице 2-10, таблице 2-11 и таблице 3-10 по таблицу 3-80 альтернативно может быть опущен. Количество ненулевых элементов в строке может быть получено в соответствии с позициями столбцов ненулевых элементов в строке. Следовательно, информация о весе строки также получена.

В реализации значения параметров в «индексе столбца ненулевого элемента» в таблице 2-10, таблице 2-11 и таблице 3-10 по таблицу 3-80 не могут быть отсортированы в порядке возрастания при условии, что положение столбца ненулевого элемента может быть получено с использованием значений параметров. Дополнительно, значения параметров в «значении смещения ненулевого элемента» в таблице 2-10, таблице 2-11 и таблице 3-10 по таблицу 3-80 не могут быть отсортированы на основании порядка столбцов, при условии, что значения параметров в «значении смещения ненулевого элемента» находятся в однозначном соответствии со значениями параметров в «индексе столбца ненулевого элемента».

В реализации для экономии объема хранения положение ненулевого элемента в части с относительно определенной структурой в базовом графе или базовой матрице может быть вычислено на основе позиции строки или позиции столбца, и могут быть не сохранены.

Например, подматрица E является диагональной матрицей и включает в себя ненулевые элементы только по диагонали матрицы. Значения смещения этих ненулевых элементов на диагонали равны 0. Индекс столбца ненулевого элемента в подматрице E может быть вычислен на основании индекса строки, или индекс строки ненулевого элемента может быть рассчитан на основании индекса столбца. Используя матрицу 30b-50 на фиг. 3b-7 в качестве примера, индекс столбца ненулевого элемента в строке me является столбец (me + Kb), где me≥4 и Kb = 22. Например, индекс столбца ненулевого элемента в строке 7 является столбцом 29, и значение смещения ненулевого элемента равно 0.

Для другого примера, двухдиагональная структура B' в подматрице B расположена в строке от 0 до строки 3 и от столбца 23 до столбца 25 в матрице 30b-50. Индекс столбца ненулевого элемента в двухдиагональной структуре B' может быть вычислен на основании индекса строки, или позиция строки ненулевого элемента может быть вычислена на основе индекса столбца. Индексы столбцов ненулевых элементов в строке mB включают столбец (mB + Kb) и столбец (mB + Kb + 1), где 0 <mB <3. Индексы столбца ненулевого элемента в строке mB включают в себя столбец (mB + Kb), где mB = 0 или mB = 3. Значение смещения ненулевого элемента в двухдиагональной структуре подматрицы B также равно 0. Можно также узнать, что часть матрицы, включающая в себя столбцы 23 и 25, которые принадлежат подматрице D, индексы столбцов ненулевые элементы в строке 5 - строке 47 не являются фиксированными, значения смещения ненулевых элементов не равны 0, и положения и значения смещения ненулевых элементов все еще должны быть сохранены.

Для другого примера, для столбца с весом 1 в подматрице B, другими словами, для столбца 26 в матрице 30b-50, индекс столбца ненулевого элемента в строке mB включает в себя столбец (mB + Kb), где mB = 4, и значение сдвига ненулевого элемента также равно 0.

Таблица 3-90 показывает параметры, относящиеся к строкам в матрице 30b-50. Индексы столбцов ненулевых элементов в столбцах с 0 по 25 могут быть сохранены, тогда как индексы столбцов ненулевых элементов в столбцах с 26 по 68 не сохранены. Другими словами, индексы столбцов ненулевых элементов в столбцах веса 1 в подматрице E и подматрице B не сохраняются.

Таблица 3-90

Таблица 3-91 показывает параметры, относящиеся к строкам в матрице 30b-50. Позиции столбцов ненулевых элементов в столбцах с 0 по 26 могут быть сохранены, тогда как позиции столбцов ненулевых элементов в столбцах с 27 по 68 не сохранены. Другими словами, позиции столбцов ненулевых элементов в подматрице E не сохраняют.

Таблица 3-91

В таблицах с 3-10 по 3-91 вес строки является возможным и индекс строки и индексы столбца ненулевых элементов указывают положения столбцов ненулевых элементов в каждой строке, что также упоминается и информация о базовом графе LDPC матрицы. В реализации информация о базовом графе и значениях смещения LDPC матрицы может быть хранена на основании способов, приведенных в таблицах с 3-10 по 3-91.

В другом исполнении базовый граф LDPC матрицы и значения смещения LDPC матрицы могут храниться отдельно. Информация о значениях смещения LDPC матрицы может храниться с использованием индексов строк и значений сдвига ненулевых элементов в таблицах с 3-10 по 3-91. Базовый граф LDPC матрицы может быть сохранен множеством способов, например, может быть сохранен в виде матрицы базового графа 30a, показанного на фиг. 3a, или могут быть сохранены на основании индексов строк и позиций ненулевых элементов в таблицах с 3-10 по 3-91, или могут быть сохранены таким образом, что 1 и 0 в каждой строке или каждом столбце в базовый граф может рассматриваться как двоичные числа, и базовый граф хранится в форме десятичных чисел или шестнадцатеричных чисел для экономии объема хранения. Базовый граф 30a используют в качестве примера. В каждой строке позиции ненулевых элементов в первых 26 столбцах или первых 27 столбцах могут храниться в четырех шестнадцатеричных числах. Например, если первые 26 столбцов в строке 0 являются 11110110 01111101 10111111 00, позиции ненулевых элементов в строке 0 могут быть обозначены как 0xF6, 0x7D, 0xBF и 0x00. Чтобы быть точным, каждые восемь столбцов образуют одну шестнадцатеричную цифру 0 может быть добавлен в последние два или три столбца для получения восьми цифр, так что получается соответствующая шестнадцатеричная цифра. То же самое верно для другой строки, и подробности здесь не описывают снова.

Возможно, в вышеупомянутых различных вариантах значения смещения LDPC могут быть сохранены в другом преобразовании. Например, чтобы облегчить обработку циклического сдвига, может быть сохранена разница между значением смещения и предшествующим значением смещения в столбце, в котором находится значение смещения. Фиг. 9 показывает значения смещения строки 0 в строку 4 и столбца 0 в столбец 26 в матрице 3b-50 после преобразования. В примере, показанном на фиг. 9, строка 0 является начальной строкой, и значение смещения в строке 0 не изменяются. Нулевые элементы в каждой строке не изменяются, и значение смещения ненулевого элемента в каждой строке представляет собой разницу между значением смещения в той же позиции в матрице 30b-50 и предшествующим ненулевым элементом в матрице 30b-50 в столбце, в котором находится значение смещения. При отсутствии ненулевого элемента перед строкой, в которой находится значение смещения и в столбце, в котором находится значение смещения, значение смещения не изменяется. Например, значение смещения в строке 1 и столбце 0 матрицы 30b-50 составляет 179, и значение смещения в строке 1 и столбце 0 на фиг. 9 является разностью -32 между 179 и предшествующим значением 211 смещения в столбце 0. Поскольку элемент в строке 0 и столбце 4 на фиг. 9 представляет собой нулевой элемент, значение смещения в строке 1 и столбце 4 на фиг. 9 соответствует значению смещения в строке 1 и столбце 4 в матрице 30b-50. Элемент в строке 2 и столбце 3 на фиг. 9 является нулевым элементом, и элемент в строке 1 и столбце 3 является ненулевым элементом, и поэтому значение смещения в строке 3 и столбце 3 представляет собой разницу -57 между значением 166 смещения в строке 3 и столбце 3 в матрице 30b-50, и значение 223 смещения в строке 1 и столбце 3 и так далее. Из-за ограниченного пространства другие строки матрицы 30b-50 не показаны на фиг. 9. То же самое относится и к другим строкам, и подробности здесь не описываются снова. Когда разность значений смещения в данном случае является положительным числом, циклическое смещение вправо выполняется на единичной матрице; когда разность является отрицательным числом, выполняют круговое смещение влево на единичной матрице. Соответственно, значение смещения, полученное после перестановки, другими словами, разность значения смещения, может быть сохранено в «значениях смещения ненулевых элементов» в таблице 3-10 - таблице 3-91. Выше приведены только примеры, и примеры не являются ограничением.

Фиг. 5 представляет собой схему процесса обработки данных. Процесс обработки данных может быть реализован с использованием устройства связи. Устройство связи может быть базовой станцией, терминалом или другим объектом, таким как микросхема связи или кодер/декодер.

Часть 501. Получают входную последовательность.

В реализации входная последовательность для кодирования может быть последовательностью информационных битов. Последовательность информационных битов иногда упоминается как кодовый блок (code block), например, может быть выходной последовательностью, полученной после того, как сегментация кодового блока выполнена на транспортном блоке. Возможно, входная последовательность может включать в себя, по меньшей мере, одно из следующего: биты заполнители или биты циклического избыточного кода (CRC). В возможной реализации последовательность информационных битов может быть вставлена в биты заполнители для получения входной последовательности, так что длина входной последовательности составляет K = Kb⋅Z и Z = K/Kb. Последовательность информационных битов может быть вставлена в биты заполнители во время сегментации кодового блока или может быть вставлена после сегментации кодового блока.

В возможной реализации значения битов заполнителей могут быть нулевыми, 0 или другими значениями, согласованными в системе. Таким образом, после кодирования эти биты заполнители могут быть идентифицированы и не отправлены. Настоящее изобретение не ограничивается этим.

В реализации входная последовательность для декодирования может быть последовательностью мягких значений LDPC кода.

Часть 502. Кодирование/декодирование входной последовательности на основании LDPC матрицы, где базовой матрицей LDPC матрицы может быть любая базовая матрица в вышеприведенных примерах.

В реализации LDPC матрица Н может быть получена на основании коэффициента Z поднятия и базовой матрицы.

В реализации параметры, относящиеся к LDPC матрице Н, могут быть сохранены, и параметры включают в себя одно или несколько из следующего:

(a) параметр, используемый для получения любой базовой матрицы, описанной в предшествующих реализациях. Базовая матрица может быть получена на основании параметров и, например, параметры могут быть одним или несколькими из следующих: индекс строки, вес строки, индекс столбца, вес столбца, позиции ненулевого элемента (такого как индексы строки ненулевых элементов или индексы столбца ненулевых элементов), значения смещения базовой матрицы, значения смещения ненулевых элементов и соответствующих позиций, смещения, коэффициента поднятия, базовый граф, кодовая скорость и т.п;

(b) базовая матрица, которая является одной из любых базовых матриц, описанных в предшествующих реализациях;

(c) матрица Hs смещения, полученная смещением, по меньшей мере, одного столбца любой базовой матрицы, перечисленной в предшествующих реализациях;

(d) матрицу, полученную поднятием базовой матрицы или поднятием матрицы Hs смещения базовой матрицы;

(e) базовая матрица, полученная путем выполнения преобразования строки/столбца в любой базовой матрице, перечисленной в предшествующих реализациях или в матрице Hs смещения;

(f) матрицу, полученную поднятием строки/столбца преобразованной базовой матрицы или строки/столбца преобразованной матрицы Hs смещения базовой матрицы; и

(g) матрица, полученную путем укорочения или выкалывания любой базовой матрицы или матрицы Hs смещения базовой матрицы, описанной в предшествующих реализациях.

В возможной реализации входная последовательность может быть кодирована/декодирована на основании LDPC матрицы с низкой плотностью проверки на четность в процессе кодирования/декодирования одним или несколькими из следующих способов: