ОБЛАСТЬ ТЕХНИКИ

Заявляемое изобретение относится к автоматическому тестовому оборудованию (АТО) для испытаний электронных полупроводниковых компонентов, в частности, к устройствам, формирующих цифровые тестовые последовательности с заданными временными параметрами.

УРОВЕНЬ ТЕХНИКИ

Автоматическое тестовое оборудование (АТО) широко используется для функционального контроля (ФК) цифровых интегральных микросхем в процессе их производства, приемосдаточных испытаний и пр.

В процессе выполнения функционального контроля АТО, иногда называемое также «Тестер», генерирует цифровые сигналы воздействия и принимает отклики от объекта контроля (микросхемы).

Полученные отклики сравниваются с ожидаемыми значениями, по результатам сравнения вырабатывается решение БРАК/ГОДЕН.

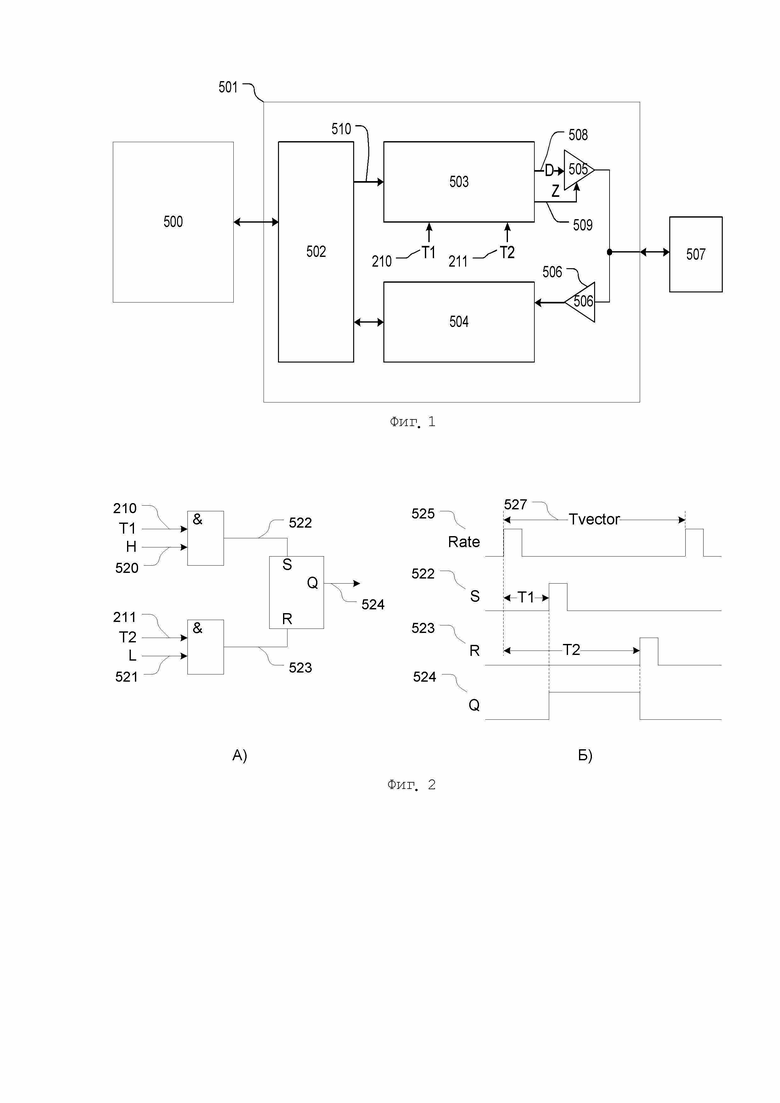

На Фиг. 1 представлена упрощенная структурная схема Тестера АТО.

Тестер включает вычислительный блок (компьютер) 500 и измерительный блок 501.

Вычислительный блок 500 обеспечивает пользовательские интерфейсы и управляет работой измерительного блока 501.

Измерительный блок 501 содержит набор «каналов», каждый из которых формирует воздействие и контролирует сигнал на соответствующем выводе объекта контроля (OK, DUT) 507 (на Фиг. 1 условно показан один канал Тестера). Каждый канал содержит генератор тестовой последовательности (ГТП) 502, форматер 503, обработчик ошибок 504, драйвер 505 и компаратор 506.

Генератор 502 формирует тестовую последовательность (ТП), состоящую из «векторов» (тактов), каждый из которых содержит данные о необходимых воздействиях и ожидаемых откликах ОК (например, состояния лог.0, лог.1, высокоимпедансного Z и др.).

Для поддержки широкой номенклатуры объектов контроля с различными особенностями функционирования, форматер 503 обеспечивает различные стили (shape) преобразования состояний ТП в сигналы воздействия на ОК. Например, в некоторых стилях лог.1 должна интерпретироваться как сигнал на выходе Тестера с высоким напряжением в течение всего вектора ФК, в других - как единичный переход от низкого напряжения к высокому внутри вектора, в-третьих - представлять собой единичный положительный импульс напряжения.

Для получения воздействующего (тестового) сигнала необходимой формы, дополнительно задаются «метки времени» (edge signal). Метки определяют моменты времени, в которые должны осуществляться переходы (фронты) сигнала внутри вектора ФК.

Например, чтобы сформировать импульс, который начинается через 5 нс после начала вектора и имеет ширину 10 нс, одна из меток времени (Т1) 210 должна быть установлена на 5 нс после начала вектора, а другая (Т2) 211 - на 15 не после начала вектора. Используя сигналы меток, форматер 503 вырабатывает на выходе данных 508 импульс заданной формы, который затем подается на драйвер 505. Драйвер 505 транслирует данное воздействие на ОК. В этом примере форматер 503 использует метку Т1 для определения момента, когда драйвер 505 переходит в состояние «HIGH», и метку Т2 - для определения момента, когда драйвер 505 переходит в состояние «LOW».

Для формирования «третьего» (tri-state, Z) состояния на входе ОК форматер 503 имеет дополнительный выход 509, который управляет переводом драйвера 505 в высокоимпедансное состояние.

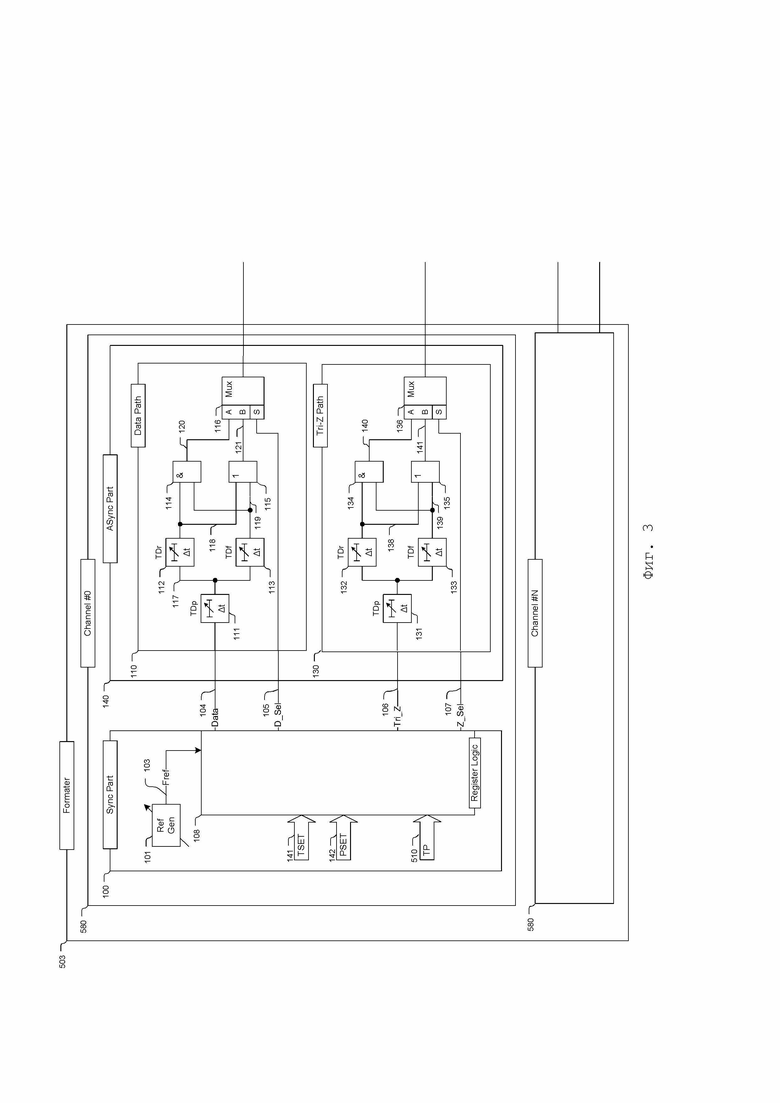

Традиционно, выходной каскад форматера реализуется на базе RS-триггера, как представлено на схеме Фиг. 2(А).

Сигнал «Н» 520 разрешает перевод выхода триггера «Q» 524 по входу установки «S» 522 в состояние лог.1 (фронт, rise), в момент времени, определяемый положением импульса «Т1» 210. Сигнал «L» 521 разрешает перевод выхода триггера «Q» 524 по входу сброса «R» 52 в состояние лог.0 (спад, fall), в момент времени, определяемый положением импульса «Т2» 211.

Известен форматер, который формирует положение импульсов меток времени Т1 и Т2 внутри вектора ФК (tvector) 527 путем задержки на необходимую величину синхросигнала начала вектора «Rate» 525, как представлено на временной диаграмме Фиг. 2.Б (патент US5703515A)

Известны и другие форматеры, использующие RS-триггер в качестве выходного каскада. Они различаются способом формирования сигналов управления выходным каскадом и меток времени, и характеризуется использованием регулируемых линий задержки для точной подстройки положения меток (патенты US5453995A, US7631234B2, US5917834A).

RS-триггер имеет вход установки (Set) и вход сброса (Reset). Когда на вход «Set» подается активный сигнал высокого логического уровня, выход Q триггера переходит в состояние лог.1. Когда на вход «Reset» подается активный сигнал высокого логического уровня, выход Q триггера переходит в состояние лог.0. Когда на оба входа «Set» и «Reset» подается неактивный сигнал низкого уровня, выход Q удерживает текущее состояние.

Одновременная подача на входы «Set» и «Reset» активного сигнала может перевести триггер в неопределенное состояние. Как следствие, недостатками указанных форматеров являются ограничения, накладываемые на допустимые положения временных меток (из-за опасности перехода триггера в неопределенное состояние). Например, это означает, что минимальная длительность импульсов на выходе форматера должна быть соизмерима с шириной импульсов временных меток. Также на высоких частотах (минимальных периодах) ФК возможно реализовать в векторе только один перепад воздействующего сигнала вместо необходимых двух при импульсных стилях форматера.

Наиболее близким к заявляемому изобретению является форматер, снижающий указанные ограничения на выходные сигналы за счет использования механизма «сжатия» (уменьшения ширины) управляющих RS-триггером импульсов. Недостатком данного форматера является сложность конструкции (патент US7987063 В2).

РАСКРЫТИЕ ИЗОБРЕТЕНИЯ

Задачей настоящего изобретения является создание форматера, позволяющего свести к минимуму или полностью устранить вышеприведенные недостатки известных форматеров.

Данная задача решается тем, что положения перепадов тестового сигнала на временной оси (временные метки) задаются неявным образом, за несколько этапов.

Первоначально с помощью регистровых элементов, синхронизированных опорной тактовой частотой, формируется сигнал-прототип (шаблон), в целом имеющий форму соответствующую необходимому тестовому сигналу, но с «грубым» (coarse) заданием моментов перепадов, привязанных к тактам опорной частоты TREF. Далее сигнал-прототип параллельно задерживается на двух переменных линиях задержки ЛЗ с «мелким» (fine) шагом регулировки. Одна ЛЗ определяет точное положение фронтов тестового сигнала внутри вектора (метка Т1), другая ЛЗ - точное положение спадов тестового сигнала внутри вектора (метка Т2). На окончательном этапе формируется выходной (тестовый) сигнал как объединение по «И» (или «ИЛИ», в зависимости от соотношения величин Т1, Т2 и TREF) сигналов с выходов ЛЗ.

При данной организации форматера отпадает необходимость использования в его выходном каскаде RS-триггера, управляемого импульсными сигналами меток времени.

Если конкретнее, предлагается форматер (503), охватывающий несколько идентичных каналов 580 для формирования воздействующих на объект контроля сигналов (122) с заданным положением перепадов, содержащих:

(А) первую часть (100), включающую в себя:

(А1) генератор (101) опорной частоты, выполненный с возможностью формирования электрических импульсов (103) опорной частоты одинаковой точно заданной длительности (Tref)(тактов), и с возможностью перестройки длительности (Tref) импульсов (103), и

(А2) формирователь (108) сигнала-прототипа, подключенный к генератору (101), выполненный таким образом, что имеет возможность генерировать подобный сигнал-прототип (104) предварительно заданной формы длительностью, кратной Tref, и

(В) вторую часть (110), включающую в себя:

(B1) первую регулируемую линию задержки (112), выполненную с возможностью задержки фронта сигнала-прототипа (104) на предварительно заданную величину, с получением первого задержанного сигнала (118), при этом шаг перестройки длительности задержки меньше, а диапазон перестройки - больше длительности импульса (103),

(B2) вторую регулируемую линию задержки (113), выполненную с возможностью задержки спада сигнала-прототипа (104) на предварительно заданную величину, с получением второго задержанного сигнала (119), при этом шаг перестройки длительности задержки меньше, а диапазон перестройки - больше длительности импульса (103),

(B3) логический элемент «И» (114), входы которого подключены к выходам линий (112, 113), выполненный таким образом, что из двух задержанных сигналов-прототипов на выходе из линий задержки (118, 119) он формирует на своем выходе сигнал (120) с более узкими положительными импульсами,

(B4) логический элемент «ИЛИ» (115), входы которого подключены к выходам линий (112, 113), выполненный таким образом, что из двух задержанных сигналов-прототипов (118, 119) на выходе из линий задержки (118, 119) он формирует на своем выходе сигнал (121) с более широкими положительными импульсами и

(B5) мультиплексор (116), управляющий вход которого (105) подключен к формирователю (108), выполненный с возможностью подачи на выход (508) форматера или сигнала (120) с выхода элемента «И» (114), или сигнала (121) с выхода элемента «ИЛИ» (115).

Форматер может дополнительно содержать линию задержки (111), выполненную с возможностью задержки сигнала (104) на величину «Р delay» (201) сведения выходов каналов (508) форматера между собой.

В одном из вариантов воплощения в форматере

формирователь (108) дополнительно выполнен с возможностью формирования сигнала-прототипа (106), длительностью, кратной Tref, а его вторая часть (130) содержит:

первую регулируемую линию задержки (132), выполненную с возможностью задержки фронта сигнала-прототипа (106) на предварительно заданную величину, с получением первого задержанного сигнала (138), при этом шаг перестройки длительности задержки меньше, а диапазон перестройки - больше длительности импульса (103),

вторую регулируемую линию задержки (133), выполненную с возможностью задержки спада сигнала-прототипа (106) на предварительно заданную величину, с получением второго задержанного сигнала (139), при этом шаг перестройки длительности задержки меньше, а диапазон перестройки - больше длительности импульса (103),

логический элемент «И» (134), входы которого подключены к выходам линий (132, 133), выполненный таким образом, что из двух задержанных сигналов-прототипов на выходе из линий задержки (138, 139) он формирует на своем выходе сигнал (140) с более узкими положительными импульсами,

логический элемент «ИЛИ» (115), входы которого подключены к выходам линий (112, 113), выполненный таким образом, что из двух задержанных сигналов-прототипов (118, 119) на выходе из линий задержки (138, 139) он формирует на своем выходе сигнал (141) с более широким положительными импульсами и

мультиплексор (136), управляющий вход которого (107) подключен к формирователю (108), выполненный с возможностью подачи на выход (509) форматера или сигнала (140) с выхода элемента «И» (134), или сигнала (141) с выхода элемента «ИЛИ» (135).

Форматер может дополнительно содержать линию задержки (131), выполненную с возможностью задержки сигнала (106) на величину сведения выходов каналов (509) форматера между собой.

Для лучшего понимания данного изобретения и его вариантов рекомендуется ознакомиться с сопровождающими фигурами чертежей.

Масштаб чертежей условный. Подобные элементы на разных чертежах обозначаются единым сквозным цифровым идентификатором.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

Фиг. 1 изображает упрощенную структурную схему Тестера АТО (уровня техники).

Фиг. 2 изображает схему (А) и временную диаграмму работы (Б) выходного буфера форматера (уровня техники).

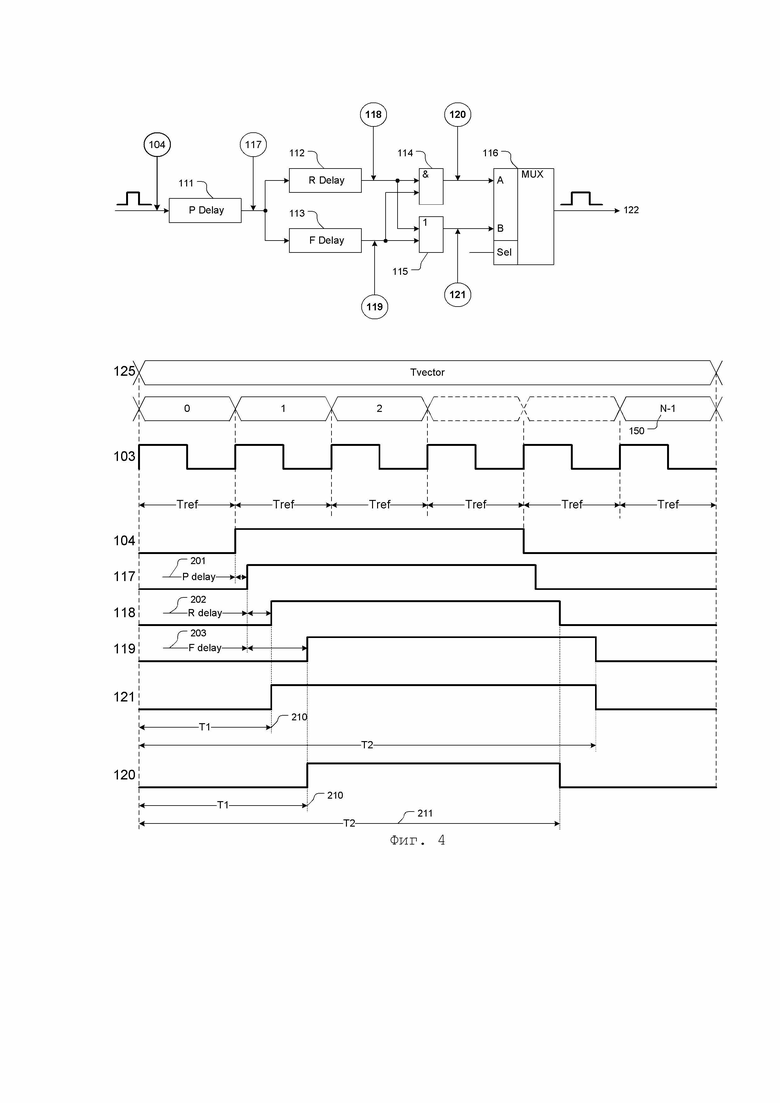

Фиг. 3 изображает упрощенную структурную схему форматера.

Фиг. 4 изображает временную диаграмму работы форматера.

ДЕТАЛЬНОЕ ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Блок-схема форматера представлена на фиг. 3. Условно показан один канал 580 Тестера АТО, устройство остальных каналов -аналогично.

Форматер работает следующим образом.

Выход «D» 508 форматера 503 управляет лог. уровнем на выходе 152 драйвера 505, выход «Z» 509 форматера 503 переводит выход 152 драйвера 505 в высокоимпедансное состояние. Величины меток времени Т1 и Т2, определяющих положение перепадов внутри вектора ФК, могут задаваться независимыми наборами для каждого из сигналов 508 и 509.

В составе форматера 503 можно выделить две части: синхронную 100 и асинхронную 140.

Синхронная часть 100 работает в домене опорной частоты «TREF» 103, вырабатываемой генератором синхросигнала переменной частоты 101. Длительность такта опорной частоты 103 равна TREF (и равна 1 / FREF), как представлено на временной диаграмме фиг. 4.

Один период вектора ФК «TVECTOR» 125 должен содержать целое число тактов опорной частоты 103, в диапазоне от 2 до N, где величина «2» определяется необходимостью наличия двух перепадов сигнала (т.е импульса) в векторе ФК, а величина N определяется минимальной необходимой частотой ФК.

Диапазон перестройки частоты генератора 101 должен быть не уже FFC_MAX…2 × FFC_MAX, где FFC_MAX - максимальная необходимая частота ФК.

Работа регистровой логики 108 синхронизируется синхросигналом опорной частоты 103.

В процессе выполнения ФК на вход регистровой логики 108 поступает тестовая последовательность «ТР» 510 от генератора ТП 502. Дополнительно поступают данные о положении временных меток «TSET» (в терминах тактов опорной частоты 103) и заданных стилях выходных сигналов 104 и 106 «PSET» 142, от внешних по отношению к форматеру 503 узлов измерительного блока Тестера 501 (внешние узлы в данном описании не рассматриваются).

Регистровая логика 108 вырабатывает «сигналы-прототипы» «Data» 104 и «Tri-Z» 106 для последующего управления уровнем и «третьим состоянием» драйвера 505.

Данные сигналы по форме в целом соответствуют необходимым тестовым сигналам, но их перепады «привязаны» к тактам опорной частоты «TREF» 103, что соответствует «грубому» (предварительному) заданию меток времени.

Способ вырабатывания сигналов 104 и 106 в регистровой логике 108 не существенен для рассматриваемого метода формирования меток времени, не влияет на принцип работы форматера и поэтому отдельно не рассматривается.

Асинхронная часть 140 форматера 503 содержит два тракта точной подстройки положения перепадов (меток): тракт подстройки сигнала управления уровнем «Data Path» 110 и тракт подстройки сигнала управления третьим состоянием «Tri-Z Path» 130.

Тракты идентичны по устройству, в дальнейшем рассматривается только тракт «Data Path» 110.

Тракт подстройки 110 содержит три регулируемые линии задержки: «TDP» 111, «TDR» 112 и «TDF» 113. Данные ЛЗ обеспечивают точную подстройку меток времени с «мелким» шагом (условно «мелким», по сравнению с «грубым» шагом - величиной периода опорной частоты 103).

Для нормальной работы форматера диапазон перестройки ЛЗ должен «перекрывать» максимально возможный период опорной частоты «TREF» 103, т.е. составлять от 0 до 1/FFC_MAX, где fFC_MAX - максимальная необходимая частота ФК.

Сигнал-прототип 104 в общем случае представляют собой последовательность импульсов различной ширины. Для примера на фиг. 4 представлен один вектор ФК длиной «N» тактов опорной частоты 150, содержащий два перепада сигнала, т.е. один положительный импульс. Вектора ФК в тестовой последовательности могут содержать два, один или ни одного перепада, что не влияет на описываемый принцип формирования меток времени.

Сигнал 104 поступает на вход вспомогательной ЛЗ 111 и задерживается на величину «Р delay» 201, предназначенную для компенсации временных разбежек выходов каналов 508 форматера (каналов 152 Тестера) между собой. Для упрощения реализации форматера ЛЗ 111 может быть исключена, в этом случае необходимая величина задержки должна быть распределена между другими элементами схемы.

Сигнал 117 с выхода ЛЗ 111 распараллеливается и подается на ЛЗ 112 и 113, одна из которых отвечает за подстройку фронтов тестового сигналов (метка Т1) а другая - за подстройку спадов сигналов (метка Т2). Распределение функций между данными ЛЗ условно, т.к. схема является симметричной.

ЛЗ 112 задерживает сигнал 117 на величину «R delay» 202, формируя сигнал 118.

ЛЗ 113 задерживает сигнал 117 на величину «F delay» 203, формируя сигнал 119.

Сигналы 118 и 119 подаются на схему «И» 114, на выходе 120 которой формируется положительный импульс, с шириной меньше исходного импульса-прототипа и положением перепадов, соответствующих одному набору меток Т1 и Т2. Сигналы 118 и 119 одновременно подаются на схему «ИЛИ» 115, на выходе 121 которой формируется положительный импульс, с шириной больше исходного импульса-прототипа и положением перепадов, соответствующих другому набору меток Т1 и Т2.

Окончательно величины меток Т1 и Т2 задаются путем подачи на выход 122 форматера соответственно или сигнала 120, или сигнала 121 посредством мультиплексора 116, управляемого сигналом выбора «D_Sel» 105. Например, если размер вектора ФК «TVECTOR» 125 равен двум периодам опорной частоты «TREF» 103, а длительность импульса тестового сигнала должна быть меньше периода опорной частоты «TREF» 103, то должна задействоваться схема «И» 114 для сокращения ширины импульса. В общем случае выбор схем «И» 114 или «ИЛИ» 114, т.е. лог.уровень сигнала «D_Sel» 105, определяется соотношением величин tref, N, Т1 и Т2.

Величина частоты опорного генератора 101, параметры регистровой логики 108 «TSET» 141, задержки «Р delay» 201, «R delay» 202, «F delay» 203, а также уровень сигнала 105 выбора входа мультиплексора 116 рассчитываются в вычислительном блоке Тестера 500 перед запуском ФК.

Изобретение относится к области автоматического тестового оборудования для испытаний электронных полупроводниковых компонентов, в частности к устройствам, формирующим цифровые тестовые последовательности с заданными временными параметрами. Техническим результатом является упрощение конструкции форматера. Для реализации технического результата в заявленном решении предусмотрены генератор, формирователь сигнала-прототипа, регулируемые линии задержки, мультиплексор, а также логические схемы «И», «ИЛИ». 3 з.п. ф-лы, 4 ил.

1. Форматер (503), охватывающий несколько идентичных каналов 580 для формирования воздействующих на объект контроля сигналов (122) с заданным положением перепадов, содержащих:

(A) первую часть (100), включающую в себя:

(A1) генератор (101) опорной частоты, выполненный с возможностью формирования электрических импульсов (103) опорной частоты одинаковой точно заданной длительности (Tref)(тактов) и с возможностью перестройки длительности (Tref) импульсов (103), и

(A2) формирователь (108) сигнала-прототипа, подключенный к генератору (101), выполненный таким образом, что имеет возможность генерировать подобный сигнал-прототип (104) предварительно заданной формы длительностью, кратной Tref, и

(B) вторую часть (110), включающую в себя:

(B1) первую регулируемую линию задержки (112), выполненную с возможностью задержки фронта сигнала-прототипа (104) на предварительно заданную величину, с получением первого задержанного сигнала (118), при этом шаг перестройки длительности задержки меньше, а диапазон перестройки больше длительности импульса (103),

(B2) вторую регулируемую линию задержки (113), выполненную с возможностью задержки спада сигнала-прототипа (104) на предварительно заданную величину, с получением второго задержанного сигнала (119), при этом шаг перестройки длительности задержки меньше, а диапазон перестройки больше длительности импульса (103),

(B3) логический элемент «И» (114), входы которого подключены к выходам линий (112, 113), выполненный таким образом, что из двух задержанных сигналов-прототипов на выходе из линий задержки (118, 119) он формирует на своем выходе сигнал (120) c более узкими положительными импульсами,

(B4) логический элемент «ИЛИ» (115), входы которого подключены к выходам линий (112, 113), выполненный таким образом, что из двух задержанных сигналов-прототипов (118, 119) на выходе из линий задержки (118, 119) он формирует на своем выходе сигнал (121) c более широкими положительными импульсами, и

(B5) мультиплексор (116), управляющий вход которого (105) подключен к формирователю (108), выполненный с возможностью подачи на выход (508) форматера или сигнала (120) с выхода элемента «И» (114), или сигнала (121) с выхода элемента «ИЛИ» (115).

2. Форматер по п. 1, характеризующийся тем, что он дополнительно содержит линию задержки (111), выполненную с возможностью задержки сигнала (104) на величину «P delay» (201) сведения выходов каналов (508) форматера между собой.

3. Форматер по любому из пп. 1 или 2, характеризующийся тем, что в нем:

формирователь (108) дополнительно выполнен с возможностью формирования сигнала-прототипа (106) длительностью, кратной Tref, а его вторая часть (130) содержит:

первую регулируемую линию задержки (132), выполненную с возможностью задержки фронта сигнала-прототипа (106) на предварительно заданную величину, с получением первого задержанного сигнала (138), при этом шаг перестройки длительности задержки меньше, а диапазон перестройки больше длительности импульса (103),

вторую регулируемую линию задержки (133), выполненную с возможностью задержки спада сигнала-прототипа (106) на предварительно заданную величину, с получением второго задержанного сигнала (139), при этом шаг перестройки длительности задержки меньше, а диапазон перестройки больше длительности импульса (103),

логический элемент «И» (134), входы которого подключены к выходам линий (132, 133), выполненный таким образом, что из двух задержанных сигналов-прототипов на выходе из линий задержки (138, 139) он формирует на своем выходе сигнал (140) c более узкими положительными импульсами,

логический элемент «ИЛИ» (115), входы которого подключены к выходам линий (112, 113), выполненный таким образом, что из двух задержанных сигналов-прототипов (118, 119) на выходе из линий задержки (138, 139) он формирует на своем выходе сигнал (141) c более широкими положительными импульсами, и

мультиплексор (136), управляющий вход которого (107) подключен к формирователю (108), выполненный с возможностью подачи на выход (509) форматера или сигнала (140) с выхода элемента «И» (134), или сигнала (141) с выхода элемента «ИЛИ» (135).

4. Форматер по п. 3, характеризующийся тем, что он дополнительно содержит линию задержки (131), выполненную с возможностью задержки сигнала (106) на величину сведения выходов каналов (509) форматера между собой.

| US 7987063 В2, 26.07.2011 | |||

| RU 2015140253 A, 30.03.2017 | |||

| US 5453995, 26.09.1995 | |||

| US 8228108 B2, 24.07.2012 | |||

| НИКОНОВ А | |||

| В | |||

| и др.: "Управление в испытательных системах электронной промышленности", Динамика систем, механизмов и машин | |||

| Способ получения цианистых соединений | 1924 |

|

SU2018A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

2021-07-29—Публикация

2020-12-30—Подача