Изобретение относится к области вычислительной техники и может использоваться при построении высоконадежных вычислительных управляющих систем, предназначенных для приема информации от абонентов, обработку принятой информации и выдачу результирующей информации абоненту.

Известна компьютерная система [1], исправляющая одиночную ошибку, которая содержит первый системный модуль с первым процессором, с шиной первого процессора и первой шиной I/O (входа/выхода), второй системный модуль со вторым процессором, с шиной второго процессора и второй шиной I/O, третий системный модуль с третьим процессором, с шиной третьего процессора и третьей шиной I/O, причем первый модуль системы включает первую память, первый процессор, первый блок управления I/O, первый мост, сравнивающий данные первой процессорной шины с данными второй и третьей процессорными шинами, причем первый выход первого модуля соединен с первыми входами второго и третьего модуля, первый выход которого соединен с первым входом первого модуля и вторым входом второго модуля, первый выход которого соединен со вторыми входами первого и третьего модуля, причем в каждом модуле память соединена с процессором, процессор соединен с мостом, мост соединен с блоком управления I/O, выход которого является вторым выходом модуля, причем второй модуль системы включает вторую память, второй процессор, второй блок управления I/O, второй мост, сравнивающий данные второй процессорной шины с данными первой и третьей процессорными шинами, причем третий модуль системы включает третью память, третий процессор, третий блок управления I/O, третий мост, сравнивающий данные третьей процессорной шины с данными первой и второй процессорными шинами.

Данная система не обеспечивает мажорирование двунаправленных линий и не может работать с мультиплексным каналом.

Известна трехканальная резервированная управляющая система [2], исправляющая одиночную ошибку, которая содержит первый системный модуль А, второй системный модуль В, третий системный модуль С, причем каждый модуль А, В, С включает процессор, с шиной процессора P-bus, ОЗУ, ПЗУ, группу мажоритарных элементов, генератор, первую группу, вторую группу, третью группу мажоритарных устройств, контроллер функциональных узлов, первое, второе, третье, четвертое приемо-передающие устройства, первый и второй контроллеры мультиплексного канала обмена, периферийный контроллер, буферное ОЗУ, шину Q-bus и шину L-bus, первая двунаправленная группа входов-выходов которой соединена с двунаправленной группой входов-выходов первого контроллера мультиплексного канала обмена, первый и второй входы которого соединены с выходами первого и второго приемо-передающего устройства, группы входов-выходов которых являются первый и второй группами входов-выходов системы соответственно, третья и четвертая группы входов-выходов которой являются группами входов-выходов третьего и четвертого приемо-передающих устройств, выходы которых соединены с первым и вторым входами второго контроллера мультиплексного канала обмена, группа входов-выходов которого является второй группой входов-выходов шины L-bus, причем первая группа выходов модуля А состоит из первых групп выходов второй и третьей групп мажоритарных устройств и соединена с первыми группами входов второй и третьей групп мажоритарных устройств модулей В и С, первая группа выходов модуля В состоит из первых групп выходов второй и третьей групп мажоритарных устройств модуля В и соединена с первыми группами входов второй и третьей групп мажоритарных устройств модуля А и со вторыми группами входов второй и третьей групп мажоритарных устройств модуля С, первая группа выходов модуля С состоит из первых групп выходов второй и третьей групп мажоритарных устройств модуля С и соединена со вторыми группами входов второй и третьей групп мажоритарных устройств модулей А и В, причем вторая группа выходов второй группы мажоритарных устройств соединена с первой группой входов периферийного контроллера, первая группа входов-выходов которого соединена с первой группой входов-выходов третьей группы мажоритарных устройств, вторая группа входов-выходов которых соединена с первой группой входов-выходов шины Q-bus, вторая группа входов-выходов которой соединена с первой группой входов-выходов контроллера функциональных узлов, вторая группа входов-выходов которого соединена с группами входов-выходов ОЗУ, ПЗУ и первой группой входов-выходов первой группы мажоритарных устройств, вторая группа входов-выходов которых является шиной P-bus и соединена с группой входов-выходов процессора, группа выходов которого соединена с первой группой входов группы мажоритарных элементов, первая группа выходов которых соединена с группой входов процессора, вход которого соединен с выходом генератора, со входами первой, второй и третьей группами мажоритарных устройств, первого и второго контроллеров мультиплексного канала обмена, периферийного контроллера и контроллера функциональных узлов, первая и вторая группы выходов соединены с группами входов ОЗУ и ПЗУ соответственно, третья группа входов-выходов шины L-bus соединена со второй группой входов-выходов периферийного контроллера, вторая группа входов которого соединена со второй группой выходов третьей группы мажоритарных устройств, третья группа входов которых соединена с первой группой входов системы, вторая группа входов которой соединена с первой группой входов первой группы мажоритарных устройств, вторая группа входов которых соединена с третьей группой выходов контроллера функциональных узлов, четвертая группа выходов которого соединена с первой группой входов шины Q-bus, первая группа выходов которой соединена с первой группой входов контроллера функциональных узлов.

Данная система не обеспечивает прием и обработку внешних импульсных и потенциальных сигналов и отсчет временных интервалов.

Описанное устройство как наиболее близкое к предполагаемому принято за прототип.

Задачей изобретения является обеспечение:

• программного доступа к регистрам функциональных узлов (т.е. поддержки обменов на шине Q-bus);

• выдачи запросов на прерывание программы по событиям в функциональных узлах и управления этой выдачей;

• конфигурирования функционального узла таймеров синхронизации (в составе трех ТмрСн), в т.ч. для выбора источника тактовой частоты;

• отсчета времени на таймерах синхронизации;

• приема и обработки 16 внешних импульсных сигналов или

приема и обработки 7 внешних импульсных сигналов и регистрации сигналов одноканальных сбоев по 9 входным каналам;

• приема и обработки 16 внешних потенциальных сигналов;

• управления выдачей потенциальных сигналов (релейных команд) программируемой длительности;

• управления выдачей в параллельном коде потенциальных сигналов программно-формируемого 8-битового кода программной телеметрии;

• управления выдачей в параллельном коде потенциальных сигналов программно-формируемого 2-битового кода "режим работы изделия".

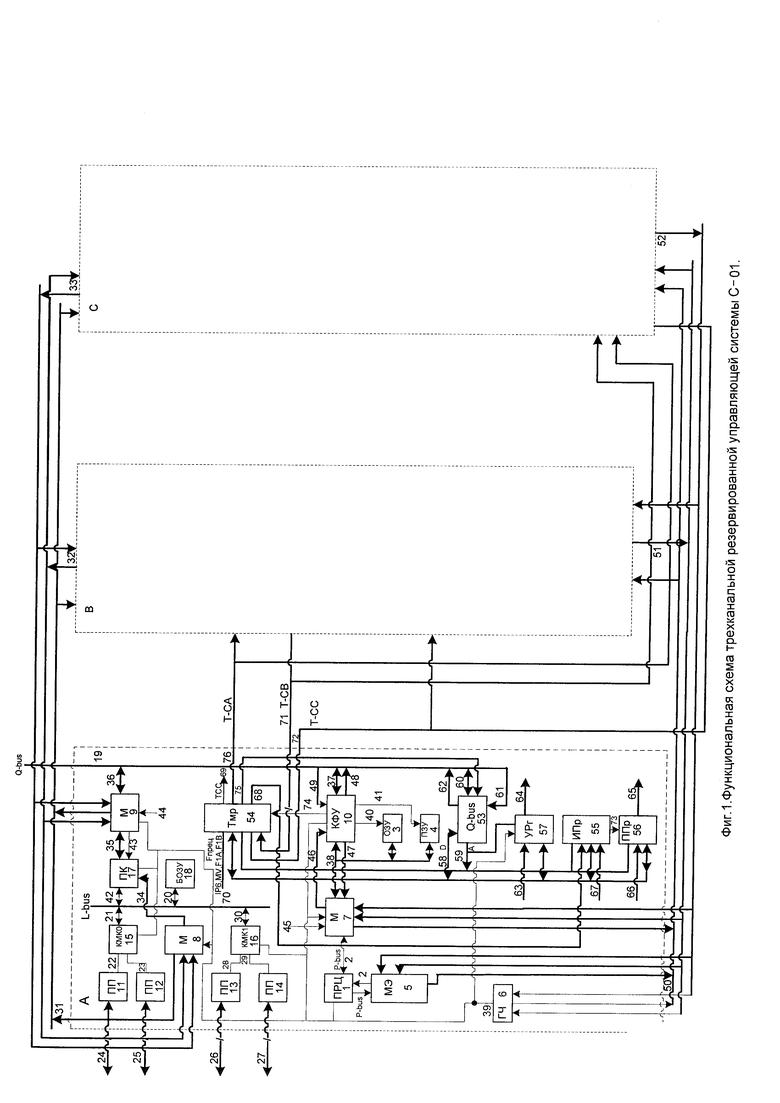

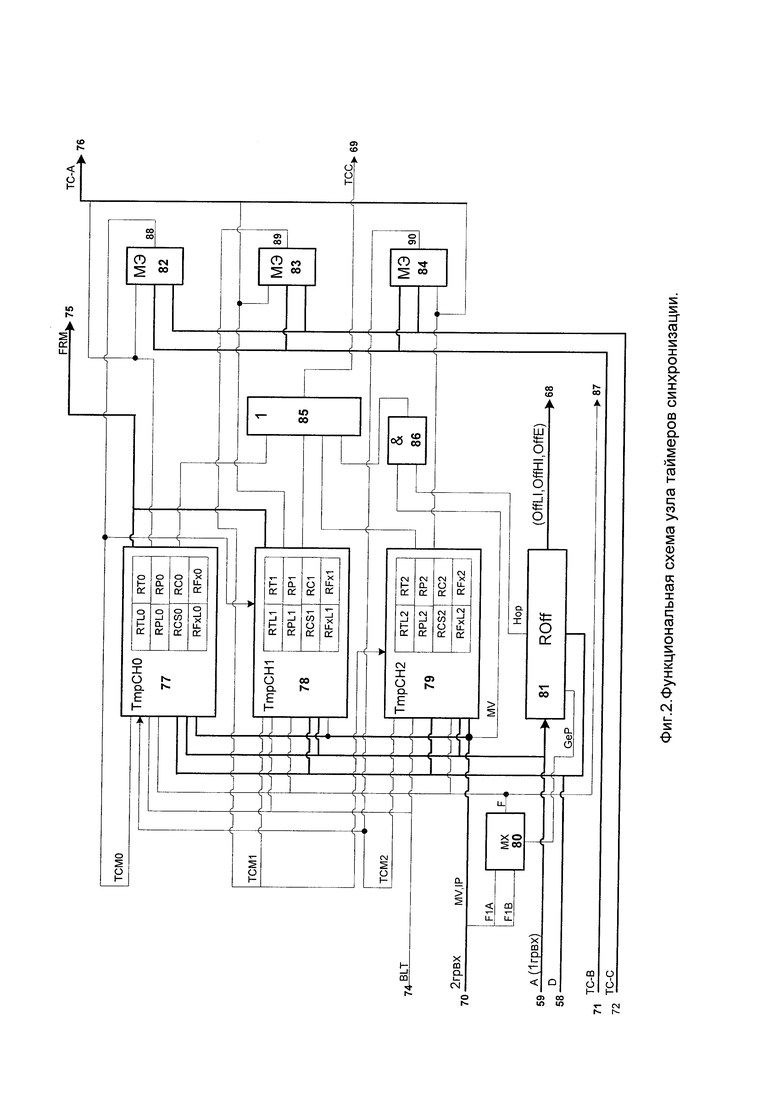

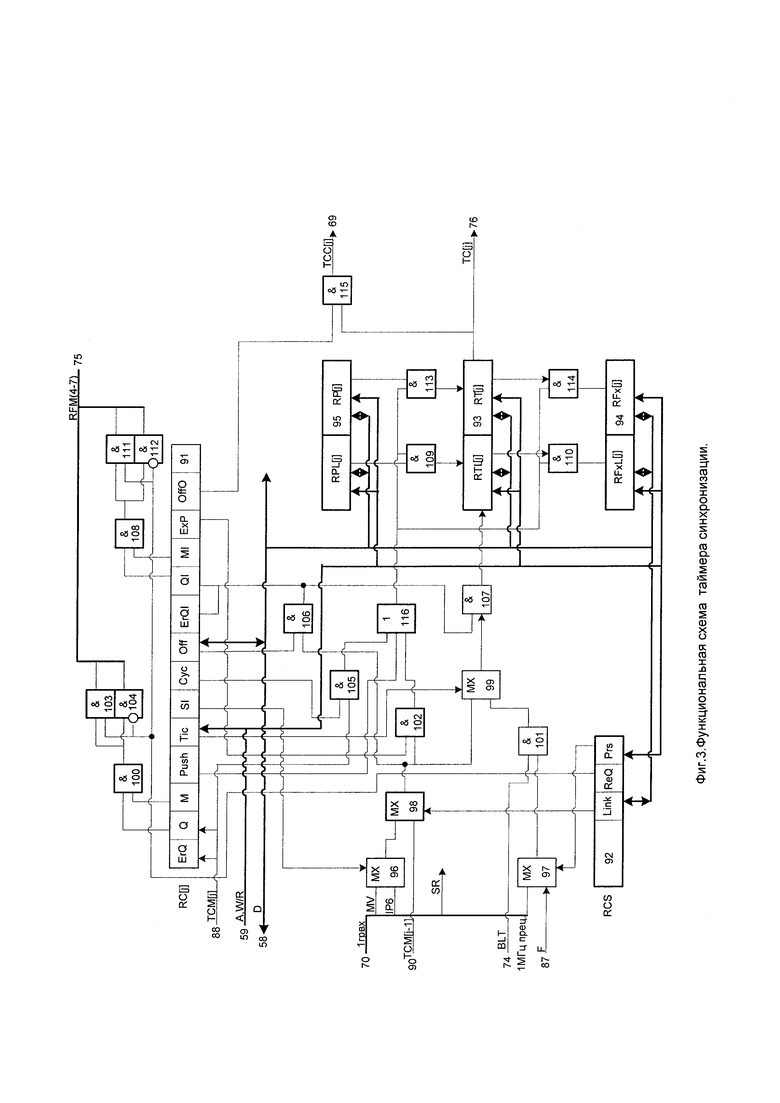

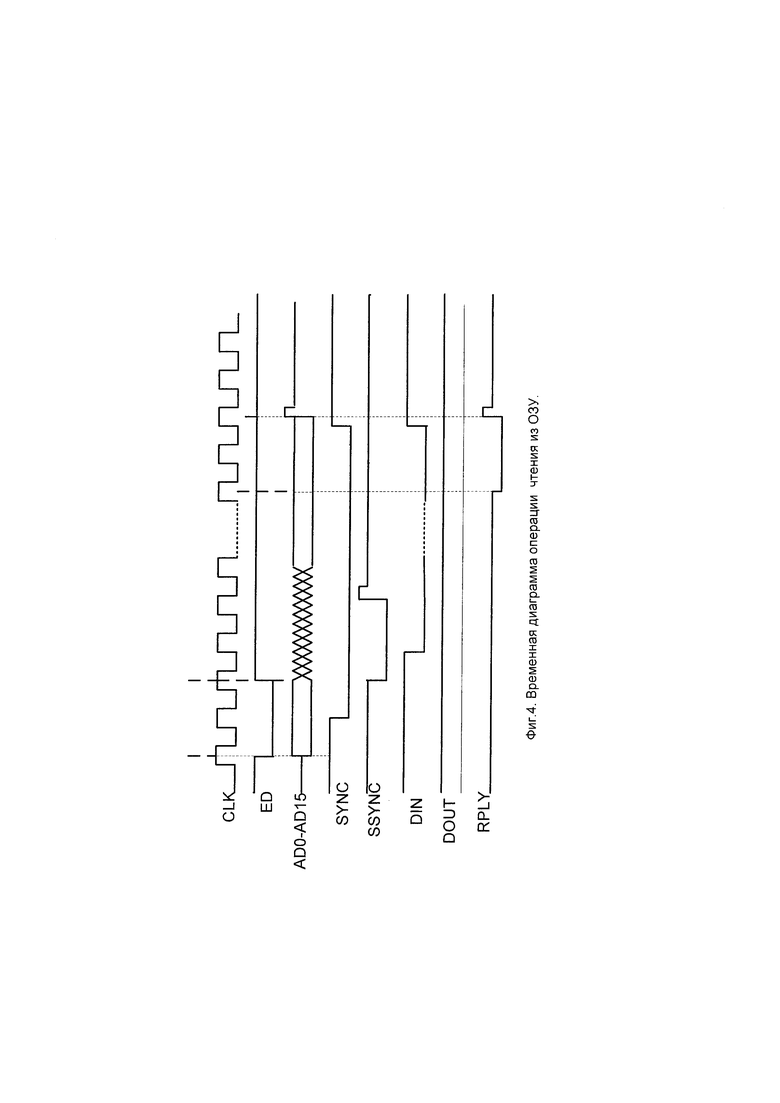

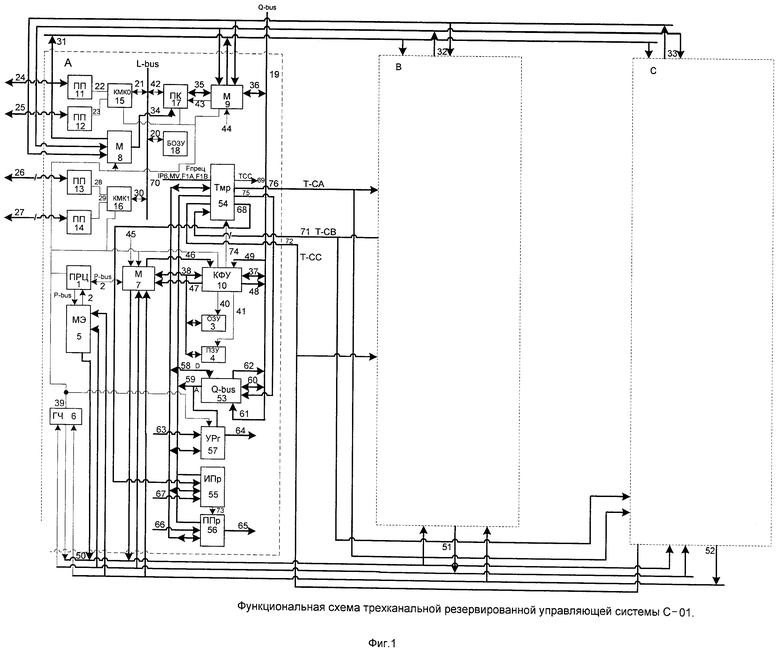

Сущность заявляемого изобретения, возможность его осуществления и промышленного использования поясняются чертежами, представленными на фиг. 1-11, где:

• на фиг. 1 представлена функциональная схема трехканальной резервированной управляющей системы С-01;

• на фиг. 2 представлена функциональная схема узла таймеров синхронизации;

• на фиг. 3 представлена функциональная схема таймера синхронизации;

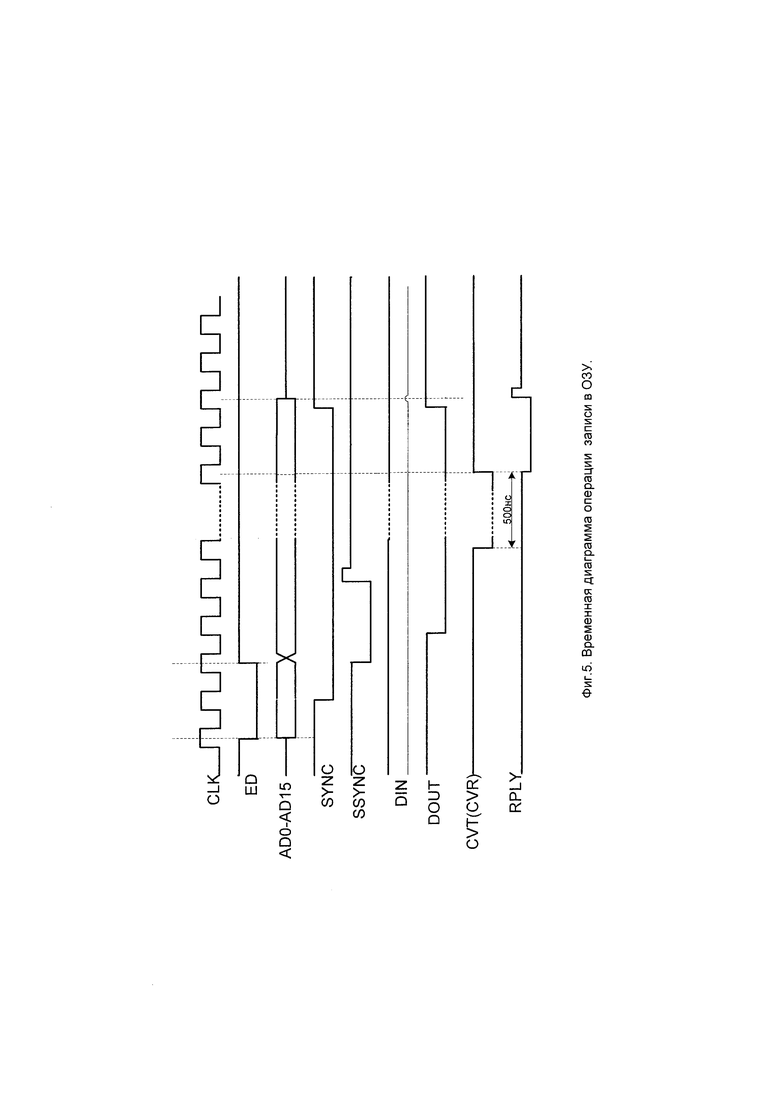

• на фиг. 4 представлена временная диаграмма операции чтения из ОЗУ;

• на фиг. 5 представлена временная диаграмма операции записи в ОЗУ;

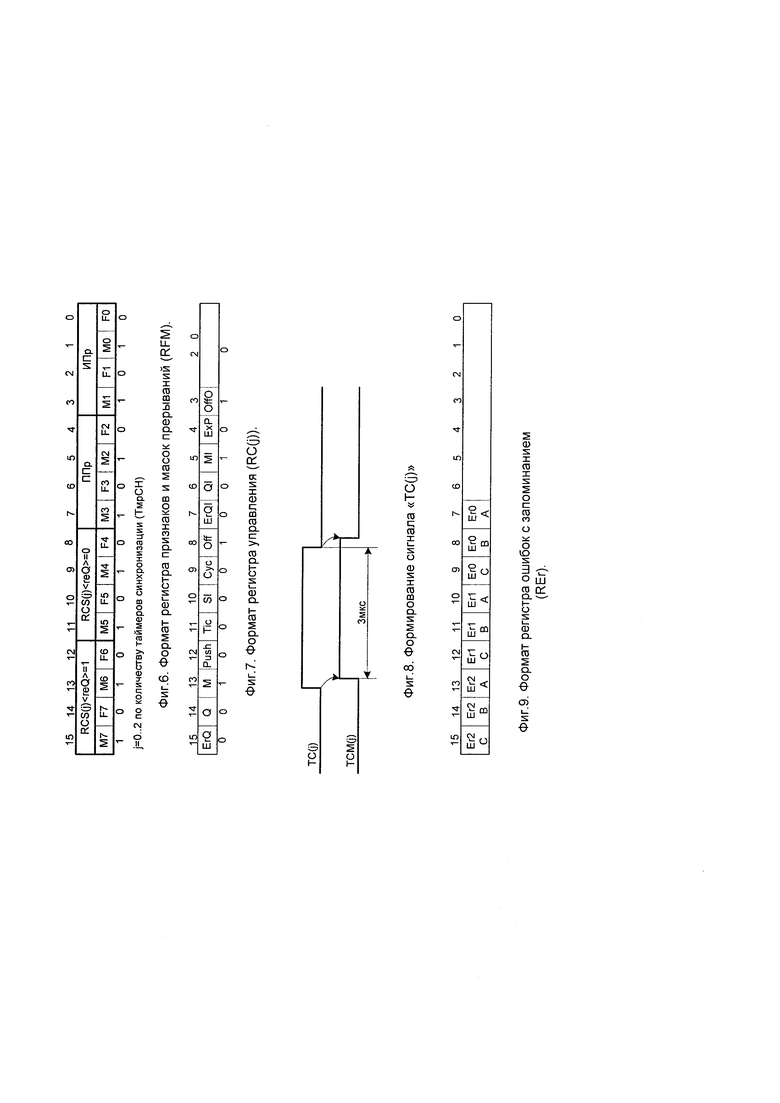

• на фиг. 6 представлен формат регистра признаков и масок прерываний (RFM);

• на фиг. 7 представлен формат регистра управления (RC(j));

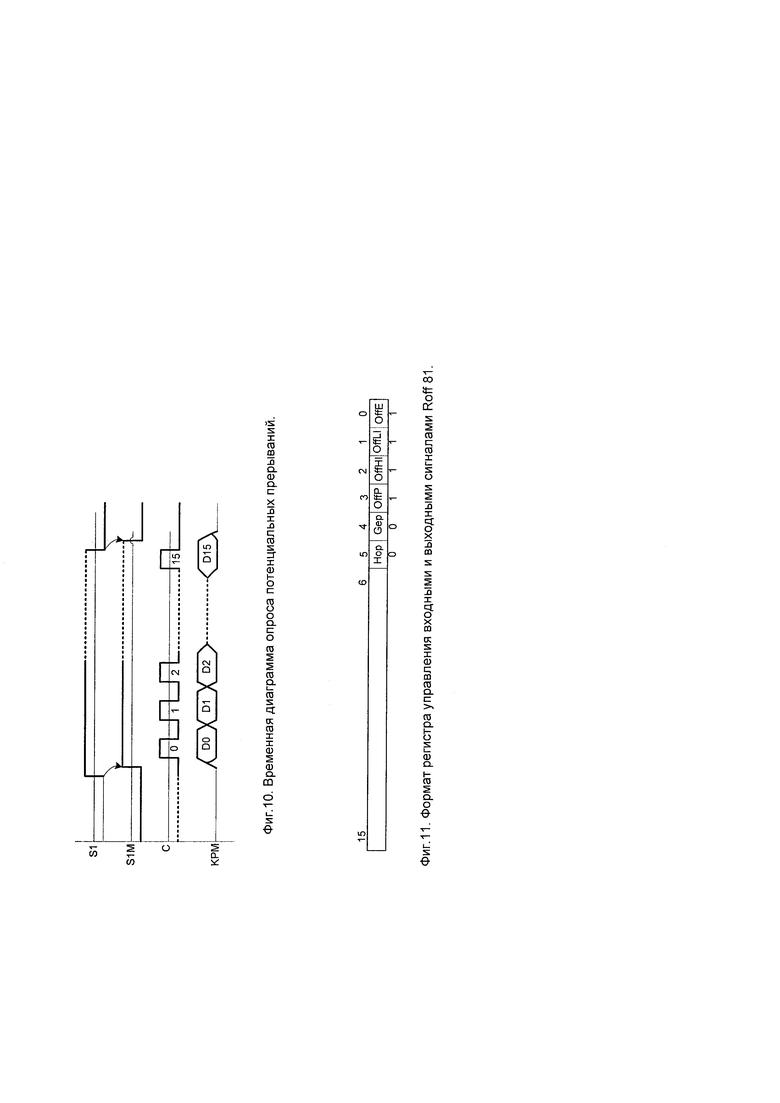

• на фиг. 8 представлено формирование сигнала «TC(j)»;

• на фиг. 9 представлен формат регистра ошибок с запоминанием (REr);

• на фиг. 10 представлена временная диаграмма опроса потенциальных прерываний;

• на фиг. 11 представлен формат регистра управления входными и выходными сигналами Roff 81.

Указанные преимущества заявляемой системы перед прототипом достигаются за счет того, что в трехканальную резервированную управляющую систему С-01, содержащую первый системный модуль А, второй системный модуль В, третий системный модуль С, причем каждый модуль А, В, С включает процессор 1, с шиной процессора P-bus 2, ОЗУ 3, ПЗУ 4, группу мажоритарных элементов 5, генератор 6, первую 7 группу, вторую 8 группу, третью 9 группу мажоритарных устройств, контроллер функциональных узлов 10, первое 11, второе 12, третье 13, четвертое 14 приемо-передающие устройства, первый 15 и второй 16 контроллеры мультиплексного канала обмена, периферийный контроллер 17, буферное ОЗУ 18, шину Q-bus 19 и шину L-bus 20, соединенную с БОЗУ 18, первая 21 двунаправленная группа входов-выходов которой соединена с двунаправленной группой входов-выходов первого 15 контроллера мультиплексного канала обмена, первый 22 и второй 23 входы которого соединены с выходами первого 11 и второго 12 приемо-передающего устройства, группы входов-выходов которых являются первой 24 и второй 25 группами входов-выходов системы соответственно, третья 26 и четвертая 27 группы входов-выходов которой являются группами входов-выходов третьего 13 и четвертого 14 приемо-передающих устройств, выходы которых соединены с первым 28 и вторым 29 входами второго 16 контроллера мультиплексного канала обмена, группа входов-выходов 30 которого является второй группой входов-выходов шины L-bus 20, причем первая 31 группа выходов модуля А состоит из первых групп выходов второй 8 и третьей 9 групп мажоритарных устройств и соединена с первыми группами входов второй 8 и третьей 9 групп мажоритарных устройств модулей В и С, первая 32 группа выходов модуля В состоит из первых групп выходов второй 8 и третьей 9 групп мажоритарных устройств модуля В и соединена с первыми группами входов второй 8 и третьей 9 групп мажоритарных устройств модуля А и со вторыми группами входов второй 8 и третьей 9 групп мажоритарных устройств модуля С, первая 33 группа выходов модуля С состоит из первых групп выходов второй 8 и третьей 9 групп мажоритарных устройств модуля С и соединена со вторыми группами входов второй 8 и третьей 9 групп мажоритарных устройств модулей А и В, причем вторая 34 группа выходов второй 8 группы мажоритарных устройств соединена с первой группой входов периферийного контроллера 17, первая 35 группа входов-выходов которого соединена с первой группой входов-выходов третьей 9 группы мажоритарных устройств, вторая 36 группа входов-выходов которых соединена с первой группой входов-выходов шины Q-bus 19, вторая 37 группа входов-выходов которой соединена с первой группой входов-выходов контроллера функциональных узлов 10, вторая 38 группа входов-выходов которого соединена с группами входов-выходов ОЗУ 3, ПЗУ 4 и первой группой входов-выходов первой 7 группы мажоритарных устройств, вторая группа входов-выходов которых является шиной 2 P-bus и соединена с группой входов-выходов процессора 1, группа выходов шины 2 Р-bus которого соединена с первой группой входов группы мажоритарных элементов 5, первая группа выходов которых соединена с группой входов шины 2 Р-bus процессора 1, вход которого соединен с выходом 39 генератора 6, со входами первой 7, второй 8 и третьей 9 группами мажоритарных устройств, первого 15 и второго 16 контроллеров мультиплексного канала обмена, периферийного контроллера 17 и контроллера функциональных узлов 10, первая 40 и вторая 41 группы выходов которого соединены с группами входов ОЗУ 3 и ПЗУ 4 соответственно, третья 42 группа входов-выходов шины L-bus соединена со второй группой входов-выходов периферийного контроллера 17, вторая группа входов которого соединена со второй 43 группой выходов третьей группы мажоритарных устройств 9, третья группа входов которых соединена с первой 44 группой входов системы, вторая 45 группа входов которой соединена с первой группой входов первой группы мажоритарных устройств 7, первая 46 группа выходов и вторая группа входов которых соединены со второй группой входов и с третьей 47 группой выходов контроллера функциональных узлов 10, четвертая 48 группа выходов которого соединена с первой группой входов шины Q-bus 19, первая 49 группа выходов которой соединена с первой группой входов контроллера функциональных узлов 10, вторая 50 группа выходов модуля А состоит из второго выхода генератора 6 и вторых групп выходов группы мажоритарных элементов 5 и первой группы мажоритарных устройств 7 и соединена с третьими группами входов модулей В и С, вторая 51 группа выходов модуля В состоит из второго выхода генератора 6 и вторых групп выходов группы мажоритарных элементов 5 и первой 7 группы мажоритарных устройств модуля В и соединена с третьей группой входов модуля А и четвертой группой входов модуля С, вторая 52 группа выходов модуля С состоит из второго выхода генератора 6 и вторых групп выходов группы мажоритарных элементов 5 и первой группы мажоритарных устройств 7 модуля С и соединена с четвертыми группами входов модулей А и С, причем третья группа входов модулей соединена с первым входом генератора 6, со второй группой входов группы мажоритарных элементов 5 и третьей группой входов первой группы мажоритарных устройств 7, четвертая группа входов модулей соединена со вторым входом генератора 6, с третьей группой входов группы мажоритарных элементов 5 и четвертой группой входов первой 7 группы мажоритарных устройств, причем в каждый модуль А, В, С дополнительно введены, узел интерфейса шины Q-bus 53, узел таймеров синхронизации 54, узел приема и обработки импульсных сигналов 55, узел приема и обработки потенциальных сигналов 56, узел регистров 57, группа входов-выходов 58 которого соединена с группами входов-выходов узла приема и обработки потенциальных сигналов 56, узла приема и обработки импульсных сигналов 55, узла интерфейса шины Gibus 53, узла таймеров синхронизации 54, первая группа входов которого соединена с первыми группами входов узла регистров 57, узла приема и обработки импульсных сигналов 55, узла приема и обработки потенциальных сигналов 56 и группой выходов 59 узла интерфейса шины Q-bus 53, группа входов-выходов 60 которого соединена с третьей группой входов-выходов шины Q-bus 19, вторая 61 группа выходов которой соединена с группой входов узла интерфейса шины Q-bus 53, вторая 62 группа выходов которого соединена со второй группой входов шины Q-bus 19, причем третья 63 группа входов системы соединена со второй группой входов узла регистров 57, группа выходов которого является первой 64 группой выходов системы, вторая 65 группа выходов которой является группой выходов узла приема и обработки потенциальных сигналов 56, вторая группа входов которого является четвертой 66 группой входов системы, пятая 67 группа входов которой является второй группой входов узла приема и обработки импульсных сигналов 55, третья группа входов которого соединена с первой 68 группой выходов узла таймеров синхронизации 54, первый выход которого соединен с первым 69 выходом системы, шестая 70 группа входов которой является второй группой входов узла таймеров синхронизации 54, третья 71 и четвертая 72 группы входов которого соединены с третьеми группами выходов модуля В и С соответственно, причем вход узла регистров 57 соединен с выходом 39 генератора 6, выход 73 узла приема и обработки импульсных сигналов 55 соединен со входом узла приема и обработки потенциальных сигналов 56, причем выход 74 контроллера функциональных узлов 10 соединен со входом узла таймеров синхронизации 54, вторая 75 группа выходов которого соединена с первой группой входов узла интерфейса шины Q-bus 53, третья 76 группа выходов узла таймеров синхронизации 54 является третьей группой выходов модуля А и соединена с третьими группами входов модулей В и С, причем третьи группы выходов модулей В и С соединены с четвертыми группами входов модулей С и В соответственно.

Узел таймеров синхронизации 54 содержит первый 77, второй 78 и третий 79 таймеры синхронизации, мультиплексор 80, регистр 81, первый 82, второй 83 и третий 84 мажоритарные элементы, элемент ИЛИ 85 и элемент И 86, выход которого соединен с первым входом элемента ИЛИ 85, выход которого является первым 69 выходом узла таймеров синхронизации 54, первая 68 группа выходов которого является группой выходов регистра 81, первый выход которого соединен с первым входом элемента И 86, второй вход которого является первым сигналом второй 70 группы входов узла таймеров синхронизации 54, которая соединена с первыми группами входов первого 77, второго 78 и третьего 79 таймеров синхронизации и первым и вторым входами мультиплексора 80, выход 87 которого является вторым выходом узла таймеров синхронизации и соединен с первыми входами таймеров синхронизации (77, 78, 79), первые выходы которых соединены с первым, вторым и третьим входами элемента ИЛИ 85, причем вторая 75 группа выходов узла таймеров синхронизации 54 соединена с первыми группами выходов первого 77 и второго 78 таймеров синхронизации, вторые выходы таймеров синхронизации (77, 78, 79) соединены с первыми входами первого 82, второго 83 и третьего 84 мажоритарных элементов и являются третьей 76 группой выходов узла таймеров синхронизации 54, группа входов-выходов 58 которого соединена с группами входов-выходов первого 77, второго 78 и третьего 79 таймеров синхронизации и регистра 81, второй выход которого соединен с третьим входом мультиплексора 80, первая 59 группа входов узла таймеров синхронизации соединена с группой входов регистра 81, со вторыми группами входов таймеров синхронизации (77, 78, 79), вторые входы которых соединены с первым 74 входом узла таймеров синхронизации 54, третья 71 и четвертая 72 группы входов которого соединены с первыми и вторыми группами входов первого 82, второго 83 и третьего 84 мажоритарных элементов, выход 88 первого 82 мажоритарного элемента соединен с третьими входами первого 77 и второго 78 таймеров синхронизации, выход 89 второго 83 мажоритарного элемента соединен с четвертым входом второго 78 таймера синхронизации и третьим входом третьего 79 таймера синхронизаци, выход 90 третьего 84 мажоритарного элемента соединен с четвертыми входами третьего 79 и первого 77 таймеров синхронизации.

Таймер синхронизации (77, 78, 79) содержит регистр управления 91, регистр управления конфигурацией 92, регистр счетчик 93, регистр фиксации 94, регистр предустановки 95, первый 96 мультиплексор, второй 97 мультиплексор, третий 98 мультиплексор, четвертый 99 мультиплексор, первый 100 элемент И, второй 101 элемент И, третий 102 элемент И, четвертый 103 элемент И, пятый 104 элемент И, шестой 105 элемент И, седьмой 106 элемент И, восьмой 107 элемент И, девятый 108 элемент И, десятый 109 элемент И, одиннадцатый 110 элемент И, двенадцатый 111 элемент И, тринадцатый 112 элемент И, четырнадцатый 113 элемент И, пятнадцатый 114 элемент И, шестнадцатый 115 элемент И, элемент ИЛИ 116, выход которого соединен с первыми входами десятого 109, одиннадцатого 110, четырнадцатого 113 и пятнадцатого 114 элементов И, выходы которых соединены с первыми входами регистра счетчика 93 младших разрядов, регистра фиксации 94 младших разрядов, регистра счетчика 93, регистра фиксации 94 соответственно, группы входов-выходов которых соединены с группами входов-выходов регистра предустановки 95 младших разрядов, регистра предустановки 95, регистра управления конфигурацией 92, регистра управления 91 и являются группой входов-выходов 58 таймера синхронизации (77, 78, 79), вторая 59 группа входов которого соединена с группами входов регистра управления 91, регистра предустановки 95 младших разрядов, регистра предустановки 95, регистра счетчика 93 младших разрядов, регистра счетчика 93, регистра фиксации 94 младших разрядов, регистра фиксации 94 и регистра управления конфигурацией 92, первый выход которого соединен с первым входом третьего 98 мультиплексора, выход которого соединен с первыми входами третьего 102 и седьмого 106 элементов И и четвертого 99 мультиплексора, выход которого соединен с первым входом восьмого 107 элемента И, выход которого соединен со вторым входом регистра счетчика 93, первый и второй выходы которого соединены со вторыми входами одиннадцатого 110 и пятнадцатого 114 элементов И, выходы которых соединены с первыми входами регистра фиксации 94 младших разрядов и регистра фиксации 94, причем первая группа выходов 75 таймера синхронизации (77, 78, 79) соединена с выходами четвертого 103, пятого 104, двенадцатого 111 и тринадцатого 112 элементов И, первые входы четвертого 103 и пятого 104 элементов И соединены между собой и с выходом первого 100 элемента И, а первые входы двенадцатого 111 и тринадцатого 112 элементов И соединены между собой и с выходом девятого 108 элемента И, первый и второй входы которого соединены с первым (QI) и вторым (MI) выходами регистра управления 91, первый (ErQI) и второй (QI) входы которого соединены со вторым входом восьмого 107 элемента И и выходом седьмого 106 элемента И, второй вход которого соединен с третьим (Off) выходом регистра управления 91, четвертый (Cyc), пятый (SI) и шестой (Push) выходы которого соединены с первыми входами шестого 105 элемента И, первого 96 мультиплексора и элемента ИЛИ 116 соответственно, второй вход которого соединен с выходом шестого 105 элемента И, второй вход которого соединен с третьим (ErQ) и четвертым (Q) входами регистра управления 91 и третьим 88 входом таймера синхронизации (77, 78, 79), первый 69 выход которого соединен с выходом шестнадцатого 115 элемента И, первый вход которого соединен с пятым (OffO) входом регистра управления 91, седьмой (ЕхР) выход которого соединен со вторым входом третьего 102 элемента И, выход которого соединен с третьим входом элемента ИЛИ 116, второй 76 выход таймера синхронизации (77, 78, 79) соединен с третьим выходом регистра счетчика 93 и вторым входом шестнадцатой 15 элемента И, причем первая 70 группа входов таймера синхронизации (77, 78, 79) соединена с первыми входами первого 96 и второго 97 мультиплексоров и вторым входом первого 96 мультиплексора, выход которого соединен со вторым входом третьего 98 мультиплексора, третий вход которого соединен с четвертым 90 входом таймера синхронизации (77, 78, 79), первый 87 и второй 74 входы которого соединены со вторым входом второго 97 мультиплексора и первым входом второго 101 элемента И, выход которого соединен со вторым входом четвертого 99 мультиплексора, третий вход которого соединен с восьмым (Tic) выходом регистра управления 91, второй выход регистра управления конфигурацией 92 соединен со вторыми входами четвертого 103 и двенадцатого 111 элементов И и инверсными входами пятого 104 и тринадцатого 112 элементов И, девятый (Q) и десятый (М) выходы регистра управления 91 соединены с первым и вторым входами первого 100 элемента И, третий выход регистра управления конфигурацией 92 соединен с третьим входом второго 97 мультиплексора, выход которого соединен со вторым входом второго 101 элемента И, выходы регистра предустановки 95 младшие разряды и регистра предустановки 95 соединены со вторыми входами десятого 109 и четырнадцатого 113 элементов И.

Трехканальная резервированная управляющая система С-01 работает следующим образом.

Предлагаемая система состоит из трех однотипных резервных каналов, которые обозначаются литерами А, В, С (фиг. 1), соединенных мажоритарными связями 31, 32, 33, 50, 51, 52. Мажоритарные элементы 5 каналов резервирования и мажоритарные устройства 7, 8, 9 работают по принципу голосования «два из трех».

В системе используются следующие интерфейсные шины для обмена информацией между функциональными устройствами (ФУ):

• шина процессора - P-bus 2;

• локальная шина устройств ввода-вывода (УВВ) - L-bus 20;

• межмодульная шина -Q-bus 19.

Шина процессора - шина P-bus - представляет собой функциональный узел параллельного интерфейса, реализованный в составе процессора.

К шине P-bus подключены: процессор 1, память 3, 4, контроллер функциональных узлов 10 (КФУ). По шине P-bus процессор 1 осуществляет программный доступ к памяти 3, 4 и к КФУ 10. По шине P-bus на процессор 1 поступают запросы на прерывания (первая группа входов).

Локальная шина УВВ - шина L-bus 20 представляет собой функциональный узел, реализованный в составе устройств ввода-вывода. К шине L-bus подключены: периферийный контроллер 17, контроллеры МКО0-15, МКО1-16 и БОЗУ 18.

Межмодульная шина - Q-bus 19 (ГОСТ Р 52070-2003) -представляет собой функциональный узел параллельного интерфейса, реализованный в составе системы.

К шине Q-bus 19 подключены процессор 1 (через КФУ10 (37) периферийный контроллер 17 (через мажоритарные устройства 9 (36) и узел интерфейса шины Q-bus 53 (60). Взаимодействие по шине Q-bus 19 обеспечивают:

• контроллер функциональных узлов 10;

• периферийный контроллер 17

• узел интерфейса шины Q-bus 53.

По шине Q-bus 19 процессор 1 осуществляет программный доступ к регистрам КФУ 10, периферийного контроллера 17, узла таймеров синхронизации 54, узла приема и обработки импульсных сигналов 55, узла приема и обработки потенциальных сигналов 56, узла регистров 57.

В состав каждого канала входит процессор 1, обеспечивающий выполнение программы, расположенной в ПЗУ 4. Часть программ может располагаться в ОЗУ3, куда они могут загружаться из ПЗУ4 или внешних интерфейсов системы. При выполнении этой программы в режиме «пользователь» процессор 1 может обращаться к части ОЗУ3, выделенной для программ пользователя. При выполнении программ в режиме «система» процессор 1 может обращаться ко всему ОЗУ3 и регистрам внешних устройств.

Процессор 1 может адресовать следующие элементы данных на шине P-bus:

• байт - 8-битовый элемент данных (наименьшая адресуемая единица);

• полуслово - 16-битовый элемент данных;

• слово - 32-битовый элемент данных.

Все выдаваемые процессором адреса 32-битовые.

Основная память ОЗУ3 и ПЗУ4, подключенная непосредственно к шине P-bus, состоит из 32-битовых ячеек, адреса которых выровнены по «словной границе» (т.е. адрес ячейки основной памяти кратен четырем). Основная память обеспечивает все типы адресации, указанные выше.

КФУ10, подключенный непосредственно к P-bus, имеет в своем составе 32-битовые регистры. КФУ10 обеспечивает только словную адресацию.

КФУ10 предоставляет процессору 1 программный доступ к регистрам КФУ 10, к памяти ОЗУ3 и ПЗУ4, к регистрам и к БОЗУ 18 всех УВВ.

КФУ 10 выдает на процессор 1 сигналы установки процессора 1 при его запуске и перезапуске, запросы на прерывания.

В формате адреса объекта на УВВ, выдаваемого процессором 1, предусмотрены:

• 12-битовое поле признака, определяющее зону адресов УВВ (зону Q-bus 19);

• 2-битовое поле номера УВВ, определяющее зону адресов УВВ.

Система обеспечивает взаимодействие с внешними абонентами по двум дублированным мультиплексным каналам информационного обмена (МКО) в соответствии с ГОСТ Р 52070-2003 и с процессором 1 по интерфейсу Q-bus 19. Электрически каждый МКО состоит из двух магистралей: основной и резервной. Обмен по каждому МКО управляется своим контроллером (КМК0 15, КМК1 16) который может быть программно установлен в режим контроллера канал (КК) или в режим оконечного устройства (ОУ). Мажорирование одноименных сигналов выполняется по принципу голосования «два из трех» (третья группа мажоритарных устройств 9).

Общее управление МКО выполняет процессор 1, обращаясь к ПК 17, контроллерам МКО (КМК0 15 и КМК1 16) и БОЗУ 18. ПК 17 является диспетчером локальной шины L-bus 20, регулирующим обращения (КМК0 15, КМК1 16 и процессора 1 к БОЗУ 18.

Каждый дублированный интерфейс МКО управляется своим КМК, который программно можно установить в режим КК или ОУ. В любом режиме КМК обеспечивает полный перечень форматов и команд ГОСТ Р 52070-2003, а также контроль достоверности информационных слов, принятых из МКО.

В режиме ОУ выполняется проверка принятых командных слов на допустимость. Допустимость той или другой команды задается программно. Адрес ОУ также задается программно.

БОЗУ 18 объемом 32К×16 разделено на восемь равных зон (страниц). В любом режиме КМК работает с одной страницей, которая назначается программно. Процессор 1 имеет доступ ко всему объему БОЗУ 18, который можно совмещать с обменами обоих КМК 15, 16 по МКО. БОЗУ 18 содержит управляющую и контрольную информацию по каждому обмену, а также буфера принятых и передаваемых данных. В режиме ОУ адрес буфера определяется подадресом из принятого командного слова.

ПП устройства 11, 12, 13, 14 осуществляют электрофизическое сопряжение каналов резервирования с магистралями МКО. В МКО активным является передатчик только одного канала резервирования, другие блокируются. Выбор активного канала резервирования программируется. Прием из МКО выполняется во всех каналах резервирования.

Каждый канал резервирования имеет два узла мажоритарных устройств (вторая 8 и третья 9 группы мажоритарных устройств). В одном узле мажоритарные сигналы шины Q-bus 19 (третья 9 группа мажоритарных устройств), в другом (вторая 8 группа мажоритарных устройств) -последовательные коды, выдаваемые на передатчик и поступающие от приемника ПП.

Информационное взаимодействие между процессором 1, ОЗУ3, ПЗУ4 и КФУ 10 производится по тридцати двух разрядной двунаправленной мультиплексной шине, в сечение которой включена первая группа мажоритарных устройств 7 исправления информации в двунаправленной шине. Первая группа мажоритарных устройств 7 связана с процессором 1 первой группой входов-выходов (P-bus 2), а с ОЗУ3, ПЗУ4 и КФУ10 второй группой входов-выходов 38. Первая группа мажоритарных устройств 7 всех резервных каналов связаны между собой мажоритарными связями 50, 51, 52, что обеспечивает работоспособность системы при отказах, возникающих в отдельных каналах. При обмене с ОЗУ3 и ПЗУ4 производится запись информации в заданную ячейку, либо из заданной ячейки производится считывание информации. Информационный обмен между процессором 1 и КФУ 10 осуществляется в результате реализации процедур записи и чтения информации по отношению к программно доступным регистрам, содержащимся в КФУ10. При выполнении процедур записи и чтения по отношению к памяти и регистрам первая группа входов-выходов 38 работает в режиме разделения времени: сначала по ней передается код адреса ячейки или регистра, а затем - информация.

Узел интерфейса шины Q-bus 53 поддерживает операции обмена на шине Q-Bus, формирует сигнал запроса на прерывание - "IRQ" 62 и сигналы управления внутренними регистрами.

Временные диаграммы обмена по шине Q-Bus представлены на фиг. 4 и фиг. 5. При выполнении операции записи в регистры выходных релейных сигналов RReI и регистр телеметрии RTIm формируются сигналы "CVR" и "CVT" (фиг. 5) соответственно, которые вложены в сигнал "DOUT" и их длительность составляет 500 нс.

Сигнал "IRQ" 62 вырабатывается (низким уровнем) при наличии хотя бы одного незамаскированного в регистре RFM запроса на прерывание (ЗПр).

В состав узла интерфейса шины Q-bus 53 входят программно-доступный регистр - признаков ("флагов") и масок прерываний RFM.

Формат регистра RFM представлен на фиг. 6.

Назначение разрядов регистра RFM:

• F0 - признак наличия импульсных запросов на прерывание (ЗПр) "линии 0"; доступен по чтению; устанавливается аппаратно при RQI<i>=1 (регистр импульсных ЗПр), если RMI<i>=0 (регистр масок импульсных ЗПр), и RNI<i>=0 (регистр номеров линий импульсных ЗПр) (i=0…15); сбрасывается аппаратно при программном сбросе соответствующих разрядов RQI, программной установке соответствующих разрядов RMI в "1" или программной установке соответствующих разрядов RNI в "1"; по приходу сигнала "SR" (70) (начальная установка) устанавливается в "0";

• М0 - маска на прерывание по F0, "1" маскирует прерывание; устанавливается и сбрасывается программно; по приходу сигнала "SR" (70) устанавливается в "1";

• F1 - признак наличия импульсных ЗПр "линии 1"; доступен по чтению; устанавливается аппаратно при RQI<i>=1, если RMI<i>=0 и RNI<i>=1 (i=0…15); сбрасывается аппаратно при программном сбросе соответствующих разрядов RQI, программной установке соответствующих разрядов RMI в "1" или программной установке соответствующих разрядов RNI в "0"; по приходу сигнала "SR" (70) устанавливается в "0";

• М1 - маска на прерывание по F1; устанавливается и сбрасывается программно; по приходу сигнала "SR" (70) устанавливается в "1";

• F2 - признак наличия потенциальных ЗПр "линии 0"; доступен по чтению; устанавливается аппаратно при RQP<i>=1 (регистр потенциальных ЗПр), если RMP<i>=0 (регистр масок потенциальных ЗПр) и RNP<i>=0 (регистр номеров линий потенциальных ЗПр) (i=0…15); сбрасывается аппаратно при программном сбросе соответствующих разрядов RQP, программной установке соответствующих разрядов RMP в "1" или программной установке соответствующих разрядов RNP в "1"; по приходу сигнала "SR" (70) устанавливается в "0";

• М2 - маска на прерывание по F2; устанавливается и сбрасывается программно; по приходу сигнала "SR" (70) устанавливается в "1";

• F3 - признак наличия потенциальных ЗПр "линии 1"; доступен по чтению; устанавливается аппаратно при RQP<i>=1, если RMP<i>=0 и RNP<i>=1 (i=0…15); сбрасывается аппаратно при программном сбросе соответствующих разрядов RQP, программной установке соответствующих разрядов RMP в "1" или программной установке соответствующих разрядов RNP в "0"; по приходу сигнала "SR" (70) устанавливается в "0";

• М3-маска на прерывание по F3; устанавливается и сбрасывается программно; по приходу сигнала "SR" (70) устанавливается в "1";

• F4 - признак наличия ЗПр по срабатыванию ТмрСн[j] (77, 78, 79), если RCS[j]<reQ>=0 (регистр конфигурации 92); доступен по чтению; устанавливается аппаратно при RC[j]<Q>=1 (регистр управления 91) (значение RC[j]<ErQ>91 не учитывается), если RC[j]<M>91=0; сбрасывается аппаратно при программном сбросе RC[j]<Q>91 или установке RC[j]<M>91=1; по приходу сигнала «SR» (70) устанавливается в "0" (j=0…2);

• М4 - маска на прерывание по F4; устанавливается и сбрасывается программно; по приходу сигнала "SR" (70) устанавливается в "1";

• F5 - признак наличия ЗПр по приходу внешнего сигнала на ТмрСн[j] (77, 78, 79), если RCS[j]<reQ>92=0; доступен по чтению; устанавливается аппаратно при RC[j]<QI>91=1 (значение RC[j]<ErQI>91 не учитывается), если RC[j]<MI>91=0; сбрасывается аппаратно при программном сбросе RC[j]<QI>91 или установке RC[j]<MI>91=1; по приходу сигнала "SR" (70) устанавливается в "0"(j=0…2);

• М5 - маска на прерывание по F5; устанавливается и сбрасывается программно; по приходу сигнала "SR" (70) устанавливается в "1";

• F6 - признак наличия ЗПр по срабатыванию ТмрСн[j] (77, 78, 79), если RCS[j]<reQ>92=1; доступен по чтению; устанавливается аппаратно при RC[j]<Q>91=1 (значение RC[j]<ErQ>91 не учитывается), если RC[j]<M>91=0; сбрасывается аппаратно при программном сбросе RC[j]<Q> или установке RC[j]<M>=1; по приходу сигнала "SR" (70) устанавливается в "0"(j=0…2);

• М6 - маска на прерывание по F6; устанавливается и сбрасывается программно; по приходу сигнала "SR" (70) устанавливается в "1";

• F7 - признак наличия ЗПр по приходу внешнего сигнала на ТмрСн[j] (77, 78, 79), если RCS[j]<reQ>92=1; доступен по чтению; устанавливается аппаратно при RC[j]<QI>91=1 (значение RC[j]<ErQI>91 не учитывается), если RC[j]<MI>91=0; сбрасывается аппаратно при программном сбросе RC[j]<QI>91 или установке RC[j]<MI>91=1; по приходу сигнала "SR" (70) устанавливается в "0";

М7 - маска на прерывание по F7; устанавливается и сбрасывается программно; по приходу сигнала "SR" (70) устанавливается в "1".

Таймеры синхронизации (77, 78, 79) ТмрСн[j] (j=0…2) одинаковы и предназначены для обеспечения синхронизации работы различных внешних систем и программного обеспечения, а также подсинхронизации по выбранному сигналу: внешней метке времени со входа MV (70), внешнему импульсному сигналу со входа IP6(70) или от предыдущего ТмрСн (77, 78, 79).

Функциональная схема ТмрСн (77, 78, 79) приведена на фиг. 3.

В состав каждого таймера синхронизации ТмрСн[j] входят:

регистр управления RC[j] 91;

• регистр управления конфигурацией RCS[j] 92;

• регистр счетчика RT[j] 93;

• регистр счетчика младших разрядов RTL[j] 93;

• регистр предустановки RPL[j] 95;

• регистр младших разрядов RPL[j] 95;

• регистр фиксации RFx[j] 94;

• регистр младших разрядов RFxL[j] 94;

• мультиплексоры, логические элементы (96-116).

Формат регистра RC[j] 91 представлен на фиг. 7.

Назначение разрядов регистра RC[j] 91:

• Q - признак однократного срабатывания ТмрСн (77, 78, 79) (счетчик досчитал до нуля), при этом выдается сигнал "ТС" 76 и, если снята маска RC<M>91=0, устанавливается RFM<F4>=1, если RCS<ReQ>92=0 или RFM<F6>=1 если RCS<ReQ>92=1; при установленной RC<M>91=1, разряды RFM<F4> или RFM<F6> не устанавливаются; Разряд Q устанавливается аппаратно, сбрасывается программной записью "0" (при этом сбрасывается соответствующий "флаг" в регистре RFM); запись "1" не изменяет состояние бита; по приходу сигнала «SR» (70) разряд Q устанавливается в "0";

• ErQ - признак повторного срабатывания ТмрСн (77, 78, 79); аппаратно устанавливается в "1", если срабатывание таймера произошло при RC<Q>91=1; сбрасывается программно; запись "1" не изменяет состояние бита; по приходу сигнала "SR" (70) устанавливается в "0";

• М - маска на прерывание от ТмрСн (77, 78, 79), "1"-маскирует прерывание - не позволяет установиться RFM<F4>=1 или RFM<F6>=1; устанавливается и сбрасывается программно; по приходу сигнала "SR" (70) устанавливается в "1";

• Push - сигнал переписи из регистра предустановки RP[j] 95 в регистр-счетчик RT[j] 93 (RPL[j] 95 в RTL[j] 93 соответственно); в "1" устанавливается программно, сбрасывается аппаратно после выполнения записи и всегда читается "0"; по приходу сигнала "SR" (70) устанавливается в "0";

• Tic - разряд выбора тактовой частоты счетчика, "0" соответствует 1 мкс (формируемой из входной частоты 12 МГц или с входов F1A, F1B (70) прецизионной частоты 1 МГц), "1"-внешнему сигналу со входа MV (RC<SI>91=0, RCS<Link>92=0), со входа IP6 (70) (RC<SI>91=1, RCS<Link>92=0), или по срабатыванию предыдущего таймера синхронизации (RCS<Link>92=1); устанавливается и сбрасывается программно, по приходу сигнала "SR" (70) устанавливается в "0";

• ЕхР - признак разрешения переписи ("1") из RP[j] 95 в RT[j] 93 (RPL[j] 95 в RTL[j] 93 соответственно) по приходу сигнала (высоким уровнем) на вход MV (70) (RC<SI>91=0, RCS<Link>92=0) или на вход IP6 (70) (RC<SI>91=1, RCS<Link>92=0) или по срабатыванию предыдущего таймера синхронизации (RCS<Link>92=1); устанавливается и сбрасывается программно; по приходу сигнала "SR" (70) устанавливается в "0";

• Cyc - признак разрешения переписи из RP[j] 95 в RT[j] 93 (RPL[j] в RTL[j] соответственно) по срабатыванию таймера (77, 78, 79) синхронизации, т.е. по приходу сигнала (высоким уровнем) на вход TCM[j] (88, 89, 90); устанавливается и сбрасывается программно; по приходу сигнала "SR" (70) устанавливается в "0";

• Off - запрет поступления счетных импульсов на вход счетчика 93, при этом, перепись по установке в "1" RC<Push>91 возможна; устанавливается и сбрасывается программно; по приходу сигнала "SR" (70) устанавливается в "1";

• QI - признак прихода внешнего сигнала на вход MV (70) (RC<SI>91=0, RCS<Link>92=0) или на вход IP6 (70) (RC<SI>91=1, RCS<Link>92=0) или по срабатыванию предыдущего таймера синхронизации (RCS<Link>92=1); сбрасывается программной записью "0"; запись "1" не изменяет состояние бита; по приходу сигнала "SR" (70) устанавливается в "0";

• ErQI - признак повторного прихода внешнего сигнала; аппаратно устанавливается в "1", если внешний сигнал пришел при RC<QI>91=1; сбрасывается программно; запись "1" не изменяет состояние бита; по приходу сигнала "SR" (70) устанавливается в "0";

• MI - маска на прерывание от ТмрСн (77, 78, 79) по приходу внешнего сигнала, "1" - маскирует прерывание - не позволяет установиться RFM<F5>=1 (RCS<ReQ>92=0) или RFM<F7>=1 (RCS<ReQ>92=1); устанавливается и сбрасывается программно; по приходу сигнала "SR" (70) устанавливается в "1";

• SI - разряд выбора внешнего сигнала, "0" соответствует сигналу со входа "MV"(70), "1" - внешнему сигналу со входа IP6 (70); устанавливается и сбрасывается программно, по приходу сигнала SR (70) устанавливается в "0"; при RCS<Link>92=1 значение разряда SI безразлично, так как в качестве внешнего сигнала в этом случае используется сигнал срабатывания предыдущего таймера синхронизации;

• OffO - бит запрета выдачи сигнала "ТСС" 69, "1" запрещает выдачу, "0" - разрешает; устанавливается и сбрасывается программно, по приходу сигнала "SR" (70) устанавливается в "1".

Назначение разрядов регистра управления конфигурацией RCS[j] 92 следующее:

• Link - при RCS<Link>92=1 в качестве входного внешнего сигнала для ТмрСН[j] (77, 78, 79) используется сигнал срабатывания ТмрСн[j-1] (90, 88, 89), для ТмрСн0 77 при этом используется сигнал срабатывания от ТмрСн2 79; при RCS<Link>92=0 в качестве внешнего сигнала используется MV 70 (при RC<SI>=0) или IP6 70 (при RC<SI>=1); по приходу сигнала "SR" (70) устанавливается в "0".

• ReQ - данный разряд определяет, в какие разряды регистра RFM направляются запросы на прерывание; при ReQ=0 запрос на прерывание по срабатыванию таймера синхронизации (77, 78, 79) направляется в RFM<F4>, а запрос на прерывание по приходу внешнего сигнала в RFM<F5>, при ReQ=1 запрос не прерывание по срабатыванию таймера синхронизации (77, 78, 79) направляется в RFM<F6>, а запрос на прерывание по приходу внешнего сигнала в RFM<F7>, естественно запросы направляются в RFM только если они не замаскированы; по приходу сигнала "SR" (70) устанавливается в "0" для ТмрСн0 77, ТмрСн2 79 и в "1" для ТмрСн1 78;

• Prs - данный разряд указывает источник счетных импульсов 1 мкс для счетчика таймера синхронизации (77, 78, 79); при Prs=0 счетные импульсы 1 мкс формируются из входной частоты 12 МГц; при Prs=1 счетные импульсы берутся со входов F1A(70) (при Roff<GeP>=0) или F1B (70) (при Roff<GeP>=1); по приходу сигнала "SR" (70) устанавливается в "0".

Все вышеперечисленные разряды регистра RCS 92 программно доступны по записи и чтению. Разряды 3-15 отсутствут и читаются нулевыми значениями.

Примечание. Для ТмрСн0 77 и ТмрСн2 79 исходное значение разряда ReQ=0, для ТмрСн1 78 исходное значение разряда ReQ=1.

Регистр счетчика RT[j] 93 и регистр счетчика младших разрядов RTL[j] 93 совместно образуют 20-разрядный счетчик старшие 16 разрядов которого находятся в RT[j] 93, а младшие 4 разряда - в RTL[j] 93. Разряды 4-15 RTL[j] 93 не используются и читаются нулевыми значениями.

По сигналу начальной инициализации SR (70) регистры RT[j] 93, RTL[j] 93 устанавливаются в "0".

Запись в RT[j] 93, RTL[j] 93 осуществляется исключительно из регистров предустановки RP[j] 95, RPL[j] 95 по любому из следующих условий:

• программной записи "1" в разряд RC<Push>91;

• срабатыванию таймера при RC<Cyc>91=1;

• приходу внешнего сигнала при RC<Exp>91=1 и RC<Off>91=0.

Текущее значение RT[j] 93, RTL[j] 93 на момент записи в них сохраняется в регистрах фиксации RFx[j] 94, RFxL[j] 94.

Прямая программная запись в RT[j] 93, RTL[j] 93 невозможна, данные регистры доступны только по чтению. При чтении необходимо сначала прочитать 16 старших разрядов из регистра RT[j] 93, а затем прочитать 4 младших разряда из регистра RTL[j] 93.

Примечания:

• при RC<Off>91=1 запись RT[j] 93, RTL[j] 93 фактически возможна только по условию программной записи "1" в разряд RC<Push>91; срабатывание таймера при этом невозможно так как при RC<Off>91=1 запрещается поступление счетных импульсов, а запись по приходу внешнего сигнала запрещена;

Запись по приходу внешнего сигнала задерживается до прихода ближайшего счетного импульса.

Если 20-разрядный, счетчик 93 содержит единичное значение и на него поступает счетный, импульс, то счетчик 93 переходит в нулевое значение и ТмрСн[j] (77, 78, 79) срабатывает - выдается сигнал срабатывания таймера "TC[j]" 76. Запись нулевого значения, в том числе когда в счетчике 93 содержится единичное значение, не приводит к срабатыванию таймера.

Формирование длительности сигнала "ТС" 76 на выходе представлено на фиг. 8. Схема формирования сигнала "TC[j]" обеспечивает выдачу сигнала длительностью от 3 до 4 мкс не чаще, чем один раз в 16 мкс. Входной сигнал "TCM[j]" (88, 89, 90) представляет собой мажоритированный сигнал "TC[j]" 76 в трехканальной резервированной системе.

Сигнал "TCM[j]" используется для межканальной синхронизации работы таймера. В системах без резервирования необходимо соединить выводы TC[j] и TCM[j].

При поступлении сигнала TCM[j] (88, 89, 90) разряд RC<Q>91 устанавливается в "1", если данный разряд уже содержал "1", то также в "1" устанавливается RC<ErQ>91, при RC<Cyc>91=1 производится перепись RP[j] 95, RPL[j] 95 → RT[j] 93, RTL[j] 93 → RFx[j] 94, RFxL[j] 94.

В качестве импульсов счета для счетчика могут использоваться (при RC<Tic>91=0) одномикросекундные импульсы от источника частоты 1 МГц с делителя частоты или от внешнего источника, или (при RC<Tic>91=1) внешние сигналы.

Подача на счетчик импульсов 93 1 мкс может быть заблокирована внешним сигналом BLT 74. На подачу внешних сигналов BLT 74 не влияет. И импульсы 1 мкс и внешние сигналы отключаются при RC<Off>91=1.

Регистр предустановки RP[j] 95, и регистр предустановки младших разрядов RPL[j] 95 совместно образуют 20-разрядный регистр предустановки 95, старшие 16 разрядов которого находятся в RP[j] 95, а младшие 4 разряда - в RPL[j] 95.

При записи необходимо сначала записать 4 младших разряда в регистр RPL[j] 95, затем необходимо записать 16 старших разрядов в RP[j] 95, при этом происходит фиксация полного значения в 20-разрядном суммарном регистре.

При чтении необходимо сначала прочитать 16 старших разрядов из регистра RP[j] 95, а затем прочитать 4 младших разряда из регистра RPL[j] 95.

Регистр фиксации RFx[j] 94, и регистр фиксации младших разрядов RFxL[j] 94 совместно образуют 20-разрядный регистр фиксации, старшие 16 разрядов которого находятся в RFx[j] 94, а младшие 4 разряда - в RFxL[j] 94.

При записи необходимо сначала записать 4 младших разряда в регистр RFxL[j] 94, затем необходимо записать 16 старших разрядов в RFx[j] 94, при этом происходит фиксация полного значения в 20-разрядном суммарном регистре.

При чтении необходимо сначала прочитать 16 старших разрядов из регистра RFx[j] 94, а затем прочитать 4 младших разряда из регистра RFxL[j] 94.

Узел приема и обработки импульсных сигналов (Ипр) 55 обеспечивает прием и обработку 16 импульсных прерываний.

В состав ИПр входят программно-доступные регистры:

• RQI - регистр импульсных ЗПр с запоминанием;

• RMI - регистр масок импульсных ЗПр;

• RNI - регистр номеров линий импульсных ЗПр;

• REr - регистр ошибок с запоминанием.

Регистр импульсных ЗПр с запоминанием доступен по чтению и записи "0", программная запись "1" в разряд регистра не изменяет его состояния.

Разряды региста импульсных ЗПр с запоминанием Q<i>, где i=0…15, аппаратно устанавливаются в "1" при появлении высокого уровня на соответствующем входе IP<i>67 и наличии «лог. 0» в разрядах регистра отключения входных сигналов Roff<OffHI>81,68 (младшие разряды) и Roff<OffHI>81 (старшие разряды). Разряды Q<i> сбрасываются программной записью "0" в соответствующий разряд регистра; по приходу сигнала "SR" (70) все разряды регистра устанавливаются в "0".

Если Roff<OffLI>81,68=1, то Q<i>, где i=0. 6 не устанавливаются, независимо от состояния входов IP0-IP6 70, если Roff<OffHI>81,68=1, то Q<i>, где i=7…15 не устанавливаются независимо от состояния входов 70 IP7 ÷ IP15.

Регистр масок импульсных ЗПр RMI доступен по чтению и записи.

При M<i>=0, где i=0…15, разрешается выдача ЗПр из соответствующего разряда Q<i> в разряд RFM<F0> или RFM<F1> в соответствие со значением соответствующего разряда N<i> регистра RNI; при M<i>=1 ЗПр не формируется.

По приходу сигнала "SR" (70) все разряды регистра устанавливаются в "1".

Регистр номеров линий импульсных ЗПр RNI доступен по чтению и записи.

При N<i>=0, где i=0…15, ЗПр Q<i> при M<i>=0 направляется в RFM<F0>,

при N<i>=1, где i=0…15, ЗПр Q<i> при M<i>=0 направляется в RFM<F1>.

По приходу сигнала "SR" (70) все разряды регистра устанавливаются в "0".

Регистр ошибок с запоминанием REr представлен на фиг. 9 доступен по чтению и записи "0", программная запись "1" не изменяет состояния соответствующего разряда.

Разряды регистра аппаратно устанавливаются в "1" при появлении высокого уровня на соответствующем входе 70 IP7 - IP15, и наличии «лог. 0» в разряде регистра отключения входных сигналов Roff<OffE>81,68. Если Roff<OffE>81,68=«лог. 1», то разряды не устанавливаютсяА независимо от состояния входов 70 IP7 - IP15.

Разряду Er0A соответствует вход 70 IP7, далее по порядку разряду Er2C соответствует вход 70 IP15.

Разряды REr сбрасываются программной записью "0", по приходу сигнала "SR" 70 все разряды регистра устанавливаются в "0". Разряды с 0 по 6 физически не существуют и читаются "0".

Узел приема и обработки потенциальных сигналов 56 (ППр) обеспечивает прием и обработку 16 потенциальных прерываний.

Потенциальные прерывания подаются на вход КРМ 66 в последовательном коде. Считывание 16-разрядного кода прерываний осуществляется по сигналу "S1" 66, период следования которого - 1 миллисекунда. Сигнал "S1M" 66 представляет собой мажорированный сигнал "S1" и используется в резервированных системах для межканальной синхронизации. В системах без резервирования необходимо соединить выводы S1 и S1M.

Сигнал на входе КРМ 66 представляет собой результат последовательного опроса состояния 16 датчиков потенциальных (контактных) прерываний. Опрос производится за 16 тактов частоты С. Временная диаграмма опроса потенциальных прерывний представлена на фиг. 10.

В состав узла ППр входят программно-доступные регистры:

• RQP - регистр потенциальных ЗПр с запоминанием;

• RMP - регистр масок потенциальных ЗПр;

• RNP - регистр номеров линий потенциальных ЗПр;

• RFP - регистр признаков потенциальных ЗПр без запоминания.

Регистр доступен по чтению и записи "0", программная запись "1" в разряд регистра не изменяет его состояния; программная запись "1" не изменяет состояния соответствующего разряда.

Разряд QP<i>, где i=0…15, аппаратно устанавливаются в "1" при высоком уровне сигнала на входе КРМ 66 во время отрицательного фронта i-го импульса опроса на выходе "С" и наличии «0» в разряде Roff<OffP>81, сбрасывается в "0" программной записью; по приходу сигнала «SR» 70 все разряды регистра устанавливаются в "0".

Регистр масок потенциальных ЗПр RMP шестнадцатиразрядный.

Регистр масок потенциальных ЗПр RMP доступен по чтению и записи.

При Mp<i>=0, где i=0…15, разрешается выдача ЗПр из соответствующего разряда QP<i> в разряд RFM<F2> или RFM<F3> в соответствие со значением соответствующего разряда NP<i> регистра RNP; при MP<i>=1 ЗПр не формируется.

По приходу сигнала "SR" 70 все разряды регистра устанавливаются в "1".

Регистр номеров линий потенциальных ЗПр RNP шестнадцатиразрядный.

Регистр RNP доступен по чтению и записи.

При NP<i>=0, где i=0…15, ЗПр QP<i> при MP<i>=0 направляется в RFM<F2>,

при NP<i>=1, где i=0…15, ЗПр QP<i> при MP<i>=0 направляется в RFM<F3>.

По приходу сигнала "SR" 70 все разряды регистра устанавливаются в "0".

Регистр признаков потенциальных ЗПр без запоминания RFP шестнадцатиразрядный.

Регистр доступен только по чтению, FP<i>, где i=0…15, аппаратно устанавливаются в "1" при высоком уровне на входе КРМ 66 во время отрицательного фронта i-го импульса опроса на выходе "С" и сбрасываются в "0" при низком уровне на входе КРМ 66 в этот момент.

По приходу сигнала «SR» 70 все разряды регистра устанавливаются в "0".

Регистр управления входными и выходными сигналами Roff 81 предназначен для включения и отключения различных групп входных сигналов.

Регистр доступен по записи и чтению.

Назначение разрядов регистра следующее:

• OffE 68 - наличие «0» в данном разряде разрешает поступление сигналов со входов IP7 - IP15 70 в регистр одноканальных ошибок REr, «1» - запрещает; по сигналу «SR» 70 данный разряд устанавливается в «1»;

• OffLI 68 - наличие «0» в данном разряде разрешает поступление сигналов со входов 70 IP0-IP6 в регистр импульсных ЗПр RQI, «1» - запрещает; по сигналу «SR» 70 данный разряд устанавливается в «1»;

• OffHI - наличие «0» в данном разряде разрешает поступление сигналов со входов IP7 - IP15 67 в регистр импульсных ЗПр RQI, «1» - запрещает; по сигналу «SR» 70 данный разряд устанавливается в «1»;

• OffP - наличие «0» в данном разряде разрешает поступление сигнала со входа КРМ 66 в регистр импульсных ЗПр RQP, «1» - запрещает; по сигналу «SR» 70 данный разряд устанавливается в «1»;

• GeP - данный разряд управляет выбором входа внешней частоты 1 МГц; при GeP=0 используется вход F1A 70, при GeP=1 используется вход F1B 70; по сигналу «SR» 70 данный разряд устанавливается в «0»;

• Нор - наличие «1» в данном разряде разрешает трансляцию сигнала метки времени со входа MV 70 на выход ТСС 69, «0» - запрещает; по сигналу «SR» 70 данный разряд устанавливается в «0».

Разряды с 6 по 15 физически отсутствуют и читаются как «0».

Узел регистров 57 состоит из регистра выдачи релейных сигналов RreI, регистра выдачи телеметрии RTIm и регистра режимов работы RR.

Регистр выдачи релейных сигналов RReI предназначен для обеспечения выдачи сигнала CVR 64 при выполнении операции программной записи в данный регистр.

Временная диаграмма выдачи сигнала CVR приведена на фиг. 5.

Регистр RReI шестнадцатиразрядный.

При выполнении операции чтения регистр всегда читается как «0».

Регистр выдачи телеметрии RTIm предназначен для обеспечения выдачи сигнала CVT 64 при выполнении операции телеметрии.

Временная диаграммы выдачи сигнала CVT приведена на фиг. 5.

Регистр RTIm шестнадцатиразрядный.

Регистр доступен по записи и чтению. По приходу сигнала "SR" 70 все разряды регистра сбрасываются в "0".

Регистр режимов работы RR предназначен для управления внешними сигналами RDY и RTST 64, индицирующими режим работы системы.

Регистр RR имеет следующий формат - RTST первый разряд, RDY - программной записи в данный регистр и для хранения кода нулевой разряд.

Регистр доступен по записи и чтению. По приходу сигнала "SR" 70 все разряды регистра сбрасываются в "0".

Состояние разряда RDY отображается на выходе RDY 64.

| название | год | авторы | номер документа |

|---|---|---|---|

| ТРЕХКАНАЛЬНАЯ РЕЗЕРВИРОВАННАЯ УПРАВЛЯЮЩАЯ СИСТЕМА | 2008 |

|

RU2387000C1 |

| Устройство для контроля магистралей электронных вычислительных машин | 1981 |

|

SU964648A1 |

| ОТКАЗОУСТОЙЧИВАЯ СИСТЕМА УПРАВЛЕНИЯ | 2021 |

|

RU2763092C1 |

| Трехканальная резервированная микропроцессорная система | 1985 |

|

SU1378287A1 |

| Устройство для обмена информацией | 1987 |

|

SU1497619A1 |

| КОНТРОЛЛЕР ПЕРЕДАЧИ ДАННЫХ | 2013 |

|

RU2514135C1 |

| ОТКАЗОУСТОЙЧИВАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА С АППАРАТНО-ПРОГРАММНОЙ РЕАЛИЗАЦИЕЙ ФУНКЦИЙ ОТКАЗОУСТОЙЧИВОСТИ И ДИНАМИЧЕСКОЙ РЕКОНФИГУРАЦИИ | 2010 |

|

RU2455681C1 |

| Многоканальное устройство управления шаговым двигателем | 1990 |

|

SU1789970A1 |

| Устройство для контроля и восстановления микропроцессорной системы | 1985 |

|

SU1317441A1 |

| Устройство для дешифрации команд | 1987 |

|

SU1532932A1 |

Изобретение относится к области вычислительной техники и может использоваться при построении высоконадежных вычислительных управляющих систем, предназначенных для приема информации от абонентов, обработки принятой информации и выдачи результирующей информации абоненту. Технический результат заключается в расширении функциональных возможностей в части обеспечения приема и обработки внешних импульсных и потенциальных сигналов и отсчета временных интервалов. Такой результат достигается за счет того, что в трехканальную резервированную управляющую систему в каждый модуль А, В, С дополнительно введены узел интерфейса шины Q-bus, узел таймеров синхронизации, узел приема и обработки импульсных сигналов, узел приема и обработки потенциальных сигналов, узел регистров с соответствующими связями. 2 з.п. ф-лы, 11 ил.

1. Трехканальная резервированная управляющая система, содержащая первый системный модуль А, второй системный модуль В, третий системный модуль С, причем каждый модуль А, В, С включает процессор с шиной процессора P-bus, ОЗУ, ПЗУ, группу мажоритарных элементов, генератор, первую группу, вторую группу, третью группу мажоритарных устройств, контроллер функциональных узлов, первое, второе, третье, четвертое приемо-передающие устройства, первый и второй контроллеры мультиплексного канала обмена, периферийный контроллер, шину Q-bus и буферное ОЗУ, соединенное с шиной L-bus, первая двунаправленная группа входов-выходов которой соединена с двунаправленной группой входов-выходов первого контроллера мультиплексного канала обмена, первый и второй входы которого соединены с выходами первого и второго приемо-передающих устройств, группы входов-выходов которых являются первой и второй группами входов-выходов системы соответственно, третья и четвертая группы входов-выходов которой являются группами входов-выходов третьего и четвертого приемо-передающих устройств, выходы которых соединены с первым и вторым входами второго контроллера мультиплексного канала обмена, группа входов-выходов которого является второй группой входов-выходов шины L-bus, причем первая группа выходов модуля А состоит из первых групп выходов второй и третьей групп мажоритарных устройств и соединена с первыми группами входов второй и третьей групп мажоритарных устройств модулей В и С, первая группа выходов модуля В состоит из первых групп выходов второй и третьей групп мажоритарных устройств модуля В и соединена с первыми группами входов второй и третьей групп мажоритарных устройств модуля А и со вторыми группами входов второй и третьей групп мажоритарных устройств модуля С, первая группа выходов модуля С состоит из первых групп выходов второй и третьей групп мажоритарных устройств модуля С и соединена со вторыми группами входов второй и третьей групп мажоритарных устройств модулей А и В, причем вторая группа выходов второй группы мажоритарных устройств соединена с первой группой входов периферийного контроллера, первая группа входов-выходов которого соединена с первой группой входов-выходов третьей группы мажоритарных устройств, вторая группа входов-выходов которых соединена с первой группой входов-выходов шины Q-bus, вторая группа входов-выходов которой соединена с первой группой входов-выходов контроллера функциональных узлов, вторая группа входов-выходов которого соединена с группами входов-выходов ОЗУ, ПЗУ и первой группой входов-выходов первой группы мажоритарных устройств, вторая группа входов-выходов которых является шиной Р-bus и соединена с группой входов-выходов процессора, группа выходов которого соединена с первой группой входов группы мажоритарных элементов, первая группа выходов которых соединена с группой входов процессора, вход которого соединен с выходом генератора, со входами первой, второй и третьей группами мажоритарных устройств, первого и второго контроллеров мультиплексного канала обмена, периферийного контроллера и контроллера функциональных узлов, первая и вторая группы выходов соединены с группами входов ОЗУ и ПЗУ соответственно, третья группа входов-выходов шины L-bus соединена со второй группой входов-выходов периферийного контроллера, вторая группа входов которого соединена со второй группой выходов третьей группы мажоритарных устройств, третья группа входов которых соединена с первой группой входов системы, вторая группа входов которой соединена с первой группой входов первой группы мажоритарных устройств, вторая группа входов которых соединена с третьей группой выходов контроллера функциональных узлов, четвертая группа выходов которого соединена с первой группой входов шины Q-bus, первая группа выходов которой соединена с первой группой входов контроллера функциональных узлов, вторая группа выходов модуля А состоит из второго выхода генератора и вторых групп выходов группы мажоритарных элементов и первой группы мажоритарных устройств и соединена с третьими группами входов модулей В и С, вторая группа выходов модуля В состоит из второго выхода генератора и вторых групп выходов группы мажоритарных элементов и первой группы мажоритарных устройств модуля В и соединена с третьей группой входов модуля А и четвертой группой входов модуля С, вторая группа выходов модуля С состоит из второго выхода генератора и вторых групп выходов группы мажоритарных элементов и первой группы мажоритарных устройств модуля С и соединена с четвертыми группами входов модулей А и С, причем третья группа входов модулей соединена с первым входом генератора, со второй группой входов группы мажоритарных элементов и третьей группой входов первой группы мажоритарных устройств, четвертая группа входов модулей соединена со вторым входом генератора, с третьей группой входов группы мажоритарных элементов и четвертой группой входов первой группы мажоритарных устройств, отличающаяся тем, что в трехканальную резервированную управляющую систему в каждый модуль А, В, С дополнительно введены узел интерфейса шины Q-bus, узел таймеров синхронизации, узел приема и обработки импульсных сигналов, узел приема и обработки потенциальных сигналов, узел регистров, группа входов-выходов которого соединена с группами входов-выходов узла приема и обработки потенциальных сигналов, узла приема и обработки импульсных сигналов, узла интерфейса шины Q-bus, узла таймеров синхронизации, первая группа входов которого соединена с первыми группами входов узла регистров, узла приема и обработки импульсных сигналов, узла приема и обработки потенциальных сигналов и группой выходов узла интерфейса шины Q-bus, группа входов-выходов которого соединена с третьей группой входов-выходов шины Q-bus, вторая группа выходов которой соединена с группой входов узла интерфейса шины Q-bus, вторая группа выходов которого соединена со второй группой входов шины Q-bus, причем третья группа входов системы соединена со второй группой входов узла регистров, группа выходов которого является первой группой выходов системы, вторая группа выходов которой является группой выходов узла приема и обработки потенциальных сигналов, вторая группа входов которого является четвертой группой входов системы, пятая группа входов которой является второй группой входов узла приема и обработки импульсных сигналов, третья группа входов которого соединена с первой группой выходов узла таймеров синхронизации, первый выход которого соединен с первым выходом системы, шестая группа входов которой является второй группой входов узла таймеров синхронизации, третья и четвертая группы входов которого соединены с третьими группами выходов модуля В и С соответственно, причем вход узла регистров соединен с выходом генератора, выход узла приема и обработки импульсных сигналов соединен со входом узла приема и обработки потенциальных сигналов, причем выход контроллера функциональных узлов соединен со входом узла таймеров синхронизации, вторая группа выходов которого соединена с первой группой входов узла интерфейса шины Q-bus, третья группа выходов узла таймеров синхронизации является третьей группой выходов модуля А и соединена с третьими группами входов модулей В и С, причем третьи группы выходов модулей В и С соединены с четвертыми группами входов модулей С и В соответственно.

2. Трехканальная резервированная управляющая система по п. 1, отличающаяся тем, что узел таймеров синхронизации содержит первый, второй и третий таймеры синхронизации, мультиплексор, регистр, первый, второй и третий мажоритарные элементы, элемент ИЛИ и элемент И, выход которого соединен с первым входом элемента ИЛИ, выход которого является первым выходом узла таймеров синхронизации, первая группа выходов которого является группой выходов регистра, первый выход которого соединен с первым входом первого элемента И, второй вход которого является первым сигналом второй группы входов узла таймеров синхронизации, которая соединена с первыми группами входов первого, второго и третьего таймеров синхронизации и первым и вторым входами мультиплексора, выход которого является вторым выходом узла таймеров синхронизации и соединен с первыми входами таймеров синхронизации, первые выходы которых соединены с первым, вторым и третьим входами элемента ИЛИ, причем вторая группа выходов узла таймеров синхронизации соединена с первыми группами выходов первого и второго таймеров синхронизации, вторые выходы соединены с первыми входами первого, второго и третьего мажоритарных элементов и являются третьей группой выходов узла таймеров синхронизации, группа входов-выходов которого соединена с группами входов-выходов первого, второго и третьего таймеров синхронизации и регистра, второй выход которого соединен с третьим входом мультиплексора, первая группа входов узла таймеров синхронизации соединена с группой входов регистра, со вторыми группами входов таймеров синхронизации, вторые входы которых соединены с первым входом узла таймеров синхронизации, третья и четвертая группы входов которого соединены с первыми и вторыми группами входов первого, второго и третьего мажоритарных элементов, выход первого мажоритарного элемента соединен с третьими входами первого и второго таймеров синхронизации, выход второго мажоритарного элемента соединен с четвертым входом второго таймера синхронизации и третьим входом третьего таймера синхронизации, выход третьего мажоритарного элемента соединен с четвертыми входами третьего и первого таймеров синхронизации.

3. Трехканальная резервированная управляющая система по п. 1, отличающаяся тем, что таймер синхронизации содержит регистр управления, регистр управления конфигурацией, регистр счетчик, регистр фиксации, регистр предустановки, первый мультиплексор, второй мультиплексор, третий мультиплексор, четвертый мультиплексор, первый элемент И, второй элемент И, третий элемент И, четвертый элемент И, пятый элемент И, шестой элемент И, седьмой элемент И, восьмой элемент И, девятый элемент И, десятый элемент И, одиннадцатый элемент И, двенадцатый элемент И, тринадцатый элемент И, четырнадцатый элемент И, пятнадцатый элемент И, шестнадцатый элемент И, элемент ИЛИ, выход которого соединен с первыми входами десятого, одиннадцатого, четырнадцатого и пятнадцатого элементов И, выходы которых соединены с первыми входами регистра счетчика младших разрядов, регистра фиксации младших разрядов, регистра счетчика, регистра фиксации соответственно, группы входов-выходов которых соединены с группами входов-выходов регистра предустановки младших разрядов, регистра предустановки, регистра управления конфигурацией, регистра управления и являются группой входов-выходов таймера синхронизации, вторая группа входов которого соединена с группами входов регистра управления, регистра предустановки младших разрядов, регистра предустановки, регистра счетчика младших разрядов, регистра счетчика, регистра фиксации младших разрядов, регистра фиксации и регистра управления конфигурацией, первый выход которого соединен с первым входом третьего мультиплексора, выход которого соединен с первыми входами третьего и седьмого элементов И и четвертого мультиплексора, выход которого соединен с первым входом восьмого элемента И, выход которого соединен со вторым входом регистра счетчика, первый и второй выходы которого соединены со вторыми входами одиннадцатого и пятнадцатого элементов И, выходы которых соединены с первыми входами регистра фиксации младших разрядов и регистра фиксации, причем первая группа выходов таймера синхронизации соединена с выходами четвертого, пятого, двенадцатого и тринадцатого элементов И, первые входы четвертого и пятого элементов И соединены между собой и с выходом первого элемента И, а первые входы двенадцатого и тринадцатого элементов И соединены между собой и с выходом девятого элемента И, первый и второй входы которого соединены с первым (QI) и вторым (MI) выходами регистра управления, первый (ErQI) и второй (QI) входы которого соединены со вторым входом восьмого элемента И и выходом седьмого элемента И, второй вход которого соединен с третьим (Off) выходом регистра управления, четвертый (Cyc), пятый (SI) и шестой (Push) выходы которого соединены с первыми входами шестого элемента И, первого мультиплексора и элемента ИЛИ соответственно, второй вход которого соединен с выходом шестого элемента И, второй вход которого соединен с третьим (ErQ) и четвертым (Q) входами регистра управления и третьим входом таймера синхронизации, первый выход которого соединен с выходом шестнадцатого элемента И, первый вход которого соединен с пятым (OffO) входом регистра управления, седьмой (ЕхР) выход которого соединен со вторым входом третьего элемента И, выход которого соединен с третьим входом элемента ИЛИ, второй выход таймера синхронизации соединен с третьим выходом регистра счетчика и вторым входом шестнадцатого элемента И, причем первая группа входов таймера синхронизации соединена с первыми входами первого и второго мультиплексоров и вторым входом первого мультиплексора, выход которого соединен со вторым входом третьего мультиплексора, третий вход которого соединен с четвертым входом таймера синхронизации, первый и второй входы которого соединены со вторым входом второго мультиплексора и первым входом второго элемента И, выход которого соединен со вторым входом четвертого мультиплексора, третий вход которого соединен с восьмым (Tic) выходом регистра управления, второй выход регистра управления конфигурацией соединен со вторыми входами четвертого и двенадцатого элементов И и инверсными входами пятого и тринадцатого элементов И, девятый (Q) и десятый (М) выходы регистра управления соединены с первым и вторым входами первого элемента И, третий выход регистра управления конфигурацией соединен с третьим входом второго мультиплексора, выход которого соединен со вторым входом второго элемента И, выходы регистра предустановки младших разрядов и регистра предустановки соединены со вторыми входами десятого и четырнадцатого элементов И.

| ТРЕХКАНАЛЬНАЯ РЕЗЕРВИРОВАННАЯ УПРАВЛЯЮЩАЯ СИСТЕМА | 2008 |

|

RU2387000C1 |

| РЕЗЕРВИРОВАННАЯ МНОГОКАНАЛЬНАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2013 |

|

RU2527191C1 |

| US 6141769 A, 31.10.2000 | |||

| US 6732300 B1, 04.05.2004. | |||

Авторы

Даты

2017-05-03—Публикация

2015-08-19—Подача