Область техники, к которой относится изобретение

Настоящее изобретение относится к технической области отображения изображения и, в частности, к подложке матрицы и устройству отображения.

Уровень техники

При увеличенном размере подложки матрицы, длина и нагрузка линии передачи сигнала из области отображения подложки матрицы увеличиваются. В случае перекрытия сопротивления линии передачи сигнала для передачи сигнала положительного напряжения (VDD) или линии передачи сигнала для передачи сигнала отрицательного напряжения (VSS), яркость отображаемых изображений подложкой матрицы является неравномерной.

Раскрытие сущности изобретения

Варианты осуществления настоящего изобретения предлагают подложку матрицы и устройство отображения, и технические решения настоящего изобретения представляют собой следующие:

В одном аспекте настоящее изобретение предлагает подложку матрицы, включающую в себя:

базовую подложку, включающую в себя область отображения и периферийную область, окружающую область отображения, причем область отображения включает в себя первую границу, вторую границу, третью границу и четвертую границу;

множество субпикселей, расположенных в области отображения, причем по меньшей мере один из субпикселей включает в себя светоизлучающий элемент, а светоизлучающий элемент включает в себя первый электрод, светоизлучающий слой и второй электрод, которые последовательно установлены один на другой;

множество линий положительного напряжения, расположенных в области отображения и электрически подключенных к первому электроду;

шину положительного напряжения, расположенную в периферийной области и расположенную вдоль первой границы, причем шина положительного напряжения электрически соединена с множеством линий положительного напряжения;

первый вывод доступа положительного напряжения, второй вывод доступа положительного напряжения и третий вывод доступа положительного напряжения, расположенные на стороне шины положительного напряжения на удалении от области отображения, причем второй вывод доступа положительного напряжения расположен между первым выводом доступа положительного напряжения и третьим выводом доступа положительного напряжения, и первый вывод доступа положительного напряжения, второй вывод доступа положительного напряжения и третий вывод доступа положительного напряжения, соответственно, электрически подключены к шине положительного напряжения;

линию отрицательного напряжения, расположенную в периферийной области и окружающую вторую границу, третью границу и четвертую границу;

вспомогательный электрод, расположенный в периферийной области и окружающий первую границу, вторую границу, третью границу и четвертую границу, причем вспомогательный электрод соответственно электрически соединен с линией отрицательного напряжения и вторым электродом;

первый вывод доступа отрицательного напряжения, второй вывод доступа отрицательного напряжения и третий вывод доступа отрицательного напряжения, расположенные на стороне шины положительного напряжения на удалении от области отображения, первый вывод доступа отрицательного напряжения, расположенный на стороне первого вывода доступа положительного напряжения на удалении от второго вывода доступа положительного напряжения, причем второй вывод доступа отрицательного напряжения расположен между первым выводом доступа положительного напряжения и третьим выводом доступа положительного напряжения, третий вывод доступа отрицательного напряжения расположен на стороне третьего вывода доступа положительного напряжения на удалении от второго вывода доступа положительного напряжения, и первый вывод доступа отрицательного напряжения и третий вывод доступа отрицательного напряжения соответственно электрически подключены к линии отрицательного напряжения; и

вспомогательную линию отрицательного напряжения, расположенную в периферийной области между первым выводом доступа положительного напряжения и третьим выводом доступа положительного напряжения и расположенную между шиной положительного напряжения и вторым выводом доступа отрицательного напряжения, причем вспомогательная линия отрицательного напряжения соответственно электрически соединена со вторым выводом доступа отрицательного напряжения и вспомогательным электродом.

Как вариант, первый вывод доступа положительного напряжения, второй вывод доступа положительного напряжения и третий вывод доступа положительного напряжения используются для передачи сигнала положительного напряжения в светоизлучающий элемент через шину положительного напряжения, линии положительного напряжения и первый электрод; и

первый вывод доступа отрицательного напряжения, второй вывод доступа отрицательного напряжения и третий вывод доступа отрицательного напряжения используются для передачи сигнала отрицательного напряжения в светоизлучающий элемент через линию отрицательного напряжения, вспомогательную линию отрицательного напряжения, вспомогательный электрод и второй электрод.

Как вариант, подложка матрицы дополнительно включает в себя:

четвертый вывод доступа положительного напряжения, расположенный на стороне шины положительного напряжения на удалении от области отображения и расположенный между первым выводом доступа положительного напряжения и третьим выводом доступа положительного напряжения, причем четвертый вывод доступа положительного напряжения электрически соединен с шиной положительного напряжения; и

четвертый вывод доступа положительного напряжения используется для передачи сигнала положительного напряжения в светоизлучающий элемент через шину положительного напряжения, линии положительного напряжения и первый электрод.

Как вариант, подложка матрицы дополнительно включает в себя:

четвертый вывод доступа отрицательного напряжения, расположенный на стороне шины положительного напряжения на удалении от области отображения и расположенный между первым выводом доступа положительного напряжения и третьим выводом доступа положительного напряжения, причем четвертый вывод доступа отрицательного напряжения электрическим соединен со вспомогательной линией отрицательного напряжения; и

четвертый вывод доступа отрицательного напряжения используется для передачи сигнала отрицательного напряжения в светоизлучающий элемент через вспомогательную линию отрицательного напряжения, вспомогательный электрод и второй электрод.

Как вариант, второй вывод доступа отрицательного напряжения расположен между вторым выводом доступа положительного напряжения и третьим выводом доступа положительного напряжения, и подложка матрицы дополнительно включает в себя:

четвертый вывод доступа положительного напряжения и четвертый вывод доступа отрицательного напряжения, расположенные на стороне шины положительного напряжения на удалении от области отображения, причем четвертый вывод доступа положительного напряжения расположен между вторым выводом доступа отрицательного напряжения и третьим выводом доступа положительного напряжения и электрически подключен к шине положительного напряжения, а четвертый вывод доступа отрицательного напряжения расположен между вторым выводом доступа отрицательного напряжения и четвертым выводом доступа положительного напряжения и электрически подключен к вспомогательной линии отрицательного напряжения; и

четвертый вывод доступа положительного напряжения используется для передачи сигнала положительного напряжения в светоизлучающий элемент через шину положительного напряжения, линии положительного напряжения и первый электрод, а четвертый вывод доступа отрицательного напряжения используется для передачи сигнала отрицательного напряжения в светоизлучающий элемент через вспомогательную линию отрицательного напряжения, вспомогательный электрод и второй электрод.

Как вариант, по меньшей мере, один из субпикселей включает в себя тонкопленочный транзистор и соединительный электрод; и

тонкопленочный транзистор включает в себя активный слой, расположенный на базовой подложке, затвор, расположенный на стороне активного слоя на удалении от базовой подложки, и исток и сток, которые расположены на стороне затвора на удалении от базовой подложки.

Как вариант, шина положительного напряжения включает в себя первый подслой шины положительного напряжения и второй подслой шины положительного напряжения, и первый подслой шины положительного напряжения электрически соединен со вторым подслоем шины положительного напряжения; и

первый подслой шины положительного напряжения и исток или сток находятся в одном и том же слое, и второй подслой шины положительного напряжения соединен с электродом, расположенным в одном и том же слое.

Как вариант, первый подслой шины положительного напряжения электрически соединен со вторым подслоем шины положительного напряжения через сквозное отверстие шины положительного напряжения.

Как вариант, линия отрицательного напряжения включает в себя первый подслой линии отрицательного напряжения и второй подслой линии отрицательного напряжения, причем первый подслой линии отрицательного напряжения электрически соединен со вторым подслоем линии отрицательного напряжения;

вспомогательная линия отрицательного напряжения включает в себя первый подслой вспомогательной линии отрицательного напряжения и второй подслой вспомогательной линии отрицательного напряжения, причем первый подслой вспомогательной линии отрицательного напряжения электрически соединен со вторым подслоем вспомогательной линии отрицательного напряжения; и

первый подслой линии отрицательного напряжения и первый подслой вспомогательной линии отрицательного напряжения оба расположены в одном и том же слое с истоком или стоком, а второй подслой линии отрицательного напряжения и второй подслой вспомогательной линии отрицательного напряжения оба расположены в одном и том же слое с соединительным электродом.

Как вариант, первый подслой линии отрицательного напряжения электрически соединен со вторым подслоем линии отрицательного напряжения через сквозное отверстие линии отрицательного напряжения, и первый подслой вспомогательной линии отрицательного напряжения электрически соединен со вторым подслоем вспомогательной линии отрицательного напряжения через сквозное отверстие вспомогательной линии отрицательного напряжения.

Как вариант, по меньшей мере один из субпикселей включает в себя тонкопленочный транзистор;

тонкопленочный транзистор включает в себя активный слой, расположенный на базовой подложке, затвор, расположенный на стороне активного слоя на удалении от базовой подложки, и исток и сток, которые расположены на стороне затвора на удалении от базовой подложки; и

первый вывод доступа положительного напряжения, второй вывод доступа положительного напряжения, третий вывод доступа положительного напряжения и четвертый вывод доступа положительного напряжения все находятся в одном и том же слое с истоком или стоком.

Как вариант, по меньшей мере один из субпикселей включает в себя тонкопленочный транзистор;

тонкопленочный транзистор включает в себя активный слой, расположенный на базовой подложке, затвор, расположенный на стороне активного слоя на удалении от базовой подложки, и исток и сток, которые расположены на стороне затвора на удалении от базовой подложки; и

первый вывод доступа отрицательного напряжения, второй вывод доступа отрицательного напряжения, третий вывод доступа отрицательного напряжения и четвертый вывод доступа отрицательного напряжения все находятся в одном и том же слое с истоком или стоком.

Как вариант, вспомогательная линия отрицательного напряжения включает в себя первый подслой вспомогательной линии отрицательного напряжения и второй подслой вспомогательной линии отрицательного напряжения, и первый подслой вспомогательной линии отрицательного напряжения электрически соединен со вторым подслоем вспомогательной линии отрицательного напряжения; и

второй вывод доступа отрицательного напряжения, четвертый вывод доступа отрицательного напряжения и первый подслой вспомогательной линии отрицательного напряжения имеют интегральную структуру.

Как вариант, подложка матрицы дополнительно включает в себя:

печатную плату, расположенную на сторонах, на удалении от области отображения, первого вывода доступа положительного напряжения, второго вывода доступа положительного напряжения, третьего вывода доступа положительного напряжения, четвертого вывода доступа положительного напряжения, первого вывода доступа отрицательного напряжения, второго вывода доступа отрицательного напряжения, третьего вывода доступа отрицательного напряжения и четвертого вывода доступа отрицательного напряжения, при этом первый вывод доступа положительного напряжения, второй вывод доступа положительного напряжения, третий вывод доступа положительного напряжения, четвертый вывод доступа положительного напряжения, первый вывод доступа отрицательного напряжения, второй вывод доступа отрицательного напряжения, третий вывод доступа отрицательного напряжения и четвертый вывод доступа отрицательного напряжения соответственно электрически подключены к печатной плате.

Как вариант, вспомогательный электрод расположен на стороне линии отрицательного напряжения на удалении от базовой подложки, и вспомогательный электрод электрически соединен со вспомогательной линией отрицательного напряжения через сквозное отверстие вспомогательной линии отрицательного напряжения.

Как вариант, светоизлучающий элемент представляет собой органический светоизлучающий диод (OLED), первый электрод служит анодом и второй электрод является катодом.

В другом аспекте, настоящее изобретение предлагает устройство отображения, включающее в себя любую подложку матрицы в вышеуказанном аспекте.

Краткое описание чертежей

Далее, с целью иллюстрации технических решений в вариантах осуществления настоящего изобретения, представлено краткое и четкое описание вариантов осуществления со ссылкой на прилагаемые чертежи. Очевидно, что прилагаемые чертежи в следующем описании относятся только к некоторым вариантам осуществления настоящего изобретения, и специалисты в данной области техники могут получить другие чертежи из этих прилагаемых чертежей без творческих усилий.

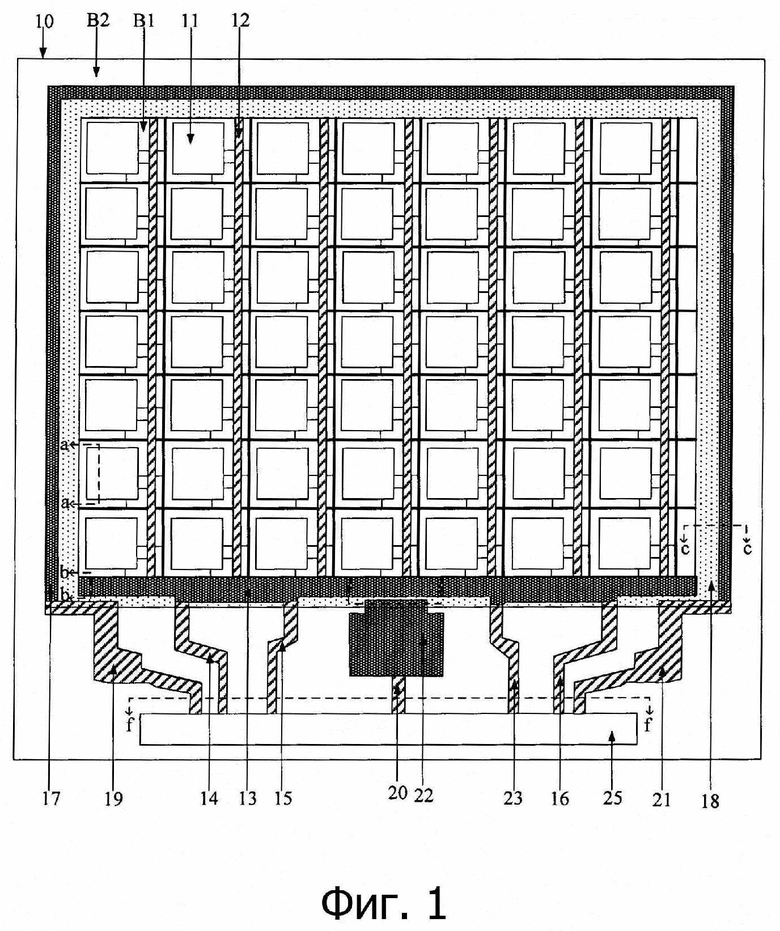

Фиг. 1 представляет собой вид спереди подложки матрицы, предоставленной вариантом осуществления настоящего изобретения;

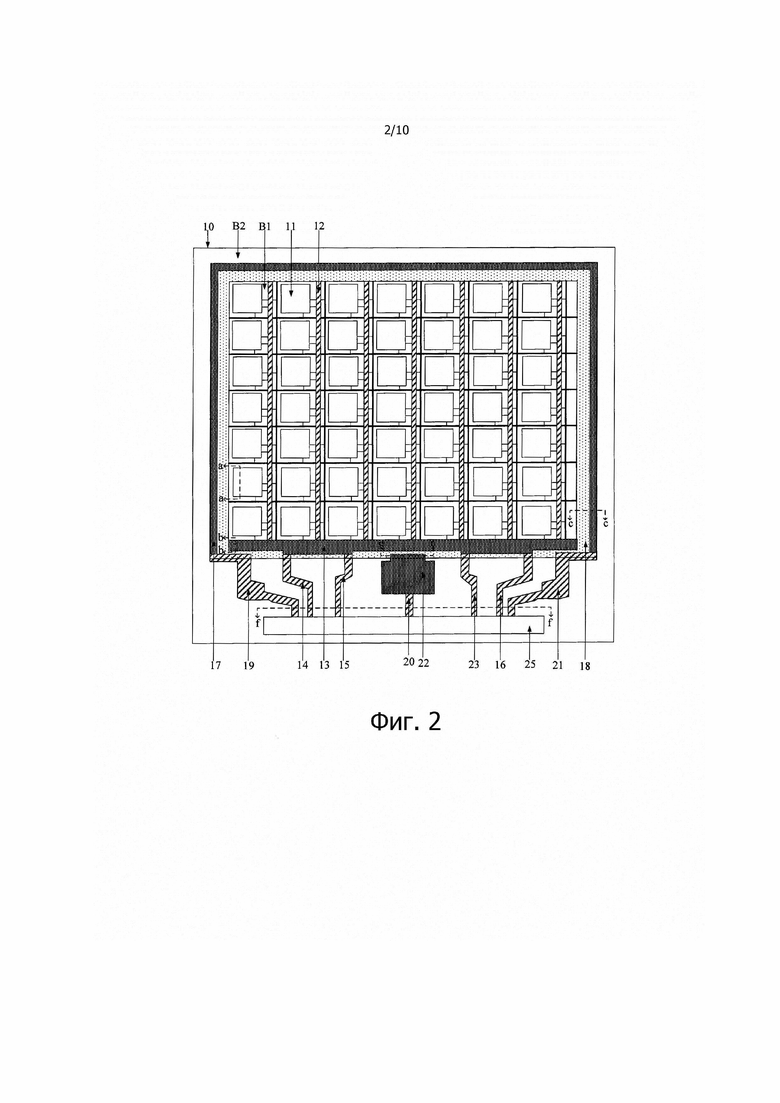

фиг. 2 является видом спереди другой подложки матрицы, предоставленной вариантом осуществления настоящего изобретения;

фиг. 3 является видом спереди другой подложки матрицы, предоставленной вариантом осуществления настоящего изобретения;

фиг. 4 является видом еще одной подложки матрицы, предоставленной вариантом осуществления настоящего изобретения;

фиг. 5 является видом в разрезе участка а-а, участка b-b, участка с-с и участка е-е подложки матрицы, показанной в любом из фиг. 1-фиг. 4;

фиг. 6 является видом в разрезе участка а-а и участка f-f подложки матрицы, показанной на фиг. 1;

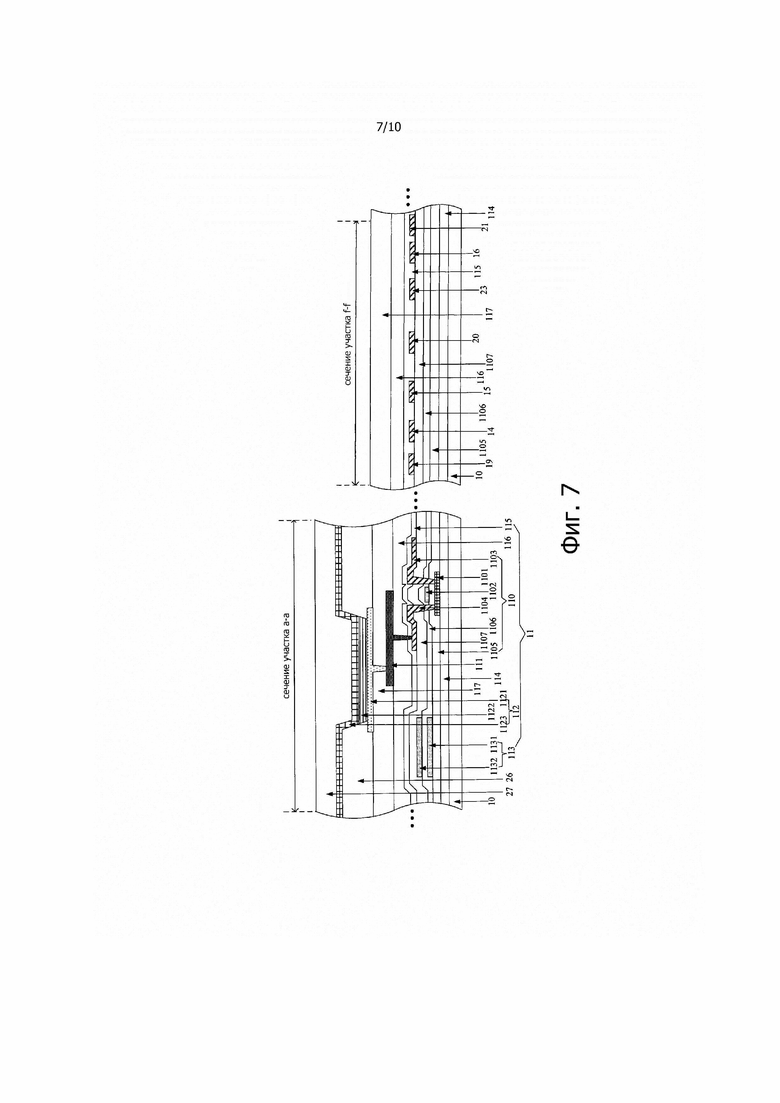

фиг. 7 является видом в разрезе участка а-а и участка f-f подложки матрицы, показанной на фиг. 2;

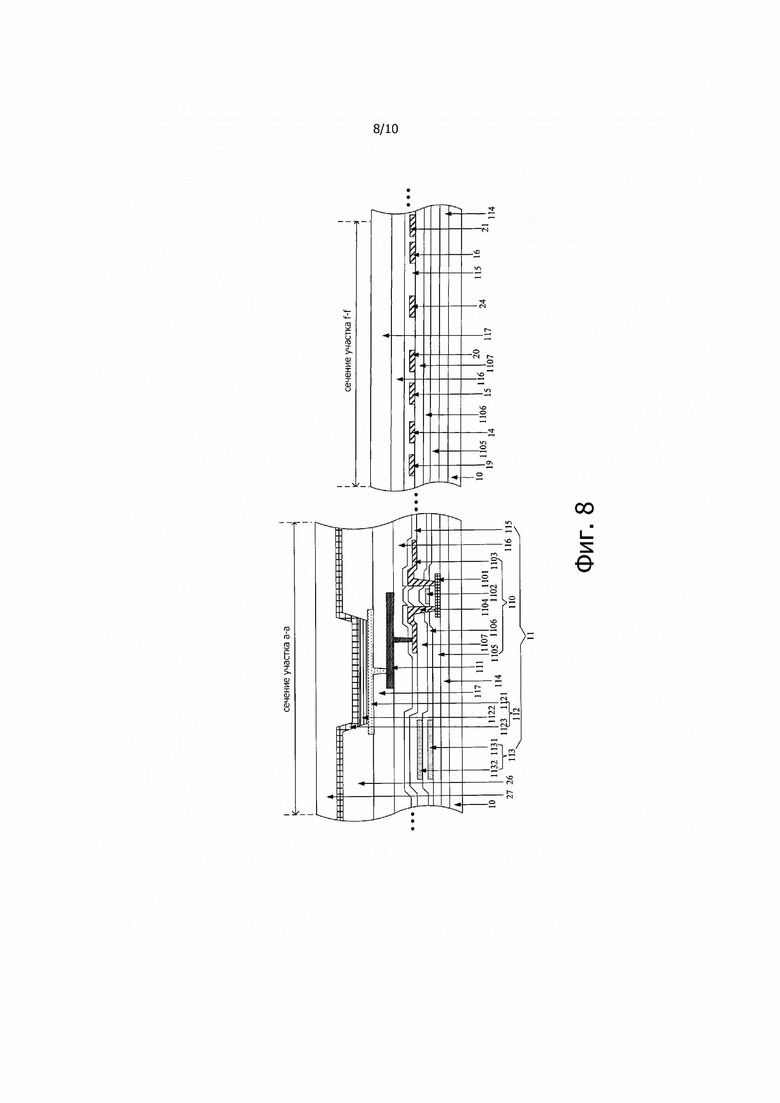

фиг. 8 является видом в разрезе участка а-а и участка f-f подложки матрицы, показанной на фиг. 3;

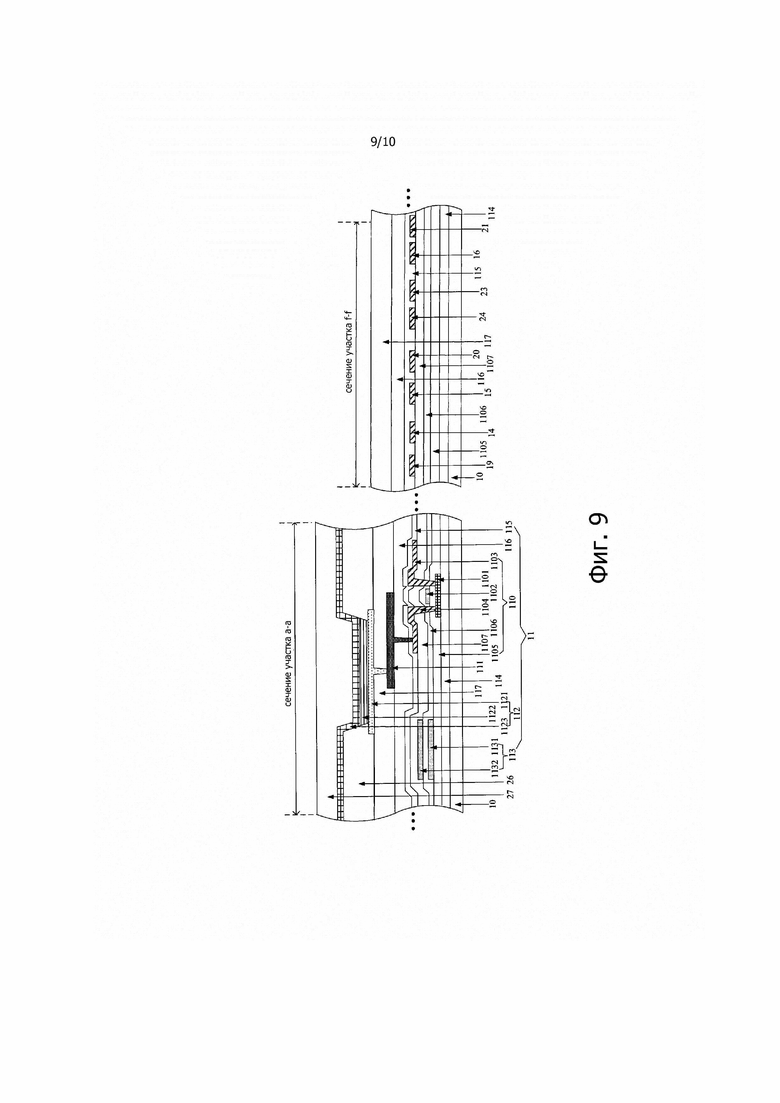

фиг. 9 является видом в разрезе участка а-а и участка f-f подложки матрицы, показанной на фиг. 4; и

фиг. 10 является видом в разрезе участка а-а и участка g-g подложки матрицы, показанной на фиг. 3 или фиг. 4.

Осуществление изобретения

Далее представлено подробное и четкое описание принципов, технических решений и преимуществ настоящего изобретения, способов реализации настоящего изобретения со ссылкой на прилагаемые чертежи.

Вариант осуществления настоящего изобретения предлагает подложку матрицы. В подложке матрицы как линия для передачи сигнала для передачи сигнала положительного напряжения в субпиксель, так и линия для передачи сигнала для передачи сигнала отрицательного напряжения в субпиксель имеют небольшое сопротивление, что снижает неравномерность яркости отображаемых изображений подложкой матрицы и обеспечивает однородность яркости изображений, отображаемых подложкой матрицы. Подробные решения настоящего изобретения представляют собой следующие.

В варианте осуществления настоящего изобретения подложка матрицы включает в себя:

базовую подложку, включающую в себя область отображения и периферийную область, окружающую область отображения, область отображения включает в себя первую границу, вторую границу, третью границу и четвертую границу;

множество субпикселей, расположенных в области отображения, причем по меньшей мере один из субпикселей включает в себя светоизлучающий элемент, и светоизлучающий элемент включает в себя первый электрод, светоизлучающий слой и второй электрод, которые последовательно размещены друг на друге;

множество линий положительного напряжения, расположенных в области отображения и электрически соединенных с первым электродом;

шину положительного напряжения, расположенную в периферийной области и расположенную вдоль первой границы, причем шина положительного напряжения электрически соединена с множеством линий положительного напряжения;

первый вывод доступа положительного напряжения, второй вывод доступа положительного напряжения и третий вывод доступа положительного напряжения, расположенные на стороне шины положительного напряжения на удалении от области отображения, второй вывод доступа положительного напряжения расположен между первым выводом доступа положительного напряжения и третьим выводом доступа положительного напряжения, и первый вывод доступа положительного напряжения, второй вывод доступа положительного напряжения и третий вывод доступа положительного напряжения соответственно электрически подключены к шине положительного напряжения;

линию отрицательного напряжения, расположенную в периферийной области и окружающую вторую границу, третью границу и четвертую границу;

вспомогательный электрод, расположенный в периферийной области и окружающий первую границу, вторую границу, третью границу и четвертую границу, причем вспомогательный электрод соответственно электрически соединен с линией отрицательного напряжения и вторым электродом;

первый вывод доступа отрицательного напряжения, второй вывод доступа отрицательного напряжения и третий вывод доступа отрицательного напряжения, расположенные на стороне шины положительного напряжения на удалении от области отображения, причем первый вывод доступа отрицательного напряжения расположен на стороне первого вывода доступа положительного напряжения на удалении от второго вывода доступа положительного напряжения, второй вывод доступа отрицательного напряжения расположен между первым выводом доступа положительного напряжения и третьим выводом доступа положительного напряжения, третий вывод доступа отрицательного напряжения расположен на стороне третьего вывода доступа положительного напряжения на удалении от второго вывода доступа положительного напряжения, и первый вывод доступа отрицательного напряжения и третий вывод доступа отрицательного напряжения соответственно электрически подключены к линии отрицательного напряжения; и

вспомогательную линию отрицательного напряжения, расположенную в периферийной области, расположенную между первым выводом доступа положительного напряжения и третьим выводом доступа положительного напряжения и расположенную между шиной положительного напряжения и вторым выводом доступа отрицательного напряжения, причем вспомогательная линия отрицательного напряжения соответственно электрически соединена со вторым выводом доступа отрицательного напряжения и вспомогательным электродом.

Как вариант, первый вывод доступа положительного напряжения, второй вывод доступа положительного напряжения и третий вывод доступа положительного напряжения используются для передачи сигнала положительного напряжения в светоизлучающий элемент через шину положительного напряжения, линии положительного напряжения и первый электрод; а первый вывод доступа отрицательного напряжения, второй вывод доступа отрицательного напряжения и третий вывод доступа отрицательного напряжения используются для передачи сигнала отрицательного напряжения в светоизлучающий элемент через линию отрицательного напряжения, вспомогательную линию отрицательного напряжения, вспомогательный электрод и второй электрод.

Например, фиг. 1-фиг. 4 иллюстрируют виды спереди четырех подложек матрицы, предоставляемых вариантом осуществления настоящего изобретения. Как показано на фиг. 1-фиг. 4, подложка матрицы включает в себя:

базовую подложку 10, включающую в себя область В1 отображения и периферийную область B2, окружающую область B1 отображения, и область В1 отображения включает в себя первую границу (на фиг. 1-фиг. 4 не обозначена), вторую границу (на фиг. 1-фиг. 4 не обозначена), третью границу (на фиг. 1-фиг. 4 не обозначена) и четвертую границу (на фиг. 1-фиг. 4 не обозначена); и вариант осуществления настоящего изобретения, в котором периферийная область B2 окружает периферию области В1 отображения в качестве примера для описания;

множество субпикселей 11, расположенных в области B1 отображения, по меньшей мере, один из субпикселей 11 включает в себя светоизлучающий элемент (на фиг. 1-фиг. 4 не обозначен) и светоизлучающий элемент включает в себя первый электрод (на фиг. 1-фиг. 4 не обозначен), светоизлучающий слой (на фиг. 1-фиг. 4 не обозначен) и второй электрод (на фиг. 1-фиг. 4 не обозначен), которые последовательно размещены друг на друге; и множество субпикселей 11, выполненные с возможностью излучать свет для реализации функции отображения;

множество линий 12 положительного напряжения, расположенных в области B1 отображения и электрически соединенных с первым электродом светоизлучающего элемента;

шину 13 положительного напряжения, расположенную в периферийной области B2 и расположенную вдоль первой границы области В1 отображения, причем шина 13 положительного напряжения электрически соединена с множеством линий 12 положительного напряжения;

первый вывод 14 доступа положительного напряжения, второй вывод 15 доступа положительного напряжения и третий вывод 16 доступа положительного напряжения, расположенные на стороне шины 13 положительного напряжения на удалении от области B1 отображения, причем второй вывод 15 доступа положительного напряжения расположен между первым выводом 14 доступа положительного напряжения и третьим выводом 16 доступа положительного напряжения, и первый вывод 14 доступа положительного напряжения, второй вывод 15 доступа положительного напряжения и третий вывод 16 доступа положительного напряжения соответственно электрически подключены к шине 13 положительного напряжения;

линию 17 отрицательного напряжения, расположенную в периферийной области B2 и окружающую вторую границу, третью границу и четвертую границу области В1 отображения;

вспомогательный электрод 18, расположенный в периферийной области B2 и окружающий первую границу, вторую границу, третью границу и четвертую границу области В1 отображения, причем вспомогательный электрод 18 соответственно электрически соединен с линией 17 отрицательного напряжения и вторым электродом светоизлучающего элемента;

первый вывод 19 доступа отрицательного напряжения, второй вывод 20 доступа отрицательного напряжения и третий вывод 21 доступа отрицательного напряжения, расположенные на стороне шины 13 положительного напряжения на удалении от области B1 отображения, первый вывод 19 доступа отрицательного напряжения расположен на стороне первого вывода 14 доступа положительного напряжения на удалении от второго вывода 15 доступа положительного напряжения, второй вывод 20 доступа отрицательного напряжения расположен между первым выводом 14 доступа положительного напряжения и третьим выводом 16 доступа положительного напряжения, третий вывод 21 доступа отрицательного напряжения расположен на стороне третьего вывода 16 доступа положительного напряжения на удалении от второго вывода 15 доступа положительного напряжения, причем первый вывод 19 доступа отрицательного напряжения и третий вывод 21 доступа отрицательного напряжения соответственно электрически подключены к линии 17 отрицательного напряжения; и вариант осуществления настоящего изобретения рассматривает случай, в котором второй вывод 20 доступа отрицательного напряжения расположен между вторым выводом 15 доступа положительного напряжения и третьим выводом 16 доступа положительного напряжения, в качестве примера для описания; и

вспомогательную линию 22 отрицательного напряжения, расположенную в периферийной области B2, расположенную между первым выводом 14 доступа положительного напряжения и третьим выводом 16 доступа положительного напряжения и расположенную между шиной 13 положительного напряжения и вторым выводом 22 доступа отрицательного напряжения, причем вспомогательная линия 22 отрицательного напряжения соответственно электрически соединена со вторым выводом 20 доступа отрицательного напряжения и вспомогательным электродом 18.

Как вариант, первый вывод 14 доступа положительного напряжения, второй вывод 15 доступа положительного напряжения и третий вывод 16 доступа положительного напряжения используются для передачи сигнала положительного напряжения в светоизлучающий элемент через шину 13 положительного напряжения, линию 12 положительного напряжения и первый электрод; и первый вывод 19 доступа отрицательного напряжения, второй вывод 20 доступа отрицательного напряжения и третий вывод 21 доступа отрицательного напряжения используются для передачи сигнала отрицательного напряжения в светоизлучающий элемент через линию 17 отрицательного напряжения, вспомогательную линию 22 отрицательного напряжения, вспомогательный электрод 18 и второй электрод.

Например, как показано на фиг. 1-фиг. 4, в первом выводе 14 доступа положительного напряжения, втором выводе 15 доступа положительного напряжения и третьем выводе 16 доступа положительного напряжения каждый вывод доступа положительного напряжения используется для передачи через шину 13 положительного напряжения, линию 12 положительного напряжения и первый электрод, который электрически подключен к линии 12 положительного напряжения, сигнала положительного напряжения в светоизлучающий элемент, где расположен первый электрод. Сигнал положительного напряжения на каждом выводе доступа положительного напряжения может быть передан в линию 12 положительного напряжения, ближайшую к выводу доступа положительного напряжения, через шину 13 положительного напряжения, тем самым передаваясь в светоизлучающий элемент, электрически подключенный к линии 12 положительного напряжения. Например, сигналы положительного напряжения на первом выводе 14 доступа положительного напряжения и третьем выводе 16 доступа положительного напряжения могут быть переданы через шину 13 положительного напряжения в светоизлучающие элементы, электрически соединенные с линиями 12 положительного напряжения с левой и правой стороны (левые и правые стороны положения размещения, показанные на фиг. 1-фиг. 4), и сигнал положительного напряжения на втором выводе 15 доступа положительного напряжения может быть передан через шину 13 положительного напряжения в светоизлучающий элемент, электрически соединенный с линией 12 положительного напряжения в центральной области (центральная область области размещения, показанная на фиг. 1-фиг. 4). Таким образом, путь, по которому проходит сигнал положительного напряжения, передаваемый из вывода доступа положительного напряжения в светоизлучающий элемент, является коротким, и линия для передачи сигнала для передачи сигнала положительного напряжения в светоизлучающий элемент является короткой и имеет небольшое сопротивление, что обеспечивает однородность яркости изображений, отображаемых подложкой матрицы.

Для специалистов в данной области техники очевидно, что первый вывод 14 доступа положительного напряжения, второй вывод 15 доступа положительного напряжения и третий вывод 16 доступа положительного напряжения одновременно передают сигнал положительного напряжения в светоизлучающие элементы всех субпикселей в подложке матрицы, и только первый вывод 14 доступа положительного напряжения и третий вывод 16 доступа положительного напряжения являются ближайшими к светоизлучающим элементам на левой и правой сторонах, так что путь, через который проходит сигнал положительного напряжения, передаваемый из первого вывода 14 доступа положительного напряжения и третьего вывода 16 доступа положительного напряжения в светоизлучающие элементы на левой и правой сторонах, является коротким и сопротивления невелико, а второй вывод 15 доступа положительного напряжения является ближайшим к светоизлучающему элементу в центральной области, так что путь, через который проходит сигнал положительного напряжения из второго вывода 15 доступа положительного напряжения в светоизлучающий элемент в центральной области, является коротким и сопротивление невелико.

Например, как показано на фиг. 1-фиг. 4, каждый вывод доступа отрицательного напряжения из первого вывода 19 доступа отрицательного напряжения и третьего вывода 21 доступа отрицательного напряжения используется для передачи сигнала отрицательного напряжения в светоизлучающий элемент через линию 17 отрицательного напряжения, вспомогательный электрод 18 и второй электрод, и второй вывод 20 доступа отрицательного напряжения используется для передачи сигнала отрицательного напряжения в светоизлучающий элемент через вспомогательную линию 22 отрицательного напряжения, вспомогательный электрод 18 и второй электрод. Сигналы отрицательного напряжения на первом выводе 19 доступа отрицательного напряжения и третьем выводе 21 доступа отрицательного напряжения могут быть переданы через линию 17 отрицательного напряжения и вспомогательный электрод 18 в светоизлучающие элементы на левой и правой сторонах (левая и правая сторона положения размещения, показанной на фиг. 1-фиг. 4), и сигнал отрицательного напряжения на втором выводе 20 доступа отрицательного напряжения может быть передан через вспомогательную линию 22 отрицательного напряжения и вспомогательный электрод 18 в светоизлучающий элемент в центральной области (центральная область положения размещения, показанной на фиг. 1-фиг. 4). Следовательно, путь по которому проходит сигнал отрицательного напряжения, передаваемый из вывода доступа отрицательного напряжения в светоизлучающий элемент, является коротким, и линия передачи сигнала для передачи сигнала отрицательного напряжения в светоизлучающий элемент является короткой и имеет небольшое сопротивление, что выгодно для обеспечения однородности яркости изображений, отображаемых подложкой матрицы.

Специалистам в данной области техники понятно, что первый вывод 19 доступа отрицательного напряжения, второй вывод 20 доступа отрицательного напряжения и третий вывод 21 доступа отрицательного напряжения одновременно передают сигнал отрицательного напряжения в светоизлучающие элементы всех субпикселей в подложке матрицы, и только первый вывод 19 доступа отрицательного напряжения и третий вывод 21 доступа отрицательного напряжения являются ближайшими к светоизлучающим элементам на левой и правой сторонах, так что путь через который проходит сигнал отрицательного напряжения, передаваемый из первого вывода 19 доступа отрицательного напряжения и третьего вывода 21 доступа отрицательного напряжения в светоизлучающие элементы на левой и правой сторонах, является небольшим и сопротивление невелико, и второй вывод 20 доступа отрицательного напряжения является блажащим к светоизлучающему элементу в центральной области, так что путь, через который проходит сигнал положительного напряжения, переданный из второго вывода 20 доступа отрицательного напряжения в светоизлучающий элемент в центральной области, является коротким и сопротивление невелико.

Таким образом, вариант осуществления настоящего изобретения предлагает подложку матрицы, в котором подложка матрицы включает в себя первый вывод доступа положительного напряжения, второй вывод доступа положительного напряжения, третий вывод доступа положительного напряжения, первый вывод доступа отрицательного напряжения, второй вывод доступа отрицательного напряжения и третий вывод доступа отрицательного напряжения, причем как второй вывод доступа положительного напряжения, так и второй вывод доступа отрицательного напряжения доступа расположены между первым выводом доступа положительного напряжения и третьим выводом доступа положительного напряжения, каждый вывод доступа положительного напряжения может передавать сигнал положительного напряжения в светоизлучающий элемент ближайшего к нему субпикселя через шину положительного напряжения и линию положительного напряжения, и каждый вывод доступа отрицательного напряжения может передавать сигнал отрицательного напряжения в светоизлучающий элемент ближайшего к нему субпикселя через линию отрицательного напряжения, вспомогательную линию отрицательного напряжения и вспомогательный электрод; и, следовательно, как линия передачи сигнала для передачи сигнала положительного напряжения в светоизлучающий элемент, так и линия передачи сигнала для передачи сигнала отрицательного напряжения в светоизлучающий элемент являются короткими и имеют небольшое сопротивление, что выгодно для обеспечения однородности яркости изображений, отображаемых подложкой матрицы.

В частности, в варианте осуществления настоящего изобретения подложка матрицы дополнительно включает в себя:

четвертый вывод доступа положительного напряжения, расположенный на стороне шины положительного напряжения на удалении от области отображения, и расположенный между первым выводом доступа положительного напряжения и третьим выводом доступа положительного напряжения, причем четвертый вывод доступа положительного напряжения электрически соединен с шиной положительного напряжения; и

четвертый вывод доступа положительного напряжения используется для передачи сигнала положительного напряжения в светоизлучающий элемент через шину положительного напряжения, линию положительного напряжения и первый электрод.

Например, как показано на фиг. 2, на основании фиг. 1, подложка матрицы дополнительно включает в себя:

четвертый вывод 23 доступа положительного напряжения, расположенный на стороне шины 13 положительного напряжения на удалении от области B1 отображения и расположенный между первым выводом 14 доступа положительного напряжения и третьим выводом 16 доступа положительного напряжения; четвертый вывод 23 доступа положительного напряжения электрически соединен с шиной 13 положительного напряжения; и четвертый вывод 23 доступа положительного напряжения используется для передачи сигнала положительного напряжения в светоизлучающий элемент через шину 13 положительного напряжения, линию 12 положительного напряжения и первый электрод.

Например, как показано на фиг. 2, четвертый вывод 23 доступа положительного напряжения расположен между вторым выводом 20 доступа отрицательного напряжения и третьим выводом 16 доступа положительного напряжения, и четвертый вывод 23 доступа положительного напряжения может быть симметричным второму выводу 15 доступа положительного напряжения. Сигналы положительного напряжения на четвертом выводе 23 доступа положительного напряжения и втором выводе 15 доступа положительного напряжения могут быть переданы через шину 13 положительного напряжения в светоизлучающий элемент, электрически подключенный к линии 12 положительного напряжения в центральной области (центральный область положения размещения, показанная на фиг. 2). Следовательно, путь, по которому проходит сигнал положительного напряжения, передаваемый из вывода доступа положительного напряжения в светоизлучающий элемент, является коротким, и линия для передачи сигнала для передачи сигнала положительного напряжения в светоизлучающий элемент является короткой и имеет небольшое сопротивление, что выгодно для обеспечения однородности яркости изображений, отображаемых подложкой матрицы.

Специалистам в данной области техники понятно, что первый вывод 14 доступа положительного напряжения, второй вывод 15 доступа положительного напряжения, третий вывод 16 доступа положительного напряжения и четвертый вывод 23 доступа положительного напряжения одновременно передают сигнал положительного напряжения в светоизлучающие элементы всех субпикселей в подложке матрицы, и только второй вывод 15 доступа положительного напряжения и четвертый вывод 23 доступа положительного напряжения являются ближайшими к светоизлучающему элементу в центральной области, так что путь, по которому проходит сигнал положительного напряжения, передаваемый из второго вывода 15 доступа положительного напряжения и четвертого вывода 23 доступа положительного напряжения в светоизлучающий элемент в центральной области, является коротким и сопротивление невелико.

В частности, в варианте осуществления настоящего изобретения подложка матрицы дополнительно включает в себя:

четвертый вывод доступа отрицательного напряжения, расположенный на стороне шины положительного напряжения на удалении от области отображения и расположенный между первым выводом доступа положительного напряжения и третьим выводом доступа положительного напряжения, причем четвертый вывод доступа отрицательного напряжения электрически соединен со вспомогательной линией отрицательного напряжения; и

четвертый вывод доступа отрицательного напряжения используется для передачи сигнала отрицательного напряжения в светоизлучающий элемент через вспомогательную линию отрицательного напряжения, вспомогательный электрод и второй электрод.

Например, как показано на фиг. 3, на основании фиг. 1, подложка матрицы дополнительно включает в себя:

четвертый вывод 24 доступа отрицательного напряжения, расположенный на стороне шины 13 положительного напряжения области B1 отображения и расположенный между первым выводом 14 доступа положительного напряжения и третьим выводом 16 доступа положительного напряжения; четвертый вывод 24 доступа отрицательного напряжения электрически соединен со вспомогательной линией 22 отрицательного напряжения; и четвертый вывод 24 доступа отрицательного напряжения используется для передачи сигнала отрицательного напряжения в светоизлучающий элемент через вспомогательную линию 22 отрицательного напряжения, вспомогательный электрод 18 и второй электрод.

Например, как показано на фиг. 3, четвертый вывод 24 доступа отрицательного напряжения расположен между вторым выводом 20 доступа отрицательного напряжения и третьим выводом 16 доступа положительного напряжения, и четвертый вывод 24 доступа отрицательного напряжения может быть симметричным второму выводу 20 доступа отрицательного напряжения. Сигналы отрицательного напряжения на четвертом выводе 24 доступа отрицательного напряжения и втором выводе 20 доступа отрицательного напряжения могут быть переданы через вспомогательную линию 22 отрицательного напряжения и вспомогательный электрод 18 в светочувствительный элемент в центральной области (центральная область положение размещения, как показано на фиг. 3). Следовательно, путь, по которому проходит сигнал отрицательного напряжения, передаваемый из вывода доступа отрицательного напряжения в светоизлучающий элемент, является коротким, и линия для передачи сигнала для передачи сигнала отрицательного напряжения в светоизлучающий элемент является короткой и имеет небольшое сопротивление, что выгодно для обеспечения однородности яркости изображений, отображаемых подложкой матрицы.

Специалистам в данной области техники очевидно, что первый вывод 19 доступа отрицательного напряжения, второй вывод 20 доступа отрицательного напряжения, третий вывод 21 доступа отрицательного напряжения и четвертый вывод 24 доступа отрицательного напряжения одновременно передают сигнал отрицательного напряжения в светоизлучающие элементы всех субпикселей в подложке матрицы и только второй вывод 20 доступа отрицательного напряжения и четвертый вывод 24 доступа отрицательного напряжения являются ближайшими к излучающему элементу в центральной области, так что путь, по которому проходит сигнал отрицательного напряжения, передаваемый из второго вывода 20 доступа отрицательного напряжения и четвертого вывода 24 доступа отрицательного напряжения в светоизлучающий элемент в центральной области, является коротким и сопротивление невелико.

В частности, в варианте осуществления настоящего изобретения, второй вывод доступа отрицательного напряжения расположен между вторым выводом доступа положительного напряжения и третьим выводом доступа положительного напряжения, и подложка матрицы дополнительно включает в себя:

четвертый вывод доступа положительного напряжения и четвертый вывод доступа отрицательного напряжения, расположенные на стороне шины положительного напряжения на удалении от области отображения, четвертый вывод доступа положительного напряжения расположен между вторым выводом доступа отрицательного напряжения и третьим выводом доступа положительного напряжения и электрически подключен к шине положительного напряжения, и четвертый вывод доступа отрицательного напряжения, расположенный между второй выводом доступа отрицательного напряжения и четвертым выводом доступа положительного напряжения, электрически подключен к вспомогательной линии отрицательного напряжения; и

четвертый вывод доступа положительного напряжения используется для передачи сигнала положительного напряжения в светоизлучающий элемент через шину положительного напряжения, линию положительного напряжения и первый электрод, и четвертый вывод доступа отрицательного напряжения используется для передачи сигнала отрицательного напряжения в светоизлучающий элемент через вспомогательную линию отрицательного напряжения, вспомогательный электрод и второй электрод.

Например, как показано на фиг. 4, на основании фиг. 1, подложка матрицы дополнительно включает в себя:

четвертый вывод 23 доступа положительного напряжения и четвертый вывод 24 доступа отрицательного напряжения, расположенные на стороне шины 13 положительного напряжения на удалении от области B1 отображения, причем четвертый вывод 23 доступа положительного напряжения расположен между вторым выводом 20 доступа отрицательного напряжения и третьим выводом 16 доступа положительного напряжения и электрически подключен к шине 13 положительного напряжения, а четвертый вывод 24 доступа отрицательного напряжения расположен между вторым выводом 20 доступа отрицательного напряжения и четвертым выводом 23 доступа положительного напряжения и электрически соединен со вспомогательной линией 22 отрицательного напряжения; причем четвертый вывод 23 доступа положительного напряжения используется для передачи сигнала положительного напряжения в светоизлучающий элемент через шину 13 положительного напряжения, линию 12 положительного напряжения и первый электрод, а четвертый вывод 24 доступа отрицательного напряжения используется для передачи сигнала отрицательного напряжения в светоизлучающий элемент через вспомогательную линию 22 отрицательного напряжения, вспомогательный электрод 18 и второй электрод.

Например, как показано на фиг. 4, четвертый вывод 23 доступа положительного напряжения может быть симметричен второму выводу 15 доступа положительного напряжения, и четвертый вывод 24 доступа отрицательного напряжения может быть симметричен второму выводу 20 доступа отрицательного напряжения. Сигналы положительного напряжения на четвертом выводе 23 доступа положительного напряжения и втором выводе 15 доступа положительного напряжения могут быть переданы через шину 13 положительного напряжения и линию 12 положительного напряжения в светоизлучающие элементы в центральной области (центральная область положения расположенной на фиг. 4), и сигналы отрицательного напряжения на четвертом выводе 24 доступа отрицательного напряжения и втором выводе 20 доступа отрицательного напряжения могут быть переданы через вспомогательную линию 22 отрицательного напряжения и вспомогательный электрод 18 в светочувствительный элемент в центральной области. (центральная область положения размещения показана на фиг. 4). Таким образом, путь, по которому проходит сигнал положительного напряжения, передаваемый из вывода доступа положительного напряжения в светоизлучающий элемент, является коротким, и путь, через который проходит сигнал отрицательного напряжения, передаваемый из вывода доступа отрицательного напряжения в светоизлучающий элемент, является коротким. Следовательно, как линия для передачи сигнала для передачи сигнала положительного напряжения в светоизлучающий элемент, так и линия для передачи сигнала для передачи сигнала отрицательного напряжения в светоизлучающий элемент являются короткими и имеют небольшое сопротивление, что выгодно для обеспечения однородности яркости изображений, отображаемых подложкой матрицы.

Специалисту в данной области техники очевидно, что первый вывод 14 доступа положительного напряжения, второй вывод 15 доступа положительного напряжения, третий вывод 16 доступа положительного напряжения и четвертый вывод 23 доступа положительного напряжения одновременно передают сигнал положительного напряжения в светоизлучающие элементы всех субпикселей в подложке матрицы, первый вывод 19 доступа отрицательного напряжения, второй вывод 20 доступа отрицательного напряжения, третий вывод 21 доступа отрицательного напряжения и четвертый вывод 24 доступа отрицательного напряжения передают сигнал отрицательного напряжения в светоизлучающие элементы всех субпикселей в подложке матрицы, и только второй вывод 15 доступа положительного напряжения и четвертый вывод 23 доступа положительного напряжения является ближайшими к светоизлучающему элементу в центральной области, таким образом, путь, через который проходит сигнал положительного напряжения, переданный из второго вывода 15 доступа положительного напряжения и четвертого вывода 23 доступа положительного напряжения в светочувствительный элемент в центральной области, является коротким и сопротивление невелико, и второй вывод 20 доступа отрицательного напряжения и четвертый вывод 24 доступа отрицательного напряжения являются ближайшими к светоизлучающему элементу в центральной области, таким образом, путь, через который проходит сигнал отрицательного напряжения, переданный из второго вывода 20 доступа отрицательного напряжения и четвертого вывода 24 доступа отрицательного напряжения в светоизлучающий элемент в центральной области является коротким, и сопротивление невелико.

В частности, в варианте осуществления настоящего изобретения, светоизлучающий элемент представляет собой OLED, первый электрод служит анодом и второй электрод является катодом.

В частности, в варианте осуществления настоящего изобретения, по меньшей мере, один из субпикселей включает в себя тонкопленочный транзистор и соединительный электрод; и тонкопленочный транзистор включает в себя активный слой, расположенный на базовой подложке, затвор, расположенный на стороне активного слоя на удалении от базовой подложки, и исток и сток, которые расположены на стороне затвора на удалении от базовой подложки.

В частности, шина положительного напряжения включает в себя первый подслой шины положительного напряжения и второй подслой шины положительного напряжения, и первый подслой шины положительного напряжения электрически соединен со вторым подслоем шины положительного напряжения; и

первый подслой шины положительного напряжения и исток или сток находятся в одном и том же слое, и второй подслой шины положительного напряжения и соединительный электрод расположены в одном и том же слое.

В частности, первый подслой шины положительного напряжения электрически соединен со вторым подслоем шины положительного напряжения через сквозное отверстие шины положительного напряжения.

В частности, линия отрицательного напряжения включает в себя первый подслой линии отрицательного напряжения и второй подслой линии отрицательного напряжения, и первый подслой линии отрицательного напряжения электрически соединен со вторым подслоем линии отрицательного напряжения;

вспомогательная линия отрицательного напряжения включает в себя первый подслой вспомогательной линии отрицательного напряжения и второй подслой вспомогательной линии отрицательного напряжения, и первый подслой вспомогательной линии отрицательного напряжения электрически соединен со вторым подслоем вспомогательной линии отрицательного напряжения; и

первый подслой линии отрицательного напряжения и первый подслой вспомогательной линии отрицательного напряжения оба расположены в одном и том же слое с истоком или стоком, и второй подслой линии отрицательного напряжения и второй подслой вспомогательной линии отрицательного напряжения расположены в том же слое с соединительным электродом.

В частности, первый подслой линии отрицательного напряжения электрически соединен со вторым подслоем линии отрицательного напряжения через сквозное отверстие линии отрицательного напряжения, и первый подслой вспомогательной линии отрицательного напряжения электрически соединен со вторым подслоем вспомогательной линии отрицательного напряжения через сквозное отверстие вспомогательной линии отрицательного напряжения.

Например, на фиг. 5 проиллюстрированы виды в разрезе участка а-а, участка b-b, участка с-с и участка е-е подложки матрицы, представленной на любому из фиг. 1 – фиг. 4. Как показано на фиг. 5, по меньшей мере один из субпикселей 11 включает в себя тонкопленочный транзистор 110 и соединительный электрод 111; и тонкопленочный транзистор 110 включает в себя активный слой 1101, расположенный на базовой подложке 10, затвор 1102, расположенный на стороне активного слоя 1101 на удалении от базовой подложки 10, и исток 1103 и сток 1104, которые расположены на стороне затвора 1102 на удалении от базовой подложки 10. Исток 1103 и сток 1104 могут быть расположены в одном слое.

Шина 13 положительного напряжения включает в себя первый подслой шины 131 положительного напряжения и второй подслой шины 132 положительного напряжения; первый подслой шины 131 положительного напряжения электрически подключен ко второму подслою шины 132 положительного напряжения через сквозное отверстие шины положительного напряжения (на фиг. 5 не обозначено); первый подслой шины 131 положительного напряжения и сток 1103 или исток 1104 находятся в одном слое; и второй подслой шины 132 положительного напряжения и соединительный электрод 111 расположены в том же слое. Предоставлено множество сквозных отверстий шин положительного напряжения; и для обеспечения надежности соединения первый подслой шины 131 положительного напряжения электрически соединен со вторым подслоем шины 132 положительного напряжения через множество сквозных отверстий шин положительного напряжения.

Линия 17 отрицательного напряжения включает в себя первый подслой линии 171 отрицательного напряжения и второй подслой линии 172 отрицательного напряжения, и первый подслой линии 171 отрицательного напряжения электрически соединен со вторым подслоем линии 172 отрицательного напряжения через сквозное отверстие линии отрицательного напряжения (на фиг. 5 не обозначено); вспомогательная линия 22 отрицательного напряжения включает в себя первый подслой вспомогательной линии 221 отрицательного напряжения и второй подслой вспомогательной линии 222 отрицательного напряжения, и первый подслой вспомогательной линии 221 отрицательного напряжения электрически соединен со вторым подслоем вспомогательной линии 222 отрицательного напряжения через сквозное отверстие вспомогательной линии отрицательного напряжения; первый подслой линии 171 отрицательного напряжения и первый подслой вспомогательной линии 221 отрицательного напряжения находятся в одном слое с истоком 1103 или стоком 1104, и второй подслой линии 172 отрицательного напряжения и второй подслой вспомогательной линии 222 отрицательного напряжения расположены в одном и том же слое с соединительным электродом 111. Предоставлено множество сквозных отверстий линии отрицательного напряжения и множество сквозных отверстий вспомогательной линии отрицательного напряжения; первый подслой линии 171 отрицательного напряжения электрически соединен со вторым подслоем линии 172 отрицательного напряжения посредством множества сквозных отверстий линии отрицательного напряжения для обеспечения надежности соединения; и первый подслой вспомогательной линии 221 отрицательного напряжения электрически подключен к второму подслою вспомогательной линии 222 отрицательного напряжения с помощью множества сквозных отверстий вспомогательной линии отрицательного напряжения для обеспечения надежности соединения.

В частности, в варианте осуществления настоящего изобретения вспомогательный электрод расположен на стороне линии отрицательного напряжения на удалении от базовой подложки, и вспомогательный электрод электрически соединен со вспомогательной линией отрицательного напряжения через вспомогательного сквозное отверстие для отрицательного напряжения.

Например, как показано на фиг. 5, вспомогательный электрод 18 расположен на стороне линии 17 отрицательного напряжения на удалении от базовой подложки 10, и вспомогательный электрод 18 электрически подключен к вспомогательной линии 22 отрицательного напряжения через вспомогательное сквозное отверстие для отрицательного напряжения. Например, вспомогательный электрод 18 электрически подключен ко второму подслою вспомогательной линии 222 отрицательного напряжения через вспомогательное сквозное отверстие для отрицательного напряжения. Может быть предусмотрено множество вспомогательных сквозных отверстий для отрицательного напряжения. Вспомогательный электрод 18 электрически соединен со вторым подслоем вспомогательной линии 222 отрицательного напряжения через множество вспомогательный сквозных отверстий для отрицательного напряжения.

В частности, в варианте осуществления настоящего изобретения вспомогательный электрод находится на стороне линии отрицательного напряжения на удалении от базовой подложки, и вспомогательный электрод электрически соединен с линией отрицательного напряжения через вспомогательное сквозное отверстие для отрицательного напряжения.

Например, как показано на фиг. 5, вспомогательный электрод 18 расположен на стороне линии 17 отрицательного напряжения на удалении от базовой подложки 10, и вспомогательный электрод 18 электрически соединен с линией 17 отрицательного напряжения через вспомогательное сквозное отверстие для отрицательного напряжения. Например, вспомогательный электрод 18 электрически соединен со вторым подслоем линии 172 отрицательного напряжения через вспомогательное сквозное отверстие для отрицательного напряжения. Может быть предусмотрено множество вспомогательных сквозных отверстий для отрицательного напряжения. Вспомогательный электрод 18 электрически соединен со вторым подслоем линии 172 отрицательного напряжения посредством множества вспомогательных сквозных отверстий для отрицательного напряжения для обеспечения надежности соединения.

Специалистам в данной области техники очевидно, что вспомогательное сквозное отверстие для отрицательного напряжения для соединения вспомогательного электрода 18 со вторым подслоем вспомогательной линии 222 отрицательного напряжения предоставляет собой сквозное отверстие, расположенное на изолирующем слое между вспомогательным электродом 18 и вторым подслоем вспомогательной линии 222 отрицательного напряжения, а вспомогательное сквозное отверстие для отрицательного напряжения для соединения вспомогательного электрода 18 со вторым подслоем линии 172 отрицательного напряжения предоставляет собой сквозное отверстие, расположенное на изолирующем слое между вспомогательным электродом 18 и вторым подслоем линии 172 отрицательного напряжения, причем вспомогательное сквозное отверстие для отрицательного напряжения для соединения вспомогательного электрода 18 со вторым подслоем вспомогательной линии 222 отрицательного напряжения и вспомогательное сквозное отверстие для отрицательного напряжения для подключения вспомогательного электрода 18 ко второму подслою линии 172 отрицательного напряжения являются различными сквозными отверстиями.

В частности, в варианте осуществления настоящего изобретения, по меньшей мере, один из субпикселей включает в себя тонкопленочный транзистор; тонкопленочный транзистор включает в себя активный слой, расположенный на базовой подложке, затвор, расположенный на стороне активного слоя на удалении от базовой подложки, и исток и сток, которые расположены на стороне затвора на удалении от базовой подложки; первый вывод доступа положительного напряжения, второй вывод доступа положительного напряжения и третий вывод доступа положительного напряжения расположен в одном и том же слое с истоком или стоком; и первый вывод доступа отрицательного напряжения, второй вывод доступа отрицательного напряжения и третий вывод доступа отрицательного напряжения расположен в одном и том же слое с истоком или стоком.

Например, на фиг. 6 проиллюстрированы виды в разрезе для участка а-а и участка f-f подложки матрицы, показанной на фиг. 1. Ссылаясь на фиг. 6, по меньшей мере, один из субпикселей 11 включает в себя тонкопленочный транзистор 110; тонкопленочный транзистор 110 включает в себя активный слой 1101, расположенный на базовой подложке 10, затвор 1102, расположенный на стороне активного слоя 1101 на удалении от базовой подложки 10, и исток 1103 и сток 1104, которые расположены на стороне затвора 1102 на удалении от базовой подложки 10; первый вывод 14 доступа положительного напряжения, второй вывод 15 доступа положительного напряжения и третий вывод 16 доступа положительного напряжения расположены в одном и том же слое с истоком 1103 или стоком 1104; и первый вывод 19 доступа отрицательного напряжения, второй вывод 20 доступа отрицательного напряжения и третий вывод 21 доступа отрицательного напряжения расположены в одном и том же слое с истоком 1103 или стоком 1104.

В частности, в варианте осуществления настоящего изобретения, когда подложка матрицы дополнительно включает в себя четвертый вывод доступа положительного напряжения и/или четвертый вывод доступа отрицательного напряжения, четвертый вывод доступа положительного напряжения и/или четвертый вывод доступа отрицательного напряжения расположены в одном и том же слое с истоком или стоком.

Например, на фиг. 7 проиллюстрированы виды в разрезе для участка а-а и участка f-f подложки матрицы, показанной на фиг. 2. Как показано на фиг. 7, первый вывод 14 доступа положительного напряжения, второй вывод 15 доступа положительного напряжения, третий вывод 16 доступа положительного напряжения и четвертый вывод 23 доступа положительного напряжения находятся в одном и том же слое с истоком 1103 или стоком 1104; и первый вывод 19 доступа отрицательного напряжения, второй вывод 20 доступа отрицательного напряжения, третий вывод 21 доступа отрицательного напряжения расположены в одном и том же слое с истоком 1103 или стоком 1104.

Например, на фиг. 8 проиллюстрированы виды в разрезе для участка а-а и участка f-f подложки матрицы, показанной на фиг. 3. Как показано на фиг. 8, первый вывод 14 доступа положительного напряжения, второй вывод 15 доступа положительного напряжения и третий вывод 16 доступа положительного напряжения расположены в одном и том же слое с истоком 1103 или стоком 1104; и первый вывод 19 доступа отрицательного напряжения, второй вывод 20 доступа отрицательного напряжения, третий вывод 21 доступа отрицательного напряжения и четвертый вывод 24 доступа отрицательного напряжения расположены в одном и том же слое с истоком 1103 или стоком 1104.

Например, на фиг. 9 проиллюстрированы виды в разрезе для участка а-а и участка f-f подложки матрицы, показанной на фиг. 4. Как показано на фиг. 9 первый вывод 14 доступа положительного напряжения, второй вывод 15 доступа положительного напряжения, третий вывод 16 доступа положительного напряжения и четвертый вывод 23 доступа положительного напряжения находятся в одном и том же слое с истоком 1103 или стоком 1104; и первый вывод 19 доступа отрицательного напряжения, второй вывод 20 доступа отрицательного напряжения, третий вывод 21 доступа отрицательного напряжения и четвертый вывод 24 доступа отрицательного напряжения расположены в одном и том же слое с истоком 1103 или стоком 1104.

В частности, в варианте осуществления настоящего изобретения вспомогательная линия отрицательного напряжения включает в себя первый подслой вспомогательной линии отрицательного напряжения и второй подслой вспомогательной линии отрицательного напряжения, причем первый подслой вспомогательной линии отрицательного напряжения электрически соединен со вторым подслоем вспомогательной линии отрицательного напряжения; и второй вывод доступа отрицательного напряжения, четвертый вывод доступа отрицательного напряжения и первый подслой вспомогательной линии отрицательного напряжения имеет интегральную структуру.

Например, на фиг. 10 проиллюстрированы виды в разрезе для участка а-а и участка g-g подложки матрицы, показанной на фиг. 3 или фиг. 4. Как показано на фиг. 10, вспомогательная линия 22 отрицательного напряжения включает в себя первый подслой вспомогательной линии 221 отрицательного напряжения и второй подслой вспомогательной линии 222 отрицательного напряжения, причем первый подслой вспомогательной линии 221 отрицательного напряжения электрически соединен со вторым подслоем вспомогательной линии 222 отрицательного напряжения через сквозное отверстие вспомогательной линии отрицательного напряжения (на фиг. 10 не обозначено); и второй вывод 20 доступа отрицательного напряжения, четвертый вывод 24 доступа отрицательного напряжения и первый подслой вспомогательной линии 221 отрицательного напряжения имеет интегральную структуру.

Следует отметить, что на фиг. 10 проиллюстрирована подложка матрицы, которая одновременно включает в себя второй вывод 20 доступа отрицательного напряжения и четвертый вывод 24 доступа отрицательного напряжения в качестве примера для описания. Когда подложка матрицы включает в себя только второй вывод 20 доступа отрицательного напряжения или только четвертый вывод 24 доступа отрицательного напряжения, второй вывод 20 доступа отрицательного напряжения или четвертый вывод 24 доступа отрицательного напряжения и первый подслой вспомогательной линии 221 отрицательного напряжения являются интегральной структурой. Например, когда подложка матрицы включает в себя второй вывод 20 доступа отрицательного напряжения, но не четвертый вывод 24 доступа отрицательного напряжения, второй вывод 20 доступа отрицательного напряжения и первый подслой вспомогательной линии 221 отрицательного напряжения имеет интегральную структуру; а когда подложка матрицы включает в себя четвертый вывод 24 доступа отрицательного напряжения, но не второй вывод 20 доступа отрицательного напряжения, четвертый вывод 24 доступа отрицательного напряжения и первый подслой вспомогательной линии 221 отрицательного напряжения имеет интегральную структуру.

В частности, в варианте осуществления настоящего изобретения подложка матрицы дополнительно включает в себя: печатную плату, расположенную на сторонах, на удалении от области отображения, первого вывода доступа положительного напряжения, второго вывода доступа положительного напряжения, третьего вывода доступа положительного напряжения, четвертого вывода доступа положительного напряжения, первого вывода доступа отрицательного напряжения, второго вывода доступа отрицательного напряжения, третьего вывода доступа отрицательного напряжения и четвертого вывода доступа отрицательного напряжения, причем первый вывод доступа положительного напряжения, второй вывод доступа положительного напряжения, третий вывод доступа положительного напряжения, четвертый вывод доступа положительного напряжения, первый вывод доступа отрицательного напряжения, второй вывод доступа отрицательного напряжения, третий вывод доступа отрицательного напряжения и четвертый вывод доступа отрицательного напряжения соответственно электрически подключены к печатной плате.

Например, как показано на фиг. 1, подложка матрицы дополнительно включает в себя: печатную плату 25, расположенной на сторонах, на удалении от области В1 отображения, первого вывода 14 доступа положительного напряжения, второго вывода 15 доступа положительного напряжения, третьего вывода 16 доступа положительного напряжения, первого вывода 19 доступа отрицательного напряжения, второго вывода 20 доступа отрицательного напряжения и третьего вывода 21 доступа отрицательного напряжения; причем первый вывод 14 доступа положительного напряжения, второй вывод 15 доступа положительного напряжения, третий вывод 16 доступа положительного напряжения, первый вывод 19 доступа отрицательного напряжения, второй вывод 20 доступа отрицательного напряжения и третий вывод 21 доступа отрицательного напряжения соответственно электрически подключены к печатной плате 25.

Например, как показано на фиг. 2, подложка матрицы дополнительно включает в себя: печатную плату 25, расположенную на сторонах, на удалении от области B1 отображения, первого вывода 14 доступа положительного напряжения, второго вывода 15 доступа положительного напряжения, третьего вывода 16 доступа положительного напряжения, четвертого вывода 23 доступа положительного напряжения, первого вывода 19 доступа отрицательного напряжения, второго вывода 20 доступа отрицательного напряжения и третьего вывода 21 доступа отрицательного напряжения; причем первый вывод 14 доступа положительного напряжения, второй вывод 15 доступа положительного напряжения, третий вывод 16 доступа положительного напряжения, четвертый вывод 23 доступа положительного напряжения, первый вывод 19 доступа отрицательного напряжения, второй вывод 20 доступа отрицательного напряжения и третий вывод 21 доступа отрицательного напряжения соответственно электрически подключены к печатной плате 25.

Например, как показано на фиг. 3, подложка матрицы дополнительно включает в себя: печатную плату 25, расположенную на сторонах, на удалении от области B1 отображения, первого вывода 14 доступа положительного напряжения, второго вывода 15 доступа положительного напряжения, третьего вывода 16 доступа положительного напряжения, первого вывода 19 доступа отрицательного напряжения, второго вывода 20 доступа отрицательного напряжения, третьего вывода 21 доступа отрицательного напряжения и четвертого вывода 24 доступа отрицательного напряжения; причем первый вывод 14 доступа положительного напряжения, второй вывод 15 доступа положительного напряжения, третий вывод 16 доступа положительного напряжения, первый вывод 19 доступа отрицательного напряжения, второй вывод 20 доступа отрицательного напряжения, третий вывод 21 доступа отрицательного напряжения и четвертый вывод 24 доступа отрицательного напряжения соответственно электрически подключены к печатной плате 25.

Например, как показано на фиг. 4, подложка матрицы дополнительно включает в себя: печатную плату 25, расположенной на сторонах, на удалении от области B1 отображения, первого вывода 14 доступа положительного напряжения, второго вывода 15 доступа положительного напряжения, третьего вывода 16 доступа положительного напряжения, четвертого вывода 23 доступа положительного напряжения, первого вывода 19 доступа отрицательного напряжения, второго вывода 20 доступа отрицательного напряжения, третьего вывод 21 доступа отрицательного напряжения и четвертого вывода 24 отрицательного напряжения; причем первый вывод 14 доступа положительного напряжения, второй вывод 15 доступа положительного напряжения, третий вывод 16 доступа положительного напряжения, четвертый вывод 23 доступа положительного напряжения, первый вывод 19 доступа отрицательного напряжения, второй вывод 20 доступа отрицательного напряжения, третий вывод 21 доступа отрицательного напряжения и четвертый вывод 24 доступа отрицательного напряжения соответственно электрически подключены к печатной плате 25.

Следует отметить, что печатная плата 25 в варианте осуществления настоящего изобретения может представлять собой гибкую печатную плату (FPC).

Например, как показано на фиг. 5-фиг. 10, по меньшей мере один из субпикселей 11 включает в себя тонкопленочный транзистор 110, соединительный электрод 111, светоизлучающий элемент 112 и накопительный конденсатор 113. Тонкопленочный транзистор 110 включает в себя активный слой 1101, расположенный на базовой подложке 10, первый изолирующий слой 1105, расположенный на стороне активного слоя 1101 на удалении от базовой подложки 10, затвор 1102, расположенный на стороне первого изолирующего слоя 1105 на удалении от базовой подложки 10, второй изолирующий слой 1106, расположенный на стороне затвора 1102 на удалении от базовой подложки 10, третий изолирующий слой 1107, расположенный на стороне второго изолирующего слоя 1106 на удалении от базовой подложки 10, и исток 1103 и сток 1104, которые расположены на стороне третьего изолирующего слоя 1107 на удалении от базовой подложки 10. Соединительный электрод 111 расположен на стороне тонкопленочного транзистора 110 на удалении от базовой подложки 10. Соединительный электрод 111 электрически соединен со стоком 1104. Светоизлучающий элемент 112 расположен на стороне соединительного электрода 111 на удалении от базовой подложки. Светоизлучающий элемент 112 включает в себя первый электрод 1121, светоизлучающий слой 1122 и второй электрод 1123, которые последовательно укладывается по направлению на удалении от базовой подложки 10. Первый электрод 1121 электрически соединен с соединительным электродом 111. Накопительный конденсатор 113 включает в себя первую полярную пластину 1131 и вторую полярную пластину 1132. Первая полярная пластина 1131 и затвор 1101 расположены в одном слое. Вторая полярная пластина 1132 расположена между вторым изолирующим слоем 1106 и третьим изолирующим слоем 1107.

Например, как показано на фиг. 5-фиг. 10, по меньшей мере один из субпикселей 11 дополнительно включает в себя буферный слой 114, расположенный между активным слоем 1101 и базовой подложкой 10, пассивирующий слой 115 и первый сглаживающий слой 116, расположенный между истоком 1103 и соединительным электродом 111 вдоль направления от базовой подложки 10, и второй сглаживающий слой 117, расположенный между соединительным электродом 111 и первым электродом 1121. На пассивирующем слое 115 и первом сглаживающем слое 116 предусмотрено сквозное отверстие. Соединительный электрод 111 электрически соединен со стоком 1104 через сквозные отверстия на пассивирующем слое 115 и первом сглаживающем слое 116. На втором сглаживающем слое 117 предусмотрено отверстие. Первый электрод 1121 электрически соединен с соединительным электродом 111 через сквозное отверстие на втором сглаживающем слое 117.

В частности, как показано на фиг. 5-фиг. 10, подложка матрицы дополнительно включает в себя: слой 26 определения пикселя, расположенный на стороне второго сглаживающего слоя 117 на удалении от базовой подложки 10, причем слой 26 определения пикселя включает в себя область апертуры, определяемую структурой подпорной стенки, и светоизлучающий элемент 112, расположенный в области апертуры слоя 26 определения пикселя; и структуру 27 упаковки, расположенная на стороне светоизлучающего элемента 112 на удалении от базовой подложки, причем структура 27 упаковки используется для упаковки светоизлучающего элемента 112.

Следует отметить, что на участке b-b, участке с-с, участке е-е, участке f-f и участке g-g на фиг. 5-фиг. 10 первый изолирующий слой 1105, второй изолирующий слой 1106, третий изолирующий слой 1107, буферный слой 114, сглаживающий слой 115, пассивирующий слой 115, первый сглаживающий слой 116 и второй сглаживающий слой 117 могут представлять собой участки, где первый изолирующий слой 1105, второй изолирующий слой 1106, третий изолирующий слой 1107, буферный слой 114, сглаживающий слой 115, пассивирующий слой 115, первый сглаживающий слой 116 и второй сглаживающий слой 117 на участке а-а соответственно расширяются до периферийной области B2. Специалисты в данной области техники понимают, что на участке b-b, участке с-с, участке е-е, участке f-f и участке g-g на фиг. 5-фиг. 10 проиллюстрированы только линия 13 положительного напряжения, первый вывод 14 доступа положительного напряжения, второй вывод 15 доступа положительного напряжения и третий вывод 16 доступа положительного напряжения, линия 17 отрицательного напряжения, вспомогательный электрод 18, первый вывод 19 доступа отрицательного напряжения, второй вывод 20 доступа отрицательного напряжения, третий вывод 21 доступа отрицательного напряжения, вспомогательная линия 22 отрицательного напряжения, четвертый вывод 23 доступа положительного напряжения и четвертый вывод 24 доступа отрицательного напряжения. Периферийная область подложки матрицы может дополнительно включать в себя другие схемные структуры, которые не показаны на фиг. 5-фиг. 10.

Кроме того, следует отметить, что за исключением структуры, описанной в настоящем изобретении, подложка матрицы может дополнительно включать в себя другие структуры. Например, подложка матрицы дополнительно включает в себя множество линий затвора, имеющих одинаковое направление расширения, и множество линий данных, имеющих одинаковое направление расширения. Множество линий затвора и множество линий данных пересекаются для ограничения множества областей пикселей. Множество субпикселей расположено во множестве областей пикселей в однозначном соответствии. Также, например, подложка матрицы может дополнительно включать в себя кристалл на ленточном носителе (COF) и интегрированную схему (IC) и т.д., которые не представлены в варианте осуществления настоящего изобретения.

Таким образом, представленный вариант осуществления настоящего изобретения предлагает подложку матрицы, которая включает в себя первый вывод доступа положительного напряжения, второй вывод доступа положительного напряжения, третий вывод доступа положительного напряжения, первый вывод доступа отрицательного напряжения, второй вывод доступа отрицательного напряжения и третий вывод доступа отрицательного напряжения, причем как второй вывод доступа положительного напряжения, так и второй вывод доступа отрицательного напряжения расположены между первым выводом доступа положительного напряжения и третьим выводом доступа положительного напряжения, каждый вывод доступа положительного напряжения может передавать сигнал положительного напряжения в светоизлучающий элемент близлежащего субпикселя через шину положительного напряжения и линию положительного напряжения, и каждый вывод доступа отрицательного напряжения может передавать сигнал отрицательного напряжения в светоизлучающий элемент близлежащего субпикселя через линию отрицательного напряжения, вспомогательную линию отрицательного напряжения и вспомогательный электрод; и, следовательно, как линия для передачи сигнала для передачи сигнала положительного напряжения в светоизлучающий элемент, так и линия для передачи сигнала для передачи сигнала отрицательного напряжения в светоизлучающий элемент являются короткими и имеют небольшое сопротивление, что выгодно для обеспечения однородности яркости изображений, отображаемых подложкой матрицы.

На основании той же концепции изобретения вариант осуществления настоящего изобретения дополнительно обеспечивает устройство отображения, включающее в себя вышеупомянутую подложку матрицы. Устройство отображения, предусмотренное вариантом осуществления настоящего изобретения, может быть любым продуктом или частью с функцией отображения, такой как мобильный телефон, планшетный компьютер, телевизор, дисплей, ноутбук, цифровой фотоаппарат, навигатор и т.д.

В вариантах осуществления настоящего изобретения термин «один и тот же слой» относится к взаимосвязи, через которую одновременно образуются слои на одном этапе. Например, при формировании второго подслоя вспомогательной линии 222 отрицательного напряжения и соединительного электрода 111 в результате одного или нескольких этапов одинаковой обработки, выполняемой в одном и том же слое материала, оба расположены в одном и том же слое. В другом примере второй подслой вспомогательной линии 222 отрицательного напряжения и соединительный электрод 111 могут быть сформированы в одном и том же слое путем одновременного выполнения этапа формирования второго подслоя вспомогательной линии 222 отрицательного напряжения и этапа формирования соединительного электрода 111. «один и тот же слой» не всегда означает, что толщина слоя или высота слоя одинакова в разрезе.

Термины «первый», «второй», «третий», «четвертый» и подобные слова, используемые в вариантах осуществления настоящего изобретения, не указывают на какую-либо последовательность, количество или важность, но просто используются для отличия различных составных частей. Термин «электрическое соединение» между двумя проводниками относится к прямому или косвенному электрическому соединению между двумя проводниками, и два проводника могут передавать электрический сигнал. Термин «по меньшей мере один» относится к одному или более, и термин «множество» относится к двум или более.

В вариантах осуществления настоящего изобретения термин «и/или» просто описывает связь между ассоциированными объектами и указывает, что могут быть три отношения. Например, A и/или B может указывать на три случая, когда существует только A, A и B одновременно или только B. Кроме того, символ «/» в этом описании обычно указывает на то, что соединенные объекты находятся в отношениях «или».

Следует отметить, что в прилагаемых чертежах для ясности иллюстрации размеры части или всех слоев или части или всех областей могут быть масштабированы. Очевидно, что, когда элемент или слой упоминается как «на» другом элементе или слое, то может быть непосредственно на другом элементе или между ними может быть промежуточный слой. Кроме того, можно понять, что когда элемент или слой называют «под» другим элементом или слоем, то может быть непосредственно на другом элементе или между ними может быть более одного промежуточного слоя или элемента. Дополнительно, очевидно, что когда элемент или слой называют «между» двумя слоями или двумя элементами, то может быть уникальный слой между двумя слоями или двумя элементами или между ними может быть более чем один промежуточный слой или элемент. Аналогичная ссылочная позиция относится к аналогичному элементу по всему тексту спецификации.

Приведенное выше описание является просто примерными вариантами осуществления настоящего изобретения и не предназначено для ограничения настоящего применения. Любые модификации, эквивалентные замены, улучшения и тому подобное, выполненные в рамках сущности и принципов настоящего изобретения, должны находиться в объеме защиты настоящего изобретения.