ОБЛАСТЬ ТЕХНИКИ

Изобретение относится к области вычислительной техники, в частности к устройствам обработки данных, и может быть использовано для построения функциональных узлов для анализа свойств генераторов псевдослучайных последовательностей двоичных чисел, фильтрации событий, обработки сигналов, изображений и результатов физических экспериментов.

ПРЕДШЕСТВУЮЩИЙ УРОВЕНЬ ТЕХНИКИ

Известно устройство для детектирования групп бит (RU №2780985 С1, МПК G06F 7/74, G06F 7/02, заявлено 01.12.2021, опубликовано 04.10.2022, Бюл. №28), содержит внешний m разрядный вход данных ID, внешний m разрядный вход заданного шаблона IG, группу внешних выходов данных QB, первый RS-триггер пуска-останова TSS 1, второй D-триггер TR2 задержки 2, счетчик CTG групп 3, выходной буфер ОВ 4, первый R1 регистр данных 5, второй R2 регистр данных 6, группу из m компараторов

группу из (m-1) элементов И

группу из (m-1) элементов И  элемент ИЛИ 9 и элемент И 10, а также введены внешние входы асинхронной установки в нулевое состояние CLR, пуска устройства START, остановки устройства STOP и тактовый С, внутренняя 2m-разрядная шина данных BD, внутренняя m-разрядная шина данных буфера IOB, внутренний флаг совпадения FE, внешняя шина управления обменом ЕО, внешние флаг «Буфер заполнен» FF и флаг «Буфер пуст» FZ.

элемент ИЛИ 9 и элемент И 10, а также введены внешние входы асинхронной установки в нулевое состояние CLR, пуска устройства START, остановки устройства STOP и тактовый С, внутренняя 2m-разрядная шина данных BD, внутренняя m-разрядная шина данных буфера IOB, внутренний флаг совпадения FE, внешняя шина управления обменом ЕО, внешние флаг «Буфер заполнен» FF и флаг «Буфер пуст» FZ.

Недостатком данного устройства является выявление на каждом такте групп бит соответствующих только заданному шаблону.

Известно устройство для детектирования групп единичных бит и максимальной группы в блоках данных (RU №280039 С1, МПК G06F 7/74, заявлено 09.03.2023, опубликовано 17.07.2023, Бюл. №20), содержит внешнюю входную шину данных IBD, группу внешних выходов количества групп в блоке QB, группу внешних выходов максимальной группы QM и группу Q1, Q2, Q3, Q4 внешних выходов количества единичных групп во входной последовательности, первую

группы из элементов И с инверсными входами, группу элементов И

группы из элементов И с инверсными входами, группу элементов И  элемент ИЛИ 5, группу сумматоров

элемент ИЛИ 5, группу сумматоров  группу регистров

группу регистров

группу блоков счета единиц

группу блоков счета единиц  группу элементов ИЛИ

группу элементов ИЛИ  приоритетный шифратор 10, первый ОВ и второй ОМ выходные буферы, а также введены внешние входы синхронной установки в нулевое состояние IR и тактовый IC, группа внутренних шин B1, В2, В3 и В4, внутренний флаг FB4, внешние шины управления обменом ЕО, внешние флаги «Буфер заполнен» FF и «Буфер пуст» FZ.

приоритетный шифратор 10, первый ОВ и второй ОМ выходные буферы, а также введены внешние входы синхронной установки в нулевое состояние IR и тактовый IC, группа внутренних шин B1, В2, В3 и В4, внутренний флаг FB4, внешние шины управления обменом ЕО, внешние флаги «Буфер заполнен» FF и «Буфер пуст» FZ.

Недостатком данного устройства является выявление только 1, 2, 3, ≥4 разрядных групп в 8-ми разрядных блоках данных.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является, принятое за прототип, устройство для детектирования единичных групп бит в бинарной последовательности (RU №2763859 С1, МПК G06F7/74, Н03К 21/00, заявлено 29.04.2021, опубликовано 11.01.2022, Бюл. №2), содержит внешний вход данных DI, группу внешних выходов данных QB, группу внешних выходов количества групп QG, первый RS-триггер пуска-останова TSS 1, первый счетчик бит СТВ 2, регистр номера первого бита группы RGB 3, первый элемент И 4, первый элемент ИЛИ 5 с одним инверсным входом, второй триггер единичных бит TR1 6, второй элемент И 7 с одним инверсным входом, второй счетчик единиц CTU 8, блок равенства нижней границе 9, блок равенства верхней границе 10, третий триггер нижней границы TRL 11, четвертый триггер верхней границы TRM 12, третий 13 и четвертый 14 элементы И с двумя инверсными входами, второй элемент ИЛИ 15, выходной буфер ОВ 16 и третий счетчик количества групп CTG 17, а также введены внешние входы асинхронной установки в нулевое состояние CLR, пуска устройства START, остановки устройства STOP и тактовый С, внешние входные шины нижней границы GL и верхней границы GM диапазона единичных бит, внешняя шина управления обменом ЕО, внешние флаг «Буфер заполнен» FF и флаг «Буфер пуст» FZ. В данном устройстве осуществляется выявление групп единичных бит заданной размерности в пределах нижней GL и верхней GM границ диапазона.

Недостатком данного устройства является низкое быстродействие, так как входные данные поступают последовательно по одному разряду (биту) на каждом такте.

ЗАДАЧА ИЗОБРЕТЕНИЯ

Задачей изобретения является разработка аппаратных средств для исследования свойств генераторов псевдослучайных последовательностей двоичных чисел, а также для обработки результатов физических экспериментов.

При анализе генераторов псевдослучайных последовательностей двоичных чисел устройство предназначено для выявления групп (рядов) подряд идущих единичных бит разрядности в заданных границах диапазона и подсчет количества таких групп.

При обработке результатов физических экспериментов устройство предназначено для выявления событий заданной размерности, определение их количества и размещение в блоках данных.

Техническим результатом изобретения является расширение арсенала средств того же назначения, в части обеспечения возможности детектирования групп единичных бит в заданном диапазоне разрядности, определение количества выявленных групп и их размещение в блоках данных.

КРАТКОЕ ОПИСАНИЕ СУЩНОСТИ ИЗОБРЕТЕНИЯ

Указанный технический результат при осуществлении изобретения достигается тем, что устройство для детектирования в блоках данных групп единичных бит в заданных границах содержит внешнюю N разрядную входную шину данных ID блоков данных G, внешние М разрядные входные шины задания нижней IL и верхней IH границ, где M=]log2 N[ большее целое, группы внешних выходов количества групп заданного диапазона QLH и больше верхней границы QH, начальных разрядов групп заданного диапазона QULH и верхней границы QUH, первый 1 и второй 2 дешифраторы, первую

и вторую

и вторую  группы из (N-1)-го элементов ИЛИ, третью группу из N элементов И с инверсным входом

группы из (N-1)-го элементов ИЛИ, третью группу из N элементов И с инверсным входом  первый 11 и второй 12 блоки счета единиц, первый модуль детектирования нижней границы 5L и второй модуль детектирования верхней границы 5Н, каждый из которых содержит группу из N блоков детектирования

первый 11 и второй 12 блоки счета единиц, первый модуль детектирования нижней границы 5L и второй модуль детектирования верхней границы 5Н, каждый из которых содержит группу из N блоков детектирования  N групп

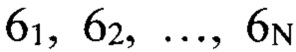

N групп  из (N+1-I) элементов ИЛИ с инверсным входом 1-ых блоков детектирования 6I, где

из (N+1-I) элементов ИЛИ с инверсным входом 1-ых блоков детектирования 6I, где  первую группу из (N-1)-го элементов И с инверсными входами

первую группу из (N-1)-го элементов И с инверсными входами  вторую группу из (N-1)-го элементов И с инверсным входом

вторую группу из (N-1)-го элементов И с инверсным входом  и элемент И 13,

и элемент И 13,

а также введены внутренние шины нижней BUL и верхней BUH границ, начальных разрядов групп заданного диапазона BLH, нижней BL и верхней ВН границ,

причем разряды внешних входных шин задания нижней IL и верхней IH границ соединены с адресными входами соответственно первого 1 и второго 2 дешифраторов, у которых выходы, с первого выхода до (N-1)-го выхода, соединены с первыми входами соответствующих одноименных (N-1)-го элементов ИЛИ соответственно первой

и второй

и второй  групп, выходы которых являются соответствующими одноименными разрядами, с первого разряда до (N-1)-го разряда, внутренних шин соответственно нижней BUL и верхней BUH границ, у которых N-ые разряды соединены с N-ми выходами соответственно первого 1 и второго 2 дешифраторов, а также выходы элементов в первой

групп, выходы которых являются соответствующими одноименными разрядами, с первого разряда до (N-1)-го разряда, внутренних шин соответственно нижней BUL и верхней BUH границ, у которых N-ые разряды соединены с N-ми выходами соответственно первого 1 и второго 2 дешифраторов, а также выходы элементов в первой  группах, начиная с выхода (N-1)-го элемента до второго элемента, соединены со вторыми входами соответствующих предыдущих элементов ИЛИ в первой

группах, начиная с выхода (N-1)-го элемента до второго элемента, соединены со вторыми входами соответствующих предыдущих элементов ИЛИ в первой  и второй

и второй  группах, начиная с (N-2)-го элемента до первого элемента, а вторые входы (N-1)-ых элементов групп соединены с N-ми выходами соответственно первого 1 и второго 2 дешифраторов,

группах, начиная с (N-2)-го элемента до первого элемента, а вторые входы (N-1)-ых элементов групп соединены с N-ми выходами соответственно первого 1 и второго 2 дешифраторов,

причем разряды внешней входной шины данных ID соединены с первыми группами входов II первого модуля детектирования нижней границы 5L и второго модуля детектирования верхней границы 5Н, у которых вторые группы входов 12 соединены с разрядами внутренних шин соответственно нижней BUL и верхней BUH границ,

кроме того в первом модуле детектирования нижней границы 5L и втором модуле детектирования верхней границы 5Н разряды первых групп входов II группами по (N+1-I) разрядов, каждая из которых начинается с 1-го разряда до N-го разряда  соединены в соответствующих 1-ых блоках 6I детектирования группы

соединены в соответствующих 1-ых блоках 6I детектирования группы  со вторыми прямыми входами элементов ИЛИ с инверсным входом групп

со вторыми прямыми входами элементов ИЛИ с инверсным входом групп  , у которых первые инверсные входы соединены с разрядами вторых групп входов 12 группами по (N+1-I) разрядов, каждая из которых начинается с 1-го разряда до (N+l-I)-го разряда, при этом выходы элементов ИЛИ с инверсным входом групп

, у которых первые инверсные входы соединены с разрядами вторых групп входов 12 группами по (N+1-I) разрядов, каждая из которых начинается с 1-го разряда до (N+l-I)-го разряда, при этом выходы элементов ИЛИ с инверсным входом групп  блоков детектирования 6I, начиная со второго блока 62 до N-го блока 6N, соединены с прямыми входами одноименных элементов И с инверсными входами первой группы

блоков детектирования 6I, начиная со второго блока 62 до N-го блока 6N, соединены с прямыми входами одноименных элементов И с инверсными входами первой группы  инверсные входы которых соединены с разрядами вторых групп входов 12 группами по J разрядов, каждая из которых начинается с N-го разряда до второго разряда, где

инверсные входы которых соединены с разрядами вторых групп входов 12 группами по J разрядов, каждая из которых начинается с N-го разряда до второго разряда, где

а выходы элементов ИЛИ с инверсным входом группы

а выходы элементов ИЛИ с инверсным входом группы  первого блока детектирования 61 соединены с входами элемента И 13,

первого блока детектирования 61 соединены с входами элемента И 13,

причем выходы элементов И с инверсными входами первой группы  соединены с прямыми входами одноименных элементов И с инверсным входами второй группы

соединены с прямыми входами одноименных элементов И с инверсным входами второй группы  у которых первые инверсные входы (N-2) элементов И, начиная с третьего элемента

у которых первые инверсные входы (N-2) элементов И, начиная с третьего элемента  до N-го элемента

до N-го элемента  соединены с прямыми входами соответствующих предыдущих (N-2) элементов И из второй группы

соединены с прямыми входами соответствующих предыдущих (N-2) элементов И из второй группы  начиная со второго элемента

начиная со второго элемента  до (N-1)-го элемента

до (N-1)-го элемента  а первый инверсный вход второго элемента

а первый инверсный вход второго элемента  соединен с выходом элемента И 13,

соединен с выходом элемента И 13,

кроме того, выходы всех (N-1) элементов И с инверсным входом из второй группы

являются соответствующими одноименными (N-1) разрядами, начиная со второго разряда до N-го разряда, групп выходов Q соответствующих модулей детектирования границ нижней 5L и верхней 5Н, а первый разряд выходов Q соединен с выходом соответствующего элемента И 13,

являются соответствующими одноименными (N-1) разрядами, начиная со второго разряда до N-го разряда, групп выходов Q соответствующих модулей детектирования границ нижней 5L и верхней 5Н, а первый разряд выходов Q соединен с выходом соответствующего элемента И 13,

причем разряды групп выходов Q модулей детектирования нижней 5L и верхней 5Н границ являются одноименными разрядами внутренних шин начальных разрядов групп соответственно нижней BL и верхней ВН границ, причем все N разрядов шины нижней границы BL соединены с прямыми входами одноименных элементов И с инверсным входом третьей группы  выходы которых являются разрядами внутренней шины начальных разрядов групп заданного диапазона BLH, которая соединена с одноименными разрядами внешних выходов начальных разрядов групп заданного диапазона QULH и подключена к входам первого блока счета единиц 11, выходы которого являются соответствующими разрядами группы внешних выходов количества групп заданного диапазона QLH,

выходы которых являются разрядами внутренней шины начальных разрядов групп заданного диапазона BLH, которая соединена с одноименными разрядами внешних выходов начальных разрядов групп заданного диапазона QULH и подключена к входам первого блока счета единиц 11, выходы которого являются соответствующими разрядами группы внешних выходов количества групп заданного диапазона QLH,

причем все N разрядов внутренней шины начальных разрядов групп верхней ВН границы соединены с инверсными входами одноименных элементов И с инверсным входом третьей группы  а также являются одноименными разрядами внешних выходов начальных разрядов групп верхней границы QUH и подключены к входам второго блока счета единиц 12, выходы которого являются соответствующими разрядами группы внешних выходов количества групп больше верхней границы QH.

а также являются одноименными разрядами внешних выходов начальных разрядов групп верхней границы QUH и подключены к входам второго блока счета единиц 12, выходы которого являются соответствующими разрядами группы внешних выходов количества групп больше верхней границы QH.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

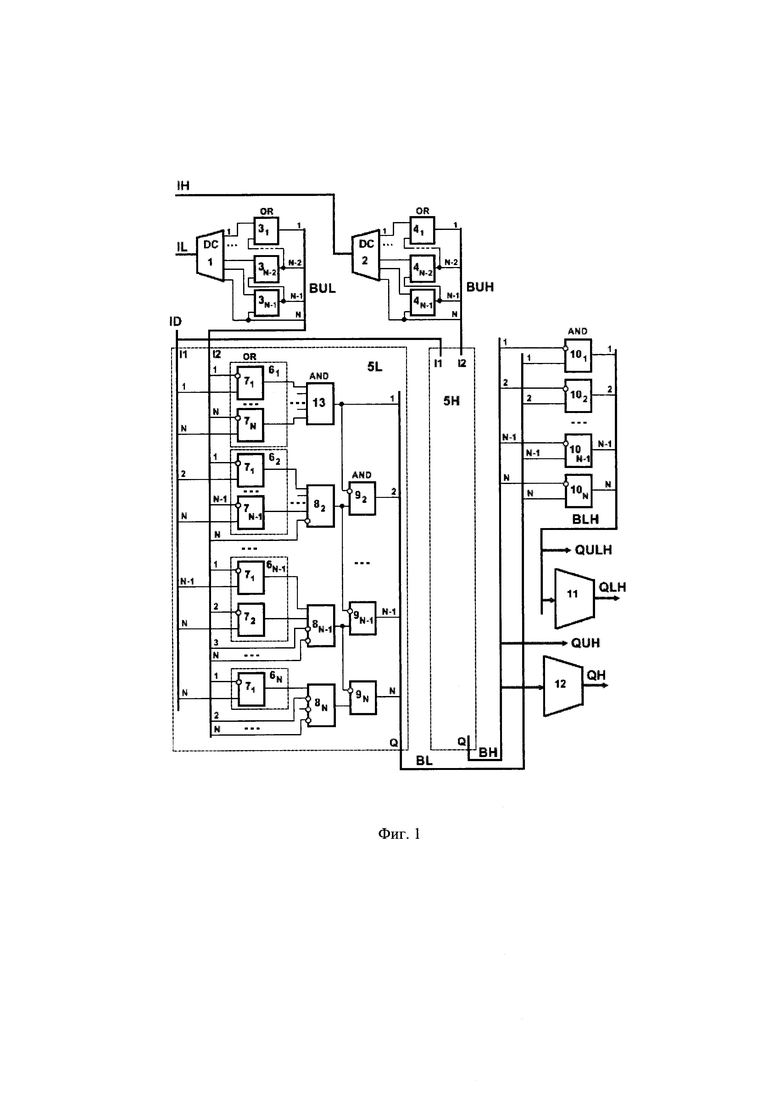

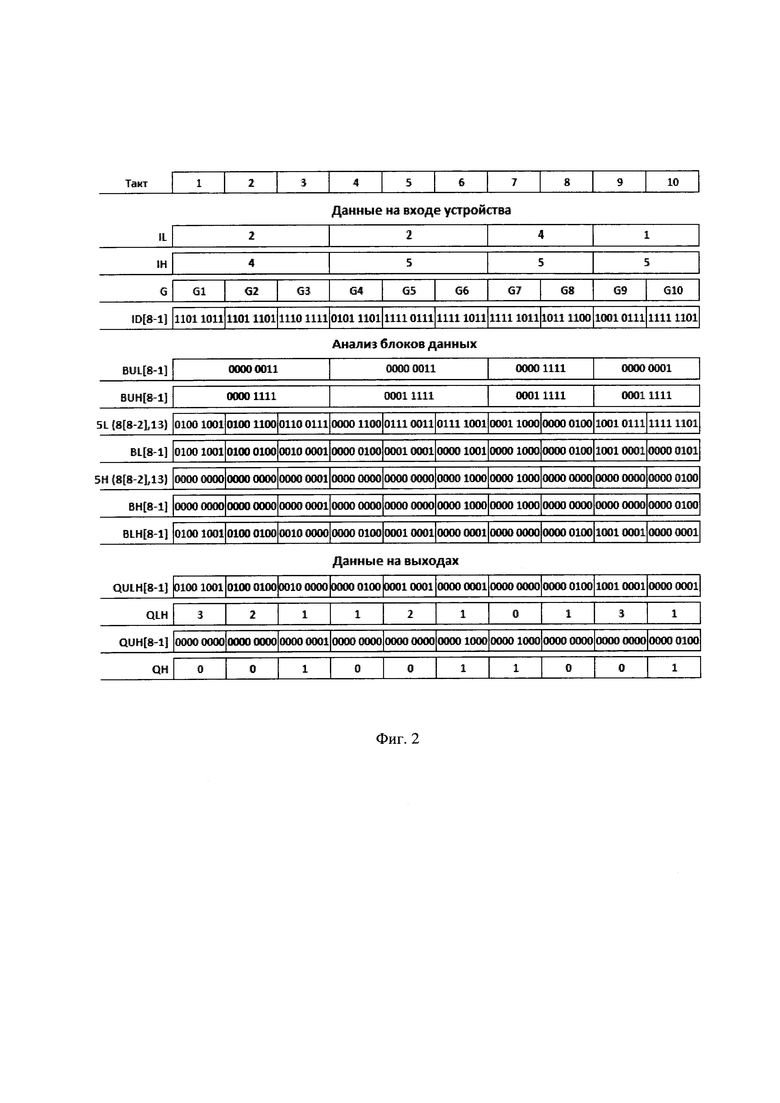

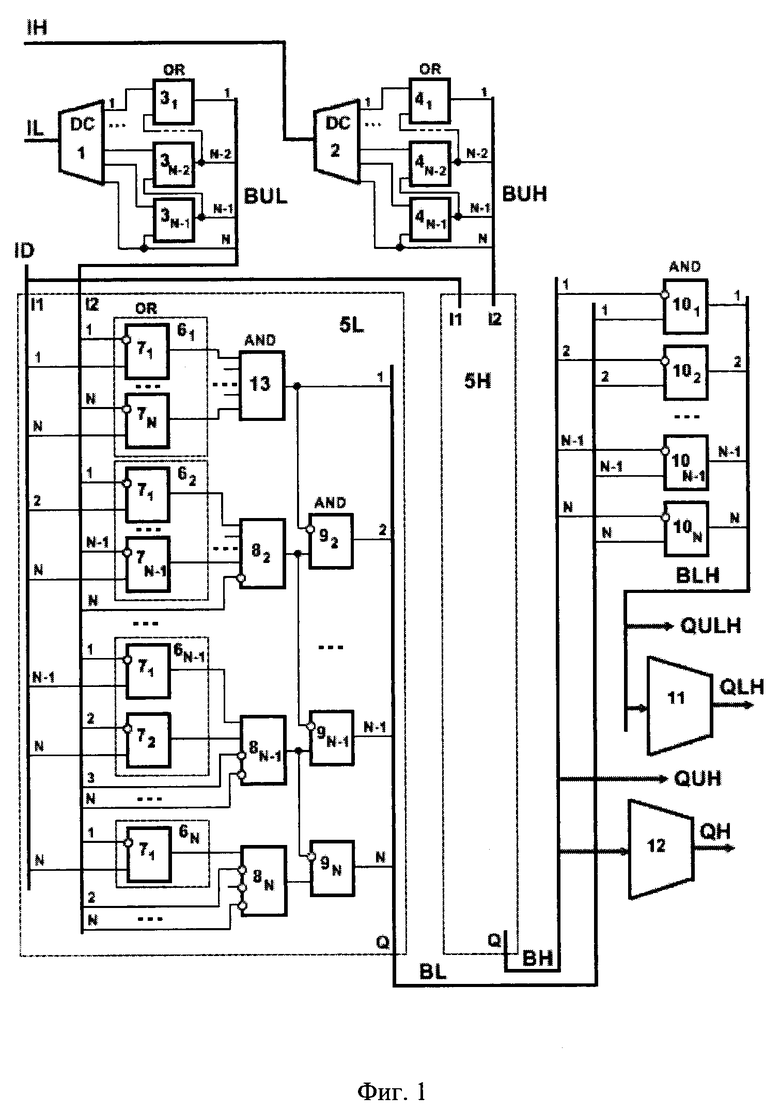

На фиг.1 представлена схема предлагаемого устройства. На фиг.2 приведена временная диаграмма работы устройства для N=8 разрядности входных блоков.

На фиг.1 - 2 и в тексте приняты следующие обозначения:

AND - элемент И,

ВН - внутренняя N разрядная шина начальных разрядов групп верхней границы,

BL - внутренняя N разрядная шина начальных разрядов групп нижней границы,

BLH - внутренняя N разрядная шина начальных разрядов групп заданного диапазона,

BUH - внутренняя N разрядная шина верхней границы,

BUL - внутренняя N разрядная шина нижней границы,

DC- дешифратор,

G (G1, G2, …, G10) - входные N разрядные блоки данных,

I1, I2 - первая и вторая группы входов модулей детектирования границ,

ID - внешняя N разрядная входная шина блоков данных G,

IH - внешняя М разрядная входная шина задания верхней границы,

где M=]log2 N[ большее целое,

IL - внешняя М разрядная входная шина задания нижней границы,

Н - верхняя граница диапазона,

L - нижняя граница диапазона,

N - разрядность входного блока данных,

OR - элемент ИЛИ,

Q - группа выходов модулей детектирования границ,

QH - группа внешних выходов количества групп больше верхней границы,

QLH - группа внешних выходов количества групп заданного диапазона,

QUH - группа внешних выходов начальных разрядов групп верхней границы,

QULH - группа внешних выходов начальных разрядов групп заданного диапазона,

1 - первый дешифратор нижней границы,

2 - второй дешифратор верхней границы,

- первая группа из (N-1)-го элементов ИЛИ,

- первая группа из (N-1)-го элементов ИЛИ,

- вторая группа из (N-1)-го элементов ИЛИ,

- вторая группа из (N-1)-го элементов ИЛИ,

5L - первый модуль детектирования нижней границы,

5Н - второй модуль детектирования верхней границы,

- группа из N блоков детектирования,

- группа из N блоков детектирования,

- N групп из (N+1-I) элементов ИЛИ с инверсным входом 1-ых блоков детектирования 6I, где 1 = 1, …, N,

- N групп из (N+1-I) элементов ИЛИ с инверсным входом 1-ых блоков детектирования 6I, где 1 = 1, …, N,

- первая группа из (N-1)-го элементов И с инверсными входами,

- первая группа из (N-1)-го элементов И с инверсными входами,

- вторая группа из (N-1)-го элементов И с инверсным входом,

- вторая группа из (N-1)-го элементов И с инверсным входом,

- третья группа из N элементов И с инверсным входом,

- третья группа из N элементов И с инверсным входом,

11 - первый блок счета единиц,

12 - второй блок счета единиц,

13 - элемент И.

Предлагаемое устройство содержит внешнюю N разрядную входную шину данных ID блоков данных G, внешние М разрядные входные шины задания нижней IL и верхней IH границ, где M=]log2 N[ большее целое, группы внешних выходов количества групп заданного диапазона QLH и больше верхней границы QH, начальных разрядов групп заданного диапазона QULH и верхней границы QUH, первый 1 и второй 2 дешифраторы, первую  и вторую

и вторую  группы из (N-1)-го элементов ИЛИ, третью группу из N элементов И с инверсным входом

группы из (N-1)-го элементов ИЛИ, третью группу из N элементов И с инверсным входом  первый 11 и второй 12 блоки счета единиц, первый модуль детектирования нижней границы 5L и второй модуль детектирования верхней границы 5Н, каждый из которых содержит группу из N блоков детектирования

первый 11 и второй 12 блоки счета единиц, первый модуль детектирования нижней границы 5L и второй модуль детектирования верхней границы 5Н, каждый из которых содержит группу из N блоков детектирования N групп

N групп  из (N+1-I) элементов ИЛИ с инверсным входом 1-ых блоков детектирования 6I, где I = 1, …, N, первую группу из (N-1)-го элементов И с инверсными входами

из (N+1-I) элементов ИЛИ с инверсным входом 1-ых блоков детектирования 6I, где I = 1, …, N, первую группу из (N-1)-го элементов И с инверсными входами  вторую группу из (N-1)-го элементов И с инверсным входом

вторую группу из (N-1)-го элементов И с инверсным входом  и элемент И 13.

и элемент И 13.

Также введены внутренние шины нижней BUL и верхней BUH границ, начальных разрядов групп заданного диапазона BLH, нижней BL и верхней ВН границ.

Разряды внешних входных шин задания нижней IL и верхней Ш границ соединены с адресными входами соответственно первого 1 и второго 2 дешифраторов, у которых выходы, с первого выхода до (N-1)-го выхода, соединены с первыми входами соответствующих одноименных (N-1)-го элементов ИЛИ соответственно первой

и второй

и второй  групп, выходы которых являются соответствующими одноименными разрядами, с первого разряда до (N-1)-го разряда, внутренних шин соответственно нижней BUL и верхней BUH границ, у которых N-ые разряды соединены с N-ми выходами соответственно первого 1 и второго 2 дешифраторов.

групп, выходы которых являются соответствующими одноименными разрядами, с первого разряда до (N-1)-го разряда, внутренних шин соответственно нижней BUL и верхней BUH границ, у которых N-ые разряды соединены с N-ми выходами соответственно первого 1 и второго 2 дешифраторов.

Выходы элементов в первой  и второй

и второй  группах, начиная с выхода (N-1)-го элемента до второго элемента, также соединены со вторыми входами соответствующих предыдущих элементов ИЛИ в первой

группах, начиная с выхода (N-1)-го элемента до второго элемента, также соединены со вторыми входами соответствующих предыдущих элементов ИЛИ в первой

группах, начиная с (N-2)-го элемента до первого элемента. Вторые входы (N-1)-ых элементов групп соединены с N-ми выходами соответственно первого 1 и второго 2 дешифраторов.

группах, начиная с (N-2)-го элемента до первого элемента. Вторые входы (N-1)-ых элементов групп соединены с N-ми выходами соответственно первого 1 и второго 2 дешифраторов.

Разряды внешней входной шины данных ID соединены с первыми группами входов II первого модуля детектирования нижней границы 5L и второго модуля детектирования верхней границы 5Н, у которых вторые группы входов 12 соединены с разрядами внутренних шин соответственно нижней BUL и верхней BUH границ.

В первом модуле детектирования нижней границы 5L и втором модуле детектирования верхней границы 5Н разряды первых групп входов И группами по (N+1-I) разрядов, каждая из которых начинается с 1-го разряда до N-го разряда  соединены в соответствующих 1-ых блоках 6i детектирования группы

соединены в соответствующих 1-ых блоках 6i детектирования группы  со вторыми прямыми входами элементов ИЛИ с инверсным входом групп

со вторыми прямыми входами элементов ИЛИ с инверсным входом групп  у которых первые инверсные входы соединены с разрядами вторых групп входов 12 группами по (N+1-I) разрядов, каждая из которых начинается с 1-го разряда до (N+l-I)-го разряда, при этом выходы элементов ИЛИ с инверсным входом групп

у которых первые инверсные входы соединены с разрядами вторых групп входов 12 группами по (N+1-I) разрядов, каждая из которых начинается с 1-го разряда до (N+l-I)-го разряда, при этом выходы элементов ИЛИ с инверсным входом групп  блоков детектирования

блоков детектирования  начиная со второго блока

начиная со второго блока  до N-го блока

до N-го блока  соединены с прямыми входами одноименных элементов И с инверсными входами первой группы

соединены с прямыми входами одноименных элементов И с инверсными входами первой группы  инверсные входы которых соединены с разрядами вторых групп входов 12 группами по J разрядов, каждая из которых начинается с N-го разряда до второго разряда, где (J = 1, …, (N-1)), а выходы элементов ИЛИ с инверсным входом группы

инверсные входы которых соединены с разрядами вторых групп входов 12 группами по J разрядов, каждая из которых начинается с N-го разряда до второго разряда, где (J = 1, …, (N-1)), а выходы элементов ИЛИ с инверсным входом группы  первого блока детектирования 61 соединены с входами элемента И 13.

первого блока детектирования 61 соединены с входами элемента И 13.

Выходы элементов И с инверсными входами первой группы  соединены с прямыми входами одноименных элементов И с инверсным входами второй группы

соединены с прямыми входами одноименных элементов И с инверсным входами второй группы

у которых первые инверсные входы (N-2) элементов И, начиная с третьего элемента

у которых первые инверсные входы (N-2) элементов И, начиная с третьего элемента  до N-го элемента

до N-го элемента  соединены с прямыми входами соответствующих предыдущих (N-2) элементов И из второй группы

соединены с прямыми входами соответствующих предыдущих (N-2) элементов И из второй группы  начиная со второго элемента

начиная со второго элемента  до (N-1)-го элемента

до (N-1)-го элемента  а первый инверсный вход второго элемента

а первый инверсный вход второго элемента  соединен с выходом элемента И 13.

соединен с выходом элемента И 13.

Выходы всех (N-1) элементов И с инверсным входом из второй группы  являются соответствующими одноименными (N-1) разрядами, начиная со второго разряда до N-го разряда, групп выходов Q соответствующих модулей детектирования границ нижней 5L и верхней 5Н, а первый разряд выходов Q соединен с выходом соответствующего элемента И 13.

являются соответствующими одноименными (N-1) разрядами, начиная со второго разряда до N-го разряда, групп выходов Q соответствующих модулей детектирования границ нижней 5L и верхней 5Н, а первый разряд выходов Q соединен с выходом соответствующего элемента И 13.

Разряды групп выходов Q модулей детектирования нижней 5L и верхней 5Н границ являются одноименными разрядами внутренних шин начальных разрядов групп соответственно нижней BL и верхней ВН границ. Причем все N разрядов шины нижней границы BL соединены с прямыми входами одноименных элементов И с инверсным входом третьей группы  выходы которых являются разрядами внутренней шины начальных разрядов групп заданного диапазона BLH, которая соединена с одноименными разрядами внешних выходов начальных разрядов групп заданного диапазона QULH и подключена к входам первого блока счета единиц 11, выходы которого являются соответствующими разрядами группы внешних выходов количества групп заданного диапазона QLH.

выходы которых являются разрядами внутренней шины начальных разрядов групп заданного диапазона BLH, которая соединена с одноименными разрядами внешних выходов начальных разрядов групп заданного диапазона QULH и подключена к входам первого блока счета единиц 11, выходы которого являются соответствующими разрядами группы внешних выходов количества групп заданного диапазона QLH.

Причем все N разрядов внутренней шины начальных разрядов групп верхней ВН границы соединены с инверсными входами одноименных элементов И с инверсным входом третьей группы  а также являются одноименными разрядами внешних выходов начальных разрядов групп верхней границы QUH и подключены к входам второго блока счета единиц 12, выходы которого являются соответствующими разрядами группы внешних выходов количества групп больше верхней границы QH.

а также являются одноименными разрядами внешних выходов начальных разрядов групп верхней границы QUH и подключены к входам второго блока счета единиц 12, выходы которого являются соответствующими разрядами группы внешних выходов количества групп больше верхней границы QH.

ПОДРОБНОЕ ОПИСАНИЕ СУЩНОСТИ ИЗОБРЕТЕНИЯ

Принцип работы предлагаемого устройства состоит в следующем.

Предлагаемое устройство позволяет детектировать в N разрядных блоках входных данных G единичные группы (ряды) содержащие количество единичных бит в заданном диапазоне от нижней границы L до верхней границы Н (группы содержат ≥L (L и более) и <Н (менее) единичных бит, где L<Н, H≤N). Кроме того определяется количество таких групп и их расположение в блоках данных, а также количество групп содержащих ≥ Н (Н и более) единичных бит.

Входные N разрядные блоки данных G последовательно в каждом такте поступают на внешнюю входную шину данных ID. Разрядность границ детектируемых единичных групп задается в двоичном коде - нижняя граница диапазона L на внешней входной шине задания IL, верхняя граница диапазона Н на внешней входной шине задания IH, (количество разрядов которых составляет M=]log2 N[большее целое), которые передаются на первый 1 и второй 2 дешифраторы DC. Далее в первой  и второй

и второй

группах элементов ИЛИ двоичные коды границ IL и IH преобразуются в соответствующие унитарные L и Н разрядные единичные ряды, начиная с первого разряда, которые передаются на соответствующие внутренние шины нижней границы BUL и верхней границы BUH, например, для L=3 формируется значение на шине BUL[8-1]=0000 0111 при разрядности блоков N=8.

группах элементов ИЛИ двоичные коды границ IL и IH преобразуются в соответствующие унитарные L и Н разрядные единичные ряды, начиная с первого разряда, которые передаются на соответствующие внутренние шины нижней границы BUL и верхней границы BUH, например, для L=3 формируется значение на шине BUL[8-1]=0000 0111 при разрядности блоков N=8.

В первом 5L и втором 5Н модулях детектирования границ осуществляется выявление единичных групп (рядов) содержащих соответственно ≥L и ≥Н единичных бит и формирование на соответствующих внутренних шинах BL и ВН начальных разрядов выявленных единичных групп в текущем блоке G на шине входных данных ID.

При этом в группах из N блоков детектирования  соответственно в первом 5L и во втором 5Н модулях детектирования границ, на элементах ИЛИ с инверсным входом соответствующих одноименных групп

соответственно в первом 5L и во втором 5Н модулях детектирования границ, на элементах ИЛИ с инверсным входом соответствующих одноименных групп  осуществляется маскирование старших разрядов с шины входных данных ID, соответствующих нулевым разрядам с внутренних шин задания разрядности нижней границы BUL и верхней границы BUH. При этом на выходах соответствующих маскируемых элементов ИЛИ с инверсным входом формируются единичные значения, а на выходы не маскируемых элементов ИЛИ с инверсным входом передаются соответствующие значения разрядов с шины входных данных ID для заданных разрядностей детектируемых групп нижней границы BUL и верхней границы BUH. При этом в соответствующих блоках детектирования

осуществляется маскирование старших разрядов с шины входных данных ID, соответствующих нулевым разрядам с внутренних шин задания разрядности нижней границы BUL и верхней границы BUH. При этом на выходах соответствующих маскируемых элементов ИЛИ с инверсным входом формируются единичные значения, а на выходы не маскируемых элементов ИЛИ с инверсным входом передаются соответствующие значения разрядов с шины входных данных ID для заданных разрядностей детектируемых групп нижней границы BUL и верхней границы BUH. При этом в соответствующих блоках детектирования  проводится выделение (N+1-I) разрядных групп, где

проводится выделение (N+1-I) разрядных групп, где

Далее на элементах И 13 и в первых группах из (N-1)-го элементов И с инверсными входами  соответственно первого 5L и во второго 5Н модулей детектирования границ, проводится проверка на наличие единичных групп содержащих соответственно ≥L и ≥Н единичных бит и при выявлении таких единичных групп на соответствующих выходах элемента И 13 и в первых группах из (N-1)-го элементов И с инверсными входами

соответственно первого 5L и во второго 5Н модулей детектирования границ, проводится проверка на наличие единичных групп содержащих соответственно ≥L и ≥Н единичных бит и при выявлении таких единичных групп на соответствующих выходах элемента И 13 и в первых группах из (N-1)-го элементов И с инверсными входами  формируются единичные значения.

формируются единичные значения.

При наличии во входных блоках G на шине ID единичных групп содержащих бит больше заданных границ, соответственно ≥L и ≥Н, будет выявлено несколько искомых соседних единичных групп (единичные значения будут установлены на выходах соседних элементов И 13 и группы  ). Маскирование соседних единичных групп, относящихся к одной группе во входном блоке ID, осуществляется во второй группе

). Маскирование соседних единичных групп, относящихся к одной группе во входном блоке ID, осуществляется во второй группе

элементов И с инверсным входом. При этом сохраняется единичное значение на выходах элементов соответствующих начальным (младшим) разрядам выявленных единичных групп.

элементов И с инверсным входом. При этом сохраняется единичное значение на выходах элементов соответствующих начальным (младшим) разрядам выявленных единичных групп.

Значения с выходов элемента И 13 и второй группы  элементов И с инверсным входом являются выходами Q модулей детектирования нижней 5L и верхней 5Н границ и соединены с соответствующими разрядами внутренних N разрядных шин начальных разрядов групп соответственно нижней границы BL и верхней границы ВН.

элементов И с инверсным входом являются выходами Q модулей детектирования нижней 5L и верхней 5Н границ и соединены с соответствующими разрядами внутренних N разрядных шин начальных разрядов групп соответственно нижней границы BL и верхней границы ВН.

Далее в третьей группе из N элементов И с инверсным входом  осуществляется маскирование выявленных групп содержащих ≥Н единичных бит.Значения с выходов третьей группы элементов

осуществляется маскирование выявленных групп содержащих ≥Н единичных бит.Значения с выходов третьей группы элементов  являются соответствующими разрядами внутренней N разрядной шины BLH начальных разрядов групп заданного диапазона, которые далее поступают на группу входов первого блока счета единиц 11, в котором осуществляется счет количества выявленных единичных групп, соответствующих заданному диапазону границ ≥L и <Н, в текущем блоке входных данных ID.

являются соответствующими разрядами внутренней N разрядной шины BLH начальных разрядов групп заданного диапазона, которые далее поступают на группу входов первого блока счета единиц 11, в котором осуществляется счет количества выявленных единичных групп, соответствующих заданному диапазону границ ≥L и <Н, в текущем блоке входных данных ID.

Далее значения с выхода первого блока счета единиц 11 передается на группу внешних выходов количества групп заданного диапазона QLH, а значения разрядов с внутренней шины BLH начальных разрядов групп заданного диапазона являются соответствующими разрядами группы внешних выходов начальных разрядов групп заданного диапазона QULH.

Кроме того значения разрядов с внутренней шины начальных разрядов групп верхней границы ВН являются соответствующими разрядами группы внешних выходов начальных разрядов групп верхней границы QUH, а также поступают на группу входов второго блока счета единиц 12, в котором осуществляется счет количества выявленных единичных групп превышающих верхнюю границу диапазона>Н, и значение с выхода второго блока счета единиц 12 передается на группу внешних выходов количества групп больше верхней границы QH.

Предлагаемое устройство работает следующим образом.

На фиг.2 приведена временная диаграмма выявления единичных групп во входных N=8 разрядных десяти блоках данных  при задании разрядности нижней границы IL=1, 2 и 4 и верхней границы IH=4 и 5.

при задании разрядности нижней границы IL=1, 2 и 4 и верхней границы IH=4 и 5.

В тактах 1-3 осуществляется детектирование групп, содержащих два и более единичных бит IL=2 и менее четырех бит 1Н=4 в трех входных блоках данных G1, G2, G3. Для заданных границ диапазона на выходах первой и второй

и второй группах элементов ИЛИ двоичные коды границ IL=2 и 1Н=4 преобразуются в соответствующие унитарные L и Н разрядные единичные ряды, начиная с первого разряда, которые передаются на соответствующие внутренние шины нижней границы BUL=0000 0011 и верхней границы BUH=0000 1111.

группах элементов ИЛИ двоичные коды границ IL=2 и 1Н=4 преобразуются в соответствующие унитарные L и Н разрядные единичные ряды, начиная с первого разряда, которые передаются на соответствующие внутренние шины нижней границы BUL=0000 0011 и верхней границы BUH=0000 1111.

В такте 1 на внешней N=8-ми разрядной входной шине данных задается код Ш[8-1]=1101 1011 первого блока G1, содержащий три двухразрядные единичные группы. На элементах ИЛИ с инверсным входом блоков детектирования

блоков детектирования в первом 5L модуле детектировани нижней границы проводится маскирование шести старших разрядов, а во втором 5Н модуле детектирования верхней границы проводится маскирование четырех старших разрядов. Далее на элементах И 13 и в первых группах из (N-1)-го элементов И с инверсными входами

в первом 5L модуле детектировани нижней границы проводится маскирование шести старших разрядов, а во втором 5Н модуле детектирования верхней границы проводится маскирование четырех старших разрядов. Далее на элементах И 13 и в первых группах из (N-1)-го элементов И с инверсными входами  соответственно первого 5L и во второго 5Н модулей детектирования границ, проводится проверка на наличие единичных групп содержащих соответственно ≥L=2 и ≥Н=4 единичных бит и на выходах формируются единичные значения 5L (8[8-1], 13)=0100 1001, соответствующее начальным разрядам трех выявленных двухразрядных единичных групп, и 5Н (8[8-1], 13)=00000000, так как отсутствуют группы, содержащие четыре и более единичных бит.Данные значения без маскирования через соответствующие вторые группы

соответственно первого 5L и во второго 5Н модулей детектирования границ, проводится проверка на наличие единичных групп содержащих соответственно ≥L=2 и ≥Н=4 единичных бит и на выходах формируются единичные значения 5L (8[8-1], 13)=0100 1001, соответствующее начальным разрядам трех выявленных двухразрядных единичных групп, и 5Н (8[8-1], 13)=00000000, так как отсутствуют группы, содержащие четыре и более единичных бит.Данные значения без маскирования через соответствующие вторые группы  элементов И с инверсным входом передаются на группы выходов Q, соответственно первого 5L и во второго 5Н модулей детектирования границ, и далее на внутренние шины начальных разрядов групп нижней границы BL=0100 1001 и верхней границы ВН=0000 0000. Далее через элементы И с инверсным входом третьей группы

элементов И с инверсным входом передаются на группы выходов Q, соответственно первого 5L и во второго 5Н модулей детектирования границ, и далее на внутренние шины начальных разрядов групп нижней границы BL=0100 1001 и верхней границы ВН=0000 0000. Далее через элементы И с инверсным входом третьей группы  значение с внутренней шины начальных разрядов групп нижней границы BL без маскирования передается на внутреннюю шину BLH=0100 1001 начальных разрядов групп заданного диапазона, которое далее передается на группу внешних выходов начальных разрядов групп заданного диапазона QULH=0100 1001, так как не выявлено групп содержащих четыре и более единичных бит.При этом в первом блоке счета единиц 11 осуществляется счет трех выявленных двухразрядных единичных групп, соответствующих заданному диапазону границ ≥L=2 и <Н=4 в первом блоке G1 входных данных для ID[8-1]=1101 1011, и формирование двоичного кода, передаваемого на группу внешних выходов количества единичных групп заданного диапазона QLH=3. Одновременно на выходе второго блока счета единиц 12 формируется нулевое значение QH=0 - отсутствие выявленных групп больше верхней границы QH.

значение с внутренней шины начальных разрядов групп нижней границы BL без маскирования передается на внутреннюю шину BLH=0100 1001 начальных разрядов групп заданного диапазона, которое далее передается на группу внешних выходов начальных разрядов групп заданного диапазона QULH=0100 1001, так как не выявлено групп содержащих четыре и более единичных бит.При этом в первом блоке счета единиц 11 осуществляется счет трех выявленных двухразрядных единичных групп, соответствующих заданному диапазону границ ≥L=2 и <Н=4 в первом блоке G1 входных данных для ID[8-1]=1101 1011, и формирование двоичного кода, передаваемого на группу внешних выходов количества единичных групп заданного диапазона QLH=3. Одновременно на выходе второго блока счета единиц 12 формируется нулевое значение QH=0 - отсутствие выявленных групп больше верхней границы QH.

В такте 2 на внешней 8-ми разрядной входной шине данных задается код ID[8-1]=1101 1101 второго блока G2, содержащий двухразрядную, трехразрядную и одноразрядную единичные группы. Далее, при маскировании шести старших разрядов в первом 5L модуле и четырех старших разрядов во втором 5Н модуле, на выходах элементов И 13 и в первых группах элементов И с инверсными входами устанавливаются значения 5L (8[8-1], 13)=0100 1100 и 5Н (8[8-1], 13)=0000 0000. При этом единичные значения, установленные на выходах соседних третьего и четвертого элементов 5L (8[4-3])=11, соответствуют одной группе (ряду) из трех единичных бит во входном блоке ID. Поэтому во второй группе

устанавливаются значения 5L (8[8-1], 13)=0100 1100 и 5Н (8[8-1], 13)=0000 0000. При этом единичные значения, установленные на выходах соседних третьего и четвертого элементов 5L (8[4-3])=11, соответствуют одной группе (ряду) из трех единичных бит во входном блоке ID. Поэтому во второй группе  элементов И с инверсным входом первого 5L модуля детектирования нижней границы маскируется единичное значение с выхода четвертого элемента 8[4]=1 и на внутренней шине начальных разрядов групп нижней границы устанавливается код BL=0100 0100, соответствующий двум единичным группам содержащим два и более единичных бит IL=2 (BUL=0000 ООП). Далее через элементы И с инверсным входом третьей

элементов И с инверсным входом первого 5L модуля детектирования нижней границы маскируется единичное значение с выхода четвертого элемента 8[4]=1 и на внутренней шине начальных разрядов групп нижней границы устанавливается код BL=0100 0100, соответствующий двум единичным группам содержащим два и более единичных бит IL=2 (BUL=0000 ООП). Далее через элементы И с инверсным входом третьей значение с внутренней шины начальных разрядов групп нижней границы BL без маскирования передается на внутреннюю шину BLH=0100 0100 начальных разрядов групп заданного диапазона, которое далее передается на группу внешних выходов начальных разрядов групп заданного диапазона QULH=0100 0100, так как не выявлено групп содержащих четыре и более единичных бит.При этом на выходе первого блока счета единиц 11 формируется код количества единичных групп заданного диапазона QLH=2 для второго блока G2 входных данных для ID[8-1]=1101 1101 и одновременно на выходе второго блока счета единиц 12 формируется нулевое значение QH=0 - отсутствие выявленных групп больше верхней границы QH.

значение с внутренней шины начальных разрядов групп нижней границы BL без маскирования передается на внутреннюю шину BLH=0100 0100 начальных разрядов групп заданного диапазона, которое далее передается на группу внешних выходов начальных разрядов групп заданного диапазона QULH=0100 0100, так как не выявлено групп содержащих четыре и более единичных бит.При этом на выходе первого блока счета единиц 11 формируется код количества единичных групп заданного диапазона QLH=2 для второго блока G2 входных данных для ID[8-1]=1101 1101 и одновременно на выходе второго блока счета единиц 12 формируется нулевое значение QH=0 - отсутствие выявленных групп больше верхней границы QH.

В такте 3 на внешней 8-ми разрядной входной шине данных задается код ID[8-1]=1110 1111 третьего блока G3, содержащий трехразрядную и четырехразрядную единичные группы. Для данного кода ID на выходах элемента И 13 и в первой группе элементов И с инверсными входами первого 5L модуля детектирования нижней границы устанавливаются значения 5L (8[8-1], 13)=0110 0111, соответствующие начальным разрядам выявленных единичных групп содержащим ≥L=2 бит.При этом единичные значения, установленные на выходах соседних элементов, соответствуют одной группе (ряду) из трех и второй группе (ряду) из четырех единичных бит во входном блоке ID. Поэтому они маскируются во второй группе

первого 5L модуля детектирования нижней границы устанавливаются значения 5L (8[8-1], 13)=0110 0111, соответствующие начальным разрядам выявленных единичных групп содержащим ≥L=2 бит.При этом единичные значения, установленные на выходах соседних элементов, соответствуют одной группе (ряду) из трех и второй группе (ряду) из четырех единичных бит во входном блоке ID. Поэтому они маскируются во второй группе  элементов И с инверсным входом и на внутренней шине начальных разрядов групп нижней границы устанавливается код BL=0010 0001. На выходах элемента И 13 и в первой группе элементов И с инверсными входами

элементов И с инверсным входом и на внутренней шине начальных разрядов групп нижней границы устанавливается код BL=0010 0001. На выходах элемента И 13 и в первой группе элементов И с инверсными входами второго 5Н модуля детектирования верхней границы устанавливаются значения 5Н (8[8-1], 13)=0000 0001, соответствующее первому разряду выявленной четырехразрядной единичной группе ≥Н=4 бит, которое без маскирования передается на внутреннюю шину начальных разрядов групп верхней границы ВН=0000 0001. Далее на элементах И с инверсным входом третьей группы

второго 5Н модуля детектирования верхней границы устанавливаются значения 5Н (8[8-1], 13)=0000 0001, соответствующее первому разряду выявленной четырехразрядной единичной группе ≥Н=4 бит, которое без маскирования передается на внутреннюю шину начальных разрядов групп верхней границы ВН=0000 0001. Далее на элементах И с инверсным входом третьей группы

осуществляется маскирование первого разряда и на внутренней шине начальных разрядов групп заданного диапазона устанавливается код BLH=0010 0000, соответствующий одной группе из заданного диапазона ≥L=2 и <Н=4, для которого на выходе первого блока счета единиц 11 формируется код количества единичных групп заданного диапазона QLH=1 для третьего блока G3 входных данных для ID[8-1]=1110 1111 и одновременно на выходе второго блока счета 12 единиц формируется значение QH=1, соответствующее одной группе содержащей одну четырехразрядную групп ≥Н=4.

осуществляется маскирование первого разряда и на внутренней шине начальных разрядов групп заданного диапазона устанавливается код BLH=0010 0000, соответствующий одной группе из заданного диапазона ≥L=2 и <Н=4, для которого на выходе первого блока счета единиц 11 формируется код количества единичных групп заданного диапазона QLH=1 для третьего блока G3 входных данных для ID[8-1]=1110 1111 и одновременно на выходе второго блока счета 12 единиц формируется значение QH=1, соответствующее одной группе содержащей одну четырехразрядную групп ≥Н=4.

В тактах 4-6 осуществляется детектирование групп, содержащих два и более единичных бит IL=2 и менее пяти бит Ш=5 в трех входных блоках данных G4, G5, G6. Для заданных границ диапазона на выходах первой и второй

и второй

группах элементов ИЛИ двоичные коды границ IL=2 и IH=5 преобразуются в соответствующие унитарные L и Н разрядные единичные ряды, начиная с первого разряда, которые передаются на соответствующие внутренние шины нижней границы BUL=0000 0011 и верхней границы BUH=0001 1111.

В такте 4 на внешней 8-ми разрядной входной шине данных задается код ID[8-1]=0101 1101 четвертого блока G4, содержащий две одноразрядные и одну трехразрядную единичные группы. Для данного кода ID на выходах элемента И 13 и в первой группе элементов И с инверсными входами первого 5L модуля детектирования нижней границы устанавливаются значения 5L (8[8-1], 13)=0000 1100, соответствующий одной трехразрядной единичной группе. Поэтому маскируется четвертый разряд и на внутренней шине начальных разрядов групп нижней границы устанавливается код BL=0000 0100. Одновременно на внутренней шине начальных разрядов групп верхней границы устанавливается код ВН=0000 0000. Поэтому через элементы И с инверсным входом третьей группы

первого 5L модуля детектирования нижней границы устанавливаются значения 5L (8[8-1], 13)=0000 1100, соответствующий одной трехразрядной единичной группе. Поэтому маскируется четвертый разряд и на внутренней шине начальных разрядов групп нижней границы устанавливается код BL=0000 0100. Одновременно на внутренней шине начальных разрядов групп верхней границы устанавливается код ВН=0000 0000. Поэтому через элементы И с инверсным входом третьей группы значение с внутренней шины начальных разрядов групп нижней границы BL без маскирования передается на внутреннюю шину начальных разрядов групп заданного диапазона BLH=0000 0100, которое далее передается на группу внешних выходов начальных разрядов групп заданного диапазона QULH=0000 0100, а на выходе первого блока счета единиц 11 формируется код количества единичных групп заданного диапазона QLH=1 для четвертого блока G4.

значение с внутренней шины начальных разрядов групп нижней границы BL без маскирования передается на внутреннюю шину начальных разрядов групп заданного диапазона BLH=0000 0100, которое далее передается на группу внешних выходов начальных разрядов групп заданного диапазона QULH=0000 0100, а на выходе первого блока счета единиц 11 формируется код количества единичных групп заданного диапазона QLH=1 для четвертого блока G4.

В такте 5 на внешней 8-ми разрядной входной шине данных задается код ID[8-1]=1111 0111 пятого блока G5, содержащий трехразрядную и четырехразрядную единичные группы. Для данного кода ID на выходах элемента И 13 и в первой группе элементов И с инверсными входами первого 5L модуля детектирования нижней границы устанавливаются значения 5L (8[8-1], 13)=0111 ООП, соответствующий четырехразрядной и трехразрядной единичным группам, для которых единичные значения установлены в соседних разрядах. Поэтому во второй группе

первого 5L модуля детектирования нижней границы устанавливаются значения 5L (8[8-1], 13)=0111 ООП, соответствующий четырехразрядной и трехразрядной единичным группам, для которых единичные значения установлены в соседних разрядах. Поэтому во второй группе элементов И с инверсным входом первого 5L модуля детектирования нижней границы маскируется единичное значение в старших разрядах для выявленных групп и на внутренней шине начальных разрядов групп нижней границы устанавливается код BL=0001 0001. Одновременно на внутренней шине начальных разрядов групп верхней границы устанавливается код ВН=0000 0000. Поэтому через элементы И с инверсным входом третьей группы

элементов И с инверсным входом первого 5L модуля детектирования нижней границы маскируется единичное значение в старших разрядах для выявленных групп и на внутренней шине начальных разрядов групп нижней границы устанавливается код BL=0001 0001. Одновременно на внутренней шине начальных разрядов групп верхней границы устанавливается код ВН=0000 0000. Поэтому через элементы И с инверсным входом третьей группы значение с внутренней шины начальных разрядов групп нижней границы BL без маскирования передается на внутреннюю шину начальных разрядов групп заданного диапазона BLH=0001 0001, которое далее передается на группу внешних выходов начальных разрядов групп заданного диапазона QULH=0001 0001, а на выходе первого блока счета единиц 11 формируется код количества единичных групп заданного диапазона QLH=2 для пятого блока G5.

значение с внутренней шины начальных разрядов групп нижней границы BL без маскирования передается на внутреннюю шину начальных разрядов групп заданного диапазона BLH=0001 0001, которое далее передается на группу внешних выходов начальных разрядов групп заданного диапазона QULH=0001 0001, а на выходе первого блока счета единиц 11 формируется код количества единичных групп заданного диапазона QLH=2 для пятого блока G5.

В такте 6 на внешней 8-ми разрядной входной шине данных задается код ID[8-1]=1111 1011 шестого блока G6, содержащий двухразрядную и пятиразрядную единичные группы. Для данного кода ID выходах элементов И 13 и первых групп элементов И с инверсными входами устанавливаются значения 5L (8[8-1], 13)=0111 1001 и 5Н (8[8-1], 13)=0000 1000. Далее в первом 5L модуле детектирования нижней границы маскируется единичное значение в трех старших разрядах для выявленной шестиразрядной группы и на внутренней шине начальных разрядов групп нижней границы устанавливается код BL=0000 1001. Далее на элементах И с инверсным входом третьей группы

устанавливаются значения 5L (8[8-1], 13)=0111 1001 и 5Н (8[8-1], 13)=0000 1000. Далее в первом 5L модуле детектирования нижней границы маскируется единичное значение в трех старших разрядах для выявленной шестиразрядной группы и на внутренней шине начальных разрядов групп нижней границы устанавливается код BL=0000 1001. Далее на элементах И с инверсным входом третьей группы осуществляется маскирование четвертого разряда и на внутренней шине начальных разрядов групп заданного диапазона устанавливается код BLH=0000 0001, соответствующий одной группе из заданного диапазона ≥L=2 и <Н=5, для которого на выходе первого блока счета единиц 11 формируется код количества единичных групп заданного диапазона QLH=T для входного блока G6 входных данных для ID[8-1]=1111 1011 и одновременно на выходе второго блока счета 12 единиц формируется значение QH=1, соответствующее одной группе содержащей больше верхней границы ≥Н=5.

осуществляется маскирование четвертого разряда и на внутренней шине начальных разрядов групп заданного диапазона устанавливается код BLH=0000 0001, соответствующий одной группе из заданного диапазона ≥L=2 и <Н=5, для которого на выходе первого блока счета единиц 11 формируется код количества единичных групп заданного диапазона QLH=T для входного блока G6 входных данных для ID[8-1]=1111 1011 и одновременно на выходе второго блока счета 12 единиц формируется значение QH=1, соответствующее одной группе содержащей больше верхней границы ≥Н=5.

В тактах 7-8 осуществляется детектирование групп, содержащих четыре и более единичных бит IL=4 и менее пяти бит Ш=5 в двух входных блоках данных G7, G8. Для заданных границ диапазона устанавливаются коды на внутренних шинах нижней границы BUL=0000 1111 и верхней границы BUH=0001 1111.

В такте 7 на внешней 8-ми разрядной входной шине данных задается код ID[8-1]=1111 1011 седьмого блока G7, содержащий шестиразрядную и двухразрядную единичные группы. Для данного кода ID выходах элементов И 13 и первых групп элементов И с инверсными входами устанавливаются значения 5L (8[8-1], 13)=0001 1000 и 5Н (8[8-1], 13)=0001 0000. Далее в первом 5L модуле детектирования нижней границы маскируется единичное значение в двух старших разрядах для выявленной шестиразрядной группы и на внутренней шине начальных разрядов групп нижней границы устанавливается код BL=0000 1000. Далее на элементах И с инверсным входом третьей группы

устанавливаются значения 5L (8[8-1], 13)=0001 1000 и 5Н (8[8-1], 13)=0001 0000. Далее в первом 5L модуле детектирования нижней границы маскируется единичное значение в двух старших разрядах для выявленной шестиразрядной группы и на внутренней шине начальных разрядов групп нижней границы устанавливается код BL=0000 1000. Далее на элементах И с инверсным входом третьей группы осуществляется маскирование четвертого разряда и на внутренней шине начальных разрядов групп заданного диапазона устанавливается нулевой код BLH=0000 0000, соответствующий отсутствию групп из заданного диапазона ≥L=4 и<Н=5, поэтому на выходе первого блока счета единиц 11 формируется нулевой код количества единичных групп заданного диапазона QLH=0 для входного блока G6 входных данных для ID[8-1]=1111 1011 и одновременно на выходе второго блока счета 12 единиц формируется значение QH=1, соответствующее одной группе содержащей больше верхней границы ≥Н=5.

осуществляется маскирование четвертого разряда и на внутренней шине начальных разрядов групп заданного диапазона устанавливается нулевой код BLH=0000 0000, соответствующий отсутствию групп из заданного диапазона ≥L=4 и<Н=5, поэтому на выходе первого блока счета единиц 11 формируется нулевой код количества единичных групп заданного диапазона QLH=0 для входного блока G6 входных данных для ID[8-1]=1111 1011 и одновременно на выходе второго блока счета 12 единиц формируется значение QH=1, соответствующее одной группе содержащей больше верхней границы ≥Н=5.

В такте 8 на внешней 8-ми разрядной входной шине данных задается код ID[8-1]=1011 1100 восьмого блока G8, содержащий одноразрядную и четырехразрядную единичные группы. Для данного кода ID устанавливаются значения 5L (8[8-1], 13)=0000 0100 и 5Н (8[8-1], 13)=0000 0000, которые без маскирования передаются на внутренние шины нижней границы BL=0000 0100 и верхней границы ВН=0000 0000. Далее значение нижней границы BL без маскирования передается на внутреннюю шину BLH=0000 0100 начальных разрядов групп заданного диапазона, и на выходах блоков счета единиц устанавливаются коды количества групп QLH=1 и QH=0. Таким образом, при задании значения нижней границы L бит, а значение верхней границы на единицу больше H=(L+1) выявляются единичные группы с разрядностью равной нижней границе L.

В тактах 9-10 осуществляется детектирование групп, содержащих один и более единичных бит IL=1 и менее пяти бит IH=5 в двух входных блоках данных G9, G10. Для заданных границ диапазона устанавливаются коды на внутренних шинах нижней границы BUL=0000 0001 и верхней границы BUH=0001 1111.

В такте 9 на внешней 8-ми разрядной входной шине данных задается код ID[8-1]=1001 0111 девятого блока G9, содержащий две одноразрядные и одну трехразрядную единичные группы. Для данного кода ID устанавливаются значения 5L (8[8-1], 13)=1001 0111 и 5Н (8[8-1], 13)=0000 0000. Далее в первом 5L модуле детектирования нижней границы маскируется единичное значение в двух старших разрядах для выявленной трехразрядной группы и на внутренней шине начальных разрядов групп нижней границы устанавливается код BL=1001 0001. Далее значение нижней границы BL без маскирования передается на внутреннюю шину BLH=1001 0001 начальных разрядов групп заданного диапазона, и на выходах блоков счета единиц устанавливаются коды количества групп QLH=3 и QH=0 для входного блока G9.

В такте 10 на внешней 8-ми разрядной входной шине данных задается код ID[8-1]=1111 1101 десятого блока G10, содержащий одноразрядную и шестиразрядную единичные группы. Для данного кода ID устанавливаются значения 5L (8[8-1], 13)=1111 1101 и 5Н (8[8-1], 13)=0000 0100. Далее в первом 5L модуле детектирования нижней границы маскируется единичное значение в пяти старших разрядах для выявленной шестиразрядной группы и на внутренней шине начальных разрядов групп нижней границы устанавливается код BL=0000 0101. Далее на элементах И с инверсным входом третьей группы  осуществляется маскирование второго разряда и на внутренней шине начальных разрядов групп заданного диапазона устанавливается код ВШ=0000 0001, соответствующий одной группе из заданного диапазона ≥L=T и <Н=5, для которого на выходе первого блока счета единиц 11 формируется код количества единичных групп заданного диапазона QLH=1 для входного блока G10 входных данных для ID[8-1]=1111 1101 и одновременно на выходе второго блока счета 12 единиц формируется значение QH=1, соответствующее одной группе содержащей больше верхней границы ≥Н=5.

осуществляется маскирование второго разряда и на внутренней шине начальных разрядов групп заданного диапазона устанавливается код ВШ=0000 0001, соответствующий одной группе из заданного диапазона ≥L=T и <Н=5, для которого на выходе первого блока счета единиц 11 формируется код количества единичных групп заданного диапазона QLH=1 для входного блока G10 входных данных для ID[8-1]=1111 1101 и одновременно на выходе второго блока счета 12 единиц формируется значение QH=1, соответствующее одной группе содержащей больше верхней границы ≥Н=5.

Таким образом, для N разрядных входных блоков данных G осуществляется выявление единичных групп (рядов) содержащих количество единичных бит в заданных границах диапазона от L до Н (группы содержат ≥L (L и более) и менее Н единичных бит, где 1≤L<Н, H≤N). проводится счет таких групп и их расположение во входных блоках

Предлагаемое устройство может быть применено для аппаратной реализации статистических тестов, разработанных лабораторией информационных технологий Национального института стандартов и технологий (NIST, США), целью которых является определение меры случайности двоичных последовательностей, порожденных генераторами случайных чисел. В частности, предлагаемое устройство осуществляет подсчет количества единичных групп заданной размерности в N разрядных входных блоках.

При обработке результатов физических экспериментов предлагаемое устройство обеспечивает выявление событий заданной размерности, определение их количества и размещение во входных блоках.

Вышеизложенные сведения позволяют сделать вывод, что предлагаемое устройство решает поставленную задачу, обладает регулярностью узлов и связей, и соответствует заявляемому техническому результату - расширение арсенала средств того же назначения в части обеспечения возможности детектирования групп единичных бит в заданном диапазоне разрядности, определение количества выявленных групп и их размещение в блоках данных.

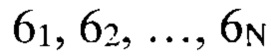

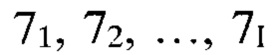

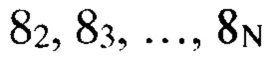

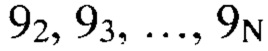

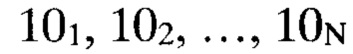

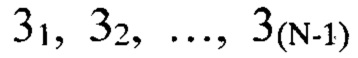

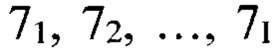

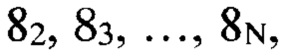

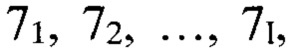

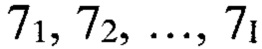

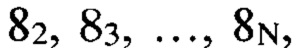

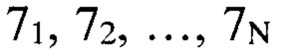

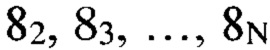

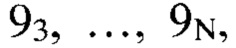

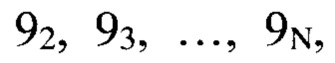

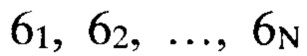

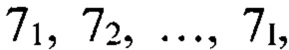

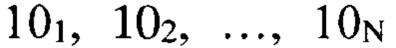

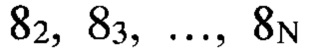

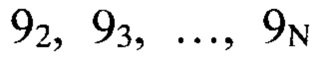

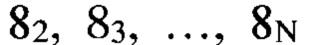

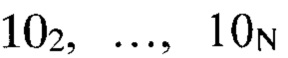

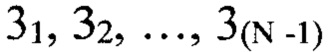

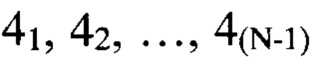

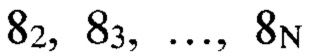

Изобретение относится к устройствам обработки данных и может быть использовано для построения функциональных узлов для анализа свойств генераторов псевдослучайных последовательностей двоичных чисел. Технический результат - обеспечение возможности детектирования групп единичных бит в заданном диапазоне разрядности, определение количества выявленных групп и их размещение в блоках данных. Устройство содержит внешнюю N разрядную входную шины, два дешифратора, две группы из (N-1)-го элементов ИЛИ, группу из N элементов И с инверсным входом 101, 102, … 10N, два блока счета единиц, первый модуль детектирования нижней границы 5L и второй модуль детектирования верхней границы 5Н, каждый из которых содержит группу из N блоков детектирования 61, 62, …, 6N, N групп 71, 72, … 71 из (N+1-I) элементов ИЛИ с инверсным входом 1-ых блоков детектирования 61, первую группу из (N-1)-го элементов И с инверсными входами 82, 83, …, 8N, вторую группу из (N-1)-го элементов И с инверсным входом 92, 93, …, 9N, элемент И 13, внутренние шины нижней BUL и верхней BUH границ, начальных разрядов групп заданного диапазона BLH, нижней BL и верхней ВН границ. 2 ил.

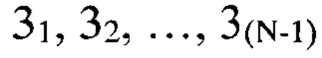

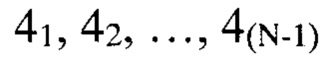

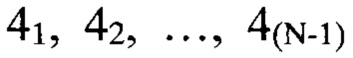

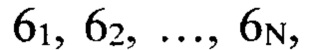

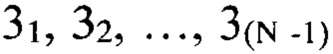

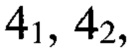

Устройство для детектирования в блоках данных групп единичных бит в заданных границах содержит внешнюю N разрядную входную шину данных ID блоков данных G, внешние М разрядные входные шины задания нижней IL и верхней IH границ, где M=]log2 N[ большее целое, группы внешних выходов количества групп заданного диапазона QLH и больше верхней границы QH, начальных разрядов групп заданного диапазона QULH и верхней границы QUH, первый 1 и второй 2 дешифраторы, первую 31, 32, …, 3(N-1) и вторую 41, 42, … 4(N-1) группы из (N-1)-го элементов ИЛИ, третью группу из N элементов И с инверсным входом 101, 102, … 10N, первый 11 и второй 12 блоки счета единиц, первый модуль детектирования нижней границы 5L и второй модуль детектирования верхней границы 5Н, каждый из которых содержит группу из N блоков детектирования 61, 62, …, 6N, N групп 71, 72, …, 71 из (N+1-I) элементов ИЛИ с инверсным входом 1-ых блоков детектирования 61, где 1=1, N, первую группу из (N-1)-го элементов И с инверсными входами 82, 83, …, 8N, вторую группу из (N-1)-го элементов И с инверсным входом 92, 93, …, 9N и элемент И 13,

а также введены внутренние шины нижней BUL и верхней BUH границ, начальных разрядов групп заданного диапазона BLH, нижней BL и верхней ВН границ,

причем разряды внешних входных шин задания нижней IL и верхней IH границ соединены с адресными входами соответственно первого 1 и второго 2 дешифраторов, у которых выходы, с первого выхода до (N-1)-го выхода, соединены с первыми входами соответствующих одноименных (N-1)-г элементов ИЛИ соответственно первой 31, 32, …, 3(N-1) и второй 41, 42, …, 4(N-1) групп, выходы которых являются соответствующими одноименными разрядами, с первого разряда до (N-1)-го разряда, внутренних шин соответственно нижней BUL и верхней BUH границ, у которых N-ые разряды соединены с N-ми выходами соответственно первого 1 и второго 2 дешифраторов, а также выходы элементов в первой 31, 32, …, 3(N-1) и второй 41, 42, …, 4(N-1) группах, начиная с выхода (N-1)-го элемента до второго элемента, соединены со вторыми входами соответствующих предыдущих элементов ИЛИ в первой 31, 32, …, 3(N-1) и второй 41, 42, …, 4(N-1) группах, начиная с (N-2)-го элемента до первого элемента, а вторые входы (N-1)-ых элементов групп соединены с N-ми выходами соответственно первого 1 и второго 2 дешифраторов,

причем разряды внешней входной шины данных ID соединены с первыми группами входов I1 первого модуля детектирования нижней границы 5L и второго модуля детектирования верхней границы 5Н, у которых вторые группы входов 12 соединены с разрядами внутренних шин соответственно нижней BUL и верхней BUH границ,

кроме того в первом модуле детектирования нижней границы 5L и втором модуле детектирования верхней границы 5Н разряды первых групп входов I1 группами по (N+1-I) разрядов, каждая из которых начинается с I-го разряда до N-го разряда (1=1, N), соединены в соответствующих I-ых блоках 61 детектирования группы 61, 62, …, 6N со вторыми прямыми входами элементов ИЛИ с инверсным входом групп 71, 72, …, 7I, у которых первые инверсные входы соединены с разрядами вторых групп входов 12 группами по (N+1-I) разрядов, каждая из которых начинается с 1-го разряда до (N+1-I)-го разряда, при этом выходы элементов ИЛИ с инверсным входом групп 71, 72, …, 7I блоков детектирования 61, начиная со второго блока 62 до N-го блока 6N, соединены с прямыми входами одноименных элементов И с инверсными входами первой группы 82, 83, …, 8N, инверсные входы которых соединены с разрядами вторых групп входов 12 группами по J разрядов, каждая из которых начинается с N-го разряда до второго разряда, где (J=1, (N-1)), а выходы элементов ИЛИ с инверсным входом группы 71, 72, …, 7N первого блока детектирования 61 соединены с входами элемента И 13,

причем выходы элементов И с инверсными входами первой группы 82, 83, …, 8N соединены с прямыми входами одноименных элементов И с инверсным входами второй группы 92, 93, …, 9N, у которых первые инверсные входы (N-2) элементов И, начиная с третьего элемента 93 до N-го элемента 9N, соединены с прямыми входами соответствующих предыдущих (N-2) элементов И из второй группы 92, 93, …, 9N, начиная со второго элемента 92 до (N-1)-го элемента 9(N-1), а первый инверсный вход второго элемента 9 г соединен с выходом элемента И 13,

кроме того, выходы всех (N-1) элементов И с инверсным входом из второй группы 92, 93, …, 9N являются соответствующими одноименными (N-1) разрядами, начиная со второго разряда до N-го разряда, групп выходов Q соответствующих модулей детектирования границ нижней 5L и верхней 5Н, а первый разряд выходов Q соединен с выходом соответствующего элемента И 13,

причем разряды групп выходов Q модулей детектирования нижней 5L и верхней 5Н границ являются одноименными разрядами внутренних шин начальных разрядов групп соответственно нижней BL и верхней ВН границ, причем все N разрядов шины нижней границы BL соединены с прямыми входами одноименных элементов И с инверсным входом третьей группы 101, 102, …, 10N, выходы которых являются разрядами внутренней шины начальных разрядов групп заданного диапазона BLH, которая соединена с одноименными разрядами внешних выходов начальных разрядов групп заданного диапазона QULH и подключена к входам первого блока счета единиц 11, выходы которого являются соответствующими разрядами группы внешних выходов количества групп заданного диапазона QLH,

причем все N разрядов внутренней шины начальных разрядов групп верхней ВН границы соединены с инверсными входами одноименных элементов И с инверсным входом третьей группы 101, 102, …, 10N, а также являются одноименными разрядами внешних выходов начальных разрядов групп верхней границы QUH и подключены к входам второго блока счета единиц 12, выходы которого являются соответствующими разрядами группы внешних выходов количества групп больше верхней границы QH.

| УСТРОЙСТВО ДЛЯ ДЕТЕКТИРОВАНИЯ ГРУПП ЕДИНИЧНЫХ БИТ И МАКСИМАЛЬНОЙ ГРУППЫ В БЛОКАХ ДАННЫХ | 2023 |

|

RU2800039C1 |

| УСТРОЙСТВО ДЛЯ ДЕТЕКТИРОВАНИЯ ГРУПП ЕДИНИЧНЫХ БИТ В БЛОКАХ ДВОИЧНОЙ ПОСЛЕДОВАТЕЛЬНОСТИ | 2023 |

|

RU2809743C1 |

| УСТРОЙСТВО ДЛЯ ДЕТЕКТИРОВАНИЯ ЕДИНИЧНЫХ ГРУПП БИТ В БИНАРНОЙ ПОСЛЕДОВАТЕЛЬНОСТИ | 2021 |

|

RU2763859C1 |

| US 7584233 B2, 01.09.2009 | |||

| US 6938061 B1, 30.08.2005 | |||

| WO 2016036602 A1, 10.03.2016. | |||

Авторы

Даты

2024-10-08—Публикация

2024-03-04—Подача