Перекрестная ссылка на родственные заявки

Данная заявка притязает на приоритет предварительной заявки на патент США № 60/941228, поданной 31 мая 2007 года, озаглавленной "ADJUSTABLE INPUT RECEIVER FOR LOW POWER HIGH SPEED INTERFACE", которая полностью содержится в качестве ссылки в данном документе.

Уровень техники

Область техники, к которой относится изобретение

Изобретение относится к области техники интегральных полупроводниковых схем. Более конкретно, изобретение относится к области техники высокоскоростных входных логических приемных устройств, таких как входные приемные устройства на базе комплементарной МОП-структуры (КМОП) или псевдодифференциальные входные приемные устройства.

Описание предшествующего уровня техники

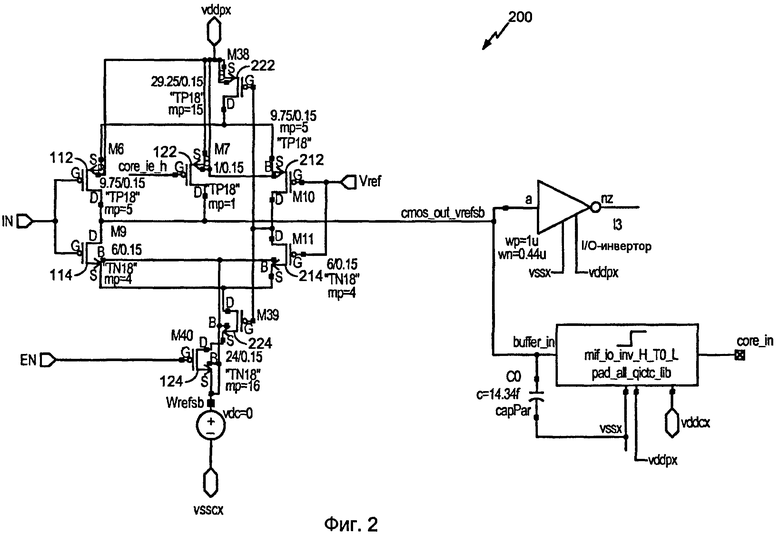

В общем, традиционные входные приемные КМОП-устройства, такие как устройства, которые не поддерживают дополнительное опорное напряжение, Vref, как показано на фиг.1, использующие "толстые" устройства или использующие "тонкие" устройства, оптимизированы под режим ниже 200 МГц для маломощного интерфейса запоминающего устройства, такого как заданный в стандартах External Bus Interface EBI1, EBI2 и т.п. Для работы на более высокой частоте, к примеру, от 200 МГц до 533 МГц, использовались несколько видов несимметричных псевдодифференциальных входных приемных устройств на основе Vref, как показано на фиг.2, с различными значениями Vref, например, при половине от напряжения питания без параллельной оконечной нагрузки или при 70% от напряжения питания с оконечной Vddq-нагрузкой.

Чтобы охватывать частоту в широком диапазоне и поддержку Vref, как, например, требуется для реализации приемного устройства с поддержкой маломощного интерфейса двойной скорости передачи данных (DDR2), простое решение состоит в том, чтобы конфигурировать (настраивать) несколько параллельных входных приемных устройств и включать только одно приемное устройство на основе значения Vref. Этот подход, тем не менее, нежелателен с точки зрения площади и мощности. Дополнительно, реализация с несколькими параллельными приемными устройствами испытывает недостаток в виде ухудшения характеристик, что может быть обусловлено повышением входной емкости, Cin и повышением задержки во входном тракте вследствие дополнительного мультиплексора.

Краткий перечень чертежей

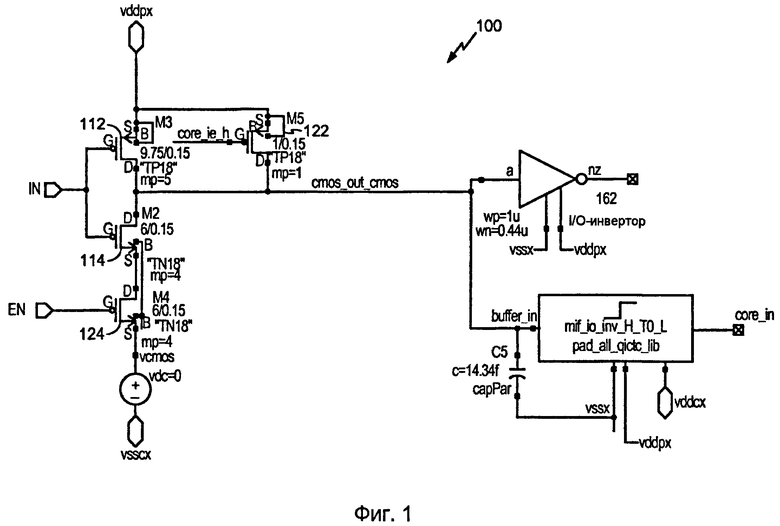

Фиг.1 - это упрощенное схематичное представление примерного варианта осуществления приемного КМОП-устройства без поддержки Vref.

Фиг.2 - это упрощенное схематичное представление примерного варианта осуществления псевдодифференциального приемного устройства с поддержкой Vref.

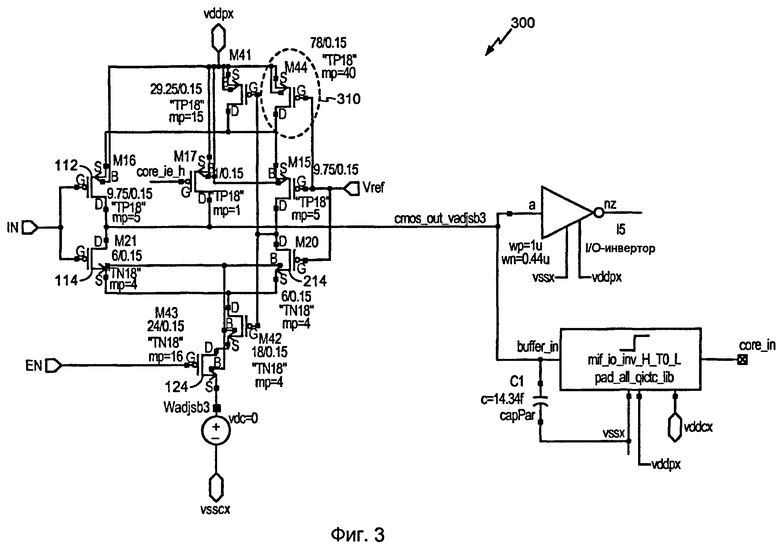

Фиг.3 - это упрощенное схематичное представление примерного варианта осуществления Vref-регулируемого псевдодифференциального приемного устройства с автоматическим смещением.

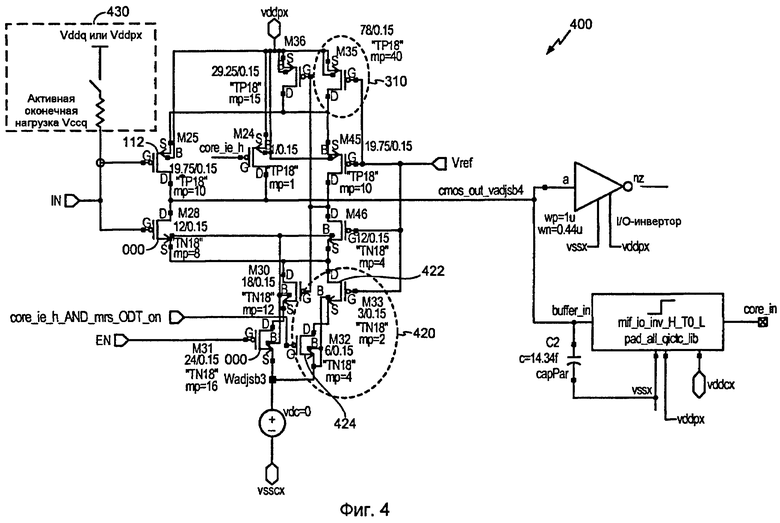

Фиг.4 - это упрощенное схематичное представление примерного варианта осуществления Vref-регулируемого псевдодифференциального приемного устройства с автоматическим смещением.

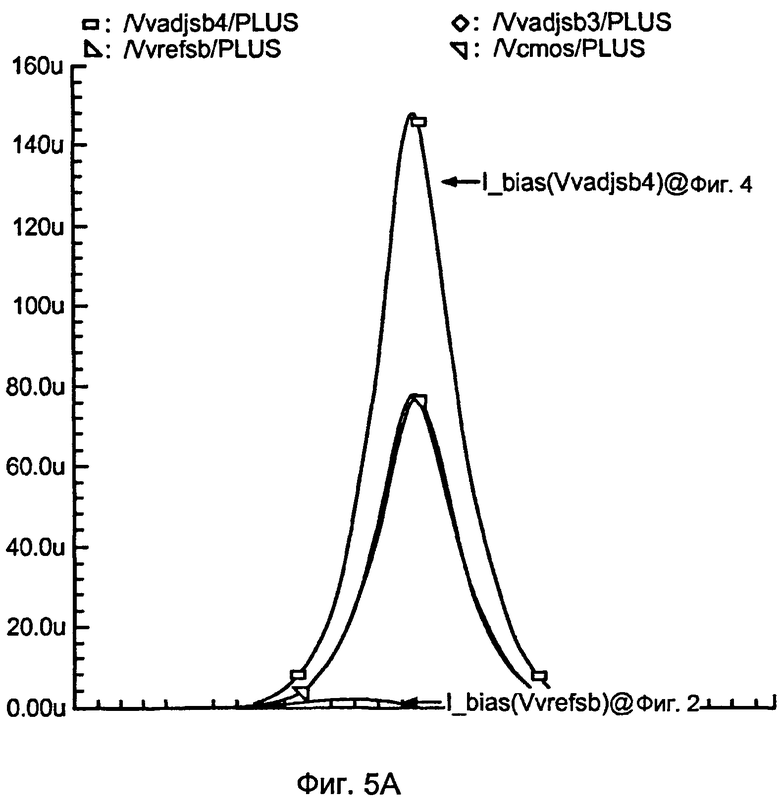

Фиг.5a-5f являются упрощенными диаграммами рабочих характеристик, сравнивающих различные примерные варианты осуществления приемного устройства.

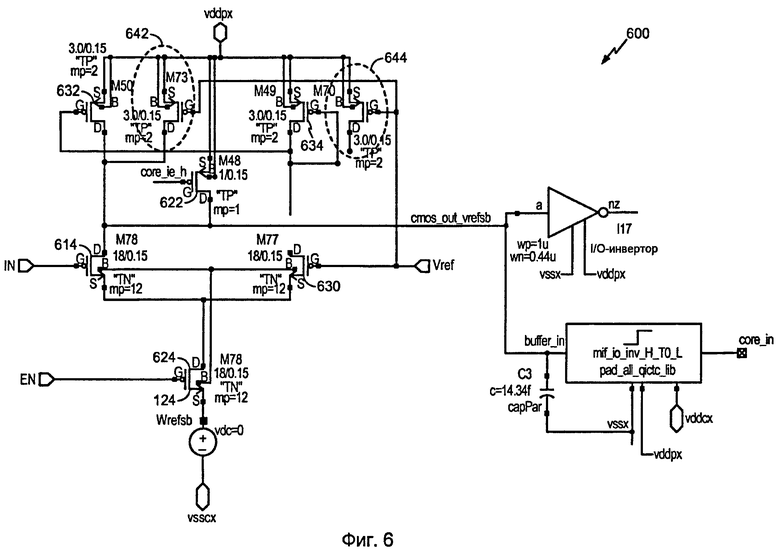

Фиг.6 - это упрощенное схематичное представление примерного варианта осуществления Vref-регулируемого псевдодифференциального приемного n-МОП-устройства с автоматическим смещением.

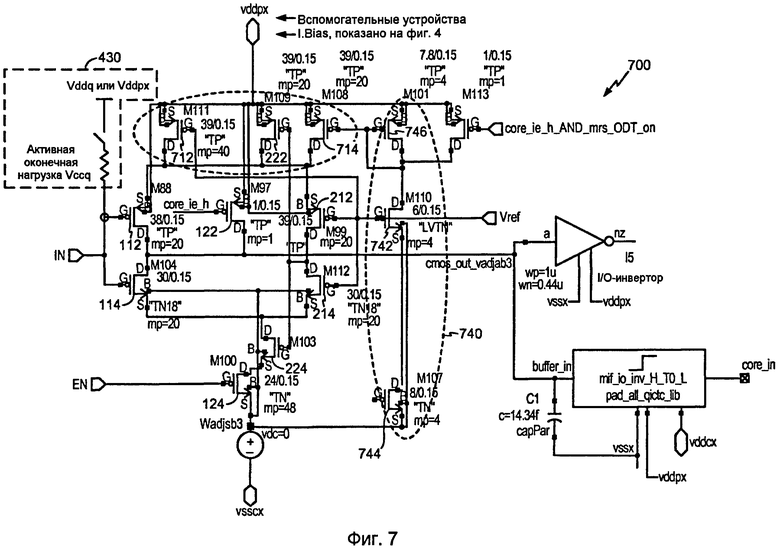

Фиг.7 - это упрощенное схематичное представление примерного варианта осуществления Vref-регулируемого псевдодифференциального приемного устройства с автоматическим смещением.

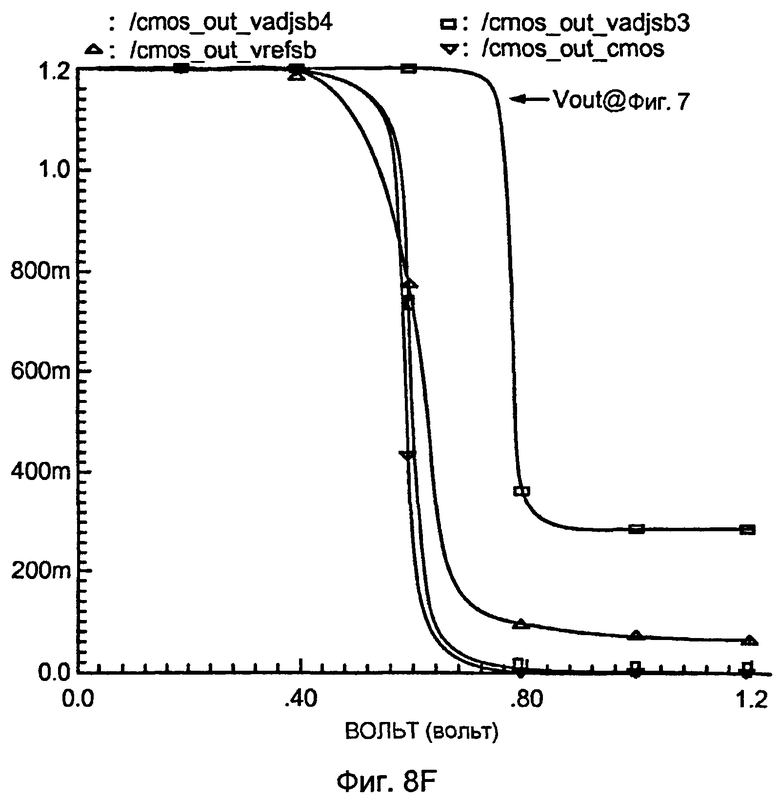

Фиг.8a-8f являются упрощенными диаграммами рабочих характеристик, сравнивающих различные примерные варианты осуществления приемного устройства.

Фиг.9 - это упрощенная блок-схема последовательности операций примерного варианта осуществления способа псевдодифференциального приемного устройства с автоматическим смещением.

Подробное описание изобретения

Слово "примерный" используется в данном документе для того, чтобы обозначать "служащий в качестве примера, отдельного случая или иллюстрации". Любой вариант осуществления, описанный в данном документе как "примерный", не обязательно должен быть истолкован как предпочтительный или преимущественный по сравнению с другими вариантами осуществления.

Изложенное ниже в связи с прилагаемыми чертежами подробное описание предназначено для использования в качестве описания примерных вариантов осуществления настоящего изобретения и не предназначено, чтобы представлять единственные варианты осуществления, которыми изобретение может быть использовано на практике. Термин "примерный", используемый в данном описании, означает "служащий в качестве примера, отдельного случая или иллюстрации" и не обязательно должен истолковываться как предпочтительный или преимущественный в сравнении с другими примерными вариантами осуществления. Подробное описание включает в себя конкретные подробности для целей предоставления полного понимания примерных вариантов осуществления изобретения. Специалистам в данной области техники должно быть очевидным, что примерные варианты осуществления изобретения могут осуществляться на практике без этих конкретных подробностей. В некоторых случаях распространенные структуры и устройства показаны в форме блок-схемы, чтобы исключать затруднения в понимании новизны представленных в данном документе примерных вариантов осуществления.

Желательно иметь только одну схему (конфигурацию) Vref-регулируемого входного приемного устройства с широким частотным диапазоном. Конфигурация (настройка) приемного устройства может быть выполнена с возможностью работать в широком частотном диапазоне и в широком диапазоне значений Vref. Производительность приемного устройства может легко регулироваться за счет изменений, которые незначительно влияют на площадь кристалла и потребляемую мощность.

Фиг.1 - это упрощенное схематичное представление примерного варианта осуществления традиционного приемного КМОП-устройства 100 без Vref. Традиционное приемное КМОП-устройство 100 по фиг.1 может быть реализовано с использованием традиционных толстых устройств или тонких устройств.

Традиционное приемное КМОП-устройство 100 включает в себя традиционную комплементарную FET-пару, выполненную как КМОП-инвертор, который включает в себя p-МОП-FET 112, помещенный поверх n-МОП-FET 114. Исток p-МОП-FET 112 соединяется с Vdd, и сток является общим со стоком n-МОП-FET 114, который служит в качестве выхода КМОП-инвертора. Затвор p-МОП-FET 112 является общим с затвором n-МОП-FET 114 и выступает в качестве входа в приемное КМОП-устройство 100.

Исток n-МОП-FET 114 может соединяться с Vss или необязательно с выводом стока n-МОП-FET 124 с вводом сигнала разрешения. Исток n-МОП-FET 124 с вводом сигнала разрешения соединяется с Vss, и затвор принимает сигнал управления разрешением. Аналогично, p-МОП-FET 122 с вводом сигнала разрешения может быть выполнен с возможностью повышать напряжение на выходе КМОП-инвертора, когда инвертор не разрешен. Исток p-МОП-FET 122 с вводом сигнала разрешения соединяется с Vdd, и сток соединяется с выходом КМОП-инвертора. Затвор p-МОП-FET 122 с вводом сигнала разрешения выполнен с возможностью принимать сигнал управления разрешением.

Традиционное приемное КМОП-устройство 100 по фиг.1 не поддерживает вход Vref. Невозможность поддерживать переменное значение Vref делает традиционное приемное КМОП-устройство 100 менее желательным для работы при более высоких частотах с небольшим перепадом на входе, совмещенным с Vref-уровнем. Значение Vref может считаться номинальным логическим порогом, и логические переходы от низкого уровня к высокому или от высокого уровня к низкому зачастую указываются с точки зрения значения Vref, когда приемное устройство поддерживает Vref. Поддержка внешне управляемого значения Vref может быть желательной для того, чтобы компенсировать или иначе взаимодействовать с шиной или устройством, которое не может работать при точно таком же напряжении питания, что используется посредством приемного КМОП-устройства 100, либо иным образом корректировать эффекты электрической шины или интерфейса. Фактически, некоторые стандарты интерфейса запоминающего устройства явно задают диапазон значений для Vref.

Примерный вариант осуществления псевдодифференциального приемного устройства 200 по фиг.2 включает в себя условия приема значения Vref. Примерный вариант осуществления псевдодифференциального приемного устройства 200 по фиг.2 может быть основан на том же КМОП-инверторе, что описан в примерном варианте осуществления по фиг.1. p-МОП-FET 112 помещается поверх n-МОП-FET 114, и эти два FET совместно используют вывод общих затворов в качестве входа инвертора.

КМОП-пара Vref размещается по существу параллельно КМОП-инвертору. Параллельная конфигурация означает начало параллельного электрического подключения, так что соединения токовых цепей на входе для КМОП-пары Vref и КМОП-инвертора являются общими, как и соединения токовых цепей на выходе.

Значение Vref возбуждает вход в КМОП-пару Vref. Значение Vref типично принимается из внешнего интерфейса в интегральную схему, хотя значение Vref также может быть сформировано внутренним образом для интегральной схемы. Как правило, значение Vref представляет логический порог, уставку или граничное значение отключения. Значение логического порога может регулироваться так, чтобы приспосабливать взаимодействие с различными устройствами, которые могут не работать с напряжением питания, идентичным напряжению для входного приемного устройства. КМОП-пара Vref включает в себя p-МОП-FET 212 с вводом Vref, помещенный поверх n-МОП-FET 214 с вводом Vref. p-МОП-FET 212 с вводом Vref и n-МОП-FET 214 с вводом Vref имеют выводы общих затворов, которые выполнены с возможностью принимать опорное напряжение Vref.

Вывод истока p-МОП-FET 212 с вводом Vref является общим с истоком p-МОП-FET 112 КМОП-инвертора. Выводы общих истоков соединяются со стоком p-МОП-FET 222 с повышением напряжения. Исток p-МОП-FET 222 с повышением напряжения соединяется с Vdd, тогда как затвор соединяется с выводами общих стоков КМОП-пары Vref.

Вывод истока n-МОП-FET 214 с вводом Vref является общим с истоком n-МОП-FET 114 КМОП-инвертора. n-МОП-FET 224 с понижением напряжения имеет сток, подключенный к выводам общих истоков, и имеет исток, подключенный к Vss или необязательно к стоку n-МОП-FET 124 с вводом сигнала разрешения. Затвор n-МОП-FET 224 с понижением напряжения соединяется с выводом общего стока КМОП-пары Vref.

КМОП-пара Vref в комбинации с p-МОП-FET 222 с повышением напряжения и n-МОП-FET 224 с понижением напряжения выполнена с возможностью управлять логическим порогом или граничным значением отключения КМОП-инвертора и управляет током смещения через КМОП-инвертор на основе зависимости входного напряжения от значения Vref. Тем не менее, традиционное псевдодифференциальное приемное устройство 200 на основе Vref не всегда может иметь оптимальное смещение для того, чтобы обеспечивать высокопроизводительную работу в широком диапазоне Vref, в частности, когда Vref находится близко к Vss или Vdd.

Традиционный подход для разрешения диапазона значений Vref состоит в том, чтобы формировать определенное число входных приемных устройств параллельно и выбирать входное приемное устройство на основе рабочего значения Vref. Конфигурирование нескольких входных приемных устройств параллельно и выбор одного из входных приемных устройств на основе значения Vref является неэффективным способом предоставления поддержки для широкого диапазона входных частот и широкого диапазона Vref. Входные приемные КМОП-устройства и способы, раскрытые в данном документе, реализуют более эффективное решение, которое использует реализацию с одним приемным устройством, которая конфигурируема так, чтобы поддерживать широкий диапазон входных частот и широкий диапазон значений Vref.

Фиг.3 - это упрощенное схематичное представление Vref-регулируемого псевдодифференциального входного приемного устройства 300 с автоматическим смещением. Псевдодифференциальное входное приемное устройство 300 с автоматическим смещением включает в себя условия приема значения Vref в КМОП-паре, которая является параллельной с активной логической КМОП-парой приемного КМОП-устройства 300. Тем не менее, в отличие от примерного варианта осуществления псевдодифференциального приемного устройства на основе Vref по фиг.2, псевдодифференциальное приемное устройство 300 с автоматическим смещением дополнительно включает в себя вспомогательный p-МОП-FET 310, альтернативно выполненный как многоярусное вспомогательное p-МОП-устройство с разрешением, которое повышает напряжение на выходе истока p-МОП-FET 302 в активной КМОП-паре. Вспомогательное p-МОП-FET 310 имеет исток, соединенный с Vdd, и сток, соединенный с истоком p-МОП-FET 112 в активной логической КМОП-паре, который также является общим с истоком p-МОП-FET 212 с вводом Vref. Таким образом, псевдодифференциальное входное приемное устройство 300 с автоматическим смещением может быть выполнено по существу идентично примерному варианту осуществления приемного КМОП-устройства по фиг.2, с добавлением вспомогательного p-МОП-FET 310, который может упоминаться в альтернативе как токовый вспомогательный FET или вспомогательный FET Ibias.

Исток вспомогательного p-МОП-FET 310 соединяется с Vdd, а его сток соединяется с истоком p-МОП-FET 112 в логической КМОП-паре. Затвор вспомогательного p-МОП-FET 310 принимает значение Vref. Таким образом, вспомогательный p-МОП-FET 310 эффективно отслеживает линию Vref и предоставляет тракт для тока Ibias для КМОП-инвертора. Добавление вспомогательного p-МОП-FET 310 дает возможность псевдодифференциальному приемному устройству 300 работать по существу как традиционное приемное КМОП-устройство, когда Vref равен нулю или примерно нулю вольт. Кроме того, примерный вариант осуществления приемного КМОП-устройства 300 по фиг.3 демонстрирует производительность, которая выше производительности традиционного приемного КМОП-устройства по фиг.1, поскольку приемное КМОП-устройство 300 по фиг.3 может работать с ненулевыми значениями Vref.

Добавление p-МОП-FET 310 к псевдодифференциальному приемному устройству с разрешением Vref дает возможность псевдодифференциальному приемному устройству 300 работать сопоставимо с псевдодифференциальным приемным устройством с разрешением Vref, таким как примерный вариант осуществления приемного устройства по фиг.2, при условиях, когда Vref составляет приблизительно 0,5 Vdd. Таким образом, конфигурация псевдодифференциального приемного устройства 300 по фиг.3 может работать в диапазоне Vref приблизительно от Vss до 50% Vdd.

Фиг.4 иллюстрирует другой примерный вариант осуществления псевдодифференциального входного приемного устройства 400. Примерный вариант осуществления входного приемного устройства по фиг.4, а также примерные варианты осуществления, проиллюстрированные на других чертежах, могут быть сконфигурированы с помощью толстых устройств, а также тонких устройств. Примерный вариант осуществления псевдодифференциального приемного устройства 400 по фиг.4 выполнен аналогично примерному варианту осуществления псевдодифференциального входного приемного устройства, проиллюстрированному на фиг.3. Псевдодифференциальное входное приемное устройство 400 включает в себя вспомогательный p-МОП-FET 310, как проиллюстрировано в примерном варианте осуществления по фиг.3, а также включает в себя конфигурацию 420 вспомогательного n-МОП-устройства.

Конфигурация 420 вспомогательного n-МОП-устройства дает возможность приемному КМОП-устройству 400 на основе Vref работать с возможностью программирования на токах смещения и граничном значении отключения в диапазоне Vref=(0,5~0,7) Vdd. Таким образом, когда конфигурация 420 вспомогательного n-МОП-устройства используется в комбинации со вспомогательным p-МОП-FET 310, приемное КМОП-устройство 400 может работать в диапазоне со значениями Vref, охватывающими приблизительно от Vss до 70% Vdd.

Конфигурация 420 вспомогательного n-МОП-устройства включает в себя многоярусную конфигурацию из двух n-МОП-FET 422 и 424. Вспомогательный n-МОП-FET 422 реализуется в многоярусной конфигурации с n-МОП-FET 424 с вводом сигнала разрешения. В многоярусной конфигурации исток вспомогательного n-МОП-FET 422 подключается к стоку n-МОП-FET 424 с вводом сигнала разрешения в последовательном соединении, так что электрический ток через вспомогательный n-МОП-FET 422 запрещен, когда n-МОП-FET 424 с вводом сигнала разрешения выключен.

Затвор n-МОП-FET 424 с вводом сигнала разрешения выполнен с возможностью принимать сигнал управления разрешением, такой как интерфейсный сигнал управления разрешением. Затвор вспомогательного n-МОП-FET 422 выполнен с возможностью принимать значение Vref и таким образом выполнен с возможностью дополнительно регулировать ток через КМОП-инвертор частично на основе значения напряжения Vref.

Псевдодифференциальное входное приемное устройство 400 также может включать в себя активную входную нагрузку 430. Производительность приемного КМОП-устройства 400 может регулироваться на основе отношения полного сопротивления предконечного задающего устройства к параллельному оконечному полному сопротивлению включения/выключения кристалла. Хотя вход примерного варианта осуществления приемного устройства 400 по фиг.4 проиллюстрирован как имеющий активную оконечную нагрузку 430 Vccq на входе в приемное КМОП-устройство 400, такая оконечная нагрузка не всегда требуется, и оконечная нагрузка может быть опущена в других конфигурациях.

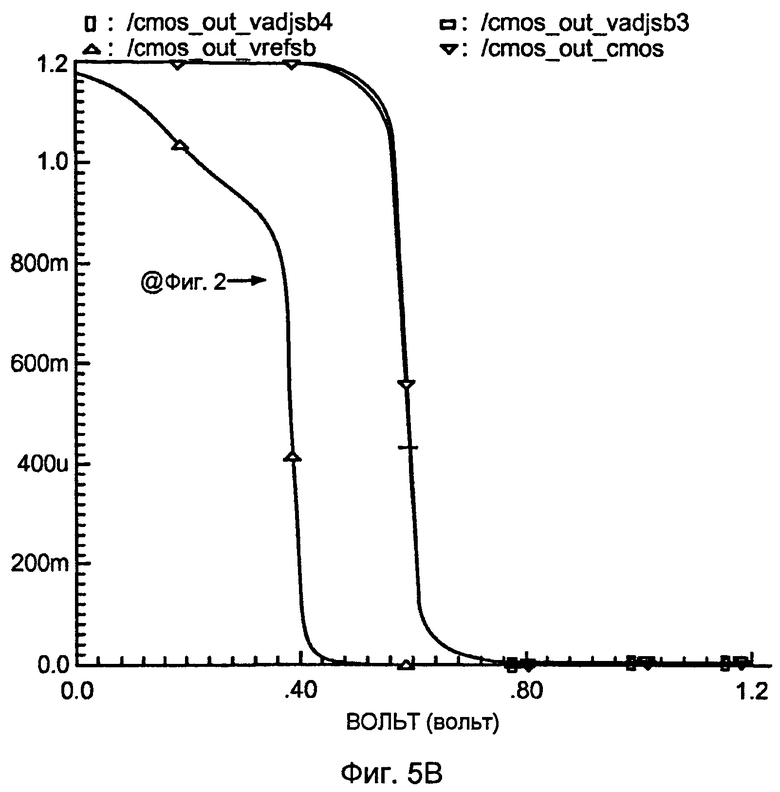

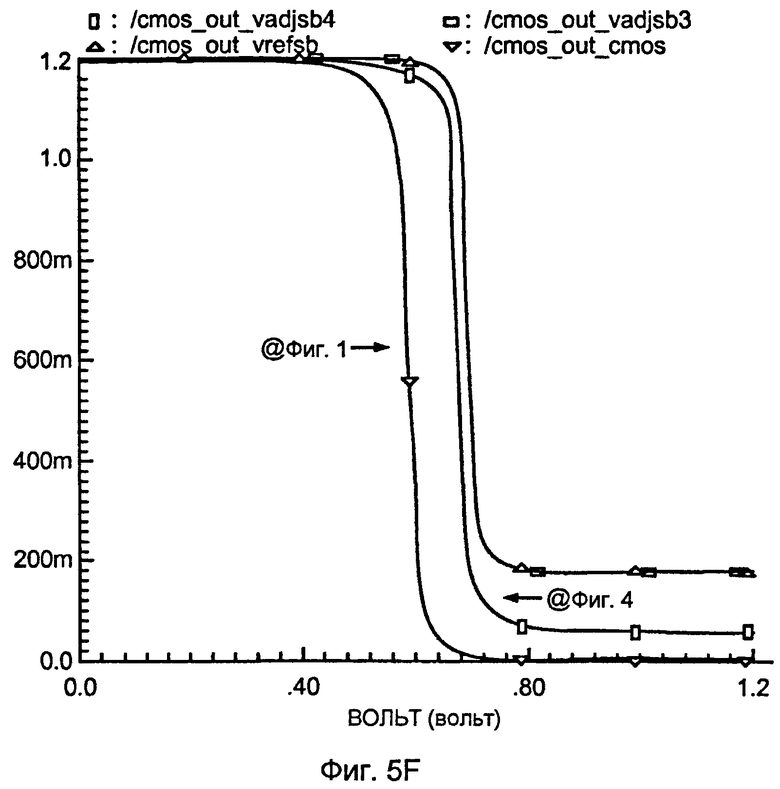

Фиг.5a-5f являются упрощенными схемами рабочих характеристик, сравнивающих различные примерные варианты осуществления приемного устройства. Фиг.5a иллюстрирует токи смещения относительно Vin для примерных вариантов осуществления приемного устройства, проиллюстрированных на фиг.1-4, когда Vref задан равным 0 В. Поскольку значение Vref задано равным 0 В, ток смещения в примерном варианте осуществления по фиг.2 существенно ограничен.

Фиг.5b иллюстрирует соответствующую передаточную функцию по напряжению Vout относительно Vin для примерных вариантов осуществления приемного устройства с Vref, заданным равным 0 В. Как можно видеть из передаточной функции по напряжению по фиг.5b, примерный вариант осуществления традиционного псевдодифференциального приемного устройства 200 с разрешением Vref по фиг.2 работает плохо, когда значение Vref близко к нулю.

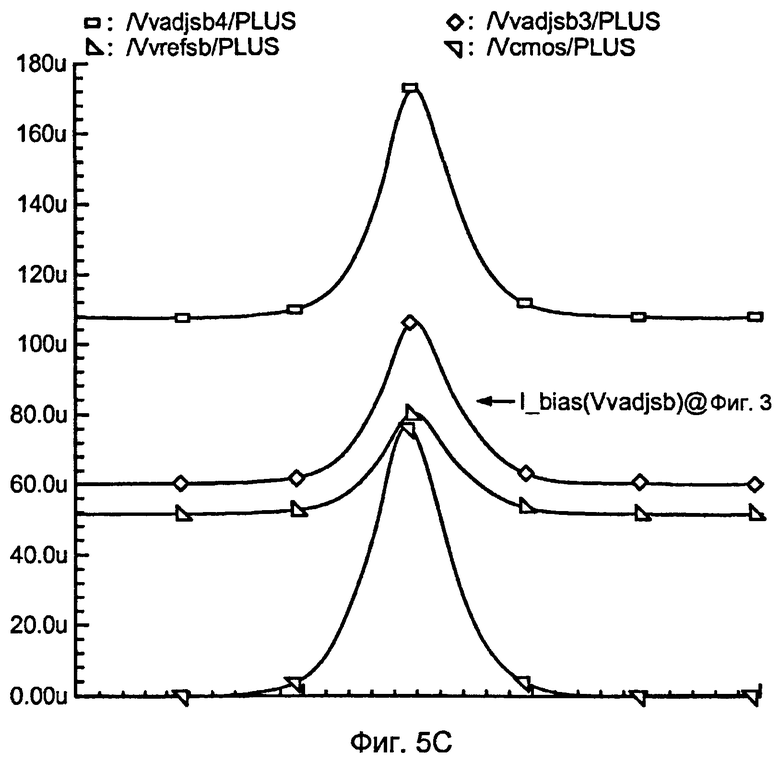

Фиг.5c иллюстрирует токи смещения относительно Vin для примерных вариантов осуществления приемного устройства, проиллюстрированных на фиг.1-4, когда Vref задан равным приблизительно половине значения Vdd для примерных вариантов осуществления, поддерживающих значение Vref. Как можно видеть, добавление вспомогательных FET увеличивает величину тока, который является током смещения установившегося режима, протекающим через входное приемное устройство.

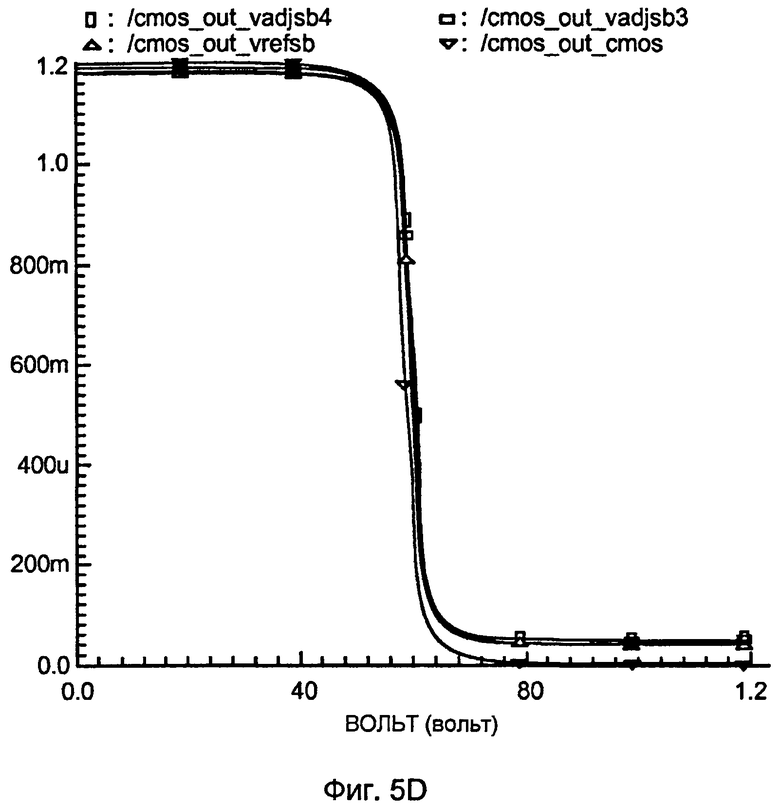

Фиг.5d иллюстрирует соответствующую передаточную функцию по напряжению Vout относительно Vin для примерных вариантов осуществления приемного устройства с Vref=(0,5) Vdd. Приемные устройства, формирующие основу рабочих кривых по фиг.5a-5f, используют Vdd 1,2 В. Таким образом, значение Vref на фиг.5b и 5c соответствует приблизительно 0,6 В. Поскольку этот логический порог представляет по существу стандартную конфигурацию, каждый из примерных вариантов осуществления работает удовлетворительно, как и можно предположить.

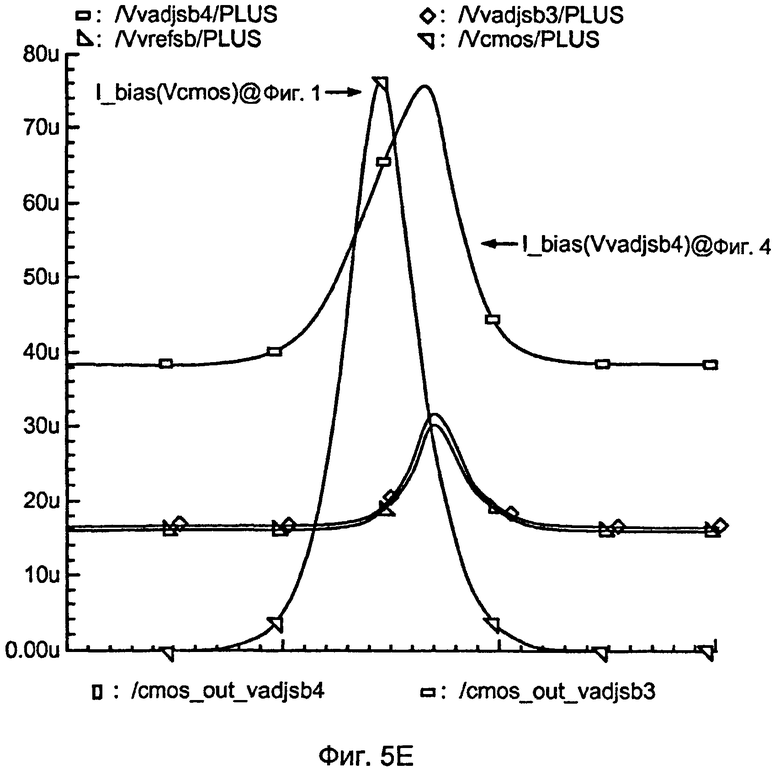

Фиг.5e иллюстрирует токи смещения относительно Vin для примерных вариантов осуществления приемного устройства, проиллюстрированных на фиг.1-4, когда Vref задано равным больше половины значения Vdd для примерных вариантов осуществления, поддерживающих значение Vref.

Фиг.5f иллюстрирует соответствующую передаточную функцию по напряжению Vout относительно Vin для примерных вариантов осуществления приемного устройства с Vref=0,7 В, соответствующим приблизительно 0,58 Vdd. Этот уровень Vref может превышать традиционно поддерживаемый посредством традиционного входного приемного устройства, даже того, которое допускает вход Vref.

Как можно видеть посредством рабочих характеристик по фиг.5e и 5f, примерный вариант осуществления приемного КМОП-устройства по фиг.1, которое не поддерживает значение Vref, не способен предоставлять возможность регулирования уставки или логического порога передаточной функции по напряжению. Примерные варианты осуществления входного приемного КМОП-устройства по фиг.2-4 тщательно отслеживают увеличение значения Vref. Тем не менее, как можно видеть на кривых передаточной функции по напряжению по фиг.5f, примерные варианты осуществления псевдодифференциального входного приемного устройства по фиг.2 и 3 могут поддерживать повышенное значение Vref, но не понижать напряжение на выходе по существу до земли при выводе низкого логического состояния. Входное приемное КМОП-устройство по фиг.4, имеющее конфигурацию вспомогательного n-МОП, дает возможность понижения выходного напряжения ближе к нулю В, когда уровень входа высокий.

Усовершенствования Vref не ограничены тем, чтобы использовать с псевдодифференциальным входным приемным устройством, а могут быть применимыми к другим входным приемным устройствам на основе других конфигураций. Фиг.6 - это упрощенное схематичное представление примерного варианта осуществления Vref-регулируемого приемного n-МОП-устройства 600.

Первый n-МОП-FET 614 выполнен как логический элемент. Затвор первого n-МОП-FET 614 выполнен с возможностью принимать входное напряжение. Исток первого n-МОП-FET 614 соединяется со стоком n-МОП-FET 624 с вводом сигнала разрешения. Исток n-МОП-FET 624 с вводом сигнала разрешения соединяется с Vss или землей, а затвор n-МОП-FET 624 с вводом сигнала разрешения выполнен с возможностью принимать активный высокий уровень сигнала разрешения.

Сток первого n-МОП-FET 614 представляет логику, выводимую из входного приемного устройства 600. Сток первого n-МОП-FET 614 соединяется со стоком р-МОП-FET 622 с вводом сигнала разрешения, который выполнен с возможностью повышать выходное напряжение, когда входное приемное устройство не разрешено. Исток р-МОП-FET 622 с вводом сигнала разрешения соединяется с Vdd, тогда как его затвор принимает активный высокий уровень сигнала разрешения.

Конфигурация устройств, реализованных так, чтобы поддерживать вход Vref, включает в себя второй n-МОП-FET 630, выполненный как n-МОП-FET с вводом Vref. Затвор второго n-МОП-FET 630 принимает сигнал Vref, тогда как исток второго n-МОП-FET 630 является общим с истоком первого n-МОП-FET 614. Сток второго n-МОП-FET 630 соединяется с выходами затвора двух отдельных FET с повышением напряжения.

Первый р-МОП-FET 632 с повышением напряжения имеет исток, соединенный с Vdd, затвор, соединенный со стоком второго n-МОП-FET 630, и сток, соединенный со стоком первого n-МОП-FET 614. Второй р-МОП-FET 634 с повышением напряжения имеет исток, соединенный с Vdd, и выходы затвора и стока, соединенные со стоком второго n-МОП-FET 630.

Входное приемное устройство 600 включает в себя конфигурацию вспомогательных FET, включающую в себя два вспомогательных FET 642 и 644. Вспомогательные FET 642 и 644 дают возможность входному приемному устройству работать в более широком диапазоне значений Vref, включая Vref при нуле или около нуля В.

Первый вспомогательный р-МОП-FET 642 повышает напряжение на выходе логического n-МОП-FET 614, который имеет затвор, выполненный с возможностью принимать входной сигнал. Затвор первого вспомогательного р-МОП-FET 644 соединяется с Vref. Исток первого вспомогательного р-МОП-FET 642 соединяется с Vdd, тогда как сток первого вспомогательного р-МОП-FET 642 соединяется со стоком логического n-МОП-FET 614.

Второй вспомогательный р-МОП-FET повышает напряжение на выходе Vref или второго n-МОП-FET 630, который имеет затвор, управляемый посредством значения Vref. Затвор второго вспомогательного р-МОП-FET 644 также соединяется с Vref. Исток второго вспомогательного р-МОП-FET 644 соединяется с Vdd, тогда как сток второго вспомогательного р-МОП-FET 644 соединяется со стоком n-МОП-FET 630 Vref.

Вспомогательные FET работают по существу идентично тому, как когда выполнены с возможностью поддерживать логический КМОП-элемент. Конфигурация вспомогательного р-МОП-FET выполнена с возможностью подавать ток смещения в логический элемент n-МОП даже при условиях, когда значение Vref является низким или около 0 В.

Фиг.7 - это упрощенное схематичное представление примерного варианта осуществления Vref-регулируемого приемного КМОП-устройства 700 с автоматическим смещением. Конфигурация приемного КМОП-устройства 700 по фиг.7 аналогична конфигурации приемного КМОП-устройства по фиг.4. Тем не менее, псевдодифференциальное приемное устройство 700 по фиг.7 включает в себя детектор 740 уровня Vref, вместо просто конфигурации вспомогательного n-МОП-FET, как в примерном варианте осуществления псевдодифференциального приемного устройства по фиг.4.

Псевдодифференциальное входное приемное устройство 700 по фиг.7 основано на приемном КМОП-устройстве по фиг.2. p-МОП-FET 112 помещается поверх n-МОП-FET 114, и эти два FET совместно используют вывод общего затвора в качестве входа инвертора.

КМОП-пара Vref размещается по существу параллельно КМОП-инвертору. КМОП-пара Vref включает в себя p-МОП-FET 212 с вводом Vref, помещенный поверх n-МОП-FET 214 с вводом Vref. p-МОП-FET 212 с вводом Vref и n-МОП-FET 214 с вводом Vref имеют выводы общих затворов, которые выполнены с возможностью принимать опорное напряжение Vref.

Вывод истока p-МОП-FET 212 с вводом Vref является общим с истоком p-МОП-FET 112 КМОП-инвертора. Выводы общих истоков соединяются со стоком p-МОП-FET 222 с повышением напряжения. Исток p-МОП-FET 222 с повышением напряжения соединяется с Vdd, тогда как затвор соединяется с выводами общих стоков КМОП-пары Vref.

Вывод истока n-МОП-FET 214 с вводом Vref является общим с истоком n-МОП-FET 114 КМОП-инвертора. n-МОП-FET 224 с понижением напряжения имеет сток, подключенный к выводам общих истоков, и имеет исток, подключенный к Vss или необязательно к стоку n-МОП-FET 124 с вводом сигнала разрешения. Затвор n-МОП-FET 224 с понижением напряжения соединяется с выводом общего стока КМОП-пары Vref.

Псевдодифференциальное приемное устройство 700 включает в себя множество вспомогательных р-МОП-FET 712 и 714. Первый вспомогательный р-МОП-FET 712 имеет затвор, соединенный с Vref, тогда как второй вспомогательный р-МОП-FET 714 имеет затвор, соединенный с сигналом от детектора 740 уровня Vref. Исток первого вспомогательного р-МОП-FET 712 соединяется с Vdd, тогда как сток первого вспомогательного р-МОП-FET 712 соединяется с выводами общих истоков логического КМОП-элемента и КМОП-пары Vref.

Исток второго вспомогательного р-МОП-FET 722 соединяется с Vdd. Сток второго вспомогательного р-МОП-FET 722 соединяется с выводами общих истоков логического КМОП-элемента и КМОП-пары Vref.

Детектор 740 уровня Vref включает в себя n-МОП-FET 742 в многоярусной конфигурации с n-МОП-FET 744 с вводом сигнала разрешения. Затвор n-МОП-FET 742 выполнен с возможностью принимать значение Vref. Исток n-МОП-FET 742 соединяется со стоком n-МОП-FET 744 с вводом сигнала разрешения. Затвор n-МОП-FET 744 с вводом сигнала разрешения выполнен с возможностью принимать сигнал разрешения, тогда как исток n-МОП-FET 744 с вводом сигнала разрешения соединяется с Vss.

Сток n-МОП-FET 742 соединяется с p-МОП-FET 746 с повышением напряжения, имеющим исток, соединенный с Vdd. Затвор p-МОП-FET 746 с повышением напряжения соединяется со стоком n-МОП-FET 742. Сток n-МОП-FET 742 также соединяется с затвором второго вспомогательного p-МОП-FET 714.

Детектор 740 уровня Vref варианта осуществления примерного псевдодифференциального приемного устройства 700 по фиг.7 предоставляет возможность приемному КМОП-устройству работать более эффективно в широком диапазоне значений Vref, чем конфигурация псевдодифференциального приемного устройства по фиг.4. Детектор 740 уровня Vref сохраняет эффективность FET вспомогательного устройства смещения по всему диапазону Vref, чтобы предоставлять возможность псевдодифференциальному приемному устройству 700 по фиг.7 работать в диапазоне Vref по существу от Vss до 72% Vdd, который соответствует приблизительно 0-0,864 В для значения Vdd в 1,2 В.

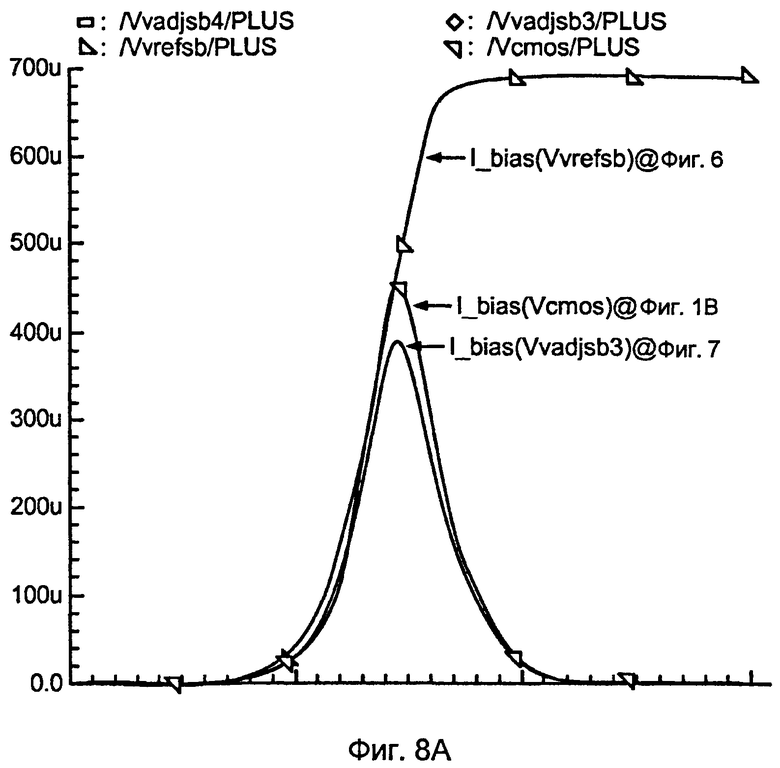

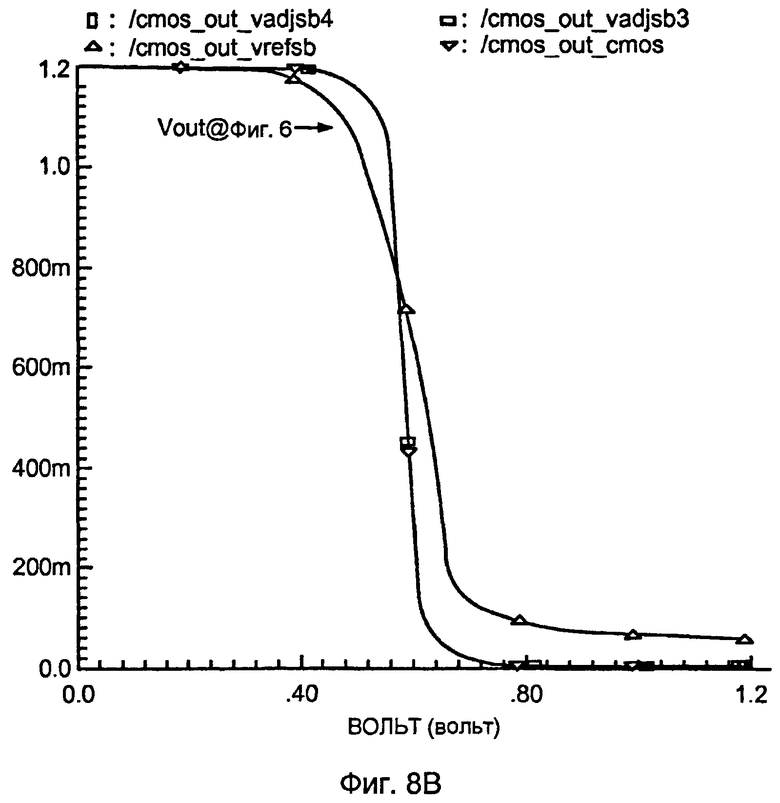

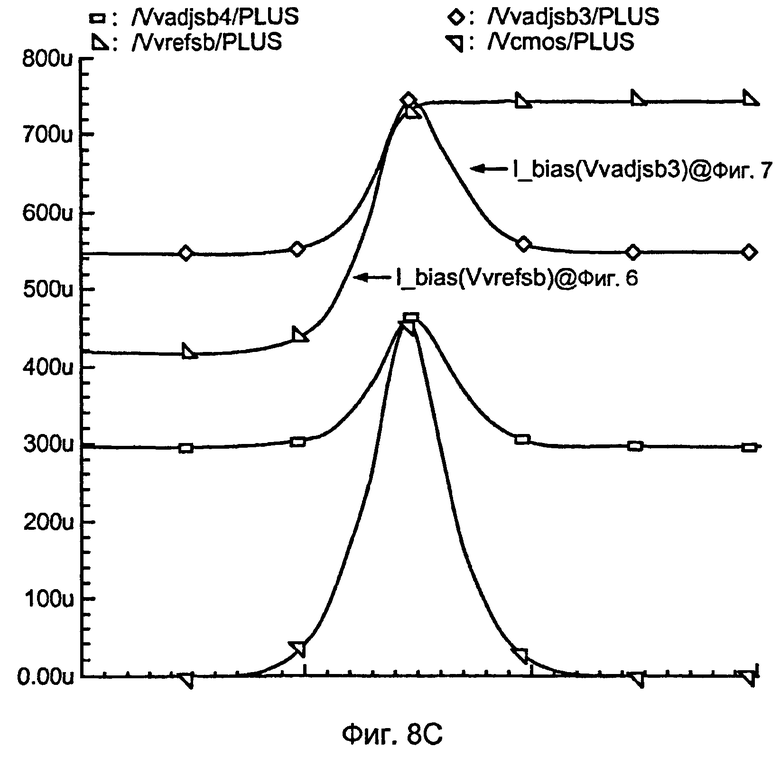

Фиг.8a-8f являются упрощенными схемами рабочих характеристик, сравнивающих различные примерные варианты осуществления приемного устройства. Фиг.8a и 8b иллюстрируют, соответственно, ток смещения относительно Vin и передаточную функцию по напряжению Vout относительно Vin для примерных вариантов осуществления входного приемного устройства по фиг.1, 4, 6 и 7, когда Vref задан равным 0 В. Как можно видеть из фиг.8a, примерный вариант осуществления приемного n-МОП-устройства продолжает работать после того, как n-МОП-FET смещается во включенное состояние.

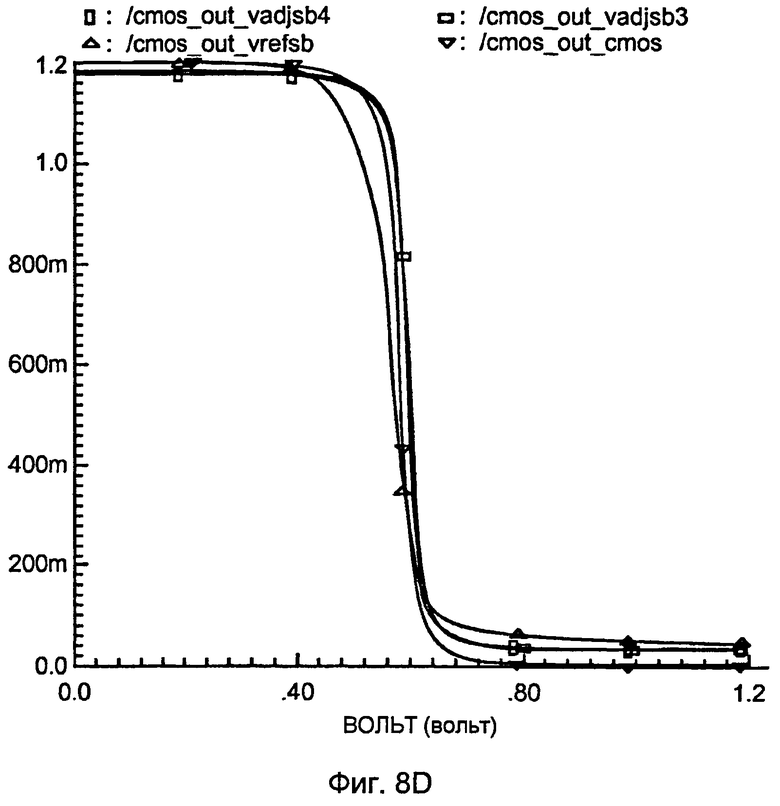

Фиг.8c и 8d иллюстрируют, соответственно, ток смещения относительно Vin и передаточную функцию по напряжению Vout относительно Vin для примерных вариантов осуществления входного приемного устройства по фиг.1, 4, 6 и 7, когда Vref задан равным приблизительно половине напряжения Vdd, которое составляет приблизительно 0,6 В для Vdd в 1,2 В. Примерный вариант осуществления приемного КМОП-устройства по фиг.1 не допускает значение Vref, и таким образом его производительность остается такой же, как на фиг.8a и 8b.

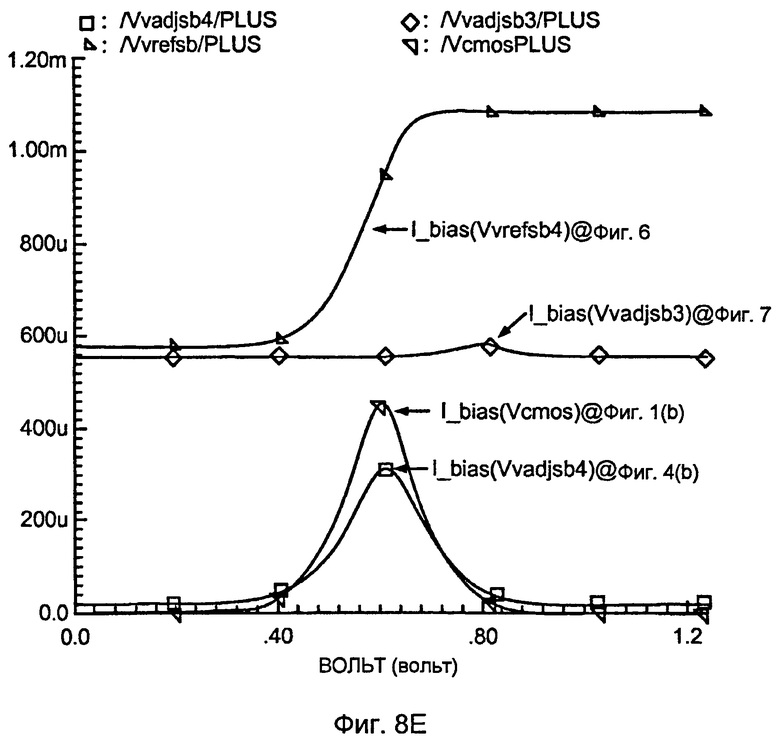

Фиг.8e и 8f иллюстрируют, соответственно, ток смещения относительно Vin и передаточную функцию по напряжению Vout относительно Vin для примерных вариантов осуществления входного приемного устройства по фиг.1, 4, 6 и 7, когда Vref задан равным значению больше половины напряжения Vdd. В рабочих характеристиках по фиг.8e и 8f, значение Vref задано равным приблизительно 0,8 В.

Как можно видеть из рабочих характеристик по фиг.8f, только приемное КМОП-устройство с обнаружением по Vref по фиг.7 может тщательно отслеживать высокий уровень Vref в 0,8 В при сохранении допустимого уровня тока.

Каждый из примерных вариантов осуществления входного приемного устройства по фиг.3-4 и фиг.6-7 может быть использован в качестве входного приемного устройства для интерфейса интегральной схемы или модуля. Например, каждый адресный вход или вход данных в модуль запоминающего устройства или в интегральную схему запоминающего устройства может быть выполнен с входным приемным устройством, как описано в данном документе, чтобы предоставлять возможность работы в широком диапазоне значений Vref и частоты.

Фиг.9 - это упрощенная блок-схема последовательности операций примерного варианта осуществления способа 900 конфигурирования приемного КМОП-устройства с автоматическим смещением. Способ 900 может осуществляться, например, при изготовлении или проектировании интегральной схемы, имеющей входное приемное устройство, описанное в данном документе, или при конфигурировании модуля, имеющего входное приемное устройство, описанное в данном документе.

Способ начинается на этапе 910, где проектировщик конфигурирует логическое устройство. Обычно, проектировщик должен конфигурировать логический КМОП-инвертор, который является основой для многих логических устройств. Тем не менее, способы и примерные варианты осуществления входного приемного устройства не ограничены конфигурациями КМОП, и проектировщик может конфигурировать, например, n-МОП-инвертор.

Проектировщик переходит к этапу 920 и конфигурирует логические устройства Vref, чтобы обеспечивать поддержку изменения уровня Vref. Как описано выше, уровень Vref может задаваться внешне относительно интегральной схемы.

Логическое устройство или устройства Vref включают в себя устройство Vref, размещенное по существу параллельно логическому устройству. В примерном варианте осуществления, КМОП-пара Vref размещается по существу параллельно КМОП-инвертору, который является логическим КМОП-элементом.

Логические устройства Vref также включают в себя FET с повышением напряжения, такой как р-МОП-FET с повышением напряжения, который имеет затвор, управляемый посредством вывода общего стока КМОП-пары Vref. Логические устройства Vref также включают в себя n-МОП-FET с понижением напряжения, который имеет затвор, управляемый посредством вывода общего стока КМОП-пары Vref. FET с понижением напряжения и с повышением напряжения управляют величиной тока, который протекает через логический КМОП-элемент.

Проектировщик переходит к этапу 924 и необязательно конфигурирует одно или более разрешающих устройств. Разрешающие устройства разрешают перевод входного приемного устройства в неактивный высокий уровень полного сопротивления или согласованное состояние. Разрешающие устройства также могут быть выполнены с возможностью предоставлять постоянное логическое состояние на выходе, чтобы предоставлять стабильный логический выход, а не "плавать" к неопределенному значению, когда не разрешены. Хотя примерные варианты осуществления, проиллюстрированные в данном документе, реализуют активный высокий уровень сигнала разрешения, разрешающие устройства могут быть реализованы с возможностью работать с использованием активного высокого уровня или активного низкого уровня сигнала разрешения.

После конфигурирования разрешающих устройств, если таковые имеются, проектировщик переходит к этапу 930 и конфигурирует одно или более вспомогательных устройств. Как показано в примерных вариантах осуществления по фиг.3-4 и 6-7, вспомогательные устройства могут включать в себя одно или более вспомогательных р-МОП-устройств, а также одно или более вспомогательных n-МОП-устройств.

Каждое вспомогательное p-МОП-устройство может быть размещено по существу параллельно p-МОП-FET с повышением напряжения и может иметь затвор, управляемый посредством значения Vref, и может быть выполнено с возможностью повышать напряжение логического выхода. Каждое вспомогательное n-МОП-устройство может быть размещено по существу параллельно n-МОП-FET с понижением напряжения и может иметь затвор, соединенный со значением Vref.

Проектировщик переходит к этапу 940 и необязательно конфигурирует детектор Vref, который также может работать как усилитель тока смещения. Как проиллюстрировано в примерном варианте осуществления по фиг.7, детектор Vref может включать в себя затвор n-МОП, управляемый посредством значения Vref. Сток затвора n-МОП соединяется с p-МОП-FET с повышением напряжения. Сток затвора n-МОП также соединяется с затвором вспомогательного p-МОП-FET, который отличается от других вспомогательных p-МОП-FET, которые могут управляться посредством значения Vref.

Использование вспомогательных FET дает возможность входному приемному устройству работать в более широком диапазоне значений Vref. Вспомогательный p-МОП-FET с повышением напряжения дает возможность току протекать в логическом устройстве, когда значение Vref является низким, например, когда он около 0 В или равно 0 В. Вспомогательные FET с понижением напряжения помогают в понижении напряжения низкого логического выходного уровня, когда значение Vref превышает используемое традиционно.

Устройства и способы для реализации входного приемного устройства, которое допускает работу в большом диапазоне значений Vref и в широком диапазоне частот, описаны в данном документе. Входное приемное устройство с разрешением Vref и широким диапазоном дает возможность использования одного входного приемного устройства в отличие от традиционных технологий наличия нескольких параллельных конфигураций входных приемных устройств, каждая из которых оптимизирована для конкретного диапазона Vref и рабочей частоты.

Специалисты в данной области техники должны понимать, что информация и сигналы могут быть представлены с помощью любой из множества различных технологий. Например, данные, инструкции, команды, информация, сигналы, биты, символы и символы шумоподобной последовательности, которые могут приводиться в качестве примера по всему описанию выше, могут быть представлены посредством напряжений, токов, электромагнитных волн, магнитных полей или частиц, оптических полей или частиц либо любой комбинации вышеозначенного.

Специалисты в данной области техники дополнительно должны принимать во внимание, что различные иллюстративные логические блоки, модули, схемы и этапы алгоритма, описанные в связи с раскрытыми в данном документе вариантами осуществления, могут быть реализованы как электронные аппаратные средства, компьютерное программное обеспечение либо комбинации означенного. Чтобы понятно проиллюстрировать эту взаимозаменяемость аппаратных средств и программного обеспечения, различные иллюстративные компоненты, блоки, модули, схемы и этапы описаны выше, в общем, на основе их функциональности. Реализована эта функциональность в качестве аппаратных средств или программного обеспечения, зависит от конкретного варианта применения и структурных ограничений, накладываемых на систему в целом. Высококвалифицированные специалисты могут реализовывать описанную функциональность различными способами для каждого конкретного варианта применения, но такие решения по реализации не должны быть интерпретированы как вызывающие отступление от объема примерных вариантов осуществления изобретения.

Различные иллюстративные логические блоки, модули и схемы, описанные в связи с раскрытыми в данном документе вариантами осуществления, могут быть реализованы или выполнены с помощью процессора общего назначения, процессора цифровых сигналов (DSP), специализированной интегральной схемы (ASIC), программируемой пользователем вентильной матрицы (FPGA) или другого программируемого логического устройства, дискретного логического элемента или транзисторной логики, дискретных компонентов аппаратных средств либо любой комбинации вышеозначенного, предназначенной для того, чтобы выполнять описанные в данном документе функции. Процессором общего назначения может быть микропроцессор, но в альтернативном варианте, процессором может быть любой традиционный процессор, контроллер, микроконтроллер или конечный автомат. Процессор также может быть реализован как комбинация вычислительных устройств, к примеру, комбинация DSP и микропроцессора, множество микропроцессоров, один или более микропроцессоров вместе с ядром DSP либо любая другая подобная конфигурация.

Этапы способа или алгоритма, описанные в связи с раскрытыми в данном документе вариантами осуществления, могут быть реализованы непосредственно в аппаратных средствах, в программном модуле, приводимом в исполнение посредством процессора, или в их комбинации. Программный модуль может постоянно размещаться в оперативном запоминающем устройстве (RAM), флэш-памяти, постоянном запоминающем устройстве (ROM), электрически программируемом ROM (EPROM), электрически стираемом программируемом ROM (EEPROM), в регистрах, на жестком диске, сменном диске, CD-ROM или любой другой форме носителя хранения данных, известной в данной области техники. Типичный носитель хранения данных соединяется с процессором так, что процессор может считывать информацию и записывать информацию на носитель хранения данных. В альтернативном варианте, носитель хранения данных может быть встроен в процессор. Процессор и носитель хранения данных могут постоянно размещаться в ASIC. ASIC может постоянно размещаться в пользовательском терминале. В альтернативном варианте, процессор и носитель хранения данных могут постоянно размещаться как дискретные компоненты в пользовательском терминале.

В одном или более примерных вариантах осуществления, описанные функции могут быть реализованы в аппаратных средствах, программном обеспечении, микропрограммном обеспечении или в любой комбинации вышеозначенного. Если реализованы в программном обеспечении, функции могут быть сохранены или переданы как одна или более инструкций или код на машиночитаемом носителе. Машиночитаемые носители включают в себя как компьютерные носители хранения данных, так и среду связи, включающую в себя любую передающую среду, которая упрощает перемещение компьютерной программы из одного места в другое. Носителями хранения могут быть любые доступные носители, к которым можно осуществлять доступ посредством компьютера. В качестве примера, но не ограничения, эти машиночитаемые носители могут содержать RAM, ROM, EEPROM, CD-ROM или другое устройство хранения на оптических дисках, устройство хранения на магнитных дисках или другие магнитные устройства хранения, либо любой другой носитель, который может быть использован для того, чтобы переносить или сохранять требуемый программный код в форме инструкций или структур данных, и к которому можно осуществлять доступ посредством компьютера. Также, любое подключение корректно называть машиночитаемым носителем. Например, если программное обеспечение передается с веб-узла, сервера или другого удаленного источника с помощью коаксиального кабеля, оптоволоконного кабеля, "витой пары", цифровой абонентской линии (DSL) или беспроводных технологий, таких как инфракрасные, радиопередающие и микроволновые среды, то коаксиальный кабель, оптоволоконный кабель, "витая пара", DSL или беспроводные технологии, такие как инфракрасные, радиопередающие и микроволновые среды, включены в определение носителя. Диск (disk) и диск (disc) при использовании в данном документе включают в себя компакт-диск (CD), лазерный диск, оптический диск, универсальный цифровой диск (DVD), гибкий диск и диск Blu-Ray, при этом диски (disk) обычно воспроизводят данные магнитно, тогда как диски (disc) обычно воспроизводят данные оптически с помощью лазеров. Комбинации вышеперечисленного также следует включать в число машиночитаемых носителей.

Предшествующее описание раскрытых примерных вариантов осуществления предоставлено, чтобы давать возможность любому специалисту в данной области техники создавать или использовать настоящее изобретение. Различные модификации в этих примерных вариантах осуществления должны быть очевидными для специалистов в данной области техники, а описанные в данном документе общие принципы могут быть применены к другим вариантам осуществления без отступления от сущности и объема изобретения. Таким образом, настоящее изобретение не имеет намерения быть ограниченным показанными в данном документе вариантами осуществления, а должно удовлетворять самому широкому объему, согласованному с принципами и новыми признаками, раскрытыми в данном документе.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО КОРРЕКЦИИ СКВАЖНОСТИ ВХОДНОГО СИГНАЛА | 2011 |

|

RU2467473C1 |

| АССОЦИАТИВНАЯ ПАМЯТЬ СО СМЕШАННЫМ ПАРАЛЛЕЛЬНО-ПОСЛЕДОВАТЕЛЬНЫМ ПОИСКОМ | 2006 |

|

RU2406167C2 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО НА ОСНОВЕ ИЗМЕНЕНИЯ СОПРОТИВЛЕНИЯ | 2014 |

|

RU2620502C2 |

| ИСТОЧНИК ОПОРНОГО НАПРЯЖЕНИЯ | 2021 |

|

RU2767980C1 |

| ОБНАРУЖЕНИЕ ЗАРЯДА ИЛИ ЧАСТИЦЫ | 2003 |

|

RU2339973C2 |

| ТРОИЧНЫЙ К-МОП-С ЛОГИЧЕСКИЙ ЭЛЕМЕНТ "ИЛИ-НЕ" | 2011 |

|

RU2468510C1 |

| Интегральный электронный КМОП синапс | 2023 |

|

RU2808951C1 |

| ТРОИЧНЫЙ К-МОП-С ЛОГИЧЕСКИЙ ЭЛЕМЕНТ "НЕ" | 2011 |

|

RU2481701C2 |

| КОЛЬЦЕВОЙ КМОП ГЕНЕРАТОР, УПРАВЛЯЕМЫЙ НАПРЯЖЕНИЕМ | 2011 |

|

RU2455755C1 |

| КМОП ЛОГИЧЕСКИЙ ВЕНТИЛЬ ИСКЛЮЧАЮЩЕЕ-ИЛИ | 2023 |

|

RU2814896C1 |

Изобретение относится к интегральным схемам и может быть использовано для высокоскоростных входных приемных устройств. Технический результат заключается в обеспечении возможности поддерживать широкий диапазон опорного напряжения Vref, причем описанные варианты осуществления изобретения эффективны с точки зрения площади, мощности и производительности. Приемное устройство может быть сконфигурировано со вспомогательным р-МОП-FET с мониторингом Vref или разрешенным многоярусным вспомогательным р-МОП-FET, чтобы давать возможность приемному устройству работать при Vref=0 В аналогично традиционному приемному КМОП-устройству. Приемное устройство также может быть сконфигурировано с помощью вспомогательного n-МОП-FET с мониторингом Vref, чтобы давать возможность входному приемному устройству на основе Vref работать с возможностью программирования на токах смещения и граничном значении отключения при Vref=(0,5~0,7) Vdd, в зависимости от отношения полного сопротивления предконечного задающего устройства к параллельному оконечному полному сопротивлению включения/выключения кристалла. 6 н. и 19 з.п. ф-лы, 9 ил.

1. Входное приемное устройство с разрешением по логическому порогу переменного диапазона, при этом устройство содержит:

инвертор;

схему логического порога, соединенную параллельно с инвертором и выполненную с возможностью принимать переменное значение логического порога и настраивать инвертор на значение логического порога; и

вспомогательное устройство, выполненное с возможностью принимать переменное значение логического порога и выполненное с возможностью предоставления инвертору тракта тока смещения, отличного от тракта тока смещения, предоставляемого инвертору посредством схемы логического порога;

причем детектор логического порога выполнен с возможностью принимать значение логического порога и предоставлять инвертору дополнительный тракт тока смещения на основе переменного значения логического порога.

2. Устройство по п.1, в котором детектор логического порога содержит:

n-МОП полевой транзистор (FET), имеющий затвор, выполненный с возможностью принимать значение логического порога;

р-МОП-FET с повышением напряжения, имеющий затвор, общий для стока и истока, соединенный с источником напряжения, и в котором сток соединяется со стоком n-МОП-FET.

3. Устройство по п.1, дополнительно содержащее разрешающее устройство, выполненное с возможностью принимать сигнал управления разрешением и выполненное с возможностью выборочно запрещать протекание тока смещения через инвертор на основе состояния сигнала управления разрешением.

4. Устройство по п.1, в котором инвертор содержит КМОП-инвертор.

5. Устройство по п.4, в котором схема логического порога содержит:

КМОП-пару опорного напряжения (Vref), имеющую исток р-МОП Vref, общий с истоком р-МОП КМОП-инвертора;

исток n-МОП Vref, общий с истоком n-МОП КМОП-инвертора;

р-МОП-FET с повышением напряжения, имеющий затвор, соединенный с общим стоком КМОП-пары Vref и соединенный так, чтобы повышать напряжение на шине общего истока р-МОП; и

FET CMOS с понижением напряжения, имеющий затвор, соединенный с общим стоком КМОП-пары Vref и соединенный так, чтобы понижать напряжение на шине общего истока n-МОП.

6. Устройство по п.4, в котором вспомогательное устройство содержит вспомогательный р-МОП-FET, имеющий затвор, соединенный со значением логического порога и выполненный с возможностью повышать напряжение на шине истока р-МОП-FET КМОП-пары.

7. Устройство по п.4, в котором вспомогательное устройство содержит вспомогательный n-МОП-FET, имеющий затвор, соединенный со значением логического порога и выполненный с возможностью понижать напряжение на шине истока n-МОП-FET КМОП-пары.

8. Устройство по п.4, дополнительно содержащее детектор логического порога, выполненный с возможностью принимать значение логического порога и предоставлять инвертору дополнительный тракт тока смещения на основе значения логического порога.

9. Устройство по п.1, в котором инвертор содержит n-МОП-инвертор.

10. Устройство по п.9, в котором схема логического порога содержит:

n-МОП-FET Vref, имеющий затвор, выполненный с возможностью принимать значение логического порога и имеющий исток, общий с истоком n-МОП-инвертора;

первый р-МОП-FET с повышением напряжения с истоком, соединенным с Vdd, и стоком, соединенным со стоком n-МОП-инвертора;

второй р-МОП-FET с повышением напряжения с истоком, соединенным с Vdd, с шиной стока, соединенной со стоком n-МОП-FET Vref.

11. Устройство по п.10, в котором первый р-МОП-FET с повышением напряжения имеет затвор, соединенный со стоком n-МОП-FET Vref.

12. Устройство по п.10, в котором первый р-МОП-FET с повышением напряжения имеет затвор, соединенный со стоком n-МОП-инвертора.

13. Устройство по п.10, в котором второй р-МОП-FET с повышением напряжения имеет затвор, соединенный со стоком n-МОП-FET Vref.

14. Устройство по п.10, в котором второй р-МОП-FET с повышением напряжения имеет затвор, соединенный со стоком n-МОП-инвертора.

15. Интегральная схема входного приемного устройства с разрешением по логическому порогу переменного диапазона по п.1.

16. Входное приемное устройство с разрешением по логическому порогу переменного диапазона, при этом устройство содержит:

КМОП-инвертор;

р-МОП полевой транзистор (FET) опорного напряжения (Vref), имеющий исток, общий с истоком р-МОП КМОП-инвертора;

n-МОП-FET Vref, имеющий сток, общий со стоком р-МОП-FET Vref, формируя таким образом КМОП-пару Vref, затвор, общий с истоком р-МОП-FET Vref, и выполненный с возможностью принимать значение логического порога, и исток, общий с истоком n-МОП КМОП-инвертора;

р-МОП-FET с повышением напряжения, имеющий затвор, соединенный с общим стоком КМОП-пары Vref, чтобы формировать шину общего истока, и соединенный так, чтобы повышать напряжение на шине общего истока;

FET КМОП (CMOS) с понижением напряжения, имеющий затвор, соединенный с общим стоком КМОП-пары Vref, и соединенный так, чтобы понижать напряжение на шине общего истока n-МОП; и

вспомогательный р-МОП-FET, имеющий затвор, выполненный с возможностью принимать значение логического порога и выполненный с возможностью повышать напряжение на шине общего истока n-МОП.

17. Устройство по п.16, дополнительно содержащее разрешающее устройство, выполненное с возможностью принимать сигнал управления разрешением и выполненное с возможностью выборочно запрещать протекание тока смещения через КМОП-инвертор на основе состояния сигнала управления разрешением.

18. Устройство по п.16, дополнительно содержащее детектор логического порога, выполненный с возможностью принимать значение логического порога и предоставлять КМОП-инвертору дополнительный тракт тока смещения на основе значения логического порога.

19. Устройство по п.18, в котором детектор логического порога содержит:

n-МОП-FET, имеющий затвор, выполненный с возможностью принимать значение логического порога, и исток, соединенный с землей;

р-МОП-FET с повышением напряжения, имеющий затвор, общий для стока и истока, соединенный с источником напряжения, и при этом сток соединяется со стоком n-МОП-FET;

вспомогательный р-МОП-FET, имеющий исток, соединенный с источником напряжения, сток, соединенный с выходом КМОП-инвертора, и затвор, соединенный со стоком n-МОП-FET.

20. Интегральная схема входного приемного устройства с разрешением по логическому порогу переменного диапазона по п.19.

21. Способ настройки логического входного приемного устройства с автоматическим смещением, при этом способ содержит этапы, на которых:

настраивают инвертор;

настраивают устройства логического порога, чтобы принимать переменное значение логического порога и настраивать инвертор на значение логического порога; и

настраивают вспомогательное устройство, чтобы принимать переменное значение логического порога, и чтобы предоставлять инвертору тракт тока смещения, отличный от тракта тока смещения, предоставляемого в инвертор посредством устройств логического порога;

настраивают детектор логического порога так, чтобы принимать значение логического порога и предоставлять инвертору дополнительный тракт тока смещения на основе значения логического порога.

22. Способ по п.21, в котором настраивание инвертора содержит этап, на котором настраивают КМОП-инвертор.

23. Способ по п.22, в котором настраивание устройств логического порога содержит этап, на котором настраивают КМОП-пару опорного напряжения (Vref), по существу, параллельно КМОП-инвертору.

24. Способ по п.22, в котором настраивание вспомогательного устройства содержит этап, на котором настраивают вспомогательный р-МОП полевой транзистор (FET), имеющий затвор, на который подается значение логического порога, и выполненный с возможностью повышать напряжение на шине истока р-МОП-FET КМОП-инвертора.

25. Входное приемное устройство с разрешением по логическому порогу переменного диапазона, при этом устройство содержит:

КМОП-инвертор;

средство для приема переменного значения логического порога и настройки КМОП-инвертора на значение логического порога; и

средство для приема переменного значения логического порога и предоставления в КМОП-инвертор тракта тока смещения, отличного от тракта тока смещения, предоставляемого КМОП-инвертору при помощи средства для приема переменного значения логического порога;

средство для приема значения логического порога и предоставления КМОП-инвертору дополнительного тракта тока смещения на основе переменного значения логического порога.

| DE 4127212 A1, 18.02.1993 | |||

| Преобразователь уровня напряжения | 1991 |

|

RU2004073C1 |

| Преобразователь уровней (его варианты) | 1985 |

|

SU1256165A1 |

| US 5831472 A, 03.11.1998 | |||

| СПОСОБ ХИМИЧЕСКОГО НАГРЕВА СТАЛИ | 2006 |

|

RU2340682C2 |

| US 7218151 B1, 15.05.2007 | |||

| Пломбировальные щипцы | 1923 |

|

SU2006A1 |

Авторы

Даты

2012-11-27—Публикация

2008-05-28—Подача