Область техники

Настоящее изобретение относится к архитектурам цифрового сигнального процессора.

Уровень техники

Цифровые сигнальные процессоры являются цифровыми электронными модулями, приспособленными для предоставления специализированной поддержки для операций обработки цифрового сигнала, таких как цифровые фильтры, сжатие и т.п.

Функциональность цифрового сигнального процессора может быть предоставлена во множестве форматов, включающих в себя автономные микропроцессоры, как часть блока "системного комплексного решения" или как специализированные блоки в FPGA-архитектуре.

FPGA являются типом программируемого логического устройства. Они, как правило, основываются на стандартном программируемом логическом блоке, большое число которых размещается вместе для реализации различных функций.

Фиг. 1 показывает схематично пример FPGA-системы, которая известна в уровне техники.

Как показано на фиг. 1, FPGA-микросхема 10 содержит множество логических блоков 11. Микросхема также содержит множество портов 12 ввода/вывода. Соединение этих логических блоков 11 и портов 12 ввода/вывода является множеством дорожек 14. В точках соединения этих дорожек предусматриваются множество программируемых областей 13 трассировки, которые могут также называться распределительными блоками. В этих программируемых областях трассировки предусматриваются коммутаторы, которые могут выборочно соединять любую пару пересекающихся дорожек, под управлением логического значения, сохраненного в одноразрядном регистре памяти, соединенном с каждым коммутатором. Значения одноразрядного регистра памяти устанавливаются при запуске системы из энергонезависимой памяти. Соответственно, посредством установки значений в запоминающих устройствах коммутатора при необходимости любые соединения любого логического блока могут быть связаны с соединениями любого другого логического блока, или любого порта 12 ввода/вывода. Аналогично любой один порт ввода/вывода может быть соединен с любым другим портом ввода/вывода. Таким образом, посредством правильного конфигурирования блоков памяти для определения операции каждого логического блока и запоминающих устройств 13 коммутатора для установления соответствующих соединений между логическими блоками любая желаемая функциональность может быть реализована.

В то время как основная философия FPGA основывается на возможности реализации любой цифровой операции посредством подходящих соединений и подходящих логических значений стандартных логических блоков, в некоторых сценариях такой общий подход является очень неэффективным с точки зрения площади поверхности микросхемы, используемой для реализации данной функции, и энергии, потребляемой при работе для применения желаемой функции. Соответственно, многие современные FPGA-архитектуры включают в себя специализированные блоки 15, содержащие схемы, специально предназначенные для поддержки некоторых конкретных функций.

Некоторые FPGA-архитектуры предоставляют такие специализированные блоки 15 для поддержки операций обработки цифровых сигналов.

Фиг. 2 показывает блок обработки цифрового сигнала, который известен в уровне техники.

Как показано на фиг. 2, предоставляется блок 200, содержащий два входа 211 и 212, каждый буферизуется посредством реле 213 и 214. Входы 211 и 212 предоставляют значения умножителю 220, который предоставляет свой выходной сигнал сумматору 230 через дополнительное реле 221. Сумматор принимает второй входной сигнал 215 через дополнительное реле 216 и выдает выходной сигнал 217 блока через дополнительное реле 231. Различные реле могут быть использованы или нет в зависимости от деталей реализации.

В качестве блока в FPGA-архитектуре, которая описана выше, DSP-блок может быть соединен с какой-либо подходящей логикой, предоставляемой посредством других блоков FPGA. В частности, эти другие блоки, которые типично будут стандартными логическими блоками, как описано выше, могут быть сконфигурированы, чтобы предоставлять любые логические входные сигналы, которые могут потребоваться для желаемой операции. Посредством предоставления подходящих значений коэффициентов на один вход 211 или 212 и подходящим образом синхронизированной по времени последовательности значений данных на другой вход и конфигурирования дополнительных логических блоков, чтобы накапливать выходные значения, фильтр и другие функции могут быть реализованы.

Примеры таких подходов могут быть найдены, например, в руководстве пользователя для FPGA-архитектур Xilinx Virtex 5 или Xilinx Virtex 4.

Будет понятно, в частности, что, в то время как подходы предшествующего уровня, как описано выше, отчасти улучшают эффективность DSP-архитектур, их опора на внешнюю логику для поддержки реализации конкретных DSP-операций означает, что результирующие схемы остаются недостаточно оптимальными с точки зрения требуемого пространства, потребляемой энергии, распределения синхросигналов и т.п. Желательно предоставить DSP-архитектуру, предоставляющую более объединенную функциональность, в то же время сохраняющую высокую степень универсальности.

Сущность изобретения

В соответствии с настоящим изобретением в первом аспекте предоставляется программируемый цифровой сигнальный процессор, содержащий цифровой фильтр, таблицу поиска сдвигового регистра и память фильтра, при этом таблица поиска сдвигового регистра включается, чтобы предоставлять входные данные цифровому фильтру в первом режиме работы, а память фильтра включается, чтобы предоставлять коэффициенты фильтра цифровому фильтру в первом режиме работы, при этом выходные сигналы памяти фильтра и таблицы поиска сдвигового регистра синхронизируются таким образом, чтобы создавать соответствующие коэффициенты фильтра и входные данные, вместе реализующие желаемую конфигурацию фильтра.

В развитии первого аспекта, таблица поиска сдвигового регистра содержит сдвиговый регистр, при этом сдвиговый регистр конфигурируется таким образом, чтобы быть функционирующим либо как один непрерывный сдвиговый регистр, либо как множество независимо функционирующих сдвиговых регистров.

В развитии первого аспекта, программируемый цифровой сигнальный процессор дополнительно содержит конечный автомат, конечный автомат предоставляет значения адресации таблице поиска сдвигового регистра и памяти фильтра.

В развитии первого аспекта, программируемые значения адресации содержат один адрес для таблицы поиска сдвигового регистра и памяти фильтра, в результате чего, значения, сохраненные в таблице поиска сдвигового регистра и памяти фильтра, структурированы так, что упомянутый один адрес ссылается на соответствующие коэффициенты и входные данные для цифрового фильтра в первом режиме работы.

В развитии первого аспекта, во втором режиме работы значения, сохраненные в таблице поиска сдвигового регистра, выводятся для обработки, отличной от цифрового фильтра.

В развитии первого аспекта, во втором режиме работы таблица поиска сдвигового регистра используется в качестве входного регистра умножителя.

В развитии первого аспекта, цифровой фильтр составляет компонент фильтра с конечной импульсной характеристикой (FIR).

В развитии первого аспекта, цифровой фильтр составляет компонент фильтра с конечной импульсной характеристикой, содержащего первый фильтр с конечной импульсной характеристикой и второй фильтр с конечной импульсной характеристикой в конфигурации обратной связи, где конечный автомат предоставляет включающие сигналы, которые координируют сочетание выходных сигналов первого фильтра с конечной импульсной характеристикой и второго фильтра с конечной импульсной характеристикой, чтобы реализовывать фильтр с бесконечной импульсной характеристикой (IIR).

В развитии первого аспекта, цифровой сигнальный процессор реализуется в FPGA-архитектуре, содержащей множество таблиц поиска, конфигурация каждой таблицы поиска определяется посредством одного или более соответствующих блоков памяти, запрограммированных при инициировании системы с помощью конфигурационного битового потока, при этом значения в памяти фильтра также программируются посредством конфигурационного битового потока.

В соответствии с настоящим вариантом осуществления во втором аспекте предоставляется способ выполнения операции цифрового сигнального процессора, способ содержит адресацию таблицы поиска сдвигового регистра, чтобы выводить данные в цифровой сигнальный процессор в первом режиме работы, и адресацию памяти фильтра, чтобы предоставлять коэффициенты цифровому фильтру в первом режиме работы, и выполнение операции цифрового фильтра по входным данным с помощью коэффициента.

В развитии второго аспекта, способ содержит дополнительный этап структурирования таблицы поиска сдвигового регистра и памяти фильтра, так что одно значение адреса ссылается на соответствующие коэффициенты и входные данные для цифрового фильтра в первом режиме работы, так что этапы адресации таблицы поиска сдвигового регистра, чтобы выводить коэффициенты в цифровой сигнальный процессор в первом режиме работы, и адресации памяти фильтра, чтобы предоставлять входные данные цифровому фильтру в первом режиме работы, выполняются с помощью упомянутого одного значения адреса.

В развитии второго аспекта, операция цифрового фильтра является операцией фильтра с конечной импульсной характеристикой.

В развитии второго аспекта, операция цифрового фильтра является операцией фильтра с бесконечной импульсной характеристикой, содержащей первую операцию с конечной импульсной характеристикой и вторую операцию с конечной импульсной характеристикой на основе значений обратной связи, способ содержит дополнительный этап предоставления включающих сигналов, координирующих сочетание результатов первой операции с конечной импульсной характеристикой и второй операции с конечной импульсной характеристикой, чтобы получать результат фильтра с бесконечной импульсной характеристикой.

В соответствии с настоящим изобретением в третьем аспекте предоставляется программа для компьютера, содержащая инструкции, приспособленные для реализации этапов второго аспекта.

Краткое описание чертежей

Вышеупомянутые и другие преимущества настоящего изобретения будут сейчас описаны со ссылкой на сопровождающие чертежи, на которых:

Фиг. 1 показывает схематично пример FPGA-системы, которая известна в уровне техники;

Фиг. 2 показывает блок обработки цифрового сигнала, который известен в уровне техники;

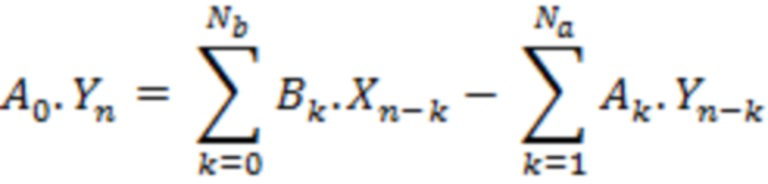

Фиг. 3 показывает программируемый цифровой сигнальный процессор в соответствии с первым вариантом осуществления;

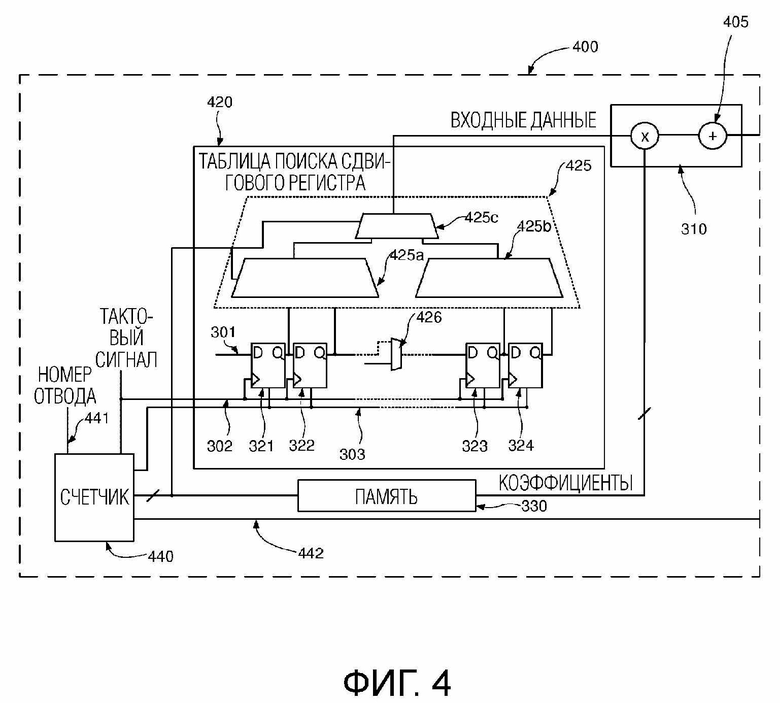

Фиг. 4 показывает программируемый цифровой сигнальный процессор в соответствии со вторым вариантом осуществления;

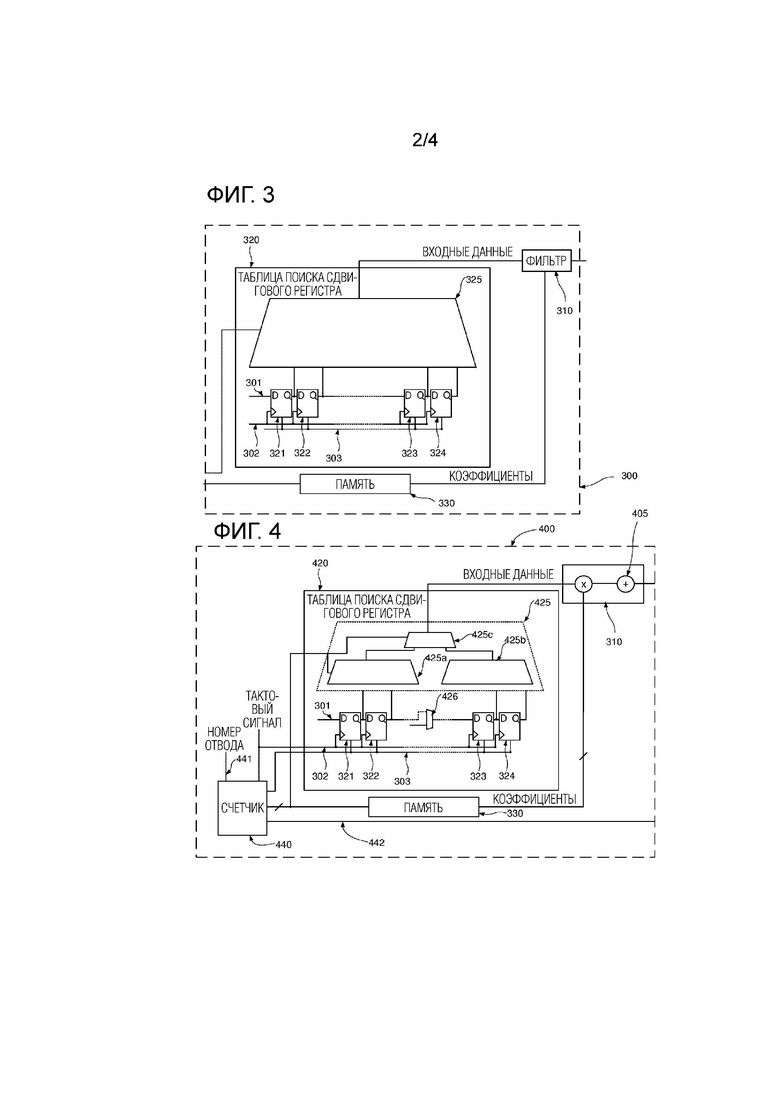

Фиг. 5 представляет параллельную реализацию фильтра с конечной импульсной характеристикой в соответствии с вариантом осуществления;

Фиг. 6 представляет параллельную реализацию фильтра с бесконечной импульсной характеристикой в соответствии с вариантом осуществления;

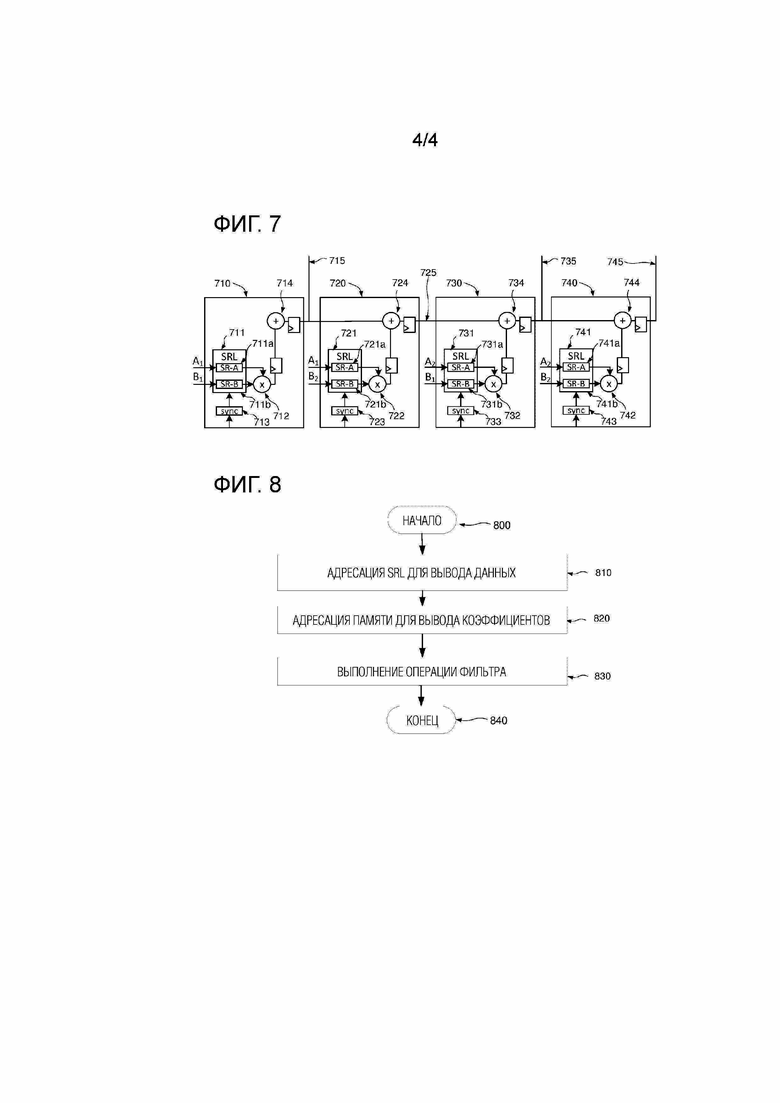

Фиг. 7 показывает умножитель со знаком, реализованный с помощью фильтра в соответствии с вариантом осуществления; и

Фиг. 8 представляет способ выполнения работы цифрового сигнального процессора в соответствии с вариантом осуществления.

Подробное описание изобретения

Фиг. 3 показывает программируемый цифровой сигнальный процессор в соответствии с первым вариантом осуществления.

Как показано, программируемый цифровой сигнальный процессор 300 содержит цифровой фильтр 310, таблицу 320 поиска сдвигового регистра и память 330. Память может содержать оперативное запоминающее устройство, такое как RAM или ROM-устройство, каскадно включенные регистры или иное. Таблица 320 поиска сдвигового регистра включается, чтобы предоставлять входные данные цифровому фильтру 310 в первом режиме работы, а память 330 фильтра включается, чтобы предоставлять коэффициенты фильтра цифровому фильтру 310 в этом первом режиме работы. Выходные сигналы памяти фильтра и таблицы поиска сдвигового регистра синхронизируются таким образом, чтобы создавать соответствующие коэффициенты фильтра и входные данные, вместе реализующие желаемую конфигурацию фильтра.

Цифровой фильтр содержит умножитель, сконфигурированный, чтобы умножать значение данных и значение коэффициента, и сумматор для суммирования последовательных значений, возможно с дополнительными регистрами, по существу, как описано выше относительно фиг. 2. Дополнительная задержка, суммирование, мультиплексирование или другие компоненты могут быть включены в расширенную функциональность.

Как показано, таблица 320 поиска сдвигового регистра содержит сдвиговый регистр, содержащий четыре триггера 321, 322, 323, 324. Будет понятно, что, в то время как только четыре триггера показаны, любое число триггеров может быть предусмотрено. Поскольку длина сдвигового регистра соответствует максимальному числу коэффициентов, которые могут быть обработаны посредством одной реализации DSP на фиг. 3, число триггеров может быть выбрано на основе числа коэффициентов, которые могут быть обработаны фильтром, т.е., числа отводов фильтра, которое, в свою очередь, является основным ограничением конструкции фильтра, отражающим сложность операций фильтра, которые могут выполняться. Целесообразным числом триггеров может быть 32 в некоторых вариантах осуществления.

Аналогично, число адресов в памяти 330 может быть равно числу коэффициентов, которые могут быть обработаны фильтром, т.е., числу отводов фильтра. В других вариантах осуществления число для множества адресов в памяти 330 может быть меньше числа коэффициентов, которые могут быть обработаны фильтром, т.е., числа отводов фильтра. В других вариантах осуществления число для множества адресов в памяти 330 может быть больше числа коэффициентов, которые могут быть обработаны фильтром, т.е., числа отводов фильтра.

Длина слова данных, хранящегося по каждому адресу памяти, может быть равна ширине шины входных данных. 24-битная входная шина предложит 24-битный коэффициент, и таблица поиска сдвигового регистра содержит 24 сдвиговых регистра и мультиплексора параллельно. Фильтр тогда будет выполнять умножение двух 24-битных значений в операции фильтрации.

В работе непрерывный поток значений двоичных данных для фильтрации прибывает на вход 301, который постепенно тактируется через сдвиговый регистр 321, 322, 323, 324, когда обработка идет, как описано далее в данном документе. Для заданного набора значений, загруженного в триггеры сдвигового регистра 321, 322, 323, 324, каждый триггер сдвигового регистра 321, 322, 323, 324 до числа отводов в фильтре адресуется последовательно, и значение передается фильтру 310 как значение данных.

Между тем, поскольку каждый триггер сдвигового регистра 321, 322, 323, 324 до числа отводов в фильтре адресуется, память 330 адресуется одновременно, в результате чего, адресованное местоположение в памяти содержит коэффициент фильтра, соответствующий адресованному триггеру, и результирующие выходные данные передаются фильтр 310 как набор значений коэффициентов.

Адресованное значение из сдвигового регистра, таким образом, обрабатывается посредством фильтра 310 с помощью соответствующих коэффициентов, предоставленных посредством памяти 330. Выходные данные фильтра накапливаются, и система затем переходит к адресу следующего триггера сдвигового регистра 321, 322, 323, 324 и соответствующей позиции в памяти 330.

На этой основе каждое значение данных в сдвиговом регистре до числа отводов в фильтре обрабатывается согласно его соответствующему набору коэффициентов, и результаты накапливаются на выходе фильтра. После того как каждый триггер в сдвиговом регистре до числа отводов в фильтре был адресован, сдвиговый регистр синхронизируется, например, посредством активизации шины 302 синхронизации, так что значение каждого триггера в сдвиговом регистре передается его соседу, новое значение данных синхронизируется в первый триггер 321 сдвигового регистра со входа 301 данных, а значение в последнем триггере в сдвиговом регистре отбрасывается.

Процесс адресации каждого триггера сдвигового регистра 321, 322, 323, 324 до числа отводов в фильтре, в свою очередь, и обработка посредством фильтра 310 с помощью соответствующих коэффициентов, предоставленных посредством памяти 330, затем начинается вновь для нового набора значений.

Этот процесс продолжается бесконечно, пока каждое входное значение во входном канале 301 не будет обработано.

Фиг. 4 показывает программируемый цифровой сигнальный процессор в соответствии со вторым вариантом осуществления.

Как описано относительно фиг. 3, адресация значений коэффициентов в памяти 330 и значения данных в таблице 420 поиска сдвигового регистра выполняется синхронизированным образом, так что, когда данные получаются из таблицы 420 поиска сдвигового регистра, соответствующие конкретной позиции отвода фильтра, соответствующий коэффициент для этой позиции отвода получается из памяти 330. Будет понятно, что эта синхронизация может быть достигнута множеством способов, например, со ссылкой на таблицу сопоставления или т.п., предоставляющую соответствующие значения адреса для памяти 330 с одной стороны и таблицы 420 поиска сдвигового регистра с другой стороны.

Будет дополнительно понятно, что память 330 и таблица 420 поиска сдвигового регистра могут быть структурированы так, что одно и то же значение адреса указывает на соответствующие значения в памяти 330 и значение данных в таблице 420 поиска сдвигового регистра.

По существу, предоставляется программируемый цифровой сигнальный процессор 400, содержащий цифровой фильтр 310, таблицу 420 поиска сдвигового регистра и память 330, при этом таблица 420 поиска сдвигового регистра включается, чтобы предоставлять входные данные цифровому фильтру 310 в первом режиме работы, а память 330 фильтра включается, чтобы предоставлять коэффициенты фильтра цифровому фильтру 310 в первом режиме работы, при этом выходные сигналы памяти 330 фильтра и таблицы 420 поиска сдвигового регистра синхронизируются таким образом, чтобы создавать соответствующие коэффициенты фильтра и входные данные, вместе реализующие желаемую конфигурацию фильтра.

Фиг. 4 представляет один способ достижения синхронизации, в соответствии с чем, предоставляется счетчик 440, принимающий входной синхронизирующий сигнал 302 и входной сигнал 441 числа отводов. Счетчик 440 дополнительно снабжается выходом, который выводит текущее значение счетчика. Счетчик 440 может быть рассмотрен более обобщенно как составляющий часть или весь конечный автомат синхронизации. Значение счетчика подается в память 330 и таблицу 420 поиска сдвигового регистра как значение адреса. На этой основе, значения коэффициентов загружаются в память 330 в последовательных позициях, так что, когда значение счетчика увеличивается, последовательные значения коэффициентов, соответствующие последовательным позициям отводов, выбираются. По тому же принципу, когда значение счетчика увеличивается, последовательные триггеры в сдвиговом регистре, соответствующие последовательным позициями отводов, выбираются посредством мультиплексора 425. Соответственно, значение счетчика служит для адресации памяти 330 и таблицы 420 поиска сдвигового регистра синхронизированным образом. Счетчик конфигурируется, чтобы перезапускать свой счет, когда он достигает подсчитанного числа отводов (которое в зависимости от деталей реализации может быть любым числом до числа триггеров в таблице 420 поиска сдвигового регистра). В некоторых вариантах счетчик может быть снабжен выходом переполнения, который выводит предварительно определенное значение, когда значение счетчика достигает входного числа отводов. Этот выход может быть использован для координирования операций множества программируемых цифровых сигнальных процессоров, например, как описано более подробно ниже.

Как показано, в компоновке на фиг. 4 мультиплексор 425 реализуется как два субмультиплексора 425a и 425b, каждый принимает фрагмент выходных сигналов сдвигового регистра 321-324. Каждый субмультиплексор 425a и 425b может принимать половину выходных сигналов сдвигового регистра 321-324, или выходные сигналы сдвигового регистра 321-324 могут быть поделены между двумя субмультиплексорами некоторым другим образом. Выходные сигналы двух субмультиплексоров 425a и 425b сами выбираются посредством третьего субмультиплексора 435c, так что три субмультиплексора 425a, 425b, 425c являются логически эквивалентными мультиплексору 325 на фиг. 3. Дополнительный мультиплексор 426 предоставляется в точке в сдвиговом регистре 321-324, соответствующей точке, где выходные сигналы сдвигового регистра отправляются одному субмультиплексору или другому, как показано между триггером 322 и триггером 323. С помощью одного выбранного значения мультиплексор 426 соединяет вход триггера 323 с выходом триггера 322, таким образом, чтобы поддерживать один сдвиговый регистр в работе. С помощью другого выбранного значения мультиплексор 426 отсоединяет вход триггера 323 от выхода триггера 322 в пользу альтернативного входа, таким образом, чтобы предоставлять два отдельных сдвиговых регистра, например, как описано со ссылкой на фиг. 7 ниже.

Как показано, фильтр 310 на фиг. 4 дополнительно содержит накапливающий сумматор 405, как обсуждалось выше, который может быть предусмотрен для накопления последовательных выходных данных от фильтра 310. Посредством него, например, полный фильтр с конечной импульсной характеристикой может быть реализован путем накопления значений, выводимых фильтром 310 для каждой позиции отвода, которая получена с помощью соответствующих значений данных и значений коэффициента, как указано выше.

По существу, программируемый цифровой сигнальный процессор может дополнительно содержать конечный автомат 440, предоставляющий значения адресации в таблицу поиска сдвигового регистра и память, когда один адрес ссылается на соответствующие коэффициенты и входные данные для цифрового фильтра в первом режиме работы.

В некоторых вариантах осуществления DSP-модуль, такой как модуль, описанный относительно фиг. 3 или 4, может быть реализован как DSP-блок в FPGA-архитектуре. Каждый DSP-блок может содержать один или более DSP-модулей, такие как модули, описанные относительно фиг. 3 или 4. Каждая FPGA может содержать любое число DSP-блоков, также как стандартные логические блоки и блоки другого типа, которые подходят для обычного предполагаемого использования FPGA-архитектуры. По существу, цифровой сигнальный процессор может быть реализован в FPGA-архитектуре, содержащей множество поисковых таблиц, конфигурация каждой поисковой таблицы определяется посредством одного или более соответствующих запоминающих устройств, запрограммированных при инициировании системы с помощью конфигурационного битового потока, при этом значения в памяти фильтра также программируются посредством конфигурационного битового потока.

Фиг. 5 представляет параллельную реализацию фильтра с конечной импульсной характеристикой в соответствии с вариантом осуществления.

FIR-фильтр на основе полупараллельной реализации может быть использован в контексте, где число отводов больше числа отводов, предусматриваемых одним DSP-модулем, например, как описано со ссылкой на фиг. 3 или 4, или когда требование по частоте может быть лучше удовлетворено посредством множества DSP-модулей, сконфигурированных, чтобы вычислять несколько отводов для каждого цикла выборки.

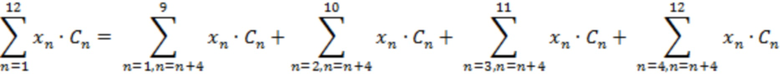

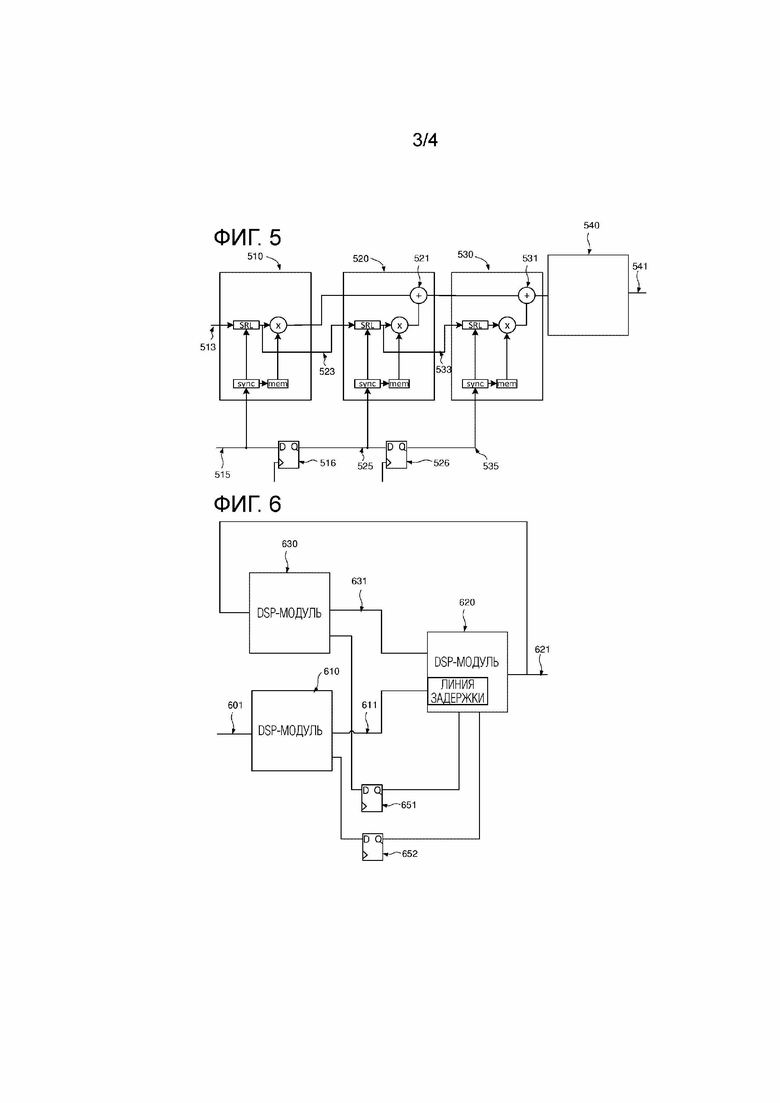

В качестве примера, в случае, когда 12-отводный фильтр с 3 DSP используется, может применяться следующая декомпозиция:

Где n - это индекс каждого отвода

Cn - это коэффициент каждого отвода n

Xn - это значение данных на каждом отводе n

Может быть отмечено, что каждый подтерм представляет одинаковую структуру и может быть реализован с помощью последовательности 3 каскадно соединенных DSP (подтермы являются суммой 4 произведений).

На этой основе, как показано на фиг. 5, предоставляется первый DSP-модуль 510, соответствующий, например, модулю, описанному со ссылкой на фиг. 3 или 4 выше, второй DSP-модуль 520, соответствующий, например, модулю, описанному со ссылкой на фиг. 3 или 4 выше, и третий DSP-модуль 530, соответствующий, например, модулю, описанному со ссылкой на фиг. 3 или 4 выше. Каждый DSP-модуль 510, 520, 530 показан схематично содержащим элемент синхронизации, элемент таблицы поиска сдвигового регистра и элемент памяти, также как умножитель и сумматор элемента фильтра.

Каждый из этих трех DSP-модулей конфигурируется как FIR-фильтр, например, как описано со ссылкой на элемент 400 на фиг. 4. Каждый из трех DSP-модулей конфигурируется, чтобы обрабатывать последовательный поднабор суммарных отводов фильтра, который должен быть реализован посредством системы в целом, так что суммарное число отводов, реализованных на всех трех DSP-модулях, является числом отводов конечного фильтра.

Первый DSP-модуль 510 принимает входные данные 513. Эти одинаковые данные подаются второму DSP-модулю 520 с выхода таблицы поиска сдвигового регистра первого DSP-модуля на вход 523 и третьему DSP-модулю 530 на вход 533 с выхода таблицы поиска сдвигового регистра второго DSP-модуля, так что таблицы поиска сдвиговых регистров соответствующих DSP-модулей составляют линию задержки, так что второй DSP-модуль 520 принимает данные через n циклов после первого DSP-модуля 510, а третий DSP-модуль 520 принимает данные через 2n циклов после первого DSP-модуля 510.

Аналогично, первый DSP-модуль 510 принимает сигнал 515 синхронизации. Соответствующий сигнал 525 синхронизации подается второму DSP-модулю 520 и соответствующий сигнал 535 синхронизации - третьему DSP-модулю 530 через линию задержки, представленную посредством триггеров 516 и 526, так что второй DSP-модуль 520 включается через один цикл после первого DSP-модуля 510, а третий DSP-модуль 520 включается через два цикла после первого DSP-модуля 510.

Выходные сигналы первого и второго DSP-модулей 510 и 520 суммируются в сумматоре 521 второго DSP-модуля, и выходные сигналы сумматора 521 и третьего DSP-модуля 531 суммируются в сумматоре 531 третьего DSP-модуля. Выходной сигнал сумматора 531 накапливается в течение полного цикла обработки фильтра посредством модуля 540, который, как обсуждалось выше, может быть реализован с помощью накапливающего блока дополнительного DSP-модуля, такого как элемент 405, как описано со ссылкой на фиг. 4.

Посредством этого подхода FIR произвольного размера может быть реализован путем соединения подходящего числа DSP-модулей, как описано выше, с предоставлением подходящих коэффициентов и сигналов синхронизации. Будет понятно, что любое желаемое число DSP-модулей может быть соединено таким образом.

Фиг. 6 представляет параллельную реализацию фильтра с бесконечной импульсной характеристикой (IIR) в соответствии с вариантом осуществления.

Общая формула, описывающая IIR-фильтр:

Формула может быть упрощена с помощью A0=1.

Первая сумма определяет FIR-фильтр для Nb отводов. Этот FIR-фильтр может применяться по дискретизированному входному сигналу.

Вторая сумма определяет FIR-фильтр для Na отводов. Этот FIR-фильтр может применяться по выходному сигналу IIR-фильтра. Это контур обратной связи фильтра.

На этой основе, как показано на фиг. 6, предоставляется первый DSP-модуль 610, соответствующий, например, модулю, описанному со ссылкой на фиг. 3 или 4 выше, второй DSP-модуль 620, соответствующий, например, модулю, описанному со ссылкой на фиг. 3 или 4 выше, и третий DSP-модуль 630, соответствующий, например, модулю, описанному со ссылкой на фиг. 3 или 4 выше.

Два из этих трех DSP-модулей 610 и 630 конфигурируются как FIR-фильтр, например, как описано со ссылкой на элемент 400 на фиг. 4.

В частности, первый DSP-модуль 610 определяет FIR-фильтр для Nb отводов. Этот FIR-фильтр может применяться по дискретизированному входному сигналу 601.

Третий DSP-модуль 630 определяет FIR-фильтр для Na отводов. Этот FIR-фильтр может применяться по выходному сигналу IIR-фильтра. Это контур обратной связи фильтра.

FIR-фильтр работает достаточно быстро, чтобы производить один результат в каждом цикле выборки, так что возможно накапливать оба результата синхронизированным образом. Оба фильтра являются полностью регистровыми, но они работают с гораздо более высокой частотой по сравнению с частотой выборки, так что конечный результат может быть получен в 1 цикле выборки. Чем более крупными являются фильтры, тем менее эффективным является IIR-фильтр, поскольку тактовое отношение непосредственно связано с числом отводов в самом крупном фильтре.

Чтобы просто разрешать синхронизацию фильтра, следующие ограничения применяются в настоящем варианте осуществления:

Непосредственный FIR-подфильтр, реализованный посредством первого DSP-модуля 610, ограничивается числом отводов, которое может быть реализовано в одном DSP-модуле, с помощью подхода с одним DSP, как описано, например, со ссылкой на фиг. 4, с тем, чтобы предоставлять одинаковую задержку конвейерной обработки во всех конфигурациях.

Закольцованный FIR-подфильтр, реализованный посредством третьего DSP-модуля 630, ограничивается половиной числа отводов первого DSP-модуля 610, а также реализуется с помощью подхода с одним DSP, как описано, например, со ссылкой на фиг. 4. Чтобы получить третий DSP-модуль 630, работающий достаточно быстро, чтобы формировать свой результат в течение одного периода выборки первого DSP-модуля 610, требуется получить третий DSP-модуль 630, работающий с 4-кратной скоростью первого DSP-модуля 610. Это может быть достигнуто посредством реализации этого фильтра с чередованием коэффициентов с 0 константой. Чередующийся подход объясняет ограничение 16 отводами.

Суммирование подфильтра и синхронизация выполняется во втором DSP-модуле 620 с помощью таблицы поиска сдвигового регистра и ALU.

Второй DSP-модуль 620 принимает информацию о синхронизации из регистров 651 и 652, которые принимают указание 442 переполнения коэффициента от первого и третьего DSP-модулей соответственно, как основу для синхронизации сигналов.

Синхронизация результата от DSP-модулей 610 и 630 требует предоставления линии задержки по выходному сигналу на выходе модуля 610, чтобы получать ту же глубину, что и для модуля 610 (корректировка разницы в числе отводов N по сравнению с N/2). Это может быть сделано с помощью таблицы поиска сдвигового регистра DSP-модуля 620 во втором режиме работы, когда существует недостаточно выделенных регистров в DSP-конфигурации. Конкретное число регистров будет зависеть от деталей реализации, но в качестве примера, если требуется 3 уровня конвейера, в качестве других сигналов с 2*3=6 триггерами, а DSP-схемы предоставляют только 2, дополнительный уровень может быть предоставлен посредством таблицы поиска сдвигового регистра дополнительного DSP-модуля.

Соответственно, фильтр с бесконечной импульсной характеристикой может содержать первый цифровой фильтр с конечной импульсной характеристикой и второй цифровой фильтр с конечной импульсной характеристикой в конфигурации с обратной связью, где конечный автомат предоставляет синхронизирующие сигналы, координирующие сочетание выходных сигналов упомянутого первого цифрового фильтра с конечной импульсной характеристикой и второго цифрового фильтра с конечной импульсной характеристикой, чтобы реализовать фильтр с бесконечной импульсной характеристикой.

В предшествующих примерах был представлен ряд различных конфигураций на основе DSP-модулей, например, как описано относительно фиг. 3 или 4. В некоторых из них отдельные DSP-модули были использованы в целях, отличных от реализации операций фильтра в самом модуле, а скорее, чтобы предоставлять другую обработку, функции хранения или синхронизации с другими DSP-модулями в предложенной системе. Будет понятно, что компоненты и конфигурация DSP-модулей, например, как описано относительно фиг. 3 или 4, и, в частности, наличие свободно доступной таблицы 320 поиска сдвигового регистра и блока 330 памяти делает каждый такой блок фильтра очень гибким и применимым ко многим прикладным задачам помимо реализации операций фильтра. DSP-модули, например, как описано относительно фиг. 3 или 4, могут, например, быть использованы для реализации умножителя, приспособленного для обработки больших, сложных или имеющих знак значений, мультиплексора, сдвигового регистра и т.д.

Фиг. 7 показывает умножитель со знаком, реализованный с помощью фильтра в соответствии с вариантом осуществления.

Умножитель любого желаемого размера может быть реализован с помощью последовательности соединенных DSP-модулей, как описано со ссылкой на фиг. 3 или 4.

47×47-битный умножитель может быть определен на основе следующей декомпозиции:

Рассмотрим:

A[46:0] x B[46:0] =

тогда

A = {A[46:23],A[22:0]} = {A2,A1}

B = {B[46:23],B[22:0]} = {B2,B1}

AxB = {A2,A1} x {B2,B1} = {A2xB2,A1xB2+A2xB1,A1xB1} =

= {P3+(A1xB2+A2xB1 + (A1xB1)[46,23])[46,23], (A1xB2+A2xB1 + (A1xB1)[46,23])[22,0], (A1xB1)[22,0]}

Как подразумевается в выше приведенном, умножитель делит данные на набор из 23 наименее значимых битов (на основе того, что умножитель в настоящем примере обрабатывает 24 имеющих знак битов, при этом один бит отбрасывается, и 23 имеющих знак бита остаются) с одной стороны и набор из 24 наиболее значимых битов с другой стороны. Переключение выполняется между обработкой соответствующего набора наиболее значимых битов и наименее значимых битов, так что соответствующие результаты могут быть объединены в следующем соответствующем DSP-модуле.

Как показано, система содержит четыре DSP-модуля 710, 720, 730, 740, каждый соответствует практически компоновкам, описанным относительно фиг. 3 или 4. В частности, DSP-модуль 710 содержит таблицу 711 поиска сдвигового регистра, конечный автомат 713 синхронизации, соответствующий, например, конечному автомату на фиг. 4, и умножитель 712 и сумматор 714, вместе соответствующие блоку фильтра на фиг. 3 или 4. Как показано, сдвиговый регистр из таблицы 711 поиска сдвигового регистра существует в состоящей из двух частей конфигурации, как описано со ссылкой на фиг. 4 выше, при этом входной сигнал A1 подается в первую секцию сдвигового регистра 711a, а второй входной сигнал B1 подается в первую секцию сдвигового регистра 711b. Каждый сдвиговый регистр 711a, 711b подает данные на соответствующий вход умножителя 712. Выходной сигнал умножителя 712 подается через сумматор 714 на выход 715. Будет понятно, что, поскольку в случае первого DSP-модуля сумматор 714 добавляет ноль к выходному сигналу умножителя, этот компонент может быть в равной степени обойден - он сохраняется в настоящем примере для демонстрации гибкости предложенной архитектуры.

Аналогично, DSP-модуль 720 содержит таблицу 721 поиска сдвигового регистра, конечный автомат 723 синхронизации, соответствующий, например, конечному автомату на фиг. 4, и умножитель 722 и сумматор 724, вместе соответствующие блоку фильтра на фиг. 3 или 4. Как показано, сдвиговый регистр из таблицы 721 поиска сдвигового регистра существует в состоящей из двух частей конфигурации, как описано со ссылкой на фиг. 4 выше, например, посредством операции мультиплексора 426, при этом входной сигнал A1 подается в первую секцию сдвигового регистра 721a, а второй входной сигнал B2 подается в первую секцию сдвигового регистра 721b. Каждый сдвиговый регистр 721a, 721b подает данные на соответствующий вход умножителя 722. Сумматор 724 складывает выходной сигнал умножителя 722 и выходной сигнал 715 предыдущего DSP-модуля 710, подвергнутого переключению между наиболее значимыми битами и наименее значимыми битами в соответствии с декомпозицией выше. Выходной сигнал умножителя 722 подается через сумматор 724 на выход 725.

Аналогично, DSP-модуль 730 содержит таблицу 731 поиска сдвигового регистра, конечный автомат 733 синхронизации, соответствующий, например, конечному автомату на фиг. 4, и умножитель 732 и сумматор 734, вместе соответствующие блоку фильтра на фиг. 3 или 4. Как показано, сдвиговый регистр из таблицы 731 поиска сдвигового регистра существует в состоящей из двух частей конфигурации, как описано со ссылкой на фиг. 4 выше, при этом входной сигнал A2 подается в первую секцию сдвигового регистра 731a, а второй входной сигнал B1 подается в первую секцию сдвигового регистра 731b. Каждый сдвиговый регистр 731a, 731b подает данные на соответствующий вход умножителя 732. Сумматор 734 складывает выходной сигнал умножителя 732 и выходной сигнал 725 предыдущего DSP-модуля 720. Выходной сигнал умножителя 732 подается через сумматор 734 на выход 735.

Аналогично, DSP-модуль 740 содержит таблицу 741 поиска сдвигового регистра, конечный автомат 743 синхронизации, соответствующий, например, конечному автомату на фиг. 4, и умножитель 742 и сумматор 744, вместе соответствующие блоку фильтра на фиг. 3 или 4. Как показано, сдвиговый регистр из таблицы 741 поиска сдвигового регистра существует в состоящей из двух частей конфигурации, как описано со ссылкой на фиг. 4 выше, при этом входной сигнал A2 подается в первую секцию сдвигового регистра 741a, а второй входной сигнал B2 подается в первую секцию сдвигового регистра 741b. Каждый сдвиговый регистр 741a, 741b подает данные на соответствующий вход умножителя 742. Сумматор 744 складывает выходной сигнал умножителя 742 и выходной сигнал 735 предыдущего DSP-модуля 730, подвергнутого переключению между наиболее значимыми битами и наименее значимыми битами в соответствии с декомпозицией выше. Выходной сигнал умножителя 742 подается через сумматор 744 на выход 745.

Выходной компонент P[22:0] является доступным, подверженным надлежащей корректировке тактирования, на выходе 715. Выходной компонент P[45:23] является доступным, подверженным надлежащей корректировке тактирования, на выходе 735. Выходной компонент P[93:46] является доступным, подверженным надлежащей корректировке тактирования, на выходе 745.

Соответствующие сдвиговые регистры 711a, 711b, 721a, 721b, 731a, 731b, 741a, 741b, как описано выше, используются в описанной конфигурации, чтобы обеспечивать синхронизацию сигналов через умножитель, так что значения на каждом выходе в любом заданном тактовом цикле соответствуют одинаковому набору входных значений A1, B1, A2 и B2. В качестве примера, сдвиговые регистры 711a, 711b могут, каждый, предоставлять однотриггерную стоимость задержки для своих соответствующих сигналов, сдвиговые регистры 721a, 721b могут, каждый, предоставлять двухтриггерную стоимость задержки для своих соответствующих сигналов, сдвиговые регистры 731a, 731b могут, каждый предоставлять трехтриггерную стоимость задержки для своих соответствующих сигналов, а сдвиговые регистры 741a, 741b могут, каждый, предоставлять четырехтриггерную стоимость задержки своих соответствующих сигналов. В некоторых вариантах осуществления DSP-блоки могут предусматривать множество входных регистров специально для этой цели, которые могут быть использованы вместо или также как и сдвиговые регистры из таблицы поиска сдвигового регистра. Например, когда реализация конкретного DSP-блока предусматривает два входных регистра, первый и второй DSP-блоки могут полагаться исключительно на этих выделенные входные регистры для синхронизации, тогда как третий и четвертый регистры могут использовать выделенные входные регистры для двух уровней задержки и затем использовать сдвиговые регистры из таблицы поиска сдвигового регистра, чтобы предоставлять один дополнительный уровень задержки, требуемый для третьего DSP-модуля, и два уровня задержки, требуемых для четвертого DSP-модуля. Кроме того, операции задержки могут быть обработаны по-разному для A-входа и B-входа каждого DSP-модуля на этой основе, в зависимости от доступных выделенных входных реле.

Как показано, каждый DSP-модуль предусматривает дополнительное реле между умножителем 712, 722, 732, 742 и сумматором 714, 724, 734, 744 и между сумматором 714, 724, 734, 744 и выходом 715, 725, 735, 745 в целях синхронизации. Некоторые или все эти реле могут быть пропущены в зависимости от особенностей реализации некоторых вариантов осуществления, или дополнительные реле могут быть предусмотрены в зависимости от требований применения для данной реализации.

Использование SRL для DSP-блоков для имитации дополнительных требуемых регистров для тактирования умножающего вычисления составляет пример использования DSP-модулей, как описано со ссылкой на фиг. 3 или 4 во втором режиме работы.

В этом втором режиме работы, как показано относительно фиг. 7, таблица поиска сдвигового регистра DSP-модуля используется в качестве входного регистра умножителя.

Соответственно описывается гибкий модуль цифрового сигнального процессора, содержащий блок фильтра, содержащий умножитель и сумматор, когда умножитель принимает входной сигнал от памяти и таблицы поиска сдвигового регистра. Модуль цифрового сигнального процессора может реализовывать цифровые фильтры, такие как FIR или IIR-фильтры, предоставляя подходящие коэффициенты фильтра из памяти и значения данных из таблицы поиска сдвигового регистра. Необязательный конечный автомат может обеспечивать синхронизацию адресации памяти и таблицы поиска сдвигового регистра, и между множеством экземпляров модуля цифрового сигнального процессора, когда они требуются для конкретной реализации фильтра. Предложенная архитектура предлагает дополнительные режимы работы, в которых поддерживаются операции, отличные от реализаций фильтра.

На этой основе, во втором режиме работы значения, сохраненные в таблице поиска сдвигового регистра, выводятся для обработки, отличной от обработки посредством цифрового фильтра.

Фиг. 8 представляет способ выполнения работы цифрового сигнального процессора в соответствии с вариантом осуществления.

Как показано, способ начинается на этапе 800 перед переходом к этапу 810, на котором таблица поиска сдвигового регистра адресуется для вывода данных в цифровой сигнальный процессор в первом режиме работы. Способ затем переходит к этапу 820, на котором память фильтра адресуется, чтобы предоставлять коэффициенты цифровому фильтру в первом режиме работы. Способ затем переходит к этапу 830 выполнения операции цифрового фильтра над входными данными с помощью коэффициента перед завершением на этапе 840.

Способ на фиг. 8 может быть выполнен итеративно, для каждого из множества коэффициентов, определяющих цифровой фильтр.

Этапы 810 и 820 могут быть выполнены в противоположном порядке, т.е., этап 820 перед 810, или оба могут быть выполнены параллельно.

Способ может содержать дополнительный этап структурирования таблицы поиска сдвигового регистра и памяти фильтра, так что одно значение адреса ссылается на соответствующие коэффициенты и входные данные для цифрового фильтра в первом режиме работы, так что этапы адресации таблицы поиска сдвигового регистра для вывода данных в цифровой сигнальный процессор в первом режиме работы и адресации памяти фильтра для предоставления коэффициентов цифровому фильтру в первом режиме работы выполняются с помощью упомянутого одного значения адреса.

В некоторых случаях способа на фиг. 8 операция цифрового фильтра может быть операцией фильтра с конечной импульсной характеристикой.

В некоторых примерах способа на фиг. 8 операция цифрового фильтра является операцией фильтра с бесконечной импульсной характеристикой, содержащей первую операцию с конечной импульсной характеристикой и вторую операцию с конечной импульсной характеристикой на основе значений обратной связи, способ содержит дополнительный этап предоставления включающих сигналов, координирующих сочетание результатов первой операции с конечной импульсной характеристикой и второй операции с конечной импульсной характеристикой, чтобы получать результат фильтра с бесконечной импульсной характеристикой.

В некоторых вариантах осуществления способы и операции, описанные в данном документе, могут быть реализованы в целом или частично посредством вычислительного устройства. Эти способы и процессы могут быть реализованы посредством прикладных компьютерных программ или служб, прикладного программного интерфейса (API), библиотеки и/или другого компьютерного программного продукта, либо любого сочетания таких сущностей. В частности, может быть предоставлена программа для компьютера, содержащая инструкции, приспособленные для реализации этапов способа на фиг. 8, или любого из его вариантов, описанных выше.

Должно быть понятно, что конфигурации и/или подходы, описанные в данном документе, являются примерными по своей природе, и что эти конкретные варианты осуществления или примеры не должны рассматриваться в ограничивающем смысле, поскольку возможны многочисленные вариации. Конкретные алгоритмы или способы, описанные в данном документе, могут представлять одну или более из любого числа стратегий обработки. По существу, различные иллюстрированные и/или описанные действия могут быть выполнены в иллюстрированной и/или описанной последовательности, в других последовательностях, параллельно или опущены. Также, порядок вышеописанных процессов может быть изменен.

Предмет изучения настоящего изобретения включает в себя все новые и неявные комбинации и подкомбинации различных процессов, систем и конфигураций, и другие признаки, функции, действия и/или свойства, раскрытые в данном документе, также как любые или все их эквиваленты.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ И СИСТЕМА ВЫЧИСЛЕНИЯ УКАЗАТЕЛЯ ДЛЯ МАСШТАБИРУЕМОГО ПРОГРАММИРУЕМОГО КОЛЬЦЕВОГО БУФЕРА | 2006 |

|

RU2395835C2 |

| ПРИЕМНИК СПУТНИКОВОЙ НАВИГАЦИИ С УСТРОЙСТВОМ БЫСТРОГО ПОИСКА НАВИГАЦИОННЫХ СИГНАЛОВ В УСЛОВИЯХ ВЫСОКОЙ ДИНАМИКИ ОБЪЕКТА | 2006 |

|

RU2341898C2 |

| СПОСОБ ОБРАБОТКИ СИГНАЛОВ СВЯЗИ В АБОНЕНТСКОМ ПУНКТЕ БЕСПРОВОДНОЙ СИСТЕМЫ ЭЛЕКТРОСВЯЗИ | 1990 |

|

RU2159007C2 |

| МАТРИЧНО-ВЕКТОРНЫЙ УМНОЖИТЕЛЬ С НАБОРОМ РЕГИСТРОВ ДЛЯ ХРАНЕНИЯ ВЕКТОРОВ, СОДЕРЖАЩИМ МНОГОПОРТОВУЮ ПАМЯТЬ | 2019 |

|

RU2795887C2 |

| АБОНЕНТСКИЙ ПУНКТ В СИСТЕМЕ БЕСПРОВОДНОЙ ЦИФРОВОЙ ТЕЛЕФОННОЙ СВЯЗИ | 1990 |

|

RU2154360C2 |

| СХЕМЫ ПОЛУЧЕНИЯ ОПОРНОГО СИГНАЛА ГАШЕНИЯ ТЕНИ ДЛЯ ТЕЛЕВИЗИОННОГО ПРИЕМНИКА И ВИДЕОМАГНИТОФОНА | 1993 |

|

RU2126599C1 |

| АБОНЕНТСКИЙ ПУНКТ В АБОНЕНТСКОЙ СИСТЕМЕ БЕСПРОВОДНОЙ СВЯЗИ | 1990 |

|

RU2138122C1 |

| РАДИОТЕЛЕФОННАЯ СИСТЕМА ДЛЯ ГРУПП УДАЛЕННЫХ АБОНЕНТОВ | 2004 |

|

RU2341038C2 |

| Цифровой фильтр | 1988 |

|

SU1555826A1 |

| ГЕНЕРАТОР ТОНАЛЬНЫХ СИГНАЛОВ СО ЗВУКОВЫМИ ЭФФЕКТАМИ (ВАРИАНТЫ) | 1995 |

|

RU2143751C1 |

Настоящее изобретение относится к архитектурам цифрового сигнального процессора. Техническим результатом изобретения является предоставление DSP-архитектуры, предоставляющей более объединенную функциональность, в то же время сохраняющей высокую степень универсальности. Программируемый цифровой сигнальный процессор содержит цифровой фильтр, таблицу поиска сдвигового регистра, память фильтра и конечный автомат. Цифровой фильтр содержит умножитель и накапливающий сумматор. Умножитель принимает входные данные из памяти фильтра и таблицы поиска сдвигового регистра. Таблица поиска сдвигового регистра содержит сдвиговый регистр, содержащий триггеры. Конечный автомат предоставляет значения адресации в таблицу поиска сдвигового регистра и память фильтра. Значения адресации содержат один адрес для таблицы поиска сдвигового регистра и памяти фильтра. 2 н. и 7 з.п. ф-лы, 8 ил.

1. Программируемый цифровой сигнальный процессор, содержащий цифровой фильтр, причем упомянутый цифровой фильтр содержит умножитель, сконфигурированный с возможностью умножения значений входных данных и значений коэффициентов фильтра, и накапливающий сумматор, накапливающий последовательные выходные сигналы от умножителя, таблицу поиска сдвигового регистра и память фильтра, при этом упомянутая таблица поиска сдвигового регистра содержит сдвиговый регистр, содержащий триггеры, причем упомянутая таблица поиска сдвигового регистра включается для предоставления входных данных упомянутому цифровому фильтру в первом режиме работы, и упомянутая память фильтра включается для предоставления коэффициентов фильтра упомянутому цифровому фильтру в упомянутом первом режиме работы, при этом выходные сигналы упомянутой памяти фильтра и упомянутой таблицы поиска сдвигового регистра синхронизируются таким образом, чтобы создавать соответствующие коэффициенты фильтра и входные данные, вместе реализующие желаемую конфигурацию фильтра,

причем программируемый цифровой сигнальный процессор дополнительно содержит конечный автомат, причем упомянутый конечный автомат предоставляет значения адресации в упомянутую таблицу поиска сдвигового регистра и упомянутую память фильтра,

при этом упомянутые значения адресации содержат один адрес для упомянутой таблицы поиска сдвигового регистра и упомянутой памяти фильтра, посредством чего значения, сохраненные в упомянутой таблице поиска сдвигового регистра и упомянутой памяти фильтра, структурированы так, что упомянутый один адрес ссылается на упомянутые соответствующие коэффициенты фильтра и входные данные для упомянутого цифрового фильтра в упомянутом первом режиме работы.

2. Программируемый цифровой сигнальный процессор по п. 1, при этом упомянутая таблица поиска сдвигового регистра содержит сдвиговый регистр, при этом упомянутый сдвиговый регистр конфигурируется таким образом, чтобы работать либо в качестве одного непрерывного сдвигового регистра, либо в качестве множества независимо функционирующих сдвиговых регистров.

3. Программируемый цифровой сигнальный процессор по любому предшествующему пункту, при этом во втором режиме работы значения, сохраненные в упомянутой таблице поиска сдвигового регистра, выводятся так, чтобы имитировать дополнительные требуемые регистры для тактирования умножающего вычисления.

4. Программируемый цифровой сигнальный процессор по любому предшествующему пункту, при этом упомянутый цифровой фильтр является компонентом фильтра с конечной импульсной характеристикой.

5. Программируемый цифровой сигнальный процессор по любому из пп. 1-4, при этом упомянутый цифровой фильтр является компонентом фильтра с бесконечной импульсной характеристикой, содержащий первый фильтр с конечной импульсной характеристикой и второй фильтр с конечной импульсной характеристикой в конфигурации с обратной связью, где упомянутый конечный автомат предоставляет включающие сигналы, координирующие сочетание выходных сигналов упомянутого первого фильтра с конечной импульсной характеристикой и упомянутого второго фильтра с конечной импульсной характеристикой для реализации упомянутого фильтра с бесконечной импульсной характеристикой.

6. Программируемый цифровой сигнальный процессор по любому предшествующему пункту, при этом упомянутый цифровой сигнальный процессор реализуется в FPGA-архитектуре, содержащей множество таблиц поиска, конфигурация каждой упомянутой таблицы поиска определяется посредством одного или более соответствующих блоков памяти, запрограммированных при инициировании системы с помощью конфигурационного битового потока, при этом значения в упомянутой памяти фильтра также программируются посредством упомянутого конфигурационного битового потока.

7. Способ выполнения операции цифрового сигнального процессора, упомянутый способ содержит этапы, на которых:

адресуют таблицу поиска сдвигового регистра, чтобы выводить данные в упомянутый цифровой сигнальный процессор в первом режиме работы, и адресуют память фильтра, чтобы предоставлять коэффициенты фильтра упомянутому цифровому фильтру в упомянутом первом режиме работы, выполняют операцию цифрового фильтра над упомянутыми входными данными с помощью упомянутых коэффициентов фильтра, причем упомянутый способ содержит дополнительный этап, на котором структурируют упомянутую таблицу поиска сдвигового регистра и упомянутую память фильтра так, что одно значение адреса ссылается на соответствующие коэффициенты фильтра и входные данные для упомянутого цифрового фильтра в упомянутом первом режиме работы, так что упомянутые этапы адресации таблицы поиска сдвигового регистра, чтобы выводить коэффициенты фильтра в упомянутый цифровой сигнальный процессор в первом режиме работы, и адресации памяти фильтра, чтобы предоставлять входные данные упомянутому цифровому фильтру в упомянутом первом режиме работы, выполняются с помощью упомянутого одного значения адреса.

8. Способ по п. 7, при этом упомянутая операция цифрового фильтра является операцией фильтра с конечной импульсной характеристикой.

9. Способ по п. 7 или 8, при этом упомянутая операция цифрового фильтра является операцией фильтра с бесконечной импульсной характеристикой, содержащей первую операцию с конечной импульсной характеристикой и вторую операцию с конечной импульсной характеристикой на основе значений обратной связи, упомянутый способ содержит дополнительный этап, на котором предоставляют включающие сигналы, координирующие сочетание результатов упомянутой первой операции с конечной импульсной характеристикой и упомянутой второй операции с конечной импульсной характеристикой, чтобы получать результат фильтра с бесконечной импульсной характеристикой.

Авторы

Даты

2022-04-11—Публикация

2019-06-19—Подача