ел ел ел эо

S3 3

Изобретение относится к вычислительной технике и может быть использовано в системах цифровой обработки сейсмических, акустических и других сигналов.

Цель изобретения - повышение быстродействия.

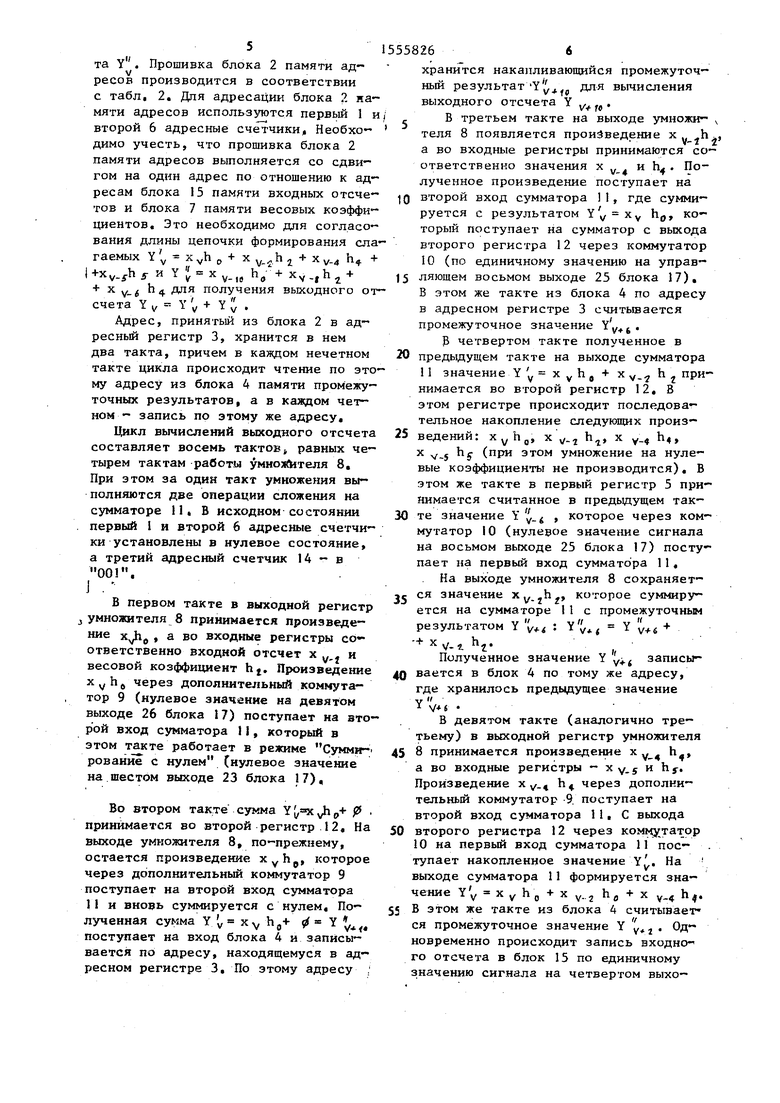

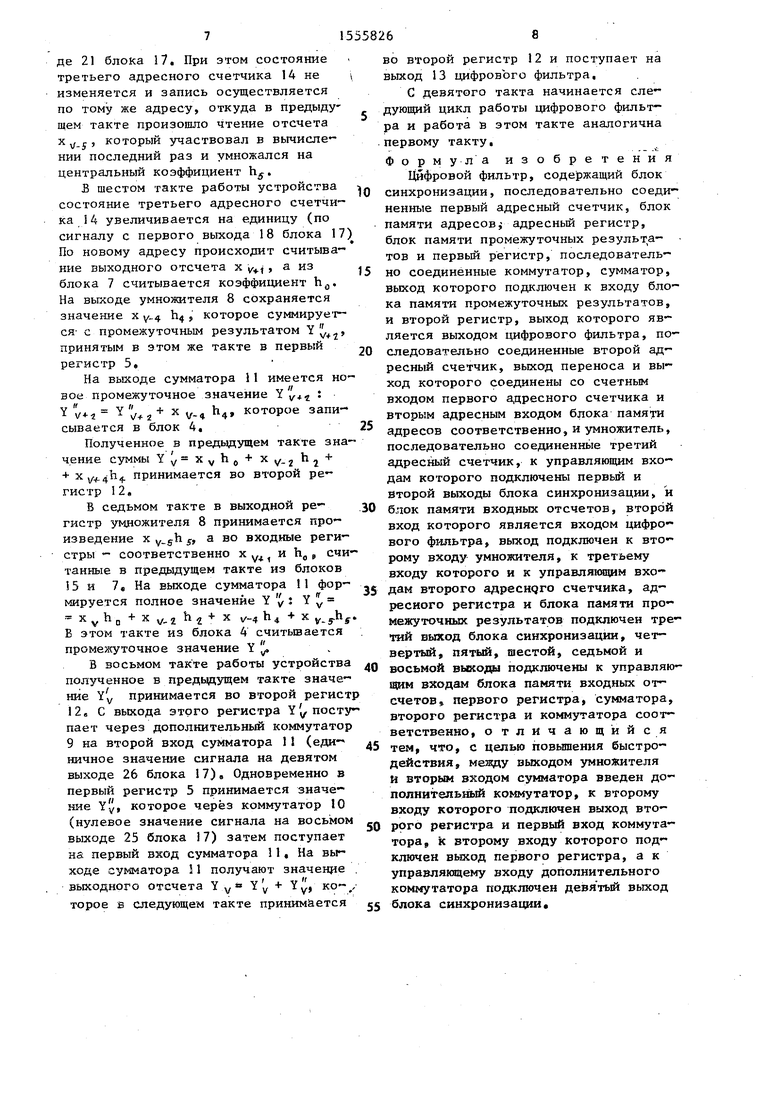

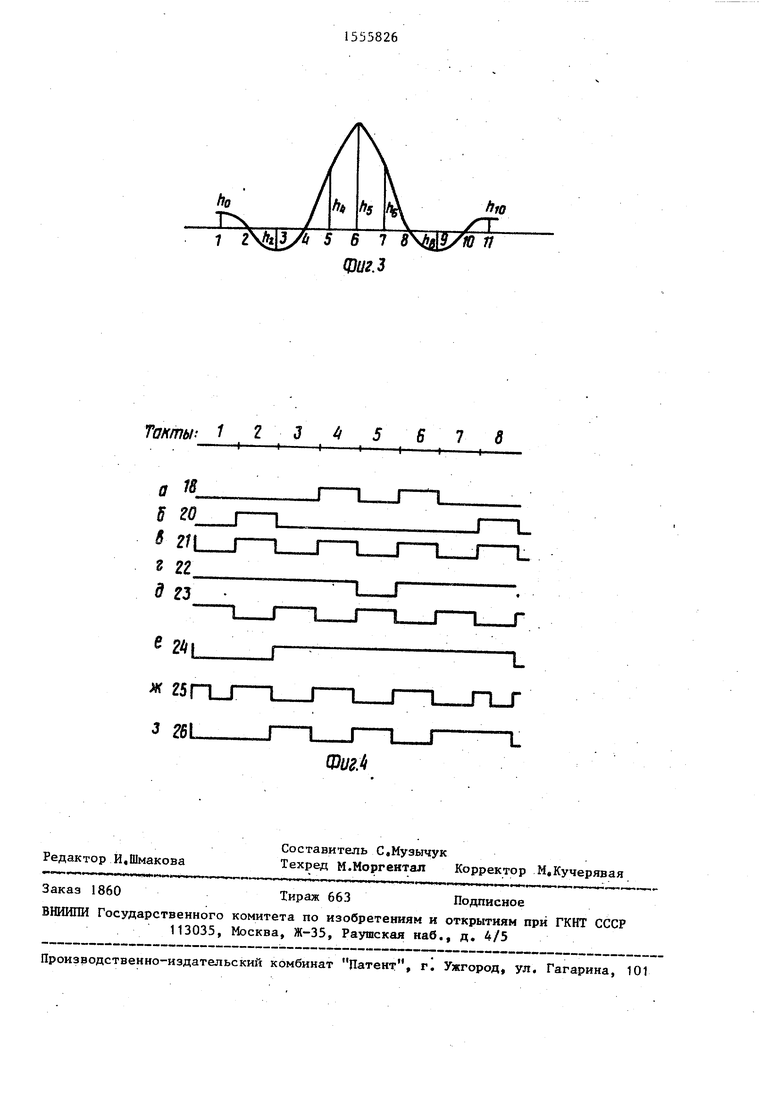

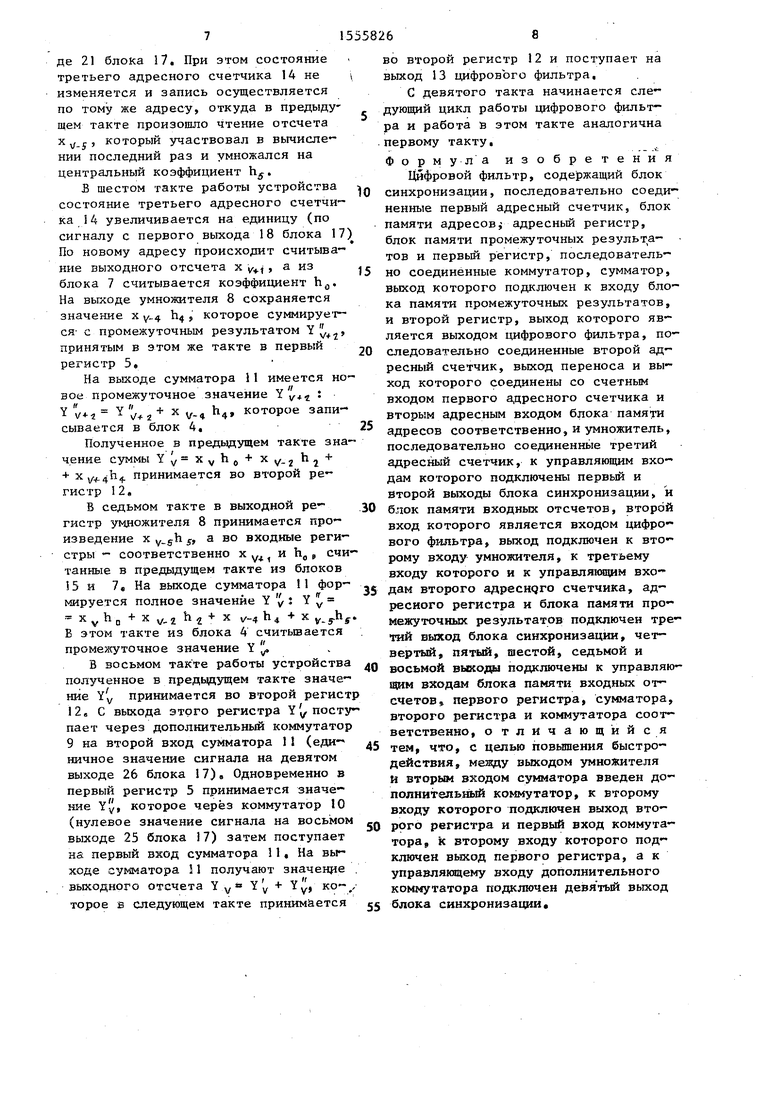

На фиг,1 приведена электрическая структурная схема цифрового фильтра; на фиг.2 - структурная электрическая схема блока синхронизации; на фигеЗ - пример импульсной характеристики цифрового фильтра; на фиг«4- временные диаграммы управляющих сигналов в

Цифровой фильтр содержит первый адресный счетчик 1, блок 2 памяти адресов, адресный регистр 3, блок 4 памяти промежуточных результатов, первый регистр 5, второй адресный счетчик 6, блок 7 памяти весовых коэффициентов, умножитель 8, допдлни- тельный коммутатор 9, коммутатор 10,

ле (1) результаты умножения xvh,

31V- ч

XV-4.V

х v.f h5 запоминают10

15

20

ся и накапливаются в блоке 4 памяти х промежуточных результатов. Промежуточные полученные результаты используются при получении входных отсчетов YV-MO Yv+4 Yv Произведение выходного стсчета на центральный коэффициент Ху. хранится, так как оно принимает участие в вычислениях только один раз.

Рассмотрим вычисление U-ro выходного отсчета фильтра Yv при длине ИХ N 11, В этом случае третий адресный счетчик 14 работает по модулю Ml (N+l)/2 , второй адресный счетчик 6 - по модулю М2 (М1+1)/2 4, первый адресный счетчик 1 - по модулю МЗ N - 1 10. С целью упрощения описания работы цифрового фильтра будем считать, что прием информации во все регистры, умножитель, переключение счетчиков осу- сумматор 11, второй регистр 12, вы- 25 ществляется положительным перепадом

синхроимпульсов, режиму записи в блоки 4 и 15 соответствует нулевое значение на управляющем входе, а режиму чтения - единичное; сигналу переноса 30 счетчиков соответствует нулевое значение на выходе переноса; нулевое значение на управляющем входе сумматора 11 соответствует режиму Суммирование с нулем, а единичное значение - режиму обычного суммирования. Цифровой фильтр осуществляет фильт- 5 Адресация блока 15 памяти входных

отсчетов обеспечивается третьим адресным счетчиком 14, причем по синхроимпульсу на первом выходе 18 блока 17 синхронизации его значение изменяется на единицу, а по синхроимпульсу на втором выходе 19 - на две единицы. Последовательность адресов, формируемых для записи входных от- АС счетов в блок 15, а также для чтения исходных данных из него, приводится

ход 13, третий адресный счетчик 14, блок 15 памяти входных отсчетов, вход 16, блок 17 синхронизации, выходы 18-26 блока 17 синхронизации,

Блок 17 синхронизации содержит счетчик 27, блок 28 постоянной памяти и генератор 29 тактовых импульсов.

рацию входного сигнала согласно выражению

N-1

I

х v Ч

(1)

40

где h - весовые коэффициенты;

V- П

N

-отсчеты входного сигнала;

-длина импульсной характеристики (ИХ).

Для иллюстрации работы цифрового фильтра рассмотрим в качестве примера реализацию цифрового фильтра с импульсной характеристикой, представленной на фиг,3

Общее число коэффициентов равно 11, В силу симметрии общее число ненулевых коэффициентов равно (Ы+О/2+1 « 7, а число различных ненулевых коэффициентов равно 4 (3 боковых и 1 центральный). Для получе- , ния выходного отсчета Yy по форму50

55

в табл. 1

Для адресации блока 7 памяти весовых коэффициентов используется второй- адресный счетчик 6, который изменяет свое состояние по сигналу с третьего выхода 20 блока I7, Для адресации блока 4 памяти промежуточных результатов используется блок 2 памяти адресов, в котором хранятся адреса записи получаемых промежуточных результатов и адрес чтения накопленного промежуточного результале (1) результаты умножения xvh,

31V- ч

XV-4.V

х v.f h5 запоминают

ся и накапливаются в блоке 4 памяти х промежуточных результатов. Промежуточные полученные результаты используются при получении входных отсчетов YV-MO Yv+4 Yv Произведение выходного стсчета на центральный коэффициент Ху. хранится, так как оно принимает участие в вычислениях только один раз.

Рассмотрим вычисление U-ro выходного отсчета фильтра Yv при длине ИХ N 11, В этом случае третий адресный счетчик 14 работает по модулю Ml (N+l)/2 , второй адресный счетчик 6 - по модулю М2 (М1+1)/2 4, первый адресный счетчик 1 - по модулю МЗ N - 1 10. С целью упрощения описания работы цифрового фильтра будем считать, что прием информации во все регистры, ум

в табл. 1

Для адресации блока 7 памяти весовых коэффициентов используется второй- адресный счетчик 6, который изменяет свое состояние по сигналу с третьего выхода 20 блока I7, Для адресации блока 4 памяти промежуточных результатов используется блок 2 памяти адресов, в котором хранятся адреса записи получаемых промежуточных результатов и адрес чтения накопленного промежуточного результата У. Прошивка блока 2 памяти адресов производится в соответствии с табл, 2. Для адресации блока 2 на- мяти адресов используются первый 1 и( второй 6 адресные счетчики, Необхо- димо учесть, что прошивка блока 2 памяти адресов выполняется со сдвигом на один адрес по отношению к адресам блока 15 памяти входных отсчетов и блока 7 памяти весовых коэффициентов. Это необходимо для согласования длины цепочки формирования слагаемых Y v х vh „ + х h г + x h + f и Y I x () h/+ xv.fh4 + + x h 4. для получения выходного отсчета Y v Y „ + Y .

Адрес, принятый из блока 2 в адресный регистр 3, хранится в нем два такта, причем в каждом нечетном такте цикла происходит чтение по этому адресу из блока 4 памяти промежуточных результатов, а в каждом четном - запись по этому же адресу

Цикл вычислений выходного отсчета составляет восемь тактов равных четырем тактам работы умножителя 8. При этом за один такт умножения выполняются две операции сложения на сумматоре 11. В исходном состоянии первый 1 и второй 6 адресные счетчики установлены в нулевое состояние, а третий адресный счетчик 14 - в 001.

В первом такте в выходной регистр умножителя 8 принимается произведение Xyha , а во входные регистры соответственно входной отсчет х „ f и весовой коэффициент ht. Произведение xvne через дополнительный коммутатор 9 (нулевое значение на девятом выходе 26 блока 17) поступает на второй вход сумматора 1I, который в

В девятом такте (аналогич тьему) в выходной регистр ум

этом такте работает в режиме Сумми- 45 8 принимается произведение х рование с нулем (нулевое значение на шестом выходе 23 блока I7),

а во входные регистры - х y.s

Произведение х h через до тельный коммутатор 9 поступае второй вход сумматора 11. С в 50 второго регистра 12 через ком 10 на первый вход сумматора 1 тупает накопленное значение Y выходе сумматора 11 формирует чение Y ., х ., h „ + х ... „ h „ +

Во втором такте сумма 0 . принимается во второй регистр 12, На выходе умножителя 8, по-прежнему, остается произведение xvhe, которое через дополнительный коммутатор 9 поступает на второй вход сумматора 11 и вновь суммируется с нулем, Полученная сумма Y

х

V V

4

V

1

поступает на вход блока 4 и записывается по адресу, находящемуся в адресном регистре 3. По этому адресу

хранится накапливающийся промежуточный результат для вычисления выходного отсчета Y v+.t

В третьем такте на выходе умножи- ч теля 8 появляется произведение х . -h, а во входные регистры принимаются соответственно значения х v и h. Полученное произведение поступает на второй вход сумматора 11, где сумми-

руется с результатом Y V. X,

о

который поступает на сумматор с выхода второго регистра 12 через коммутатор 10 (по единичному значению на управ- ляющем восьмом выходе 25 блока 17). В этом же такте из блока 4 по адресу в адресном регистре 3 считывается

промежуточное значение Y1

V+b

5

0

5

В четвертом такте полученное в 0 предыдущем такте на выходе сумматора 11 значение + x v.2 h г при нимается во второй регистр 12, В этом регистре происходит последовательное накопление следующих произ- х ,/..„ п„, х Ь4,

ведений: х v h0,

V-4

х hj (при этом умножение на нулевые коэффициенты не производится). В этом же такте в первый регистр 5 при- нимается считанное в предыдущем такте значение Y , которое через коммутатор 10 (нулевое значение сигнала на восьмом выходе 25 блока 17) поступает на первый вход сумматора 11,

На выходе умножителя 8 сохраняется значение xv h, которое суммируется на сумматоре 11 с промежуточным

результатом Y v+t : Y yA Y

v+t

+ x

.

ft

Полученное значение Y v+t записывается в блок 4 по тому же адресу, где хранилось предыдущее значение

v

I у

В девятом такте (аналогично третьему) в выходной регистр умножителя

8 принимается произведение х

8 принимается произведение х

V-4 « а во входные регистры - х y.s и hf.

Произведение х h через дополнительный коммутатор 9 поступает на второй вход сумматора 11. С выхода второго регистра 12 через коммутатор 10 на первый вход сумматора 11 поступает накопленное значение Y . На выходе сумматора 11 формируется значение Y ., х ., h „ + х ... „ h „ +х

V-4

В этом же такте из блока 4 ся промежуточное значение Y

считывает

v г °Д новременно происходит запись входно

го отсчета в блок 15 по единичному значению сигнала на четвертом выходе 21 блока 17. При этом состояние третьего адресного счетчика 14 не изменяется и запись осуществляется по тому же адресу, откуда в предыду щем такте произошло чтение отсчета х sj который участвовал в вычислении последний раз и умножался на центральный коэффициент h5.

В шестом такте работы устройства состояние третьего адресного счетчика 14 увеличивается на единицу (по сигналу с первого выхода 18 блока 17) По новому адресу происходит считывание выходного отсчета х 1, а из блока 7 считывается коэффициент Ь0. На выходе умножителя 8 сохраняется значение х 4 которое суммируется с промежуточным результатом Y , принятым в этом же такте в первый регистр 5,

На выходе сумматора i1 имеется новое промежуточное значение Y у+4 : Y Vj Y 2 + х v-4 h4 которое записывается в блок 4.

Полученное в предыдущем такте значение суммы + х v 2 h + + принимается во второй регистр 12.

В седьмом такте в выходной ре- гистр умножителя 8 принимается произведение х 5, а во входные регистры - соответственно х V4 f и h0„ считанные в предыдущем такте из блоков 15 и 7, На выходе сумматора 1 фор- мируется полное значение Y j Y v xvhB+xv zh2+x V,4h4+xv 5.hff

8этом такте из блока 4 считывается промежуточное значение Y J.

В восьмом такте работы устройства полученное в предыдущем такте значение Y V принимается во второй регистр 12„ С выхода этого регистра Y v поступает через дополнительный коммутатор

9на второй вход сумматора 11 (еди- ничное значение сигнала на девятом выходе 26 блока 17) Одновременно в первый регистр 5 принимается значение Y, которое через коммутатор 10 (нулевое значение сигнала на восьмом выходе 25 блока 17) затем поступает

на первый вход сумматора 11, На выходе сумматора 51 получают значение выходного отсчета Y v Y v + Yy, ко-,, торое в следующем такте принимается

во второй регистр 12 и поступает на выход 13 цифрового фильтра,

С девятого такта начинается следующий цикл работы цифрового фильтра и работа в этом такте аналогична первому такту. Формула изобретения

Цифровой фильтр, содержащий блок синхронизации, последовательно соединенные первый адресный счетчик, блок памяти адресов адресный регистр, блок памяти промежуточных результатов и первый регистр, последовательно соединенные коммутатор, сумматор, выход которого подключен к входу блока памяти промежуточных результатов, и второй регистр, выход которого является выходом цифрового фильтра, последовательно соединенные второй адресный счетчик, выход переноса и выход которого соединены со счетным входом первого адресного счетчика и вторым адресным входом блока памяти адресов соответственно,и умножитель, последовательно соединенные третий адресный счетчик, к управляющим входам которого подключены первый и второй выходы блока синхронизации, и бцок памяти входных отсчетов, второй вход которого является входом цифрового фильтра, выход подключен к второму входу умножителя, к третьему входу которого и к управляющим входам второго адресного счетчика, адресного регистра и блока памяти промежуточных результатов подключен третий выход блока синхронизации, четвертый, пятый, шестой, седьмой и восьмой выходы подключены к управляющим входам блока памяти входных отсчетов первого регистра, сумматора, второго регистра и коммутатора соответственно, отличающийся тем, что, с целью повышения быстродействия, между выходом умножителя и вторым входом сумматора введен дополнительный коммутатор, к второму входу которого подключен выход второго регистра и первый вход коммутатора , к второму входу которого подключен выход первого регистра, а к управляющему входу дополнительного коммутатора подключен девятый выход блока синхронизации

1555826

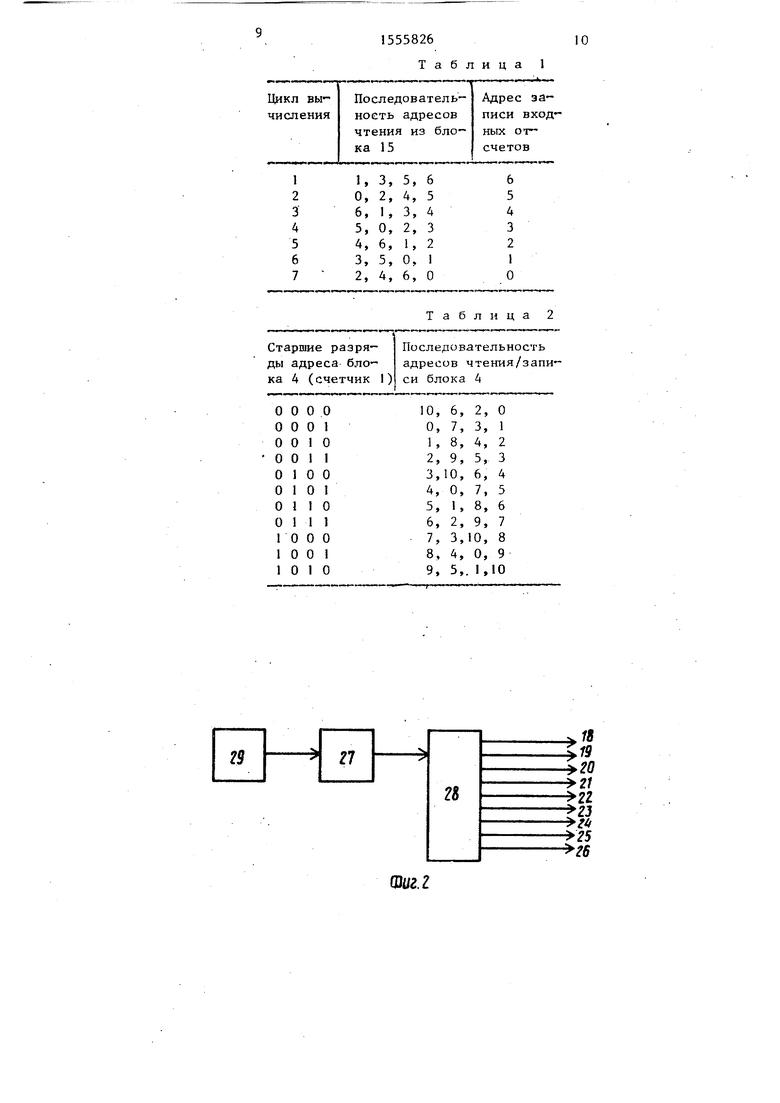

Таблица 1

10

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой фильтр | 1986 |

|

SU1357976A1 |

| Цифровой фильтр | 1987 |

|

SU1501088A1 |

| Цифровой фильтр | 1986 |

|

SU1387015A1 |

| Устройство для цифровой фильтрации | 1985 |

|

SU1381541A1 |

| Устройство для цифровой фильтрации | 1985 |

|

SU1325511A1 |

| Цифровой анализатор спектра | 1985 |

|

SU1256044A1 |

| Устройство для цифровой фильтрации | 1984 |

|

SU1264306A1 |

| Специализированный процессор для цифровой фильтрации | 1989 |

|

SU1631558A1 |

| Цифровой фильтр | 1983 |

|

SU1145346A1 |

| Устройство для цифровой фильтрации | 1986 |

|

SU1377872A1 |

Изобретение относится к вычислительной технике. Цель изобретения - повышение быстродействия. Цифровой фильтр содержит адресные счетчики 1,6 и 14, блок памяти (БП) 2 адресов, адресный регистр 3, БП 4 промежуточных результатов, регистры 5 и 12, БП 7 весовых коэффициентов, умножитель 8, коммутаторы 9 и 10, сумматор 11, БП 15 входных отсчетов и блок 17 синхронизации. Цель достигается введением коммутатора 9, с помощью которого цикл вычисления выходного отсчета фильтра осуществляется за восемь тактов. 4 ил., 2 табл.

1

2 3 4 5 6 7

Старшие разряды адреса блока 4 (счетчик I)

000 001 О

О О

000 001 010

1 1 1

0о

01

1О

11

6 5 4 3 2 I О

Таблица 2

Последовательность адресов чтения/записи блока 4

/

Л

Л

5

72 Јli/4 567 8 4d9/fO П

фиг.з

Таты- 12345 678

1111111

з 26i

5

V

Ью ST

| Цифровой фильтр | 1986 |

|

SU1357976A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-04-07—Публикация

1988-04-04—Подача