ПРЕДПОСЫЛКИ ИЗОБРЕТЕНИЯ

[0001] Система печати в качестве одного примера системы выброса текучей среды может включать в себя печатающую головку, источник чернил, который подает жидкие чернила в печатающую головку, и электронный контроллер, который управляет печатающей головкой. Печатающая головка выбрасывает капли текучей среды для печати через множество активаторов текучей среды или дюз на носитель печати. Печатающие головки могут включать в себя тепловые или пьезоэлектрические печатающие головки, изготовленные на полупроводниковых пластинах или кристаллах интегральной схемы. Сначала изготавливаются приводная электроника и управляющие элементы, затем добавляются столбцы нагревательных резисторов, и, наконец, добавляются структурные слои, например, сформированные из эпоксидной смолы с возможностью формирования фотоизображений, и обрабатываются с формированием микроструйных эжекторов или генераторов капель. В некоторых примерах микроструйные эжекторы располагаются в по меньшей мере одном столбце или матрице, благодаря чему выброс чернил из дюз в надлежащем порядке вызывает печать знаков или других изображений на носителе печати, когда печатающая головка и носитель печати перемещаются относительно друг друга. Другие системы выброса текучей среды включают в себя системы трехмерной печати или другие системы высокоточного распределения текучей среды, например, для естественнонаучных, лабораторных, криминалистических или фармацевтических применений. Подходящие текучие среды могут включать в себя чернила, агенты печати или любую другую текучую среду, используемые этими системами выброса текучей среды.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

[0002] Некоторые примеры описаны в нижеследующем подробном описании и со ссылкой на чертежи, на которых:

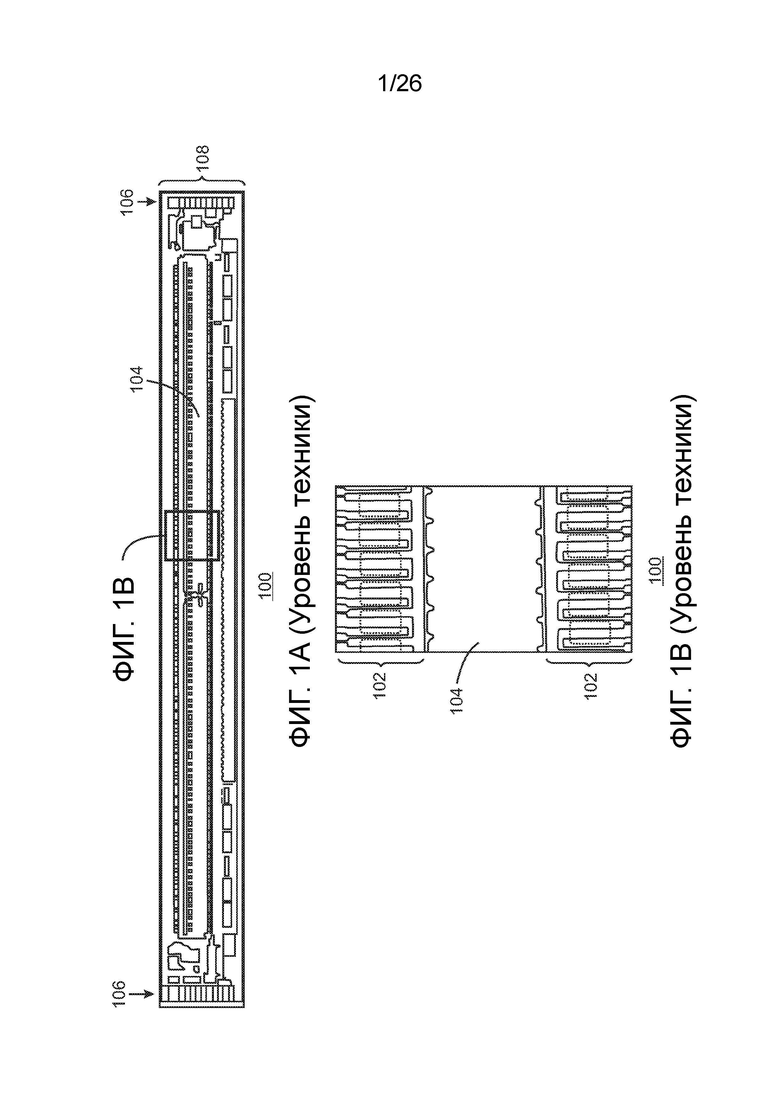

[0003] фиг. 1A - вид части матрицы, используемой для головки струйной печати уровня техники;

[0004] фиг. 1B - увеличенный вид участка матрицы;

[0005] фиг. 2A - вид примера матрицы, используемой для печатающей головки;

[0006] фиг. 2B - увеличенный вид участка матрицы;

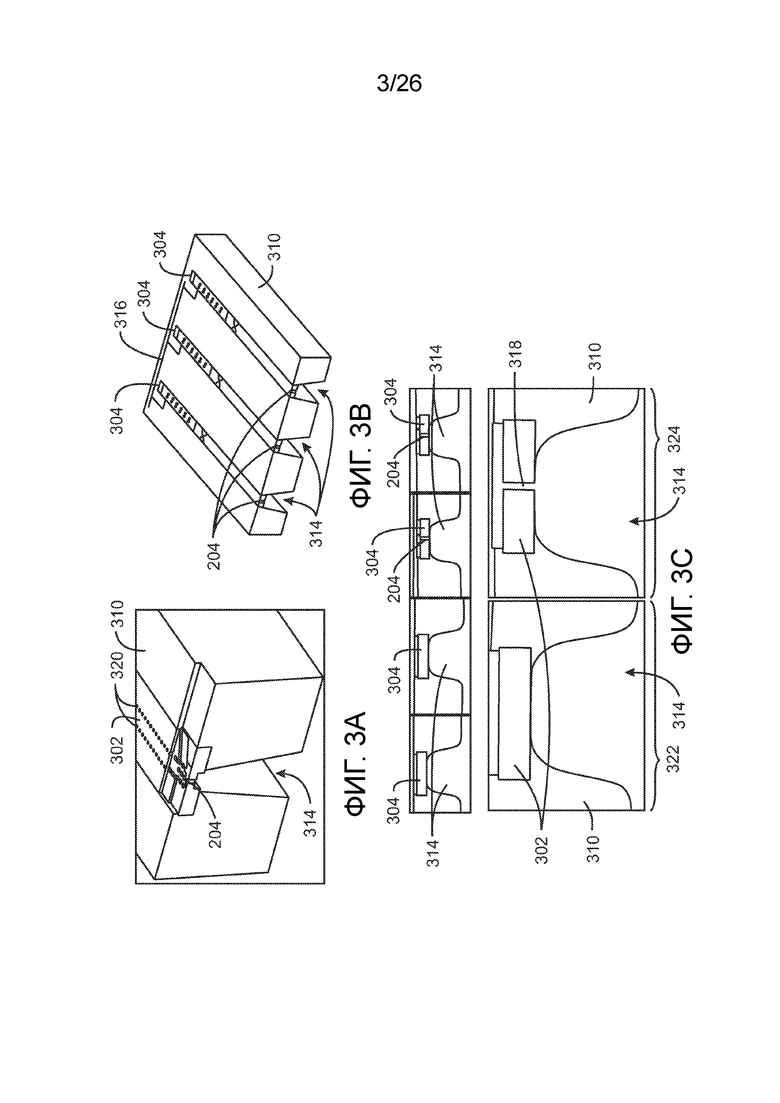

[0007] фиг. 3A - чертеж примера печатающей головки, включающей в себя матрицу с черными чернилами, которая установлена в заливочном компаунде;

[0008] фиг. 3B - чертеж примера печатающей головки, включающей в себя три матрицы, которые можно использовать для чернил трех цветов;

[0009] фиг. 3C показывает виды в разрезе печатающих головок, включающих в себя установленные матрицы, через сплошные секции и через секции, имеющие отверстия для подачи текучей среды;

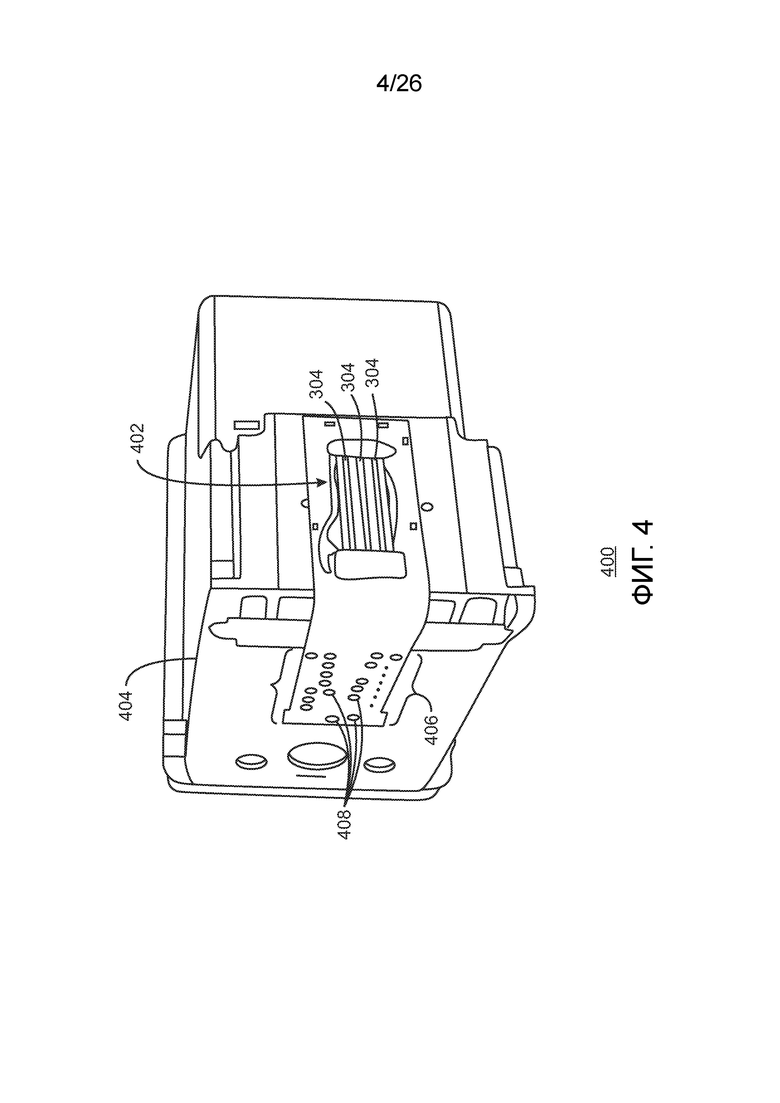

[0010] фиг. 4 - пример картриджа принтера, который включает в себя печатающую головку, описанную со ссылкой на фиг. 3B;

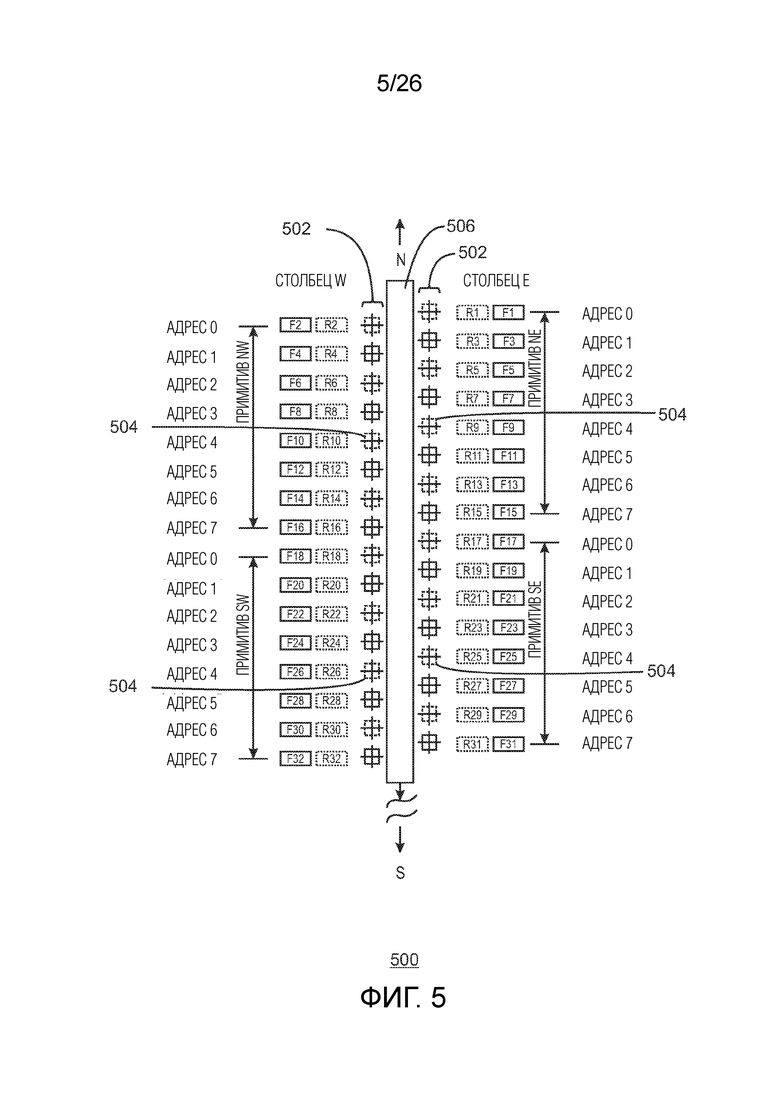

[0011] фиг. 5 - принципиальная схема примера набора из четырех примитивов, называемого четверным примитивом;

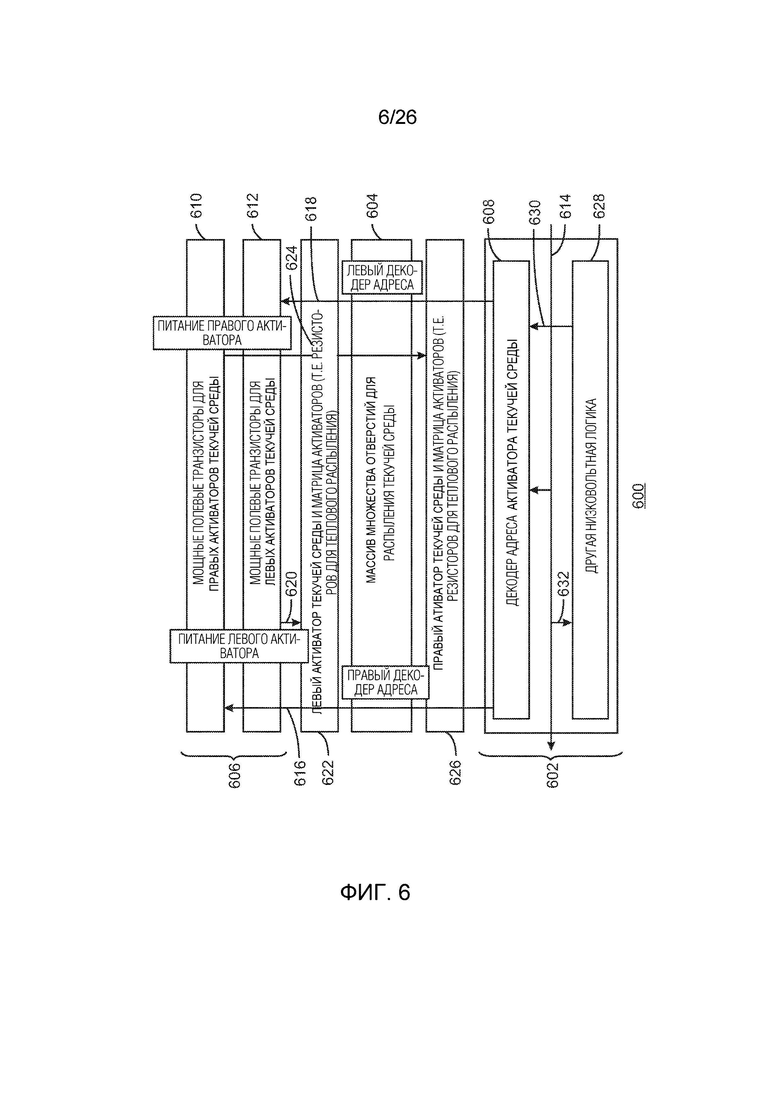

[0012] фиг. 6 - чертеж примера компоновки схемы матрицы, показывающий упрощение, которого можно достичь с помощью единичного набора схемы активатора текучей среды;

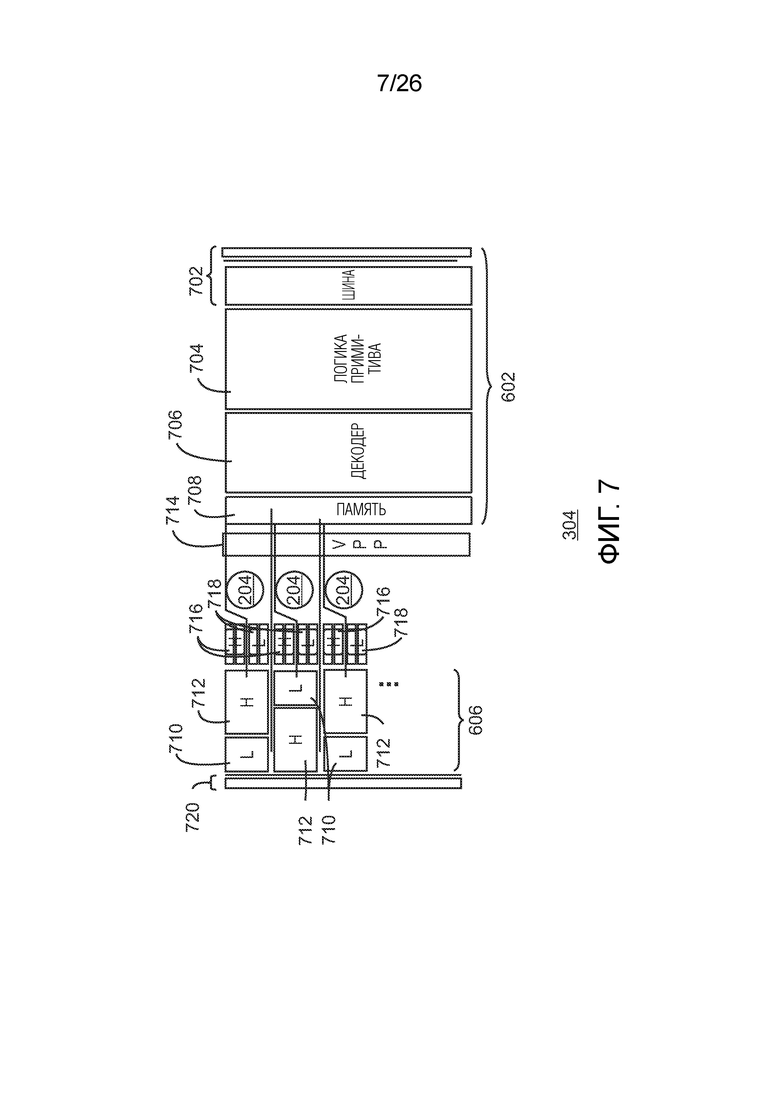

[0013] фиг. 7 - чертеж примера компоновочного плана схемы, показывающий серию зон матрицы для матрицы цветных чернил;

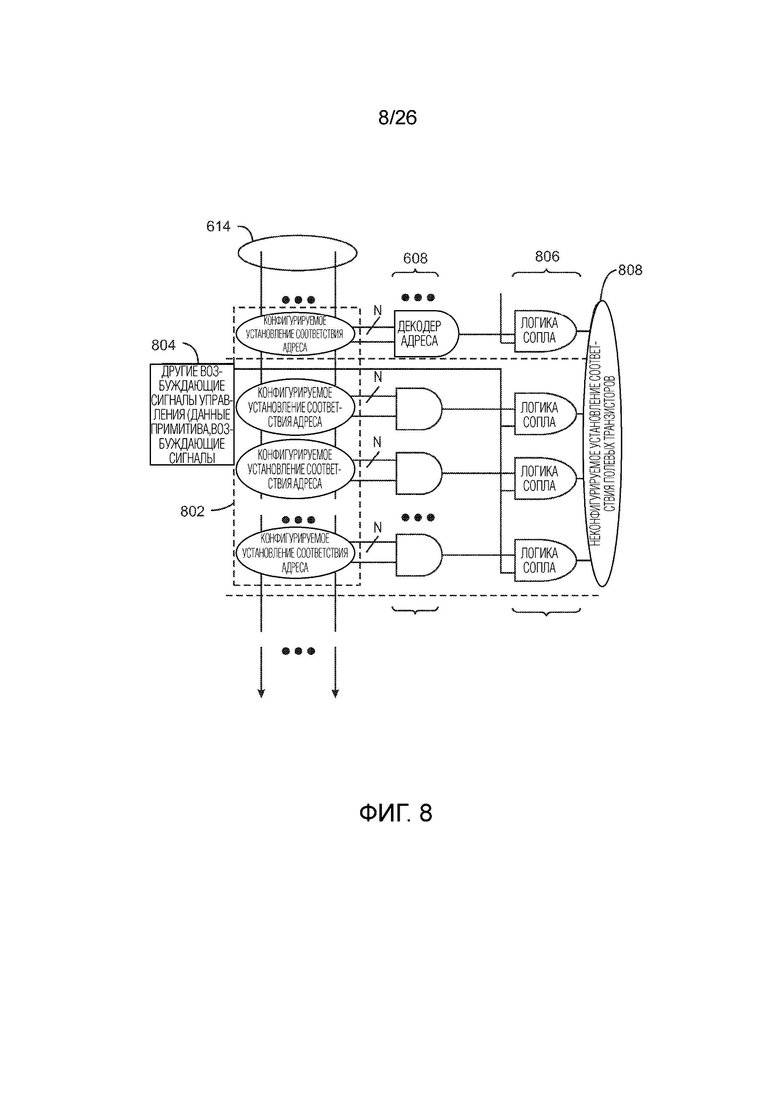

[0014] фиг. 8 - принципиальная схема примера декодирования адреса на матрице;

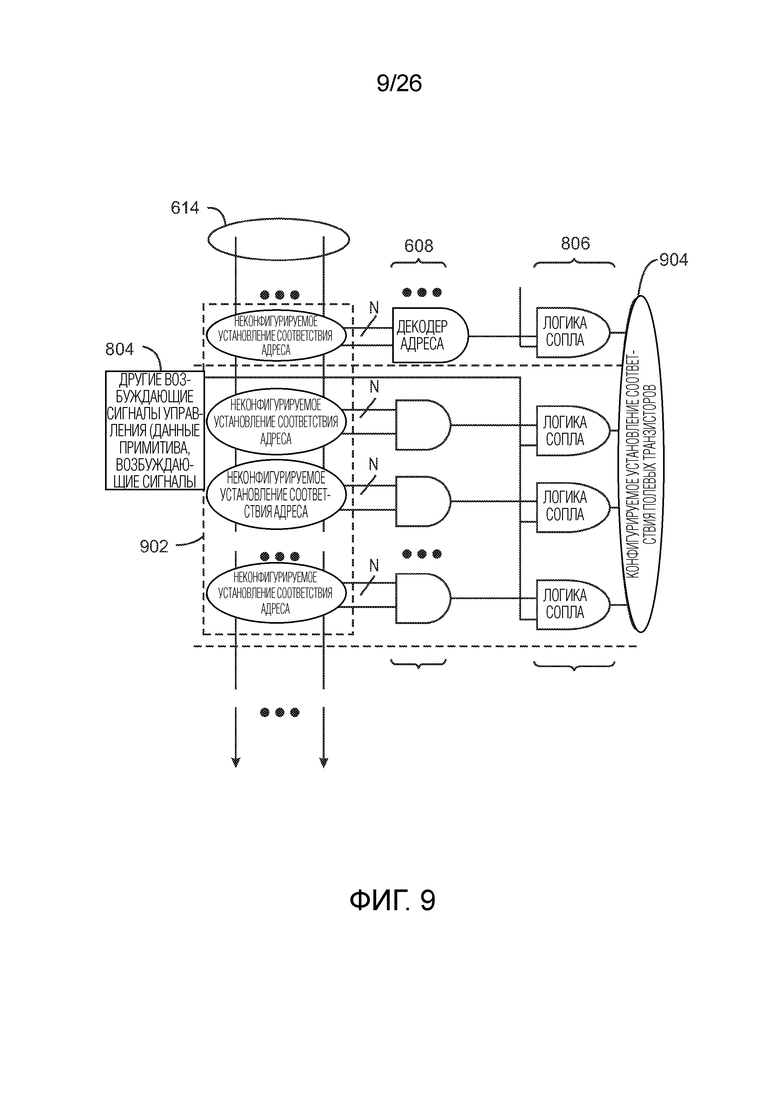

[0015] фиг. 9 - принципиальная схема примера другой реализации декодирования адреса на матрице;

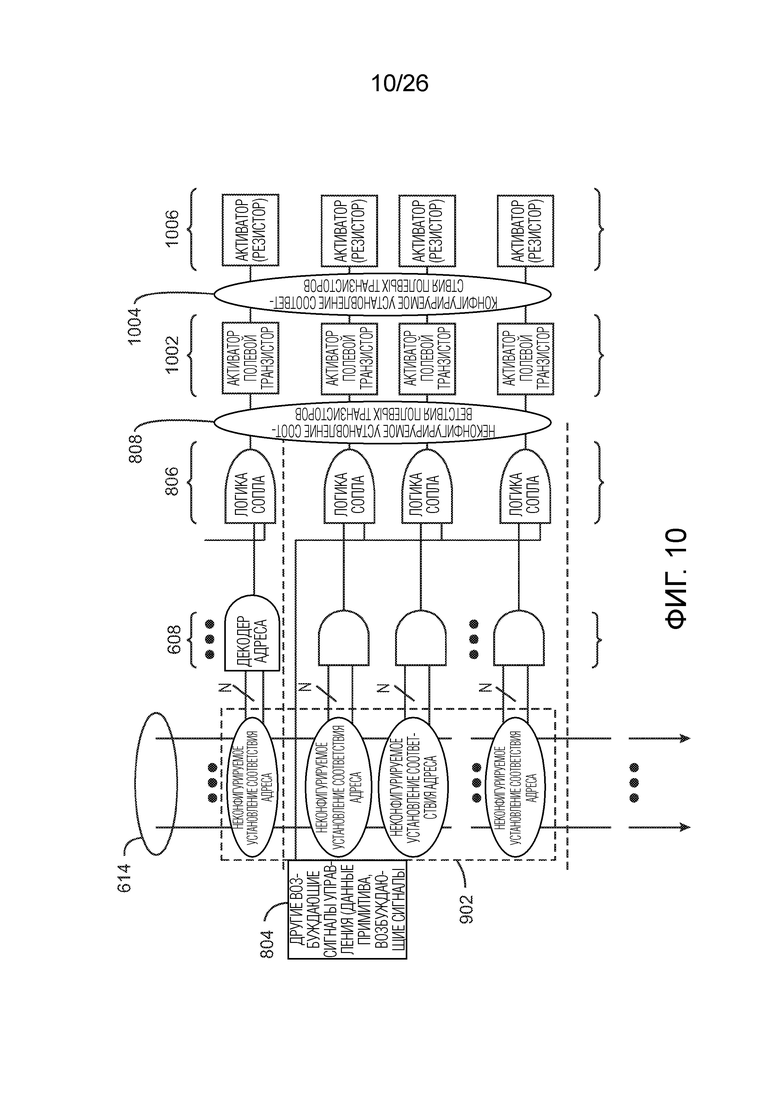

[0016] фиг. 10 - принципиальная схема примера другой реализации декодирования адреса на матрице;

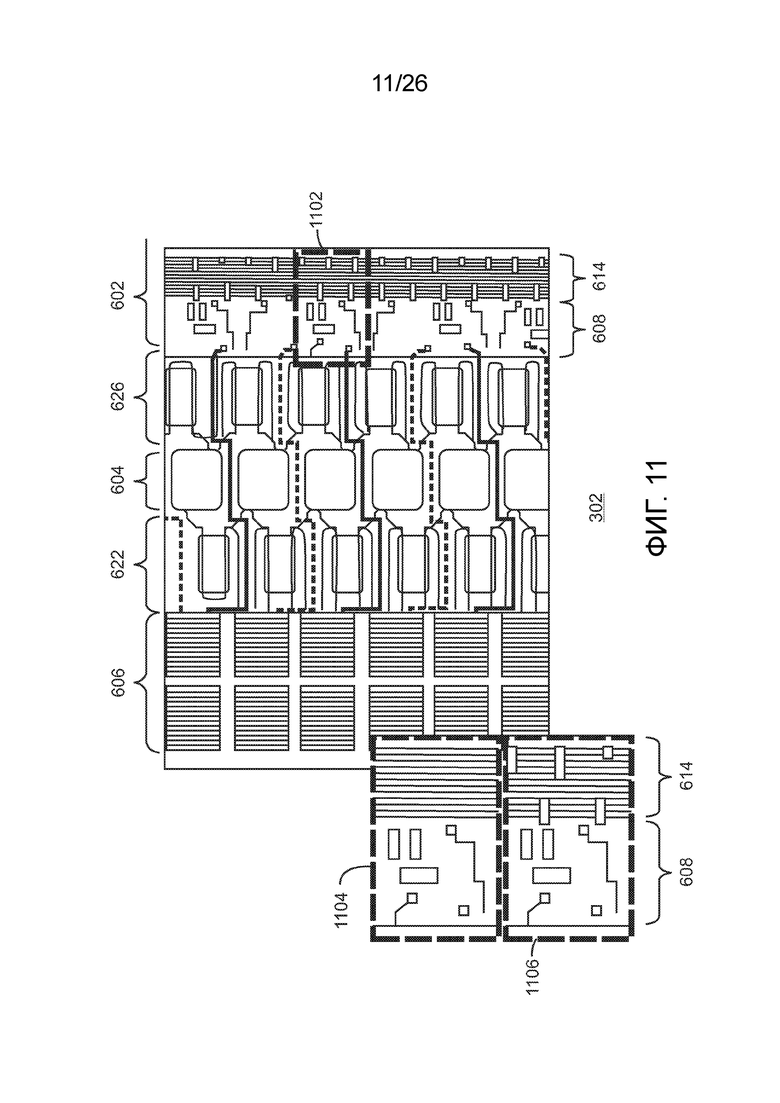

[0017] фиг. 11 - чертеж примера матрицы черных чернил, показывающий формирование межсоединений от адресных линий к логической схеме;

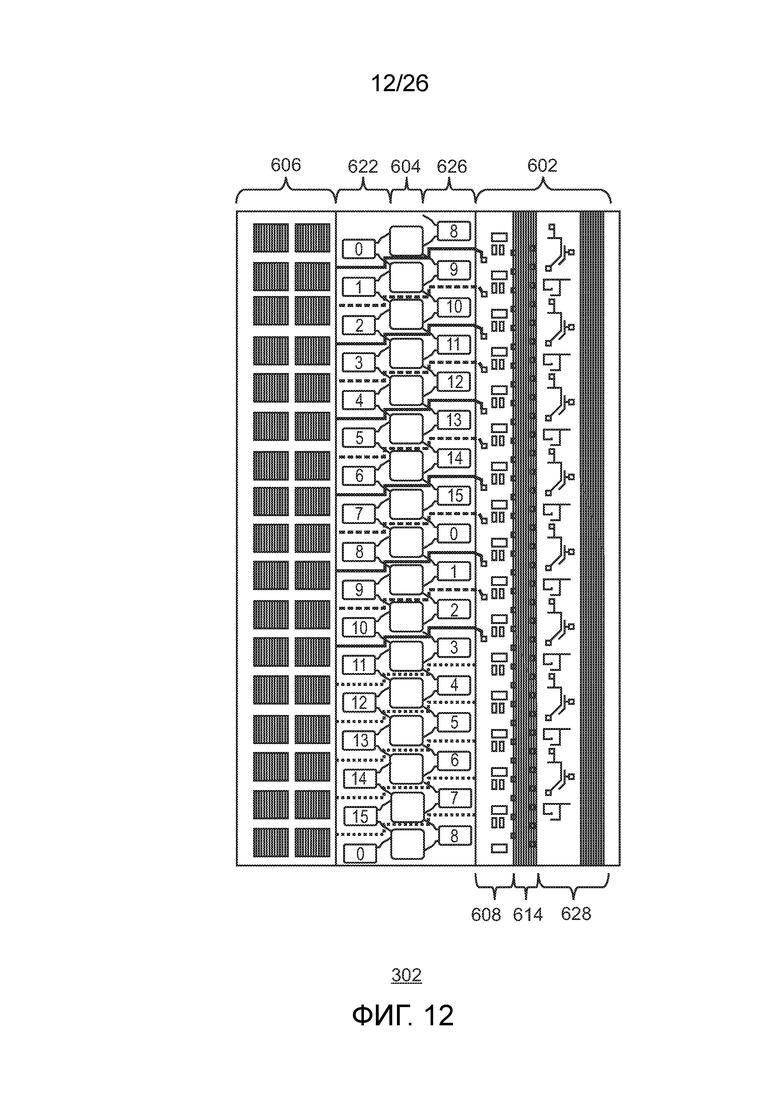

[0018] фиг. 12 - чертеж примера матрицы черных чернил, показывающий смещение в порядке адресов примитивов между столбцами активаторов текучей среды на каждой стороне массива отверстий для подачи текучей среды в соответствии с примером;

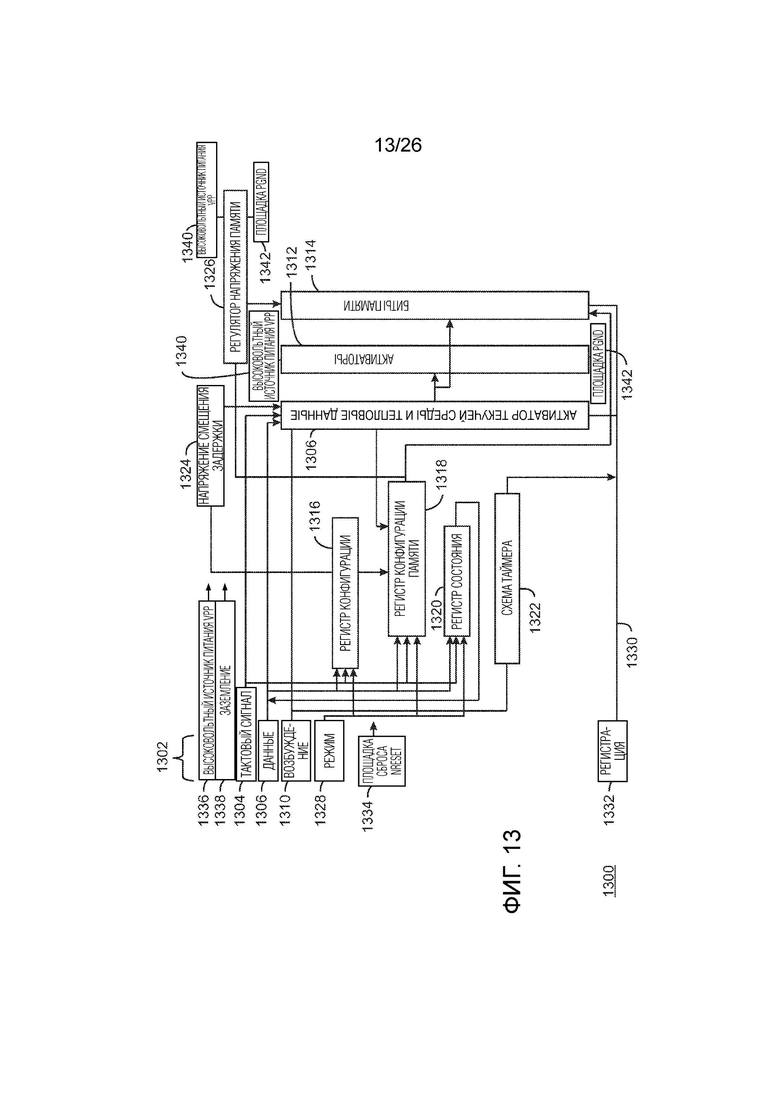

[0019] фиг. 13 - пример блок-схемы матрицы;

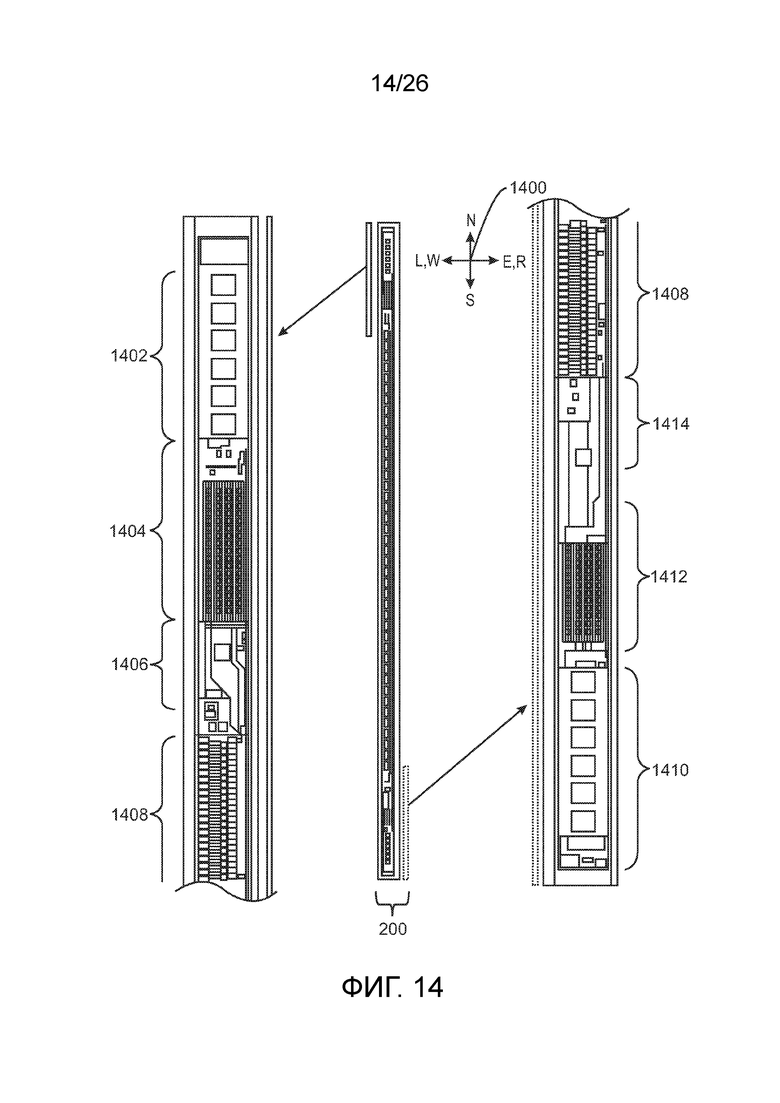

[0020] фиг. 14 - чертеж примера матрицы, показывающий интерфейсные площадки и позиции логических схем, используемые для загрузки данных и сигналов управления в матрицу;

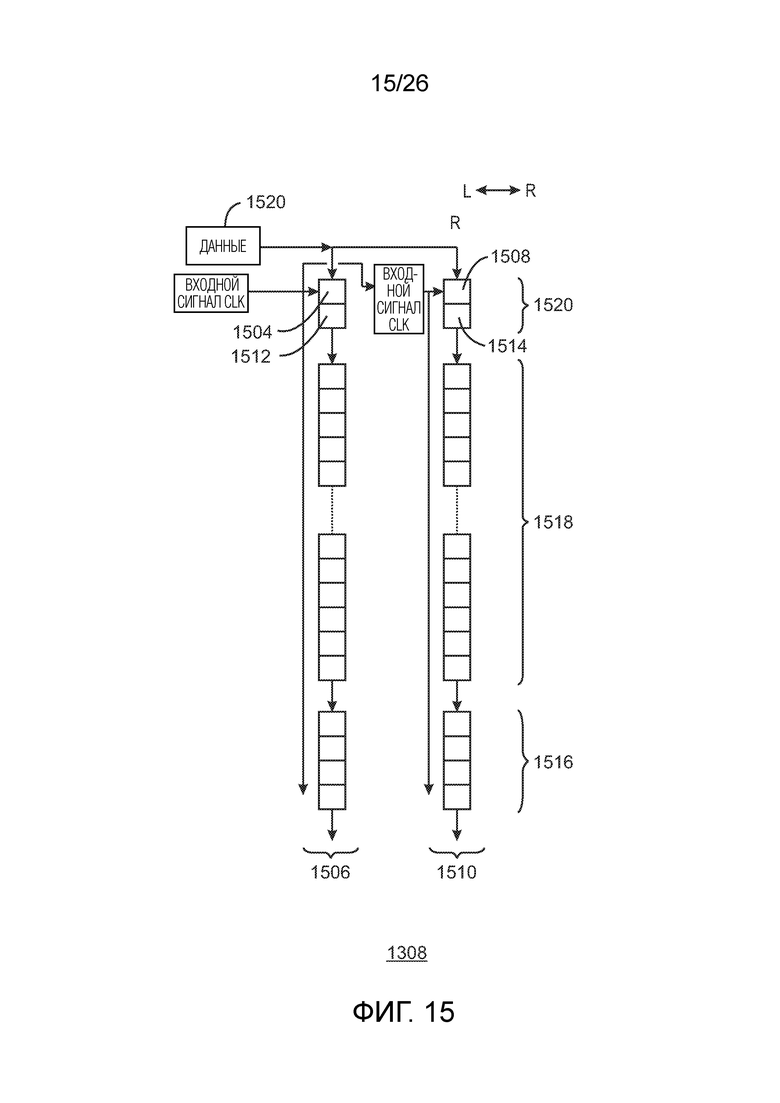

[0021] фиг. 15 - принципиальная схема примера последовательной загрузки данных в хранилище данных;

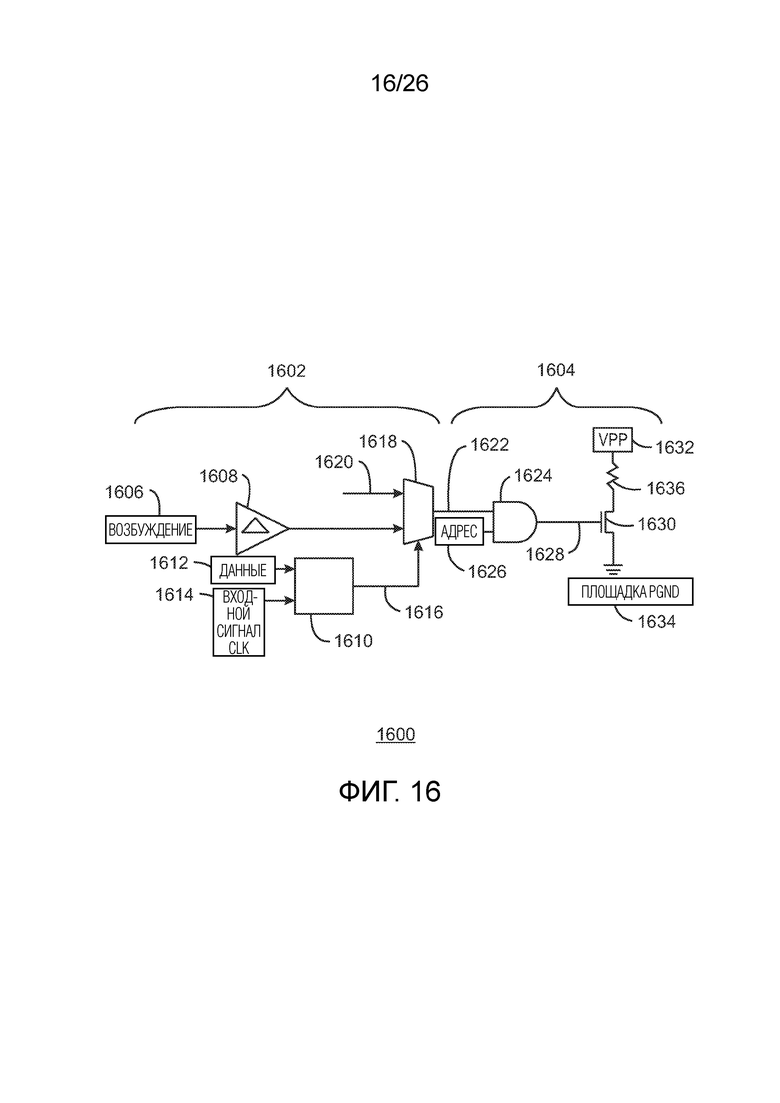

[0022] фиг. 16 - блок-схема примера логической функции для возбуждения единичного активатора текучей среды в примитиве;

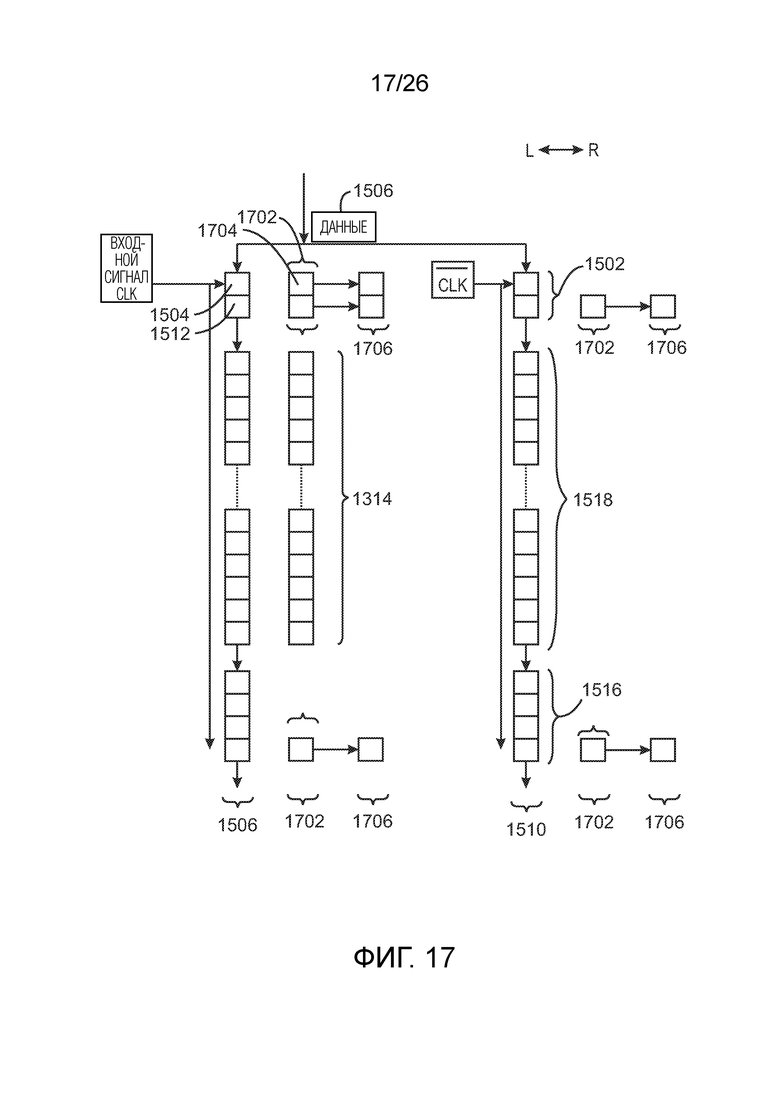

[0023] фиг. 17 - пример принципиальной схемы битов памяти, затеняющих блоки примитивов в хранилище данных;

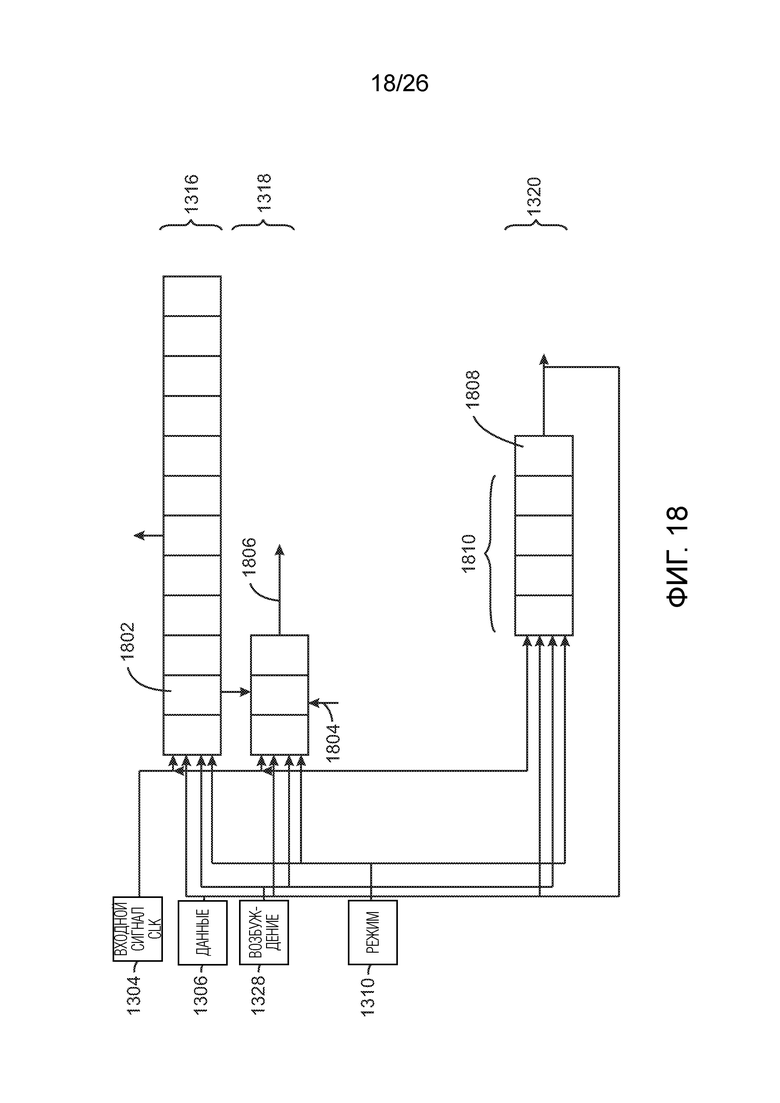

[0024] фиг. 18 - пример блок-схемы регистра конфигурации, регистра конфигурации памяти и регистра состояния;

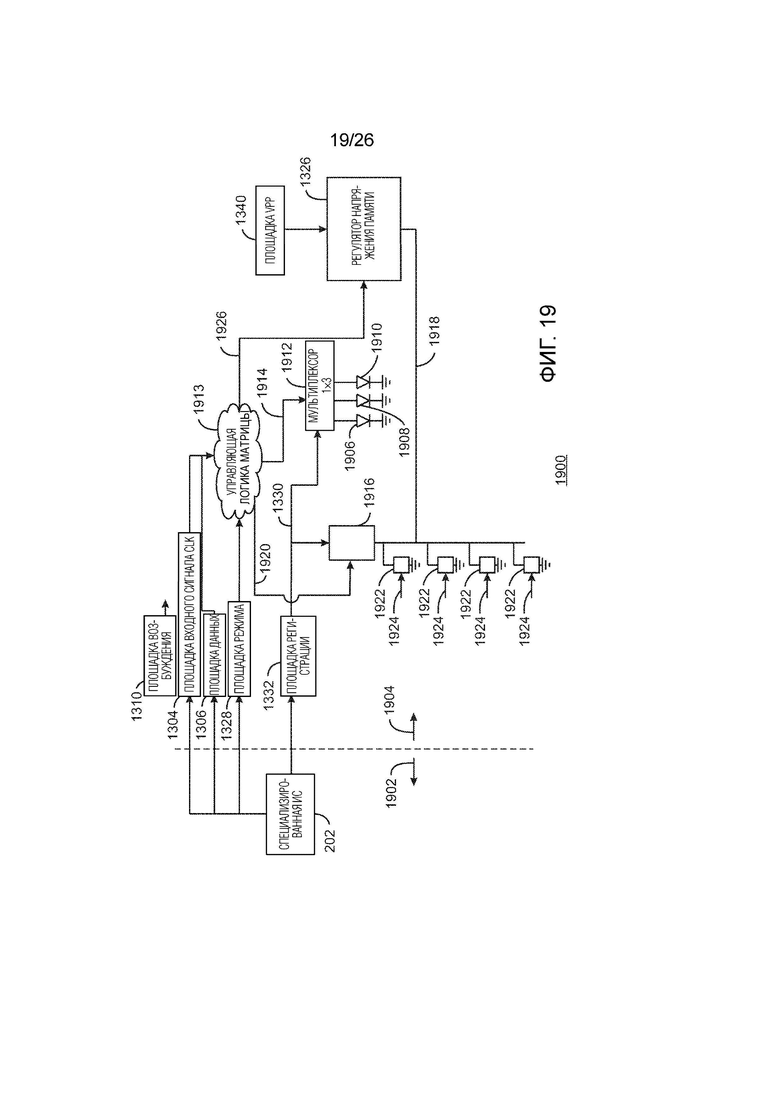

[0025] фиг. 19 - схематичный чертеж примера матрицы, показывающий шину регистрации для считывания и программирования битов памяти и осуществления доступа к тепловым датчикам;

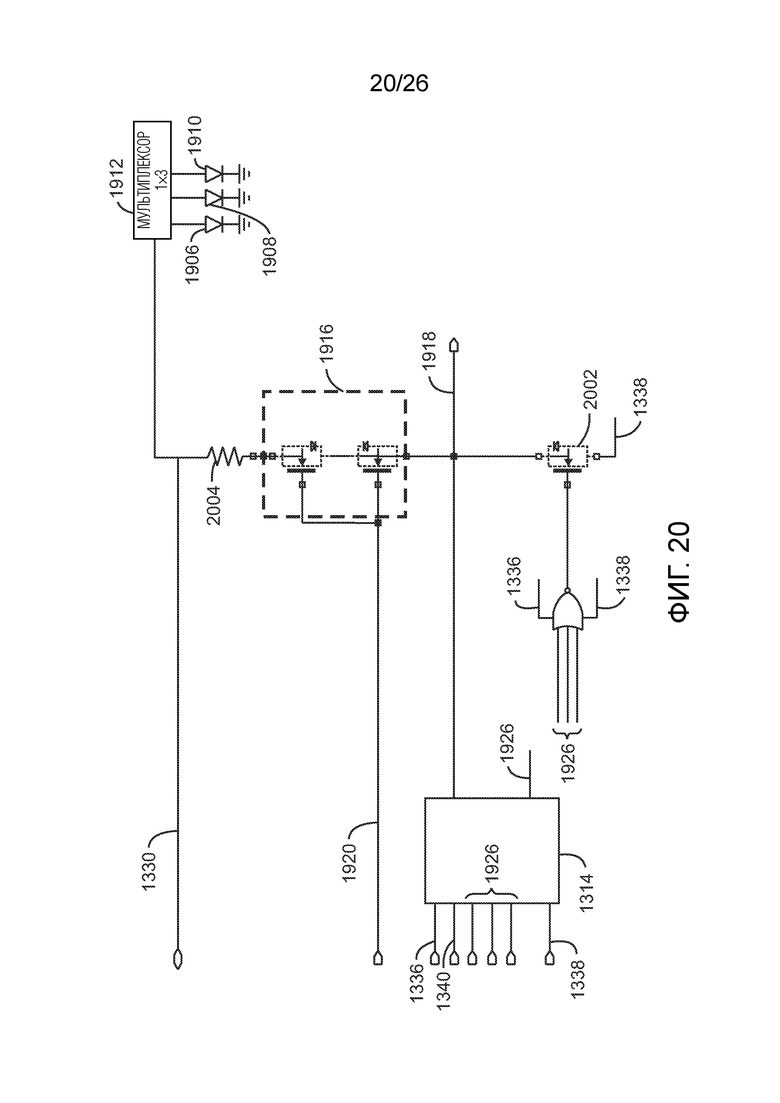

[0026] фиг. 20 - блок-схема примера переключателя защиты от высокого напряжения, используемого для защиты низковольтной МОП-схемы от повреждения высоким напряжением;

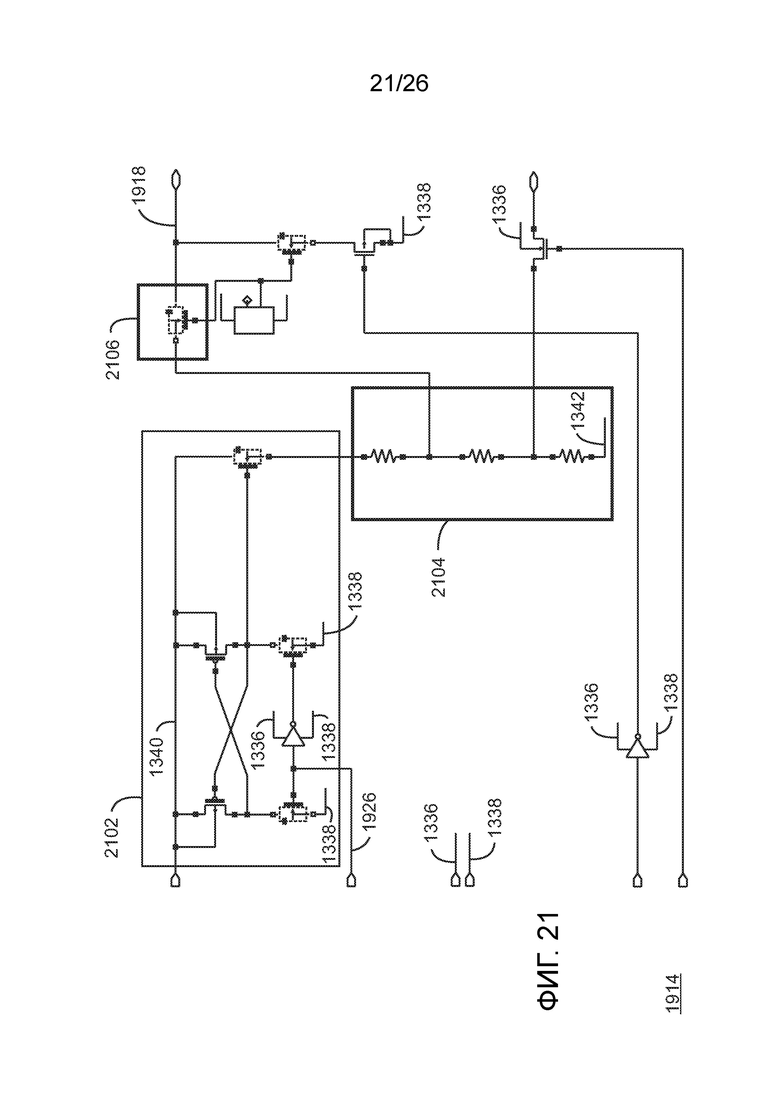

[0027] фиг. 21 - блок-схема примера регулятора напряжения памяти;

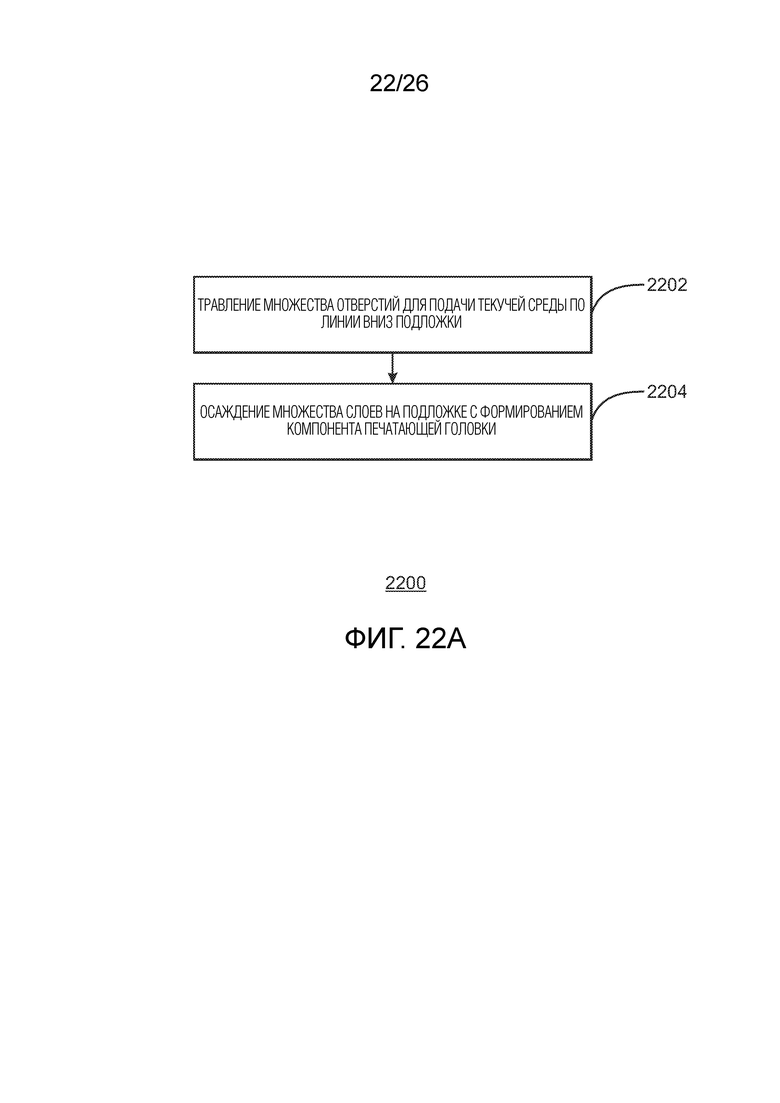

[0028] фиг. 22A - блок-схема последовательности операций процесса примера способа формирования компонента печатающей головки;

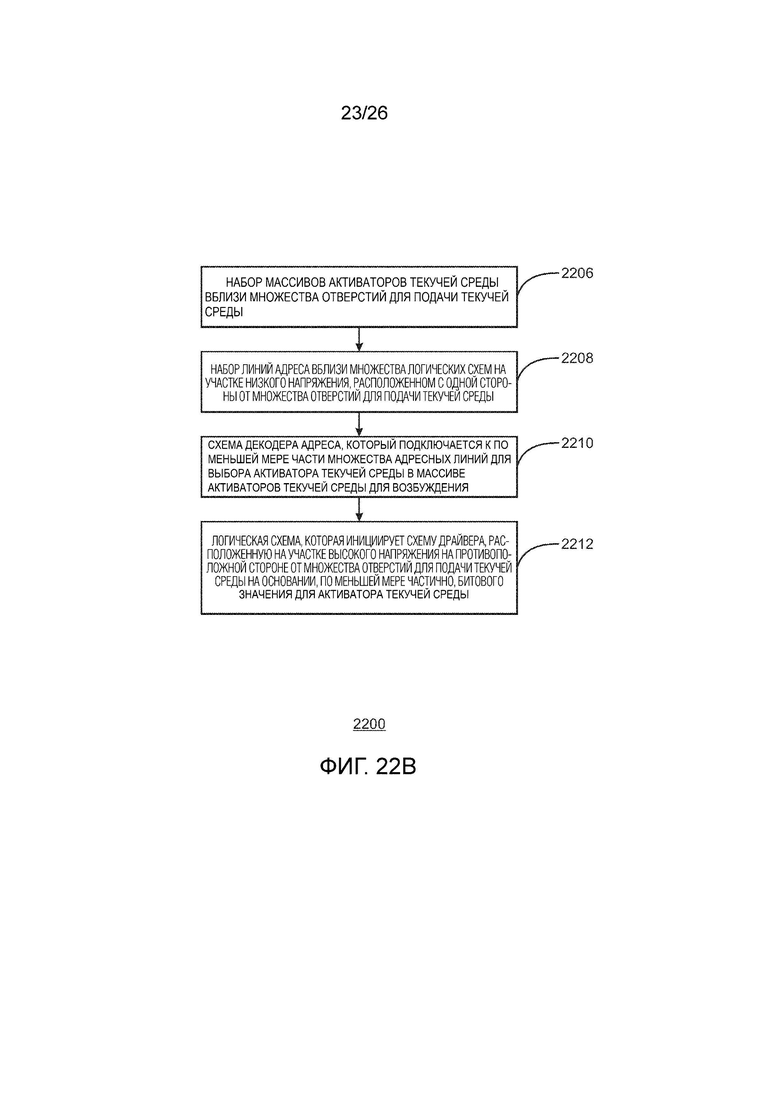

[0029] фиг. 22B - блок-схема последовательности операций процесса формирования компонентов с помощью слоев по этапу 2204 в способе;

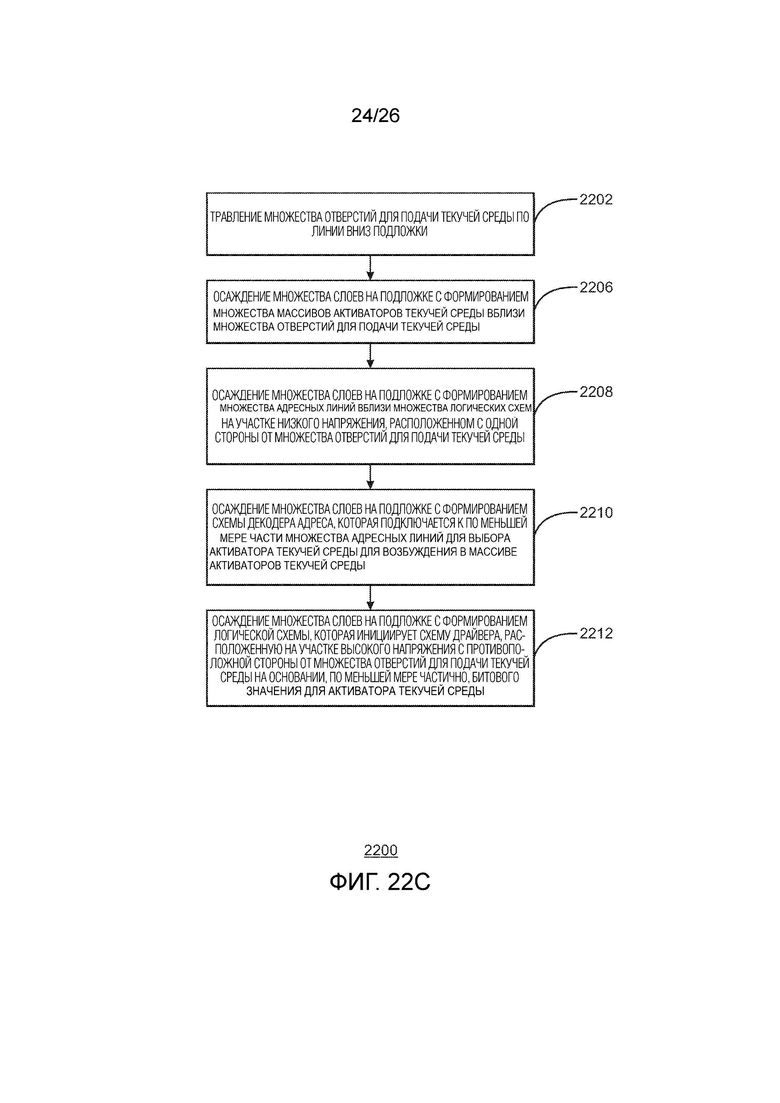

[0030] фиг. 22C - блок-схема последовательности операций процесса комбинированного способа, демонстрирующая формируемые слои и структуры;

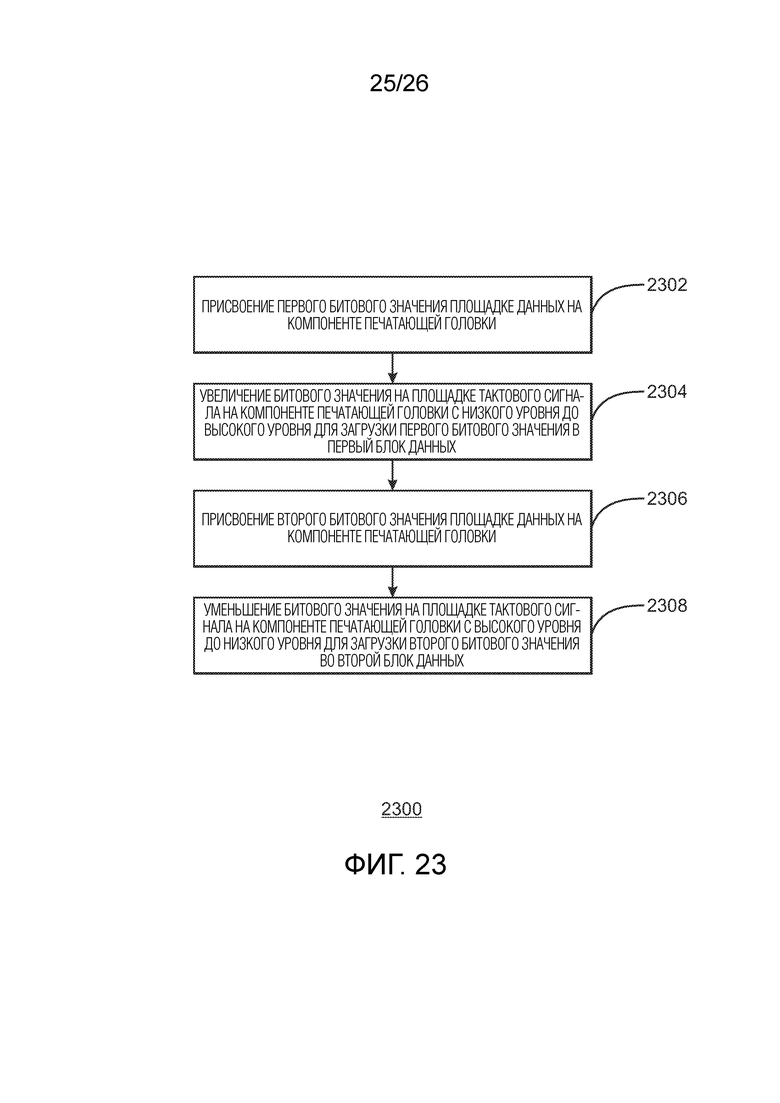

[0031] фиг. 23 - блок-схема последовательности операций процесса способа загрузки данных в компонент печатающей головки; и

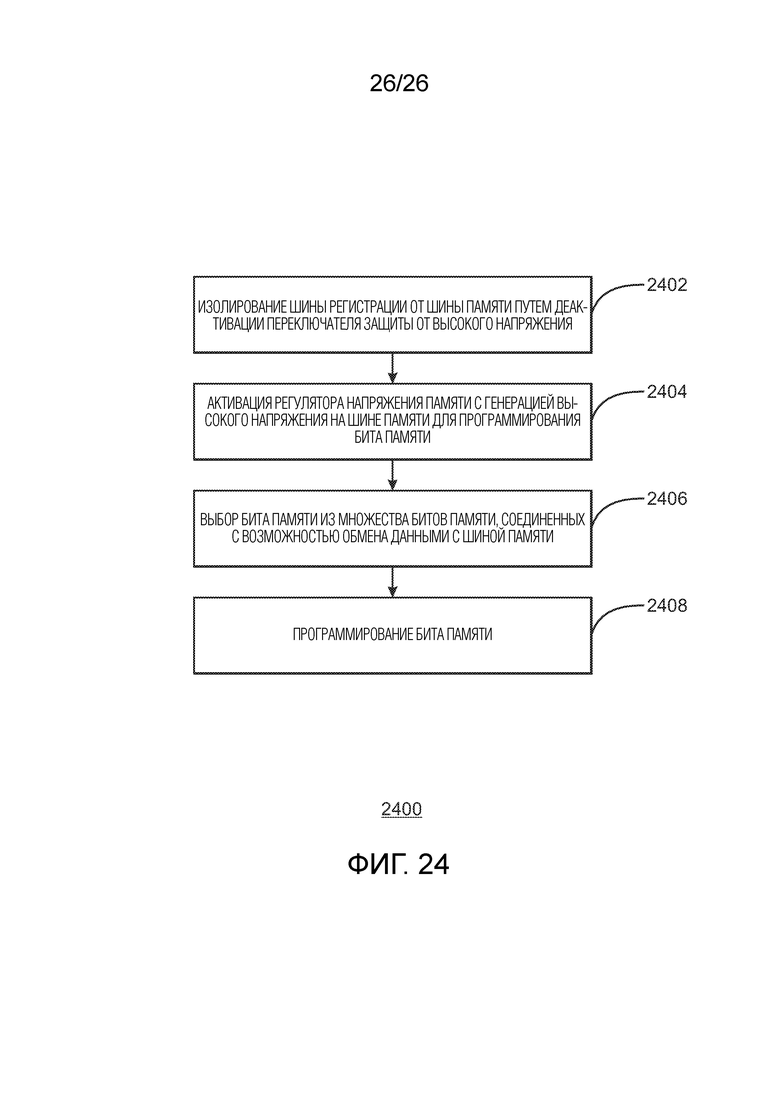

[0032] фиг. 24 - блок-схема последовательности операций процесса по примеру способа записи бита памяти в компонент печатающей головки.

ПОДРОБНОЕ ОПИСАНИЕ КОНКРЕТНЫХ ПРИМЕРОВ

[0033] Печатающие головки формируются с использованием активаторов текучей среды, таких как микроструйные эжекторы и микроструйные насосы. Активаторы текучей среды могут основываться на терморезисторах или пьезоэлектрических технологиях, которые обеспечивают выброс капли из сопла или перемещение небольшого объема текучей среды из нагнетательной камеры. Активаторы текучей среды формируются с использованием длинных, узких кусков кремния, называемых здесь матрицами или компонентами печати. В описанных здесь примерах микроструйный эжектор используется в качестве эжектора для сопла в матрице, используемой для печати и других применений. Например, печатающие головки можно использовать как устройства выброса текучей среды в применениях двухмерной и трехмерной печати и других системах высокоточного распределения текучей среды, включая фармацевтические, лабораторные, медицинские, естественнонаучные и криминалистические применения. Хотя это раскрытие может относиться к струйным и чернильным применениям, раскрытые здесь принципы относятся к любым применениям приведения в движение текучей среды или выброса текучей среды, не ограниченной чернилами.

[0034] Стоимость печатающих головок часто определяется количеством кремния, используемого в матрицах, поскольку стоимость матрицы и процесса изготовления увеличиваются пропорционально суммарному количеству кремния, используемого в кристалле (матрице). Соответственно, более дешевые печатающие головки можно формировать, перемещая функционал из матрицы в другие интегральные схемы, что позволяет использовать более мелкие матрицы.

[0035] Многие современные матрицы имеют паз для подачи чернил в середине матрицы для подачи чернил в активаторы текучей среды. Обычно паз для подачи чернил привносит барьер для переноса сигналов с одной стороны матрицы на другую сторону матрицы, что часто требует дублирования схемы на обеих сторонах матрицы, что приводит к дополнительному увеличению размера матрицы. В этой конфигурации активаторы текучей среды с одной стороны паза, которая может называться левой или западной, имеют схемы шин адресации и питания, независимые от активаторов текучей среды с противоположной стороны паза для подачи чернил, которая может называться правой или восточной.

[0036] Описанные здесь примеры обеспечивают новый подход к подаче текучей среды в активаторы текучей среды капельных эжекторов. В этом подходе паз для подачи чернил заменяется массивом отверстий для подачи текучей среды, расположенных вдоль матрицы, вблизи активаторов текучей среды. Массив отверстий для подачи текучей среды, расположенных вдоль матрицы, может называться здесь зоной подачи. В результате сигналы могут маршрутизироваться через зону подачи между отверстиями для подачи текучей среды, например, от логической схемы, расположенной с одной стороны отверстий для подачи текучей среды, на схемы питания для печати, такие как полевые транзисторы (FET), расположенные с противоположной стороны отверстий для подачи текучей среды. Здесь это называется маршрутизацией через паз. Схема для маршрутизации сигналов включает в себя дорожки, обеспеченные в слоях между соседними отверстиями для подачи чернил или текучей среды.

[0037] Как использовано здесь, первая сторона матрицы и вторая сторона матрицы обозначают длинные края матрицы, выровненные с отверстиями для подачи текучей среды, которые располагаются вблизи или в центре матрицы. Дополнительно, как использовано здесь, активаторы текучей среды располагаются на передней поверхности матрицы, а чернила или текучая среда подаются в отверстия для подачи текучей среды из паза на задней поверхности матрицы. Соответственно, ширина матрицы измеряется от края первой стороны матрицы до края второй стороны матрицы. Подобным образом толщина матрицы измеряется от передней поверхности матрицы до задней поверхности матрицы.

[0038] Маршрутизация через паз обеспечивает возможность устранения дублирующей схемы на матрице, что может уменьшить ширину матрицы, например, на 150 микрон (мкм) или более. В некоторых примерах это может обеспечить матрицу шириной примерно 450 мкм или примерно 360 мкм, или менее. В некоторых примерах устранение дублирующей схемы благодаря маршрутизации через паз можно использовать для увеличения размера схемы на матрице, например, для повышения производительности в более значимых применениях. В этих примерах мощные FET (силовые полевые транзисторы), схемные дорожки, дорожки питания и подобное могут увеличиваться в размере. Это позволяет обеспечить матрицы, способные выдавать более тяжелые капли. Соответственно, в некоторых примерах матрицы могут быть менее чем примерно 500 мкм или менее чем примерно 750 мкм, или менее чем примерно 1000 мкм в ширину.

[0039] Толщина матрицы от передней поверхности до задней поверхности также уменьшается за счет эффективного использования отверстий для подачи текучей среды. Предыдущие матрицы, которые используют пазы для подачи чернил, могут иметь толщину более чем примерно 675 мкм, тогда как матрицы с отверстиями для подачи текучей среды могут иметь толщину менее чем примерно 400 мкм. Длина матриц может составлять примерно 10 миллиметров (мм), примерно 20 мм или примерно 20 мм, в зависимости от числа активаторов текучей среды, используемых для конструкции. Длина матриц включает в себя пространство для схемы на каждом конце матрицы, соответственно активаторы текучей среды занимают часть длины матрицы. Например, для матрицы черных чернил длиной примерно 20 мм активаторы текучей среды могут занимать примерно 13 мм, что является длиной захвата (прогона). Длина захвата является шириной диапазона печати или выброса текучей среды, формируемого при перемещении печатающей головки по носителю печати.

[0040] Дополнительно, маршрутизация через паз позволяет совмещать подобные устройства для повышенной эффективности и улучшенной компоновки. Маршрутизация через паз оптимизирует подачу питания, позволяя левому и правому столбцам активаторов текучей среды совместно использовать схемы маршрутизации питания и заземления. Однако более узкая матрица может быть хрупче, чем более широкая матрица. Соответственно матрица может устанавливаться в полимерном заливочном компаунде, который имеет паз с обратной стороны, позволяющий чернилам течь в отверстия для подачи текучей среды. В некоторых примерах заливочным компаундом является эпоксидная смола, хотя это может быть акрил, поликарбонат, полифениленсульфид и пр.

[0041] Маршрутизация через паз также позволяет оптимизировать компоновку схемы. Например, высоковольтная и низковольтная области могут быть изолированы с противоположных сторон отверстий для подачи текучей среды, обеспечивая улучшение надежности и форм-фактора матриц. Разделение высоковольтной и низковольтной областей может уменьшать или устранять паразитные напряжения, перекрестные помехи и другие явления, которые негативно влияют на надежность матрицы. Дополнительно, единичная копия адресных данных переносится на логические блоки, которые декодируют значение адреса уникальным образом для каждой стороны массива отверстий для подачи текучей среды.

[0042] Для удовлетворения ограничений по текучим средам и минимизации влияний течения текучей среды на множественные активаторы текучей среды, таких как жидкостные перекрестные помехи, которые могут отрицательно влиять на качество изображения, декодирование адреса смещается для активаторов текучей среды на каждой соответствующей стороне массива отверстий для подачи текучей среды. Декодирование адреса может индивидуализироваться под каждую группу активаторов текучей среды или примитивов в ходе изготовления матрицы, например, на окончательном этапе в ходе процесса изготовления. Другие индивидуальные настройки можно использовать для определения тех активаторов текучей среды, которые подлежат возбуждению, по значениям на адресных линиях.

[0043] Матрица, используемая для печатающей головки, как описано здесь, использует резисторы для нагрева текучей среды в микроструйном эжекторе, вызывающие выброс капель за счет теплового расширения. Однако матрицы не ограничиваются активаторами текучей среды теплового действия и могут использовать пьезоэлектрические активаторы текучей среды, подача в которые осуществляется из отверстий для подачи текучей среды.

[0044] Дополнительно, матрицу можно использовать для формирования активаторов текучей среды для других применений, помимо печатающей головки, таких как микроструйные насосы, используемые в аналитическом оборудовании. В этом примере в активаторы текучей среды из отверстий для подачи текучей среды могут подаваться испытательные растворы или другие текучие среды вместо чернил. Соответственно в различных примерах отверстия для подачи текучей среды и чернила можно использовать для обеспечения жидкостных материалов, которые могут выбрасываться или нагнетаться путем выброса капель за счет теплового расширения или пьезоэлектрической активации.

[0045] Помимо эффективности, обеспеченной за счет перекрестной маршрутизации сигналов от одной стороны к другой, описанные здесь матрицы позволяют переносить логические схемы из матрицы на внешнюю микросхему (чип) или другую опорную схему. В различных примерах внешняя микросхема представляет собой специализированную интегральную схему (ASIC), встроенную в принтер. Дополнительно, разные цвета делятся между отдельными матрицами вместо того, чтобы объединять множественные цвета на одной матрице, что обеспечивает гидравлические трубопроводы более низкой стоимости для подачи чернил и других текучих сред в матрицы. Вынос цикла теплового управления за пределы микросхемы также обеспечивает гораздо более сложное поведение тепловой системы без увеличения затрат, такое как, помимо прочего, способность производить и усреднять множественные измерения, использовать относительные контрольные точки, обеспечивать регистрацию с более высоким тепловым разрешением и увеличивать число датчиков или зон регистрации на отдельных матрицах и цветах. Связывание битов памяти с декодирующей логикой для обращения к активаторам текучей среды обеспечивает создание больших массивов памяти (запоминающих устройств) при низких издержках.

[0046] В некоторых примерах биты памяти считываются с помощью шины регистрации, которая также используется для внешних аналоговых измерений, таких как тепловые измерения, для дополнительного снижения стоимости. Поскольку шина регистрации совместно используется различными датчиками, такими как тепловые датчики, дефектоскопические датчики, и битами памяти на матрице, схема защиты от высокого напряжения препятствует повреждению низковольтных устройств, подключенных к сенсорной шине при записи в память. В некоторых примерах для записи битов памяти без необходимости в дополнительном электрическом интерфейсе от внешней схемы используется генератор напряжения на кристалле или регулятор напряжения памяти.

[0047] Фиг. 1A представляет собой вид части матрицы 100, используемой для головки струйной печати уровня техники. Матрица 100 включает в себя все схемы для работы активаторов 102 текучей среды по обе стороны от паза 104 для подачи чернил. Соответственно все электрические соединения вынесены на площадки 106, расположенные на каждом конце матрицы 100. Фиг. 1B представляет собой увеличенный вид участка матрицы 100. Как можно видеть на этом увеличенном виде, паз 104 подачи чернил занимает достаточно много места в центре матрицы 100, увеличивая ширину 108 матрицы 100.

[0048] Фиг. 2A представляет собой пример матрицы 200, используемой для печатающей головки. По сравнению с матрицей 100 по фиг. 1A, матрица 200 имеет эффективную и новую компоновку схемы, в которой отдельные блоки схемы могут иметь больше функций, позволяя матрице 200 быть сравнительно узкой и/или эффективной, как описано здесь. В этой конструкции некоторый функционал предоставляется матрице внешней схемой, такой как специализированная интегральная схема (ASIC) 200.

[0049] В этом примере матрица 200 использует отверстия 204 для подачи текучей среды, чтобы подавать текучую среду, такую как чернила, активаторам 206 текучей среды для выброса с помощью терморезисторов 208. Как описано здесь, маршрутизация через паз позволяет маршрутизировать схему по кремниевым перемычкам (мостикам) 210 между отверстиями 204 для подачи текучей среды и поперек продольной оси 212 матрицы 200. В одном примере это также обеспечивает возможность сравнительно небольшой ширины 214 матрицы 200, например, менее чем примерно 420 мкм, менее чем примерно 500 мкм или менее чем примерно 750 мкм, или менее чем примерно 1000 мкм, например, от примерно 330 мкм до примерно 460 мкм. Небольшая ширина матрицы 200 может уменьшать затраты, например, за счет снижения количества кремния, используемого в матрице 200.

[0050] Как описано здесь, матрица 200 также включает в себя сенсорную схему для операций и диагностики. В некоторых примерах матрица 200 включает в себя тепловые датчики 216, например, расположенные вдоль продольной оси матрицы вблизи одного конца матрицы, в середине матрицы и вблизи противоположного конца матрицы. В некоторых примерах для улучшения теплового управления используется больше тепловых датчиков 216.

[0051] Фиг. 3A-3C представляют собой чертежи печатающих головок, сформованных путем установки матриц 302 и 304 в полимерной опоре 310, сформированной из заливочного компаунда. В некоторых примерах матрицы 302 и 304 слишком узки для непосредственного присоединения тел перьев или жидкостной маршрутизации чернил или других текучих сред из сосудов для текучих сред. Соответственно матрицы 302 и 304 можно устанавливать в полимерной опоре 310, сформированной из заливочного компаунда, такого как эпоксидная смола и пр. Полимерная опора 310 имеет пазы 314, которые обеспечивают открытый участок, позволяющий текучей среде течь из сосуда для текучей среды в отверстия 204 для подачи текучей среды на задней поверхности матриц 302 и 304.

[0052] Фиг. 3A представляет собой чертеж примера печатающей головки, включающей в себя матрицу 302 черных чернил, которая установлена в заливочном компаунде. В матрице 302 черных чернил по фиг. 3A видны две линии активаторов текучей среды 320, причем в каждую группу из двух перемежающихся активаторов текучей среды 320 подача осуществляется из одного из отверстий 204 для подачи текучей среды вдоль матрицы 302 черных чернил. Каждый из активаторов текучей среды 320 представляет собой отверстие в камеру для текучей среды над терморезистором. Активация терморезистора заставлять текучую среду выходить через активаторы текучей среды 320, таким образом каждая комбинация терморезистора, камеры для текучей среды и сопла представляет активатор текучей среды, в частности, микроструйный эжектор. Можно отметить, что отверстия 204 для подачи текучей среды не изолированы друг от друга, что позволяет чернилам вытекать из отверстий 204 для подачи текучей среды в близлежащие отверстия 204 для подачи текучей среды, обеспечивая более высокий расход для активных активаторов текучей среды.

[0053] Фиг. 3B представляет собой чертеж примера печатающей головки, включающей в себя три матрицы 304, которые можно использовать для чернил трех цветов. Например, одну матрицу 304 цветных чернил можно использовать для голубых чернил, другую матрицу 304 цветных чернил можно использовать для пурпурных чернил, а последнюю матрицу 304 цветных чернил можно использовать для желтых чернил. Чернила каждого цвета поступают в соответствующий паз 314 матриц 304 цветных чернил из отдельного сосуда для цветных чернил. Хотя на этом чертеже показаны только три матрицы 304 цветных чернил в опоре, для формирования матрицы CMYK может быть включена четвертая матрица, такая как матрица 302 черных чернил. Подобным образом можно использовать другие конфигурации матрицы. Линии (каналы) 316 связи могут внедряться в полимерную опору 310 для сопряжения с матрицами 304 цветных чернил. Как описано здесь, некоторые из линий 316 связи, такие как адресные линии, шина регистрации и линия возбуждения, среди прочих, могут совместно использоваться матрицами 304 цветных чернил. Линии 316 связи также включают в себя отдельные линии данных для обеспечения отдельных сигналов управления для активации массивов активаторов текучей среды или примитивов.

[0054] Фиг. 3C представляет собой виды в разрезе печатающих головок, включающих в себя установленные матрицы 302 и 304, через сплошные секции 322 и через секции 324, имеющие отверстия 204 для подачи текучей среды. Это показывает, что отверстия 204 для подачи текучей среды сообщаются с пазами 314, чтобы чернила могли вытекать из пазов 314 через установленные матрицы 302 и 304. Как описано здесь, структуры на фиг. 3A - 3C не ограничиваются чернилами, но могут использоваться для обеспечения системы подача текучей среды в активаторы текучей среды в матрицах.

[0055] Фиг. 4 представляет собой пример картриджа 400 принтера, который включает в себя печатающую головку, описанную со ссылкой на фиг. 3B. Установленные матрицы 304 цветных чернил образуют площадку 402. Как описано здесь, площадка 402 включает в себя множественные кремниевые матрицы и полимерный монтажный компаунд, такой как заливочный компаунд на основе эпоксидной смолы. Корпус 404 удерживает сосуды для чернил, используемые для питания установленных на площадке 402 матриц 304 цветных чернил. Гибкое соединение 406, такое как гибкая схема, удерживает контакты или площадки 408 принтера, используемые для сопряжения с картриджем 400 принтера. Описанная здесь конструкция схемы позволяет использовать меньше площадок 408 в картридже 400 принтера по сравнению с картриджами принтеров уровня техники. Например, применение совместно используемой шины регистрации, которая мультиплексируется между всеми матрицами 304 цветных чернил, присутствующими в картридже 400 принтера, позволяет использовать единичную площадку 408 для одной или более функций регистрации, включая регистрацию температуры, дефектоскопию, а также для считывания из памяти. Дополнительно, единичные площадки совместно используются матрицами для каждого из тактового сигнала, сигнала режима и сигнала возбуждения.

[0056] Фиг. 5 представляет собой принципиальную схему 500 примера набора из четырех примитивов, называемого четверным примитивом. Как описано здесь, примитив представляет собой группу активаторов текучей среды, которые совместно используют набор адресных линий. Для облегчения объяснения примитивов и совместно используемой адресации, примитивы с правой части принципиальной схемы 500 обозначены как восточные, например, северо-восточные (NE) и юго-восточные (SE). Примитивы с левой части схемы 500 обозначены как западные, например, северо-западные (NW) и юго-западные (SW). В этом примере каждый активатор 502 текучей среды разблокируется с помощью FET, обозначенного Fx, где x составляет от 1 до 32, и при этом FET соединяет TIJ-резистор (резистор струйного теплового выброса чернил) для активатора текучей среды 502 с высоковольтным источником питания (Vpp) и заземлением. Принципиальная схема 500 также показывает TIJ-резисторы, обозначенные Rx, где x также составляет от 1 до 32, которые соответствуют каждому активатору 502 текучей среды. Хотя активаторы текучей среды показаны на каждой стороне подачи чернил на принципиальной схеме 500, это виртуальная компоновка. В некоторых примерах матрица 304 цветных чернил, сформированная с использованием современных методов, будет иметь активаторы 502 текучей среды на той же стороне подачи чернил.

[0057] В этом примере в каждом примитиве NE, NW, SE и SW, восемь адресов, обозначенных от 0 до 7, используются для выбора активатора текучей среды для возбуждения. В других примерах на каждый примитив приходится 16 адресов, и на каждый четверной примитив приходится 64 активатора текучей среды. Адреса используются совместно, причем адрес выбирает активатор текучей среды в каждой группе. В этом примере, если обеспечено четыре адреса, то активаторы 504 текучей среды, разблокируемые полевыми транзисторами (FET) F9, F10, F25 и F26, выбираются для возбуждения. В некоторых примерах порядки возбуждения могут смещаться, минимизируя жидкостные перекрестные помехи между разблокированными активаторами 504 текучей среды, как дополнительно описано со ссылкой на фиг. 12. Какой, при наличии, из этих активаторов 504 текучей среды возбуждать, зависит от отдельных вариантов выбора примитива, которые являются битовыми значениями, сохраненными в блоке данных, уникальном для каждого примитива. Сигнал возбуждения также переносится на каждый примитив. Активатор текучей среды в пределах примитива возбуждается, когда адресные данные, переносимые на этот примитив, выбирают активатор текучей среды для возбуждения, значение данных, загруженное в блок данных для этого примитива, указывает, что для этого примитива должно произойти возбуждение, и отправляется сигнал возбуждения.

[0058] В некоторых примерах пакет данных активатора текучей среды, именуемый здесь группой импульсов возбуждения (FPG), включает в себя стартовые биты, используемые для идентификации начала FPG, биты адреса, используемые для выбора активатора 502 текучей среды в данных каждого примитива, данные возбуждения для каждого примитива, данные, используемые для конфигурирования рабочих настроек, и стоповые биты FPG, используемые для идентификации окончания FPG. В других примерах FPG не имеет стартовых и стоповых битов, что повышает эффективность переноса данных. Это дополнительно рассмотрено со ссылкой на фиг. 15.

[0059] После загрузки FPG сигнал возбуждения отправляется на все группы примитивов, которые будут возбуждать все адресованные активаторы текучей среды. Например, для возбуждения всех активаторов текучей среды на печатающей головке FPG отправляется для каждого значения адреса, совместно с активацией всех примитивов в печатающей головке. Таким образом, будет создано восемь FPG, каждая из которых связана с уникальным адресом 0-7. Как описано здесь, адресацию, показанную на принципиальной схеме 500, можно модифицировать для решения вопросов жидкостных перекрестных помех, качества изображения и ограничений подачи питания. FPG также может использоваться для записи элемента памяти, связанного с каждым активатором текучей среды, например, вместо возбуждения активатора текучей среды.

[0060] Центральный участок 506 подачи текучей среды может представлять собой паз подачи чернил или отверстия для подачи текучей среды. Однако, если центральный участок 506 подачи текучей среды является пазом подачи чернил, логическая схема и адресные линии, такие как три адресные линии в этом примере, которые используются обеспечивающими адреса 0-7 для выбора активатора текучей среды с возбуждением в каждом примитиве, дублируются, поскольку дорожки не могут пересекать центральный участок 506 подачи текучей среды. Однако, если центральный участок 506 подачи текучей среды выполнен с отверстиями для подачи текучей среды, каждая сторона может совместно использовать схему, что упрощает логику.

[0061] Хотя активаторы 502 текучей среды в примитивах, описанных на фиг. 5, показаны в двух столбцах на противоположных сторонах матрицы, например, на каждой стороне центрального участка 506 подачи текучей среды, это виртуальные столбцы. Положение активаторов 502 текучей среды относительно центрального участка 506 подачи текучей среды зависит от конструкции матрицы, как описано на нижеследующих фигурах. В примере матрица 302 черных чернил имеет расположенные в шахматном порядке активаторы текучей среды на каждой стороне от отверстия для подачи текучей среды, причем расположенные в шахматном порядке активаторы текучей среды имеют одинаковый размер. В другом примере матрица 304 цветных чернил имеет линию активаторов текучей среды вниз матрицы, причем размер активаторов текучей среды на линии активаторов текучей среды перемежается между увеличенными активаторами текучей среды и уменьшенными активаторами текучей среды.

[0062] Фиг. 6 представляет собой чертеж примера компоновки 600 схемы матрицы, показывающий упрощение, которого можно достичь единичным набором схемы активатора текучей среды. В одном примере проиллюстрированная компоновка 600 связана с матрицей 302 черных чернил, где активатор текучей среды и массивы активаторов находятся по обе стороны отверстий 204 для подачи текучей среды. Однако компоновку 600 можно использовать либо для матрицы 302 черных чернил, либо для матрицы 304 цветных чернил.

[0063] В компоновке 600 низковольтные устройства и логика сгруппированы на низковольтной стороне 602 массива 604 отверстий для подачи текучей среды. Высоковольтные устройства, такие как устройства подачи питания для активаторов текучей среды, сгруппированы на высоковольтной стороне 606 массива 604 отверстий для подачи текучей среды. Поскольку все декодеры 608 адреса, в том числе декодеры, используемые мощными FET 610 для правых активаторов текучей среды, и декодеры, используемые мощными FET 612 для левых активаторов текучей среды, совмещены, единичная копия адресных данных 614 может маршрутизироваться на низковольтную сторону 602 массива 604 отверстий для подачи текучей среды. Адресные данные 614 включают в себя серию адресных линий, каждая из которых несет бит адресных данных 614. Затем сигналы управления маршрутизируются по массиву 604 отверстий для подачи текучей среды, включая перекрестные маршруты для сигналов 616 активации для мощных FET 610 для правых активаторов текучей среды и перекрестные маршруты для сигналов 618 активации для мощных FET 612 для левых активаторов текучей среды.

[0064] Линии 620 электропитания соединяют левый массив 622 активаторов текучей среды с мощными FET 612 для активации выбранных активаторов текучей среды. Перекрестно маршрутизированные линии 624 электропитания перекрестно маршрутизируются по массиву 604 отверстий для подачи текучей среды для подключения мощных FET 610 для правых активаторов текучей среды и декодеров к правой матрице 626 активаторов текучей среды для активации выбранных активаторов текучей среды. Перекрестные маршруты 616, 618, 624 могут маршрутизироваться между отверстиями 202, 320 для подачи текучей среды или между поднаборами отверстий 202, 320 для подачи текучей среды.

[0065] Помимо декодеров 608 адреса, низковольтная сторона 602 массива 604 отверстий для подачи текучей среды также имеет другую низковольтную логику 628, включающую в себя безадресные средства управления, такие как возбуждающие сигналы, данные примитива, элементы памяти, регистрация температуры и пр. От этой низковольтной логики 628 сигналы 630 поступают на декодеры 608 адреса для объединения с сигналами адреса для выбора примитивов, подлежащих возбуждению. Низковольтная логика 628 также может использовать адресные данные 632 для выбора элементов памяти, датчиков и пр.

[0066] Фиг. 7 представляет собой чертеж примера компоновочного плана схемы, показывающий серию зон матрицы для матрицы 304 цветных чернил. Одинаково обозначенные элементы описаны со ссылкой на фиг. 2, 6 и 7. В матрице 304 цветных чернил шина 702 несет линии управления, линии данных, адресные линии и линии (электро)питания для логической схемы 704 примитива, включая зону питания логики, которая включает в себя общую линию питания логики (Vdd) и общую линию заземления логики (Lgnd) для обеспечения напряжения питания от примерно 2,5 В до примерно 15 В для логической схемы. Шина 702 также включает в себя зону адресных линий, включающую в себя адресные линии, используемые для предоставления адреса для активатора текучей среды в каждой группе примитивов активаторов текучей среды. Как описано здесь, группа примитивов является группой или поднабором активаторов текучей среды из активаторов текучей среды на матрице 304 цветных чернил.

[0067] Зона адресной логики включает в себя схемы адресных линий, такие как логическая схема 704 примитива и схема 706 декодирования. Логическая схема 704 примитива соединяет адресные линии со схемой 706 декодирования для выбора активатора текучей среды в группе примитивов. Логическая схема 704 примитива также сохраняет биты данных, загруженные в примитив, по линиям данных. Биты данных включают в себя значения адреса для адресных линий и бит, связанный с каждым примитивом, который выбирает, возбуждает ли этот примитив адресованный активатор текучей среды или сохраняет данные.

[0068] Схема 706 декодирования выбирает активатор текучей среды для возбуждения или выбирает элемент памяти в области 708 памяти, который включает в себя биты или элементы памяти, для приема данных. Когда сигнал возбуждения принимается по линиям данных в шине 702, данные либо сохраняются в элемент памяти в области 708 памяти, либо используются для активации FET 710 или 712 в зоне схемы питания на высоковольтной стороне 606 матрицы 304 цветных чернил. Активация FET 710 или 712 подключает соответствующий TIJ-резистор 716 или 718 к совместно используемой шине 714 питания (Vpp). Шина 714 Vpp находится под напряжением от примерно 25 В до примерно 35 В. В этом примере дорожки включают в себя схему питания для питания TIJ-резисторов 716 или 718. Другую совместно используемую шину 720 питания можно использовать для обеспечения заземления TIJ-резисторов 716 или 718. В некоторых примерах шина 714 Vpp и вторая совместно используемая шина 720 питания могут меняться местами.

[0069] Зона подача текучей среды включает в себя отверстия 204 для подачи текучей среды и дорожки между отверстиями 204 для подачи текучей среды. Для матрицы 304 цветных чернил можно использовать капли двух размеров, выбрасываемые терморезисторами, связанными с каждым активатором текучей среды. Капли большой массы (HWD) могут выбрасываться с использованием более крупного TIJ-резистора 716. Капли небольшой массы (LWD) могут выбрасываться с использованием меньшего TIJ-резистора 718. В некоторых примерах FET могут иметь одинаковый размер для TIJ-резисторов разных размеров, причем FET для меньших TIJ-резисторов 718 будет пропускать меньший ток. Электрически активаторы текучей среды LWD находятся в первом столбце, например, левом, как описано со ссылкой на фиг. 6. Активаторы текучей среды HWD электрически соединены во втором столбце, например, правом, как описано со ссылкой на фиг. 6. В этом примере физические активаторы текучей среды матрицы 304 цветных чернил представляют собой активаторы текучей среды LWD и активаторы текучей среды HWD, перемежающимися во встречно-гребенчатой структуре.

[0070] Эффективность компоновки можно дополнительно повышать, изменяя размер соответствующих FET 710 и 712 для удовлетворения требований к мощности TIJ-резисторов 716 и 718. Соответственно, в этом примере размер соответствующих FET 710 и 712 определяется питанием TIJ-резистора 716 или 718. Более крупный TIJ-резистор 716 разблокируется более крупным FET 712, тогда как меньший TIJ-резистор 718 разблокируется меньшим FET 710. В других примерах FET 710 и 712 имеют одинаковый размер, хотя мощность, поступающая через FET 710, которые используются для запитывания меньших TIJ-резисторов 718, ниже.

[0071] Аналогичный компоновочный план схемы можно использовать для матрицы 302 черных чернил. Однако, как описано здесь для примеров, FET для матрицы черных чернил могут быть одного размера, поскольку TIJ-резисторы и активаторы текучей среды имеют одинаковый размер.

[0072] Фиг. 8 представляет собой принципиальную схему, демонстрирующую пример декодирования адреса на матрице. Одинаково обозначенные элементы описаны со ссылкой на фиг. 6. Целью декодирования адреса является получение адресных данных 614 и выбор одного активатора текучей среды в примитиве для возбуждения. Декодирование адреса можно модифицировать для изменения порядка возбуждения активаторов в соответствии с последовательностью адресных данных, отправленных на примитив. Соответственно, порядок возбуждения оптимизируется в соответствии с ограничениями по текучей среде, электрическими и другими ограничениями системы для оптимизации качества изображения. Как описано здесь, примитивы на матрице могут группироваться в столбцы или массивы. В некоторых примерах примитивы в столбце или массиве используют один и тот же порядок декодирования адреса.

[0073] Декодирование адреса можно модифицировать с использованием конфигурируемых соединений 802 для приведения в соответствие с адресом, которые выбирают, какие адресные данные 614 используются декодирующей логикой в декодерах 608 адреса. Это может осуществляться в операции постпроизводства или постобработки, в которой между адресными линиями и декодирующей логикой по завершении начального изготовления матрицы формируются соединения или межсоединения (перемычки). Это дополнительно рассмотрено со ссылкой на фиг. 11. Помимо декодеров 608 адреса, другие возбуждающие сигналы 804 управления используются для активации логики 806 активатора текучей среды для выбора и возбуждения активатора текучей среды в примитиве.

[0074] В примере по фиг. 8 в ходе начального изготовления матрицы формируются другие соединения, такие как соединения, приводимые в соответствие между декодерами 608 адреса и логикой 806 активатора текучей среды, и устанавливаются соответствия (приводятся в соответствие) соединений 808 между логикой 806 активатора текучей среды и FET. В этом примере эти соединения, сформированные в ходе начального изготовления матрицы, не конфигурируются.

[0075] Фиг. 9 представляет собой принципиальную схему примера другой реализации декодирования адреса на матрице. Одинаково обозначенные элементы описаны со ссылкой на фиг. 6 и 8. В этом примере установление соответствия 902 адреса между адресными данными 614 и декодерами 608 адреса не является конфигурируемым. Дополнительно, установление соответствия адреса между декодерами 608 адреса и логикой 806 активатора текучей среды также не является конфигурируемым. Однако установление соответствия 904 адреса между логикой 806 активатора текучей среды и FET является конфигурируемым. В некоторых примерах это осуществляется в ходе стадии начального изготовления матрицы, например, путем маршрутизации дорожек от низковольтной логики активатора текучей среды к более отдаленным FET.

[0076] Установление соответствия соединений после декодеров 608 адреса может осуществляться другими методами. В одном примере соединения между декодерами 608 адреса и логикой 806 активатора текучей среды являются конфигурируемыми, например, отправляющими сигналы от отдельных блоков декодирования адреса на логические блоки активатора текучей среды, используемые для активации более отдаленных FET. Дополнительно, в некоторых примерах декодеры 608 адреса и логика 806 активатора текучей среды для примитива сгруппированы в единый логический блок, и соединения между сгруппированными логическими выходами и FET активаторов сконфигурированы для выбора порядка возбуждения.

[0077] Фиг. 10 представляет собой принципиальную схему примера другой реализации декодирования адреса на матрице. Одинаково обозначенные элементы описаны со ссылкой на фиг. 6, 8 и 9. В этом примере установление соответствия 902 адреса адресных данных 614 с декодерами 608 адреса не является конфигурируемым. Дополнительно, установление соответствия соединений 808 логики 806 активатора текучей среды с FET 1002 также не является конфигурируемым. Однако установление соответствия 1004 FET 1002 с активаторами 1006 текучей среды, например, терморезисторами, является конфигурируемым. В примерах установление соответствия 1004 осуществляется в ходе начального изготовления для установления соответствия FET 1002 с активаторами 1006 текучей среды, расположенными на большем расстоянии, например, с обходом более близких активаторов 1006 текучей среды.

[0078] Хотя примеры на фиг. 8-10 показывают три отдельных метода установления соответствия, в которых другие методы установления соответствия указаны как неконфигурируемые, методы не ограничиваются упомянутыми. Например, в ходе обработки можно использовать несколько методов установления соответствия. В некоторых примерах установление соответствия 904 адреса между логикой 806 активатора текучей среды и FET является конфигурируемым, как описано со ссылкой на фиг. 9, и установление соответствия соединений 802, которые выбирают, какие адресные данные 614 используются декодирующей логикой в декодерах 608 адреса, как описано со ссылкой на фиг. 8, также является конфигурируемым.

[0079] Фиг. 11 представляет собой пример матрицы 302 черных чернил, демонстрирующий формирование межсоединений от адресных линий к логической схеме. Одинаково обозначенные элементы описаны со ссылкой на фиг. 3 и 6. На этом чертеже прямоугольник 1102 иллюстрирует соединение между адресными данными 614 и декодером 608 адреса. Как описано со ссылкой на фиг. 8, после начального изготовления адресные данные 614 не связаны с декодером 608 адреса, поскольку конфигурации маски межсоединений не завершена, как показано на увеличенном виде блока 1104. После завершения вторичной обработки, увеличенный вид блока 1106 демонстрирует завершенные межсоединения между декодером 608 адреса и адресными данными 614. Хотя фиг. 11 относится к матрице 302 черных чернил, подобные соединения между адресными данными 614 и декодером 608 адреса будут выполнены для матрицы 304 цветных чернил.

[0080] Фиг. 12 представляет собой чертеж примера матрицы 302 черных чернил, демонстрирующий смещение в порядке адресов примитивов между матрицами 622 и 626 активаторов текучей среды на каждой стороне массива 604 отверстий для подачи текучей среды, в соответствии с примером. Одинаково обозначенные элементы описаны со ссылкой на фиг. 3 и 6. Фиг. 12 показывает примитивы, каждый с 16-ю активаторами текучей среды, причем на каждой стороне массива 604 отверстий для подачи текучей среды присутствует один примитив. В этом примере смещение на восемь в порядках адресов между левым массивом 622 активаторов текучей среды и правым массивом 624 активаторов текучей среды реализовано с использованием конфигурируемых маской соединений между декодером 608 адреса и адресными данными 614. Это позволяет системе печати отправлять единичный набор адресных данных 614, который декодируется для активаторов текучей среды по обе стороны массива 604 отверстий для подачи текучей среды.

[0081] Таким образом, на основании конфигурации соединений между адресными данными 614 и декодером 608 адреса адрес смещается на нужную величину. В результате менее проблематичны ограничения по текучей среде, например, в расходе текучей среды через массив 604 отверстий для подачи текучей среды на активаторы по обе стороны массива 604 отверстий для подачи текучей среды.

[0082] Фиг. 13 представляет собой пример блок-схемы 1300 матрицы. В одном примере в матрицу включены элементы памяти и датчики, такие как тепловые датчики. Элементы памяти могут включать в себя блоки данных и биты памяти. В одном примере измерение температуры и система управления могут обеспечиваться вне матрицы, например, на главной ASIC печатающего устройств. Соответственно, внешняя схема управления, например, ASIC, может поддерживать множественные матрицы на совместно используемой шине регистрации. В одном примере это обеспечивает сравнительно простую конструкцию благодаря сравнительно небольшому количеству кремния в матрице и сравнительно низкие затраты.

[0083] Внешние соединения или (контактные) площадки 1302 используются для осуществления доступа к функциям матрицы. Площадки 1302 включают в себя площадку 1304 тактового сигнала, используемую для обеспечения тактового сигнала для загрузки данных. Как дополнительно описано здесь, данные на площадке 1306 данных загружаются в один столбец активаторов в хранилище 1308 данных, например, левый столбец, на переднем фронте тактового импульса (сигнала), и загружаются во второй столбец активаторов в хранилище 1308 данных, например, правый столбец, на заднем фронте тактового импульса. Каждый раз, когда новый набор битов данных загружается в первый и второй столбцы активаторов, предыдущий бит данных в этом положении сдвигается в новое положение, например, действуя как большой сдвиговый регистр. Это дополнительно описано со ссылкой на фиг. 15.

[0084] Сигнал возбуждения подается через площадку 1310 возбуждения и используется либо для инициирования активатора текучей среды в матрице 1312 активаторов, которая была выбрана через биты адреса в потоке данных, либо для инициирования доступа к битам 1314 памяти, которые совместно используют адрес с соответствующим TIJ-резистором в матрице 1312 активаторов.

[0085] Матрица имеет регистры, которые можно использовать для конфигурирования параметров. Можно отметить, что, как использовано здесь, термин регистр включает в себя любое число конфигураций хранилища, включая сдвиговые регистры, триггеры и пр. Они включают в себя, например, регистр 1316 конфигурации, регистр 1318 конфигурации памяти и регистр 1320 состояния.

[0086] В некоторых примерах регистры 1316 и 1318 конфигурации предназначены только для записи. Подтверждение битов, которые были записаны, производится по поведению матрицы. Исключение доступа для считывания к регистрам 1316 и 1318 уменьшает счетчик схемы и сохраняет некоторую площадь на матрице. Регистр 1318 конфигурации памяти является теневым регистром, запараллеливающим регистр 1316 конфигурации, но разблокируется только для записи, когда удовлетворены некоторые сложные условия, например, биты данных активатора текучей среды и биты данных регистра конфигурации заданы в определенном порядке, совместно с конкретными состояниями входной площадки. Регистр 1320 состояния используется для считывания данных для идентификации отказа матрицы или значения версии и также используется в целях испытания для тестирования интегральной схемы в ходе производства.

[0087] Помимо регистров 1316, 1318 и 1320, матрица имеет аналоговые блоки, включающие в себя, например, схему 1322 таймера, контроллер 1324 напряжения смещения задержки и регулятор 1326 напряжения памяти. Площадка 1328 режима используется для выбора различных режимов работы, таких как конфигурации загрузки с площадки 1306 данных в регистр 1316 конфигурации или в регистр 1318 конфигурации памяти. Площадку 1328 режима также можно использовать для выбора того, какие датчики подключаются к шине 1330 регистрации, которая считывается через площадку 1332 регистрации, включая, например, среди прочих, тепловые датчики или биты 1314 памяти. В некоторых примерах площадка 1334 NReset используется для приема сигнала сброса всех функциональных блоков матрицы, заставляющего их возвращаться к начальной конфигурации. Это может осуществляться, например, если схема 1322 таймера сообщает о проблеме от матрицы на внешнюю ASIC, например, из состояния ожидания.

[0088] Помимо вышеупомянутых площадок 1304, 1306, 1310, 1328, 1332 и 1334 сигнала, используются четыре площадки 1336, 1338, 1340 и 1342 питания для подачи питания на матрицу. Они включают в себя площадку 1336 Vdd и площадку 1338 Lgnd для подачи низковольтного питания на логическую схему. Площадка 1340 Vpp и площадка 1342 Pgnd обеспечивают высоковольтное питание для активации TIJ-резисторов матрицы 1312 активаторов и подачи питания на регулятор 1326 напряжения памяти, используемый для подачи более высокого напряжения для записи битов 1314 памяти. Регулятор 1326 напряжения памяти может предназначаться для одновременного программирования множественных битов 1314 памяти.

[0089] Фиг. 14 представляет собой чертеж примера матрицы 200, показывающий интерфейсные площадки и логические позиции, используемые для загрузки данных и сигналов управления в матрице. Для пояснения компоновки включена диаграмма 1400 сторон горизонта для указания заданного направления на передней поверхности матрицы. В частности, направление длины матрицы может указываться осью север-юг, тогда как направление ширины матрицы может указываться осью запад-восток (или лево-право). 12 интерфейсных площадок, описанных со ссылкой на фиг. 13, делятся и располагаются на каждом конце матрицы. Северные площадки 1402 представляют собой шесть площадок, расположенных на северном конце матрицы. Перемещающийся от верхнего или северного конца матрицы, север 1404 цифрового регулятора включает в себя логическую схему для декодирования последовательно загружаемых данных и их загрузки в регистры конфигурации или адреса. Секция, называемая севером 1406 конфигурация адресов, используется для отображения адресных данных в адресные линии, проходящие по длине матрицы. Большую часть матрицы занимает участок 1408, который включает в себя столбцовые примитивы, активаторы текучей среды и мощные FET. Биты памяти могут располагаться на севере 1404 цифрового регулятора или в секциях цифровой логики участка 1408.

[0090] Другой набор площадок располагается на юге в матрице. Южные площадки 1410 обеспечивают оставшуюся часть из 12 площадок, рассмотренных со ссылкой на фиг. 13. Они соседствуют с югом 1412 цифрового регулятора, который, как и север 1404 цифрового регулятора, используется для декодирования последовательно загружаемых данных и загрузки битов адреса в регистры адреса. Юг 1414 конфигурации адресов устанавливает соответствие этого набора битов адреса с другим набором адресных линий, проходящих по длине матрицы.

[0091] Фиг. 15 представляет собой принципиальную схему примера последовательной загрузки данных в хранилище 1308 данных. Одинаково обозначенные элементы описаны со ссылкой на фиг. 13. На принципиальной схеме значение бита данных (нуль или единица) помещается на линию 1502 данных. При переднем фронте тактового импульса бит данных загружается в первый блок 1504 данных левого столбца 1506 хранилища 1308 данных. Как использовано здесь, блок данных может означать элемент памяти, триггер или другие декодеры или хранилища, используемые для сохранения и/или сдвига битового значения. Затем другое значение данных придается линии 1502 данных. При заднем фронте тактового импульса новый бит данных загружается в первый блок данных 1508 правого столбца 1510 хранилища 1308 данных. По мере того, как каждый следующий бит данных загружается в столбцы 1506 и 1510 хранилища 1308 данных, предыдущие биты данных, сохраненные в блоках 1504 и 1508 данных, сдвигаются в следующие блоки 1512 и 1514 данных хранилища 1308 данных. Это продолжается, пока весь набор данных не будет загружен в хранилище 1308 данных.

[0092] Как описано здесь, загруженные данные называются группой импульсов возбуждения (FPG). После полной загрузки данных в хранилище 1308 данных начальные данные, называемые здесь головными данными 1516, находятся в окончательных блоках данных хранилища 1308 данных. В некоторых примерах головные данные 1516 включают в себя биты адреса и биты управления. В других примерах порядок битов изменяется, и головные данные 1516 включают в себя только биты адреса. Следующие данные, называемые здесь данными 1518 активатора текучей среды, включают в себя битовое значение в каждом блоке данных для каждого примитива. Битовое значение указывает, подлежит ли возбуждению активатор текучей среды в этом примитиве. В этом примере каждый примитив включает в себя 16 активаторов текучей среды, как описано со ссылкой на фиг. 12. В некоторых примерах существует 256 примитивов, хотя число примитивов зависит от конструкции матрицы. Например, некоторые матрицы могут включать в себя 128 примитивов, 512 примитивов, 1024 примитива или более. В этих примерах все количества примитивов представлены как степень двойки, но количество не ограничивается степенями двойки, и может включать в себя примерно 100 примитивов, примерно 200 примитивов, примерно 500 примитивов и пр. Последний набор данных, называемый здесь хвостовыми данными 1520, может включать в себя биты адреса и другие биты управления, такие как биты управления памятью, биты теплового управления и пр. В этом примере только 21 примитив показан на каждой стороне. Однако, как описано здесь, может быть включено любое количество примитивов.

[0093] В примере данных FPG по таблице 1 адресные данные делятся между головными данными 1516 и хвостовыми данными 1520. Это позволяет делить схему адресации между севером 1404 цифрового регулятора и югом 1412 цифрового регулятора, описанными со ссылкой на фиг. 14. За счет включения информации управления как в головные данные, так и хвостовые данные FPG, схемы матрицы, которые считывают головную и хвостовую информацию, можно сегментировать, обеспечивая возможность, чтобы схемы могли быть распределенными, что в ряде случаев позволяет добиваться сравнительно узкого отпечатка (занимаемой площади) матрицы. Однако, в некоторых случаях адресация, биты теплового управления и другие биты управления могут находиться полностью в головных данных или хвостовых данных FPG, когда схема управления полностью располагается на одном конце матрицы.

[0094] Таблица 1: Иллюстративные данные FPG

[0095] Таким образом, в нормальном режиме работы, в котором площадка 1328 режима, описанная со ссылкой на фиг. 13, имеет значение нуль, данные сдвигаются в блоки данных хранилища 1308 данных как на переднем фронте, так и заднем фронте тактовых импульсов, как описано здесь. В некоторых примерах площадка 1310 возбуждения переводится от 0 к 1 к 0 к 1 к 0 в качестве сигнала возбуждения для возбуждения активатора текучей среды. В этом примере два положительных импульса используются для обеспечения возможности того, чтобы другие последовательности импульсов управляли подогревом матрицы и доступом к памяти.

[0096] Фиг. 16 представляет собой блок-схему примера логической функции 1600 для возбуждения единичного активатора текучей среды в примитиве. Со ссылкой также на фиг. 8-12 логическая функция 1600 показана здесь как логика 806 активатора текучей среды. Как описано здесь, примитивы могут включать в себя 16 активаторов текучей среды. Каждый примитив будет совместно использовать первые логические схемы 1602, тогда как каждый активатор текучей среды будет иметь вторые логические схемы 1604, связанные с логической функцией 1600.

[0097] Для первой логической схемы 1602 совместно используемой всеми активаторами текучей среды в примитиве сигнал 1606 возбуждения принимается от совместно используемой шины возбуждения, которая подключена ко всем примитивам в матрице. Совместно используемая шина возбуждения принимает сигнал 1606 возбуждения от площадки 1310 возбуждения, описанной со ссылкой на фиг. 13. Сигнал 1606 возбуждения генерируется во внешней ASIC. В этом примере сигнал 1606 возбуждения подается на аналоговый блок 1608 задержки, например, для настройки возбуждения примитива для синхронизации с другими примитивами. С каждым примитивом связан блок 1610 данных, как описано для данных 1518 активатора текучей среды по фиг. 15. Блок 1610 данных загружается из линии 1612 данных, идущей из блока данных для предыдущего примитива или контрольного значения. Как описано здесь, блок 1610 данных загружается на переднем фронте тактового импульса 1614 для примитива, расположенного в левом столбце, или на следующем фронте тактового импульса 1614 для примитива, расположенного в правом столбце. Данные 1616 из блока 1610 данных используются на элементе ИЛИ/И 1618 для обеспечения пропускания либо импульса 1620 подогрева, либо сигнала 1606 возбуждения в качестве импульса 1622 активации. В частности, если данные 1616 являются высоким логическим уровнем, то либо сигнал 1606 возбуждения, либо импульс 1620 подогрева проходит в качестве импульса 1622 активации.

[0098] Во вторых логических схемах 1604, связанных с каждым активатором текучей среды, элемент И 1624 принимает импульс 1622 активации, который совместно используется элементами И для всех активаторов текучей среды в примитиве. Адресная линия 1626 исходит от декодера 608 адреса, описанного со ссылкой на фиг. 6. Когда и импульс 1622 активации, и адресная линия имеют высокое логическое значение, элемент И 1624 пропускает сигнал 1628 управления на мощный FET 1630. Мощный FET 1630 10 включается, позволяя току вытекать из Vpp 1632 на Pgnd 1634 через TIJ-резистор 1636. Сигнал 1606 возбуждения может обеспечивать сигнал достаточно долгое время, чтобы вызвать нагрев текучей среды в активаторе текучей среды, приводящий к выбросу капли. Напротив, импульс 1620 подогрева может быть более коротким, позволяя использовать TIJ-резистор 1636 для нагрева матрицы вблизи активатора текучей среды в примитиве.

[0099] Фиг. 17 представляет собой пример принципиальной схемы битов 1314 памяти, затеняющих блоки примитивов в хранилище 1308 данных. Одинаково обозначенные элементы описаны со ссылкой на фиг. 13 и 15. В этом примере биты памяти связаны только с левым столбцом 1506 данных активатора текучей среды, хотя другие примеры могут иметь биты памяти, связанные с обоими столбцами 1506 и 1510 хранилища 1308 данных. К битам 1314 памяти обращаются (адресуются) с помощью комбинации данных активатора текучей среды, адреса возбуждения и, в некоторых примерах, битов регистра конфигурации.

[0100] Головные данные 1516 и хвостовые данные 1520 не связаны с битами 1314 памяти. Однако с битами адреса могут быть связаны особые биты 1702 памяти для конфигурации матрицы. Биты памяти связаны с входными данными как переднего фронта, так и заднего фронта. Бит 1704 блокировки доступа к памяти можно использовать для предотвращения записи в некоторые или все биты 1314 памяти. В некоторых примерах особые биты 1702 памяти переносятся в энергонезависимые защелки 1706 после перехода в состояние сброса.

[0101] Фиг. 18 представляет собой пример блок-схемы регистра 1316 конфигурации, регистра 1318 конфигурации памяти и регистра 1320 состояния. Одинаково обозначенные элементы описаны со ссылкой на фиг. 13. Как описано здесь, регистр 1316 конфигурации предназначен только для записи и использует особую конфигурацию для обеспечения записи. В одном примере регистр 1316 конфигурации разблокируется для записи, когда площадка 1328 режима находится на высоком уровне, данные находятся на высоком уровне, и при первом положительном фронте тактового сигнала. После разблокировки регистра 1316 конфигурации для записи дальнейшие тактовые импульсы будут сдвигать данные через регистр 1316 конфигурации.

[0102] Регистр 1318 конфигурации памяти дополнительно защищен от записи с помощью особой последовательности битов в регистре 1316 конфигурации, сигналов управления и пакетных данных FPG. Например, задание бита 1802 конфигурации памяти в регистре 1316 конфигурации совместно с битом из данных 1804 активатора текучей среды разблокирует запись в регистр 1318 конфигурации памяти. Затем регистр 1318 конфигурации памяти может выдавать биты 1806 управления памятью в хранилище 1308 данных и биты 1314 памяти, например, разблокируя доступ к битам 1314 памяти. В некоторых примерах биты 1314 памяти, доступные для записи, выдаются из соответствующих блоков данных для данных 1518 активатора текучей среды, например, из блоков данных, имеющих те же самые адреса, что и выбранные биты 1314 памяти.

[0103] В некоторых примерах площадка 1310 возбуждения остается на высоком уровне, обеспечивая доступ к памяти. Когда площадка 1310 возбуждения падает до низкого уровня, биты в регистре 1318 конфигурации памяти, а также бит 1802 конфигурации памяти в регистре 1316 конфигурации очищаются. В дополнение к этому примеру можно использовать любое число методов, разблокирующих (разрешающих) доступ к регистру 1318 конфигурации памяти и к битам 1314 памяти.

[0104] Регистр 1320 состояния может быть регистром только для считывания, где записана информация о матрице. В примере считывание регистра 1320 состояния разрешается, когда площадка 1328 режима находится на высоком уровне, значение данных на площадке 1306 данных находится на высоком уровне и на переднем фронте тактового сигнала. В этом примере площадка 1310 возбуждения затем переходит на высокий уровень, позволяя сдвигать данные из регистра состояния и считывать их через площадку 1306 данных, когда сигнал на площадке 1304 тактового сигнала растет и падает. В некоторых примерах регистр 1320 состояния включает в себя бит 1808 сбоя сторожевого таймера, который задан на высокий уровень, чтобы указать состояние ошибки, такой как ожидание. Другие биты в этом примере могут включать в себя биты 1810 версии, например, указывающие номер версии матрицы. В других примерах в регистре 1320 состояния используется больше битов, например, для указания других условий, для добавления битов к номеру версии или для предоставления другой информации о матрице.

[0105] Фиг. 19 представляет собой принципиальную схему примера матрицы 1900, показывающую шину 1330 регистрации для считывания и программирования битов памяти и осуществления доступа к тепловым датчикам. Одинаково обозначенные элементы описаны со ссылкой на фиг. 2 и 13. На принципиальной схеме проиллюстрировано разделение функций между ASIC 202 принтера 1902 и матрицей 1900 печатающей головки 1904.

[0106] В некоторых примерах рассмотренные здесь матрицы используют архитектуру памяти на основе битов энергонезависимой памяти (NVM), которые являются однократно программируемыми (OTP). Биты памяти NVM записываются с использованием особой последовательности доступа, разблокируя регулятор 1326 напряжения памяти. Эта схема регулятора на матрице генерирует высокое напряжение, необходимое для программирования битов памяти, например, примерно 11 В. Однако структуры металл-оксид-полупроводник имеют максимальное рабочее напряжение от примерно 2,5 В до примерно 6 В. При превышении этого низкого напряжения устройства могут быть повреждены. Соответственно архитектура матрицы включает в себя высоковольтные устройства, способные обеспечивать высоковольтную изоляцию низковольтных устройств от напряжения режима записи, генерируемого на матрице.

[0107] Описанные здесь конструкции могут уменьшить количество внутренних соединений системы за счет обеспечения генерации напряжения на матрице в регуляторе 1326 напряжения памяти для записи битов памяти без дополнительных площадок электрического интерфейса. Дополнительно, схема защиты от высокого напряжения на матрице может предотвращать повреждение низковольтных устройств, подключенных к шине 1330 регистрации в ходе записи в память, что позволяет считывать биты памяти через площадку 1332 регистрации. Конструкция регулятора может быть сравнительно несложной, что может быть связано со сравнительно небольшой площадью отпечатка схемы.

[0108] В различных примерах шина 1330 регистрации подключена к термодиодным датчикам 1906, 1908 и 1910 через мультиплексор 1912 под управлением линий 1914 управления, заданных битовыми значениями, загруженными в управляющую логику 1913 матрицы, которая может включать в себя регистр 1316 конфигурации и регистр 1318 управления памятью, помимо других схем. Число термодиодных датчиков не ограничивается тремя, в других примерах может быть пять, семь или более, например, по одному тепловому датчику на примитив. Термодиодные датчики 1906, 1908 и 1910 используются для измерения температуры матрицы, например, на северном конце, южном конце и в середине. Линии 1914 управления от управляющей логики 1913 матрицы выбирают, какой из термодиодных датчиков 1906, 1908 или 1910 подключается к шине 1330 регистрации. Линии 1914 управления также могут использоваться для отмены выбора или отключения всех трех термодиодных датчиков 1906, 1908 и 1910 от шины 1330 регистрации, например, когда память, дефектоскопы или другие датчики подключены. В этом примере все линии 1914 управления могут быть заданы на нуль для отмены выбора термодиодных датчиков 1906, 1908 и 1910.

[0109] В дополнение к подключению к термодиодным датчикам 1906, 1908 и 1910 шина 1330 регистрации используется для считывания программируемых битов памяти через переключатель 1916 защиты от высокого напряжения, подключенный к шине 1918 памяти. В ходе процедуры считывания переключатель 1916 защиты от высокого напряжения активируется для подключения с возможностью обмена данными шины 1918 памяти к шине 1330 регистрации, например, через линию 1920 управления, заданную на битовое значение в управляющей логике 1913 матрицы, например, в регистре 1318 конфигурации памяти. Отдельные биты 1922 выбираются через линии 1924 разрешения бита и доступны через комбинации значений, присвоенных другим площадкам, например, разрешение бита может активироваться комбинацией бита режима памяти в регистре конфигурации, адресных данных примитива и импульса возбуждения.

[0110] Последовательность записи может использовать логику разрешения бита, объединенную с конкретной последовательностью, для блокировки переключателя 1916 защиты от высокого напряжения, что приводит к отключению шины 1918 памяти от шины 1330 регистрации. Линию 1926 управления от управляющей логики 1913 матрицы можно использовать для активации регулятора 1326 напряжения памяти. На регулятор 1326 напряжения памяти с площадки 1340 Vpp подается напряжение примерно 32 В. Затем регулятор 1326 напряжения памяти преобразует его в напряжение примерно 11 В и подает 11 В на шину 1918 памяти в ходе процедуры записи.

[0111] По окончании процедуры записи регулятор 1326 напряжения памяти деактивируется, сбрасывая напряжение на шину 1918 памяти, которая затем может доводиться до потенциала заземления. Когда последовательность записи не активна, считывание из памяти может осуществляться путем задания битового значения в управляющей логике 1913 матрицы, например, в регистре 1318 управления памятью для разблокирования переключателя 1916 защиты от высокого напряжения и подключения шины 1918 памяти к шине 1330 регистрации. Поскольку шина 1330 регистрации является совместно используемой, мультиплексированной шиной, в ходе процедур считывания из памяти мультиплексор 1912 деактивируется, отключая термодиодные датчики 1906, 1908 и 1910 от шины 1330 регистрации. Подобным образом в ходе операций теплового считывания переключатель 1916 защиты от высокого напряжения отключается, отсоединяя шину 1918 памяти от шины 1330 регистрации.

[0112] Фиг. 20 представляет собой блок-схему примера переключателя 1916 защиты от высокого напряжения, используемого для защиты схемы на низковольтных MOS (структурах металл-оксид-полупроводник) от повреждения высоким напряжением. Одинаково обозначенные элементы описаны со ссылкой на фиг. 13 и 19. В примере, показанном на фиг. 20, переключатель 1916 защиты от высокого напряжения включает в себя два включенных навстречу, высоковольтных MOSFET (полевых транзисторах на структуре металл-оксид-полупроводник), каждый из которых с обратными паразитными диодами. Эти два высоковольтных устройства способны обеспечивать защиту между 11 В режима программирования и низковольтной логикой, например, менее примерно 3,6 В, подключенной к шине 1330 регистрации. В некоторых примерах, когда регулятор 1326 напряжения памяти деактивирован, другой MOSFET 2002 можно использовать, чтобы доводить шину 1918 памяти до заземления. Этот MOSFET 2002 может отключаться в ходе последовательности считывания из памяти. Для защиты от условий защелкивания может быть предусмотрен резистор 2004.

[0113] Фиг. 21 представляет собой блок-схему примера регулятора 1326 напряжения памяти. Одинаково обозначенные элементы описаны со ссылкой на фиг. 13, 16 и 19. В этом примере регулятор 1326 напряжения памяти включает в себя три основные подсхемы. Устройство сдвига 2102 уровня напряжения использует матрицу MOSFET для преобразования низковольтного сигнала управления в высоковольтный выходной сигнал для использования высоковольтным резисторным делителем. Затем высоковольтный резисторный делитель 2104 делит напряжение, выдавая выходной сигнал 11 В. Выходной сигнал 11 В проходит через защиту 2106 высоковольтного диода перед поступлением на шину 1918 памяти, например, в ходе цикла записи.

[0114] Фиг. 22A представляет собой блок-схему последовательности операций процесса по примеру способа 2200 формирования компонента печатающей головки. Способ 2200 можно использовать для создания матрицы 304 цветных чернил, используемой в качестве компонента печатающей головки для цветных принтеров, а также матрицы 302 черных чернил, используемой для черных чернил, и матриц других типов, которые включают в себя активаторы текучей среды. Способ 2200 начинается на этапе 2202 с травления отверстий для подачи текучей среды вниз от центра кремниевой подложки. В некоторых примерах сначала наносят слои, затем, после формирования слоев, осуществляют травление отверстий для подачи текучей среды.

[0115] В примере для защиты зон, не подлежащих травлению, на участке матрицы формируется слой полимерного фоторезиста, такого как SU-8. Фоторезист может быть негативным фоторезистом, поперечно сшиваемым светом, или позитивным фоторезистом, который становится более растворимым под воздействием света. В примере маска подвергается воздействию источника UV-света для проявления участков защитного слоя, и участки, не освещенные UV-светом удаляются, например, с помощью вымывания растворителем. В этом примере маска предотвращает поперечное сшивание участков защитного слоя, покрывающего зону отверстий для подачи текучей среды.

[0116] На этапе 2204 для формирования компонента печатающей головки на подложке формируется множество слоев. Слои могут включать в себя поликристаллический кремний, диэлектрик поверх поликристаллического кремния, первый металлический слой, диэлектрик поверх первого металлического слоя, второй металлический слой, диэлектрик поверх второго металлического слоя и слой тантала наверху. Затем поверх кристалла (матрицы) может наслаиваться SU-8 и структурироваться для реализации проточных каналов и активаторов текучей среды. Формирование слоев может осуществляться путем химического осаждения из паровой фазы с осаждением слоев с последующим травлением для удаления ненужных участков. Методы изготовления могут быть стандартным изготовлением, используемым при формировании комплементарных структур металл-оксид-полупроводник (CMOS). Слои, которые могут формироваться на этапе 2204, и положение компонентов дополнительно рассмотрено со ссылкой на фиг. 22B.

[0117] Фиг. 22B представляет собой блок-схему последовательности операций процесса получения компонентов, образованных слоями по этапу 2204 в способе 2200. Способ начинается на этапе 2206 с формирования серии массивов активаторов текучей среды вблизи отверстий для подачи текучей среды. На этапе 2208 формируют серию адресных линий вблизи серии логических схем на низковольтном участке, расположенном с одной стороны от множества отверстий для подачи текучей среды. На этапе 2210 на матрице формируют схему декодера адреса, которая подключается к по меньшей мере части адресных линий для выбора активатора текучей среды в массиве активаторов текучей среды для возбуждения. На этапе 2212 на матрице формируют логическую схему, которая инициирует схему драйвера, расположенную на высоковольтном участке на противоположной стороне от отверстий для подачи текучей среды на основании, по меньшей мере частично, битового значения, связанного с активатором текучей среды.

[0118] Этапы, показанные на фиг. 22B, не следует рассматривать как последовательные. Как будет ясно специалисту в данной области техники, различные линии и схемы (цепи) формируют на матрице одновременно с формированием различных слоев. Дополнительно, процессы, описанные со ссылкой на фиг. 22B, можно использовать для формирования компонентов либо на матрице цветных чернил, либо на матрице черно-белой печати.

[0119] Фиг. 22C представляет собой блок-схему последовательности операций процесса комбинированного способа 2200, демонстрирующую формируемые слои и структуры. Одинаково обозначенные элементы описаны со ссылкой на фиг. 22A и 22B.

[0120] Фиг. 23 представляет собой блок-схему последовательности операций процесса по примеру способа 2300 загрузки данных в компонент печатающей головки. Способ 2300 начинается на этапе 2302, когда битовое значение присваивается площадке данных на компоненте печатающей головки. На этапе 2304 битовое значение на площадке тактового сигнала на компоненте печатающей головки повышается с низкого уровня до высокого уровня для загрузки битового значения в первый блок данных. На этапе 2306 второе битовое значение присваивается площадке данных на компоненте печатающей головки. На этапе 2308 битовое значение площадки тактового сигнала снижается с высокого уровня до низкого уровня для загрузки второго битового значения во второй блок данных.

[0121] Фиг. 24 представляет собой блок-схему последовательности операций процесса по примеру способа 2400 записи бита памяти в компонент печатающей головки. На этапе 2402 шину регистрации изолируют от шины памяти путем деактивации переключателя защиты от высокого напряжения. На этапе 2404 регулятор напряжения памяти активируют, генерируя высокое напряжение на шине памяти для программирования бита памяти. На этапе 2406 выбирают бит памяти из множества битов памяти, соединенных с возможностью обмена данными с шиной памяти. На этапе 2408 бит памяти программируют. Программирование может осуществляться в течение заранее заданного периода времени, такого как примерно 0,1 миллисекунды (мс), примерно 0,5 мс, примерно 1 мс или более, например, до примерно 100 мс. Чем больше время программирования, тем сильнее будет реагировать бит памяти. По истечении заранее заданного периода времени регулятор напряжения памяти может деактивироваться для завершения последовательности программирования.

[0122] Настоящие примеры могут быть подвержены различным модификациям и альтернативным формам и показаны только в иллюстративных целях. Кроме того, следует понимать, что настоящие методы не предназначены ограничиваться конкретными раскрытыми здесь примерами. В действительности считается, что объем приложенной формулы изобретения включает в себя все альтернативы, модификации и эквиваленты, которые очевидны специалистам в области техники, к которой относится раскрытый предмет изобретение.

В примерах предоставлена матрица для печатающей головки. Матрица включает в себя серию массивов активаторов текучей среды. Блок данных связан с каждым из множества массивов активаторов текучей среды. Матрица включает в себя интерфейс, содержащий площадку данных и площадку тактового сигнала, причем битовое значение данных, присутствующее на площадке данных, загружается в первый блок данных, соответствующий первому массиву активаторов текучей среды на переднем фронте тактового сигнала, и загружается во второй блок данных, соответствующий второму массиву активаторов текучей среды на заднем фронте тактового сигнала. 3 н. и 13 з.п. ф-лы, 24 ил., 1 табл.

1. Матрица для печатающей головки, содержащая:

множество массивов активаторов текучей среды;

хранилище данных, содержащее первый и второй столбцы активаторов и блоки данных, причем каждый блок данных связан с соответствующим массивом активаторов текучей среды из множества массивов активаторов текучей среды, каждый блок расположен в соответствующем из первого и второго столбцов активаторов; и

интерфейс, содержащий площадку данных и площадку тактового сигнала, причем блоки данных сконфигурированы таким образом, что битовое значение данных, присутствующее на площадке данных, загружается в первый блок данных, соответствующий первому массиву активаторов текучей среды, на переднем фронте тактового сигнала и загружается во второй блок данных, соответствующий второму массиву активаторов текучей среды, на заднем фронте тактового сигнала, причем последующие битовые значения данных, присутствующие на площадке данных, загружаются в первый и второй блоки данных на соответствующих переднем и заднем фронтах тактового сигнала таким образом, что предыдущие биты данных, сохраненные в первом и втором блоках данных, сдвигаются в следующие блоки данных первого и второго столбцов активаторов, и при этом битовые значения данных, загруженные в первый и второй блоки данных, содержат головные данные и хвостовые данные с адресными данными, разделенными между головными данными и хвостовыми данными.

2. Матрица по п. 1, дополнительно содержащая схему для декодирования загруженных битовых значений данных, причем схема разделена между северным и южным концами матрицы.

3. Матрица по п. 1 или 2, в которой интерфейс содержит площадку возбуждения, причем битовое значение возбуждения на площадке возбуждения разблокирует активатор текучей среды в массиве активаторов текучей среды.

4. Матрица по любому из пп. 1-3, дополнительно содержащая множество битов памяти, причем каждый из множества битов памяти совместно использует адрес с блоком данных для первого массива активаторов текучей среды.

5. Матрица по любому из пп. 1-4, в которой интерфейс содержит площадку режима, причем битовое значение режима на площадке режима управляет режимом доступа к памяти.

6. Матрица по п. 5, дополнительно содержащая регистр конфигурации, причем запись в регистр конфигурации осуществляется при высоком битовом значении режима.

7. Матрица по п. 6, дополнительно содержащая регистр конфигурации памяти, причем запись в регистр конфигурации памяти осуществляется при высоком битовом значении, сохраненном в регистре конфигурации.

8. Матрица по любому из пп. 1-7, в которой первый массив активаторов текучей среды расположен вдоль первой стороны множества отверстий для подачи текучей среды (IFH), а второй массив активаторов текучей среды расположен вдоль второй стороны множества отверстий для подачи текучей среды, и причем второй массив активаторов текучей среды расположен таким образом, что каждый активатор текучей среды позиционирован для печати между парой активаторов текучей среды в первом массиве активаторов текучей среды.

9. Матрица по любому из пп. 1-8, в которой первый массив активаторов текучей среды содержит множество увеличенных активаторов текучей среды, а второй массив активаторов текучей среды содержит множество уменьшенных активаторов текучей среды, причем увеличенный активатор текучей среды расположен между каждой парой уменьшенных активаторов текучей среды.

10. Печатающая головка, содержащая матрицу по любому из пп. 1-9.

11. Печатающая головка по п. 10, в которой множество отверстий для подачи текучей среды находится вблизи множества массивов активаторов текучей среды, причем печатающая головка содержит полимерную опору, содержащую паз, предназначенный для сообщения по текучей среде с сосудом для чернил, и причем множество отверстий для подачи текучей среды осуществляет сообщение по текучей среде множества массивов активаторов текучей среды с сосудом для чернил.

12. Печатающая головка по п. 10, дополнительно содержащая шину, подключенную к матрице и к множеству интерфейсных площадок на картридже принтера.