УРОВЕНЬ ТЕХНИКИ

[0001] Некоторые компоненты печати могут включать в себя массив сопел и/или насосов, каждое/ый из которых включает в себя камеру текучей среды и активатор текучей среды, где активатор текучей среды может активироваться, чтобы вызвать перемещение текучей среды в камере. Некоторые иллюстративные струйные матрицы могут представлять собой печатающие головки, где текучая среда может соответствовать чернилам или агентам печати. Компоненты печати включают в себя печатающие головки для систем 2D (двумерной) и 3D (трехмерной) печати и/или других высокоточных систем раздачи текучей среды.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

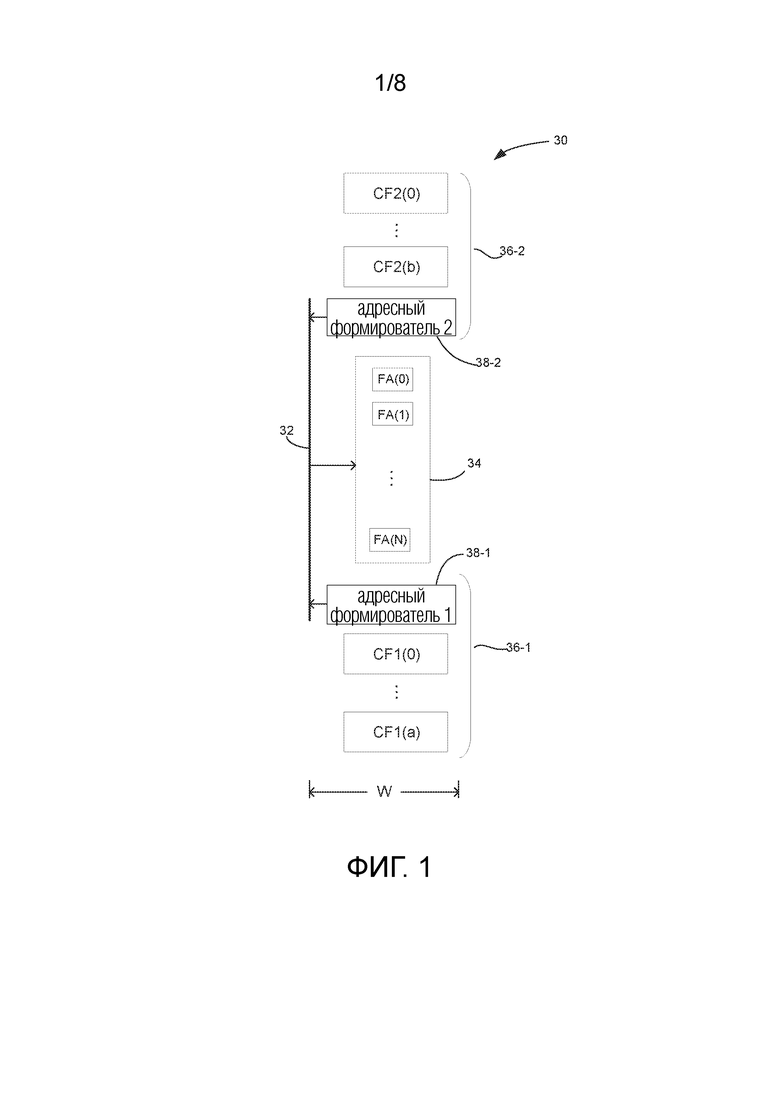

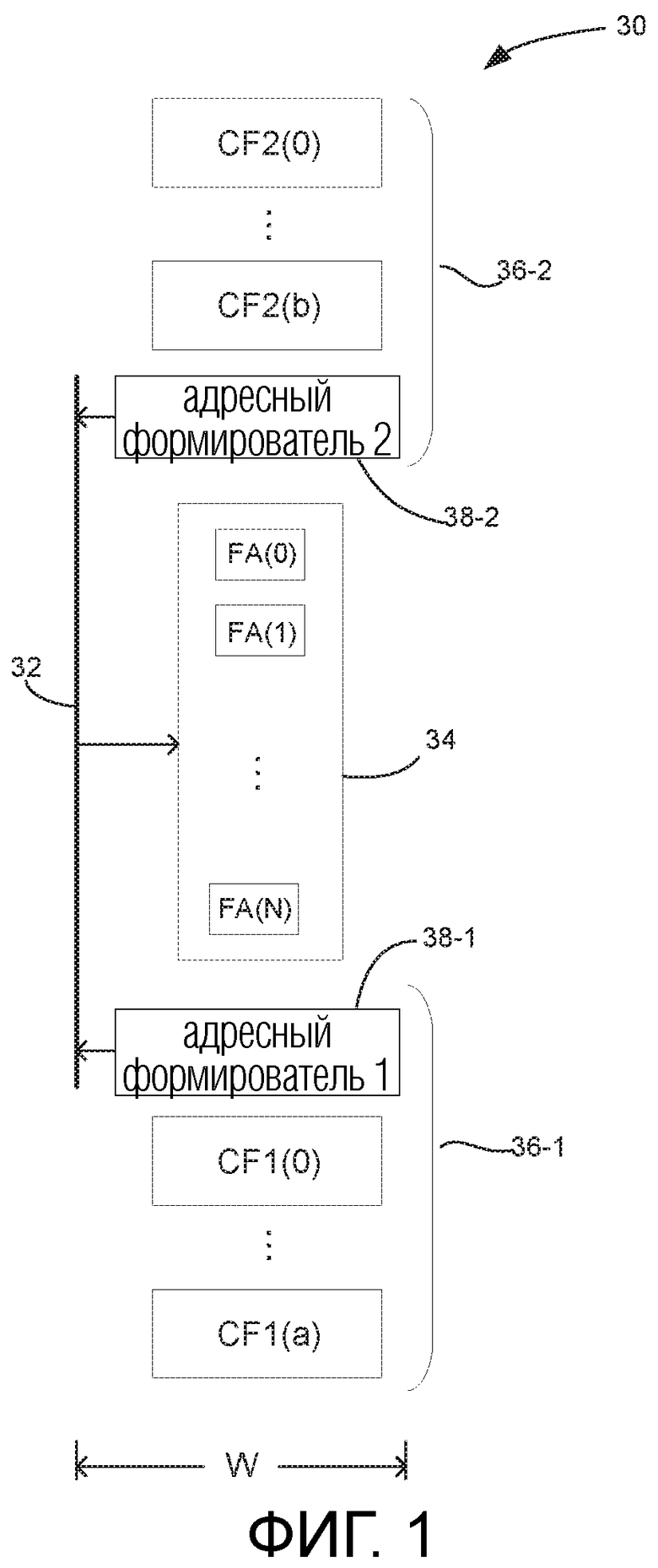

[0002] Фиг. 1 - блок-схема, демонстрирующая интегральную схему для струйной матрицы, согласно одному примеру.

[0003] Фиг. 2 - блок-схема, демонстрирующая струйную матрицу, согласно одному примеру.

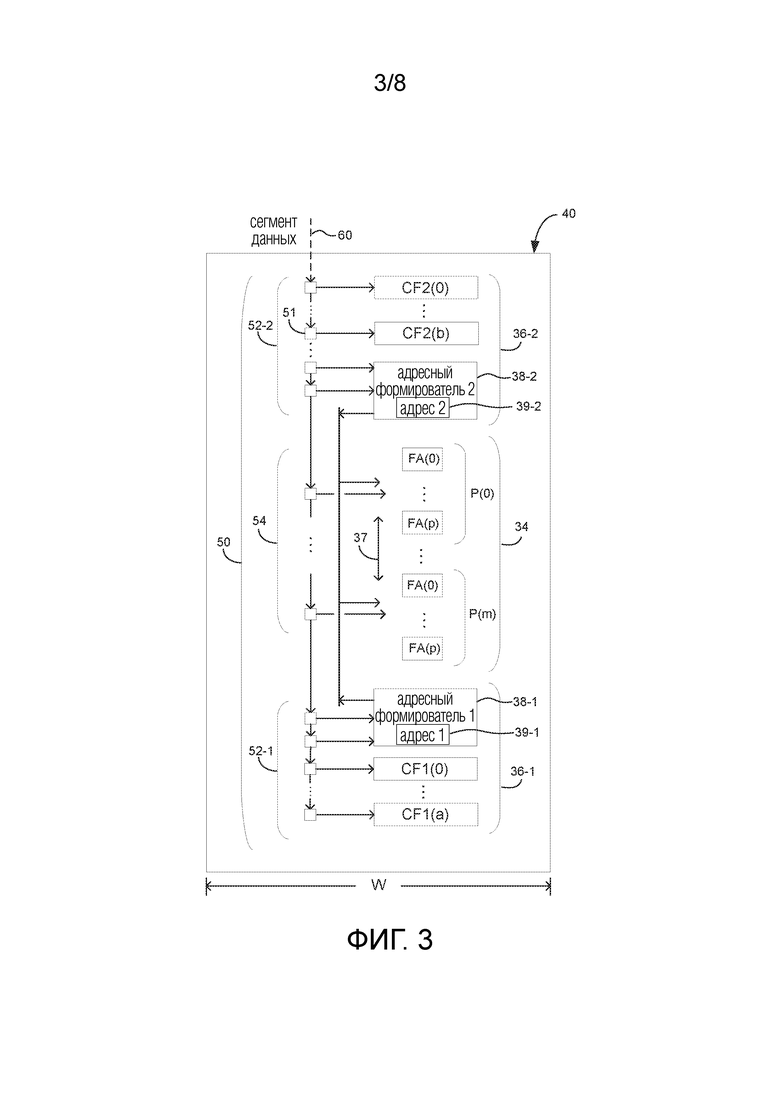

[0004] Фиг. 3 - блок-схема, демонстрирующая струйную матрицу, согласно одному примеру.

[0005] Фиг. 4 - схема, демонстрирующая в целом сегмент данных, согласно одному примеру.

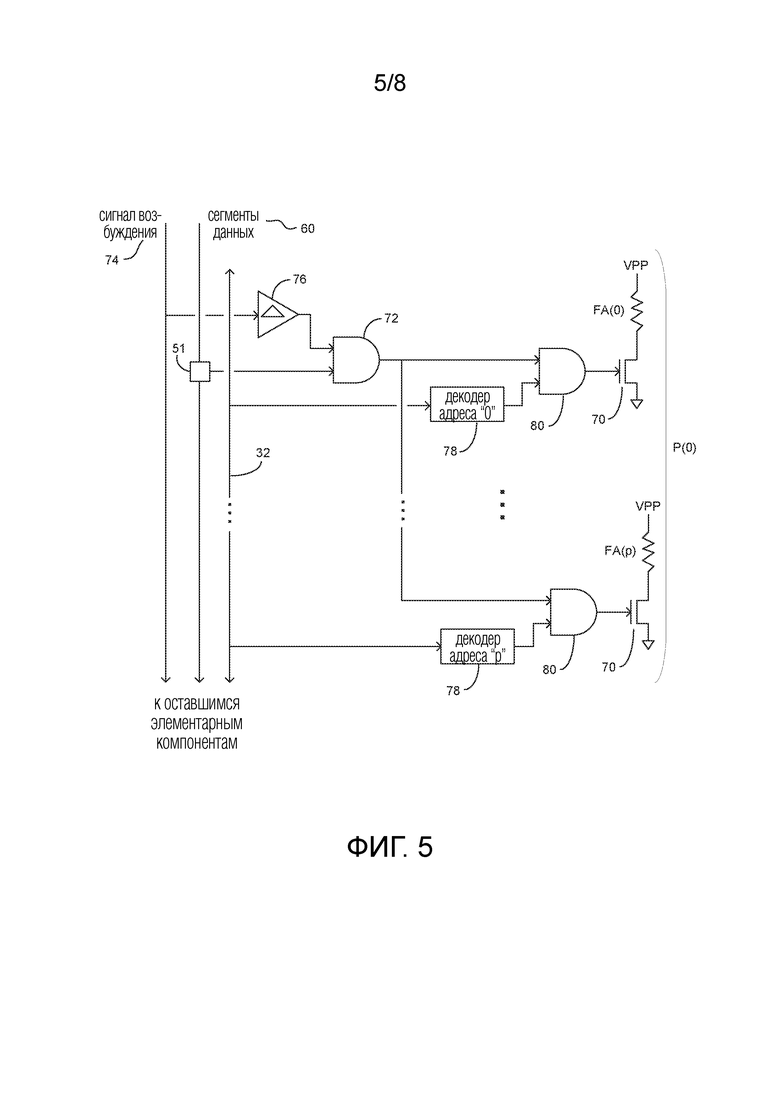

[0006] Фиг. 5 - блок-схема, демонстрирующая в целом участки компоновки элементарных компонентов, согласно одному примеру.

[0007] Фиг. 6 - блок-схема, демонстрирующая интегральную схему для струйной матрицы, согласно одному примеру.

[0008] Фиг. 7 - блок-схема, демонстрирующая один пример системы выброса текучей среды.

[0009] Фиг. 8 - блок-схема операций, демонстрирующая способ работы струйной матрицы, согласно одному примеру.

[0010] На чертежах одинаковые ссылочные позиции указывают аналогичные, но не обязательно одинаковые, элементы. Чертежи не обязательно выполнены в масштабе, и размер некоторых деталей может быть преувеличен, чтобы более наглядно проиллюстрировать показанный пример. Кроме того, чертежи обеспечивают примеры и/или реализации, согласующиеся с описанием; однако описание не ограничивается примерами и/или реализациями, представленными на чертежах.

ПОДРОБНОЕ ОПИСАНИЕ

[0011] Нижеследующее подробное описание, приведено со ссылкой на прилагаемые чертежи, которые составляют его часть, и где в порядке иллюстрации показаны конкретные примеры практического осуществления изобретения. Следует понимать, что можно использовать другие примеры и вносить структурные или логические изменения, не выходя за рамки объема настоящего изобретения. Поэтому нижеследующее подробное описание не следует рассматривать в ограничительном смысле, и объем настоящего изобретения задается нижеследующей формулой изобретения. Следует понимать, что особенности различных описанных здесь примеров можно комбинировать друг с другом частично или полностью, если конкретно не указано обратное.

[0012] Примеры струйных матриц могут включать в себя активаторы текучей среды. Активаторы текучей среды могут включать в себя терморезисторные активаторы (например, для возбуждения или рециркуляции текучей среды), пьезоэлектрические мембранные активаторы, электростатические мембранные активаторы, мембранные активаторы механического/ударного действия, магнитострикционные активаторы или другие подходящие устройства, которые могут вызывать перемещение текучей среды в ответ на электрическую активацию. Описанные здесь струйные матрицы могут включать в себя множество активаторов текучей среды, которое может именоваться массивом активаторов текучей среды. Активация может означать однократное или одновременное возбуждение активаторов текучей среды струйной матрицы, приводящее к перемещению текучей среды. Примером события активации является событие возбуждения текучей среды, в результате которого текучая среда струей выбрасывается через сопло.

[0013] В иллюстративных струйных матрицах массив активаторов текучей среды может быть организован в виде наборов активаторов текучей среды, где каждый такой набор активаторов текучей среды может именоваться “элементарным компонентом” или “элементарным компонентом возбуждения”. Количество активаторов текучей среды в элементарном компоненте может именоваться размером элементарного компонента. В некоторых примерах, активаторы текучей среды каждого элементарного компонента адресуются с использованием одного и того же набора адресов активации, причем каждый активатор текучей среды элементарного компонента соответствует отличному от других адресу активации из набора адресов активации. В примерах, набор адресов передается каждому элементарному компоненту через шину адреса, которая совместно используется всеми элементарными компонентами.

[0014] В одном примере, помимо адресных данных, каждый элементарный компонент принимает данные активации (иногда именуемые данными возбуждения или данными сопел) по соответствующей линии данных, и сигнал возбуждения (также именуемый импульсом возбуждения) по линии сигнала возбуждения. В одном примере, в ходе активации или события возбуждения, при наличии сигнала возбуждения на линии сигнала возбуждения, в каждом элементарном компоненте активатор текучей среды, соответствующий адресу, передаваемому по линии адреса, будет активировать (например, возбуждать) на основании данных активации, соответствующих элементарному компоненту.

[0015] В ряде случаев эксплуатационные ограничения по электричеству и текучей среде струйной матрицы могут ограничивать возможности активаторов текучей среды каждого элементарного компонента одновременно активироваться для данного события активации. Элементарные компоненты облегчают активацию поднаборов активаторов текучей среды, которые могут одновременно активироваться для данного события активации в соответствии с такими эксплуатационными ограничениями.

[0016] Для иллюстрации в порядке примера, если струйная матрица содержит четыре элементарного компонента, причем каждый элементарный компонент включает в себя восемь активаторов текучей среды (причем каждый активатор текучей среды соответствует отличному от других адресу из набора адресов 0-7), и где ограничения по электричеству и текучей среде ограничивают активацию одним активатором текучей среды для каждого элементарного компонента, всего четыре активатора текучей среды (по одному из каждого элементарного компонента) могут одновременно активироваться для данного события активации. Например, для первого события активации, может активироваться соответствующий активатор текучей среды каждого элементарного компонента, соответствующий адресу “0”. Для второго события активации, может активироваться соответствующий активатор текучей среды каждого элементарного компонента, соответствующий адресу “5”. Очевидно, что такой пример приведен лишь в целях иллюстрации, причем рассматриваемые здесь струйные матрицы могут содержать больше или меньше активаторов текучей среды для каждого элементарного компонента и больше или меньше элементарных компонентов для каждой матрицы.

[0017] Иллюстративные струйные матрицы могут включать в себя камеры текучей среды, отверстия и/или другие признаки, которые могут задаваться поверхностями, изготовленными на подложке струйной матрицы в процессах травления, микропроизводства (например, фотолитографии), микрообработки или других подходящих процессах или их комбинациях. Некоторые иллюстративные подложки могут включать в себя кремниевые подложки, стеклянные подложки, подложки из арсенида галлия и/или подложки других подходящих типов для микроизготовленных устройств и структур. Используемый здесь термин "камеры текучей среды" может включать в себя эжекторные камеры в сообщении по текучей среде с отверстиями сопел, из которых может выбрасываться текучая среда, и каналами текучей среды, по которым текучая среда может передаваться. В некоторых примерах каналы текучей среды могут быть микроканалами текучей среды, причем используемый здесь термин "микроканал текучей среды" может соответствовать каналу достаточно малого размера (например, порядка нанометров, порядка микронов, порядка миллиметров и т.д.) для облегчения переноса малых объемов текучей среды (например, порядка пиколитров, порядка нанолитров, порядка микролитров, порядка миллилитров и т.д.).

[0018] В некоторых примерах активатор текучей среды может быть скомпонован как часть сопла где, помимо активатора текучей среды, сопло включает в себя эжекторную камеру в сообщении по текучей среде с отверстием сопла. Активатор текучей среды располагается относительно камеры текучей среды так, что активация активатора текучей среды приводит к перемещению текучей среды в камере текучей среды, что может приводить к выбросу капли текучей среды из камеры текучей среды через отверстие сопла. Соответственно, активатор текучей среды, скомпонованный как часть сопла, иногда может именоваться эжектором текучей среды или активатором выброса.

[0019] В некоторых примерах активатор текучей среды может быть скомпонован как часть насоса, где, помимо активатора текучей среды, насос включает в себя канал текучей среды. Активатор текучей среды располагается относительно канала текучей среды так, что активация активатора текучей среды приводит к перемещению текучей среды в канале текучей среды (например, микроканале текучей среды) для переноса текучей среды в струйной матрице, например, между источником текучей среды и соплом. Пример перемещения/нагнетания текучей среды в матрице иногда также именуется микро-рециркуляцией. Активатор текучей среды, предназначенный для переноса текучей среды в канале текучей среды, иногда называют неинжекционным или микро-рециркуляционным активатором. В одном примере сопла активатор текучей среды может содержать тепловой активатор, где активация активатора текучей среды (иногда именуемая “возбуждением”) нагревает текучую среду для формирования в камере текучей среды движущего пузырька газа, что может приводить к выбросу капли текучей среды из отверстия сопла. Как описано выше, активаторы текучей среды могут быть скомпонованы в виде массивов (таких как столбцы, например), где активаторы могут быть реализованы в виде эжекторов текучей среды и/или насосов, причем выборочное использование эжекторов текучей среды приводит к выбросу капель текучей среды, и выборочное использование насосов приводит к перемещению текучей среды в струйной матрице. В некоторых примерах, активаторы текучей среды таких массивов могут быть скомпонованы в виде элементарных компонентов.

[0020] Некоторые струйные матрицы принимают данные в виде пакетов данных, иногда именуемых группами импульсов возбуждения или пакетами данных группы импульсов возбуждения, где каждая группа импульсов возбуждения включает в себя головную часть и серединную часть. В некоторых примерах, головная часть включает в себя, например, данные конфигурации для функционального элемента конфигурации на матрице, например, адресные данные (представляющие адрес из набора адресов активации) для адресных формирователей, данные импульса возбуждения для схемы управления импульсами возбуждения, и данные датчиков для схемы управления датчиками (например, выбирающей и конфигурирующей тепловые датчики). В одном примере, серединная часть каждой группы импульсов возбуждения включает в себя данные активатора, которые позволяют выбрать, какие сопла, соответствующие адресу, представленному адресными данными в головной части, будут активироваться в ответ на импульс возбуждения.

[0021] В некоторых струйных матрицах адресный формирователь принимает адресные биты данных из головной части каждой группы импульсов возбуждения и направляет адрес, представленный битами данных, в шину адреса, причем шина адреса передает адрес массиву активаторов текучей среды. Помимо направления адреса, представленного битами адреса группы импульсов возбуждения, в шину адреса, в ряде случаев, адресные формирователи также направляют в шину адреса дополняющие адреса.

[0022] Схема адресного формирователя занимает сравнительно большую площадь кремния на струйной матрице, что увеличивает размер и стоимость матрицы. Как будет описано здесь более подробно, согласно примерам настоящего изобретения, схема адресного формирователя делится на множественные участки, каждый из которых направляет в шину адреса отличную от других часть адреса. В одном примере адресный формирователь делится на два участка, каждый из которых направляет в шину адреса отличную от других часть адреса активации. Благодаря делению адресного формирователя на множественные участки, можно сохранить размер необходимой области кремния в по меньшей мере одном направлении, например, направлении ширины, и уменьшить струйную матрицу в по меньшей мере одном направлении матрицы.

[0023] На фиг. 1 показана блок-схема, демонстрирующая в целом интегральную схему 30 для массива активаторов текучей среды, согласно одному примеру настоящего изобретения. В одном примере, интегральная схема 30 составляет часть струйной матрицы, которая будет более подробно описана ниже. Интегральная схема 30 включает в себя шину 32 адреса для передачи набора адресов в массив 34 устройств активации текучей среды, проиллюстрированных как устройства FA(0) - FA(N) активации текучей среды, где устройства FA(0) - FA(N) активации текучей среды адресуются с использованием набора адресов. В одном примере, каждое устройство FA(0) - FA(N) активации текучей среды соответствует отличному от других одному из адресов из набора адресов. В одном примере, устройства FA(0) - FA(N) активации текучей среды массива 34 располагаются в виде столбца.

[0024] В одном примере, интегральная схема 30 включает в себя первую группу 36-1 функциональных элементов конфигурации, включающую в себя первый адресный формирователь 38-1 и несколько дополнительных функциональных элементов конфигурации, проиллюстрированных как CF1(0) - CF1(a), и вторую группу 36-2 функциональных элементов конфигурации, включающую в себя второй адресный формирователь 38-2 и несколько дополнительных функциональных элементов конфигурации проиллюстрированных как CF2(0) - CF2(b). В ряде случаев, помимо адресных формирователей 38-1 и 38-2, дополнительные функциональные элементы CF1(0) - CF1(a) и CF2(0) - CF2(b) конфигурации первой и второй групп 36-1 и 36-2 функциональных элементов конфигурации включают в себя, помимо прочего, например, функциональный элемент конфигурации управления импульсами возбуждения (например, для регулировки конфигураций подогрева, предшественника и импульса возбуждения), и функциональные элементы конфигурации датчиков (например, для выбора и управления конфигурациями тепловых датчиков).

[0025] В ходе работы, первый адресный формирователь 38-1 направляет первую часть адреса из набора адресов в шину 32 адреса, и второй адресный формирователь 38-2 направляет оставшуюся часть адреса из набора адресов в шину 32 адреса, где по меньшей мере одно из устройств активации текучей среды массива 34 устройств активации текучей среды соответствует адресу, направленному в шину 32 адреса первым и вторым адресными формирователями 38-1 и 38-2. Благодаря делению адресного формирователя на множественные участки, например, на адресные формирователи 38-1 и 38-2, как показано на фиг. 1, место на кремнии, необходимое для схемы адресного формирователя в по меньшей мере одном направлении, например, направлении ширины, W, уменьшается, что позволяет струйной матрице, часть которой может составлять интегральная схема 30, быть меньше в по меньшей мере одном направлении.

[0026] На фиг. 2 показана блок-схема, демонстрирующая пример струйной матрицы 40, в соответствии с одним примером настоящего изобретения. Согласно проиллюстрированному примеру, в дополнение к массиву активаторов 34 текучей среды, который, как описано выше, адресуется набором адресов, струйная матрица 40 включает в себя первый адресный формирователь 38-1, который обеспечивает первую часть адреса из набора адресов на основании первого набора битов 39-1 адреса, и второй адресный формирователь 38-2, который обеспечивает вторую часть адреса из набора адресов на основании второго набора битов 39-2 адреса. В одном примере, первый и второй наборы битов адреса совместно обеспечивают один адрес из набора адресов.

[0027] Струйная матрица 40 дополнительно включает в себя массив элементов памяти 50, например, проиллюстрированный элементом 51 памяти. Согласно одному примеру, массив элементов памяти 50 включает в себя первую часть элементов 52-1 памяти, соответствующую первому адресному формирователю 38-1, вторую часть элементов 52-2 памяти, соответствующую второму адресному формирователю 38-2, и третью часть элементов 54 памяти, соответствующую массиву активаторов 34 текучей среды. В одном примере, массив элементов памяти 50 служит для последовательной загрузки сегментов 60 данных, причем каждый сегмент данных включает в себя последовательность битов данных, благодаря чему по завершении загрузки сегмента 60 данных, элементы памяти первой части элементов 52-1 памяти сохраняют первый набор битов 39-1 адреса, и элементы памяти второй части элементов 52-2 памяти сохраняют второй набор битов 39-2 адреса. Согласно примерам, первый и второй адресные формирователи 38-1 и 38-2 соответственно принимают первый и второй наборы битов 39-1 и 39-2 адреса из первого и второго участков элементов 52-1 и 52-2 памяти для обеспечения первого и второго участков адреса из набора адресов массиву активаторов 34 текучей среды.

[0028] В одном примере, активаторы текучей среды массива активаторов 34 текучей среды располагаются в виде столбца, проходящего в продольном направлении 37. В одной компоновке, как показано, первый и второй адресные формирователи 38-1 и 38-2 располагаются на противоположных концах столбца активаторов текучей среды (FA) массива 34. В одном примере, элементы памяти 41 массива элементов памяти 40 располагаются в виде цепочки или последовательности элементов памяти, реализованной как последовательно-параллельный преобразователь данных, причем последовательность элементов памяти проходит в продольном направлении 37 массива активаторов 34 текучей среды, благодаря чему первый и второй участки элементов 52-1 и 52-2 памяти располагаются, соответственно, рядом с первым и вторым адресными формирователями 38-1 и 38-2, и третья часть элементов 54 памяти располагается рядом с массивом активаторов 34 текучей среды.

[0029] Благодаря расположению первого и второго адресных формирователей 38-1 и 38-2 на противоположных концах столбца активаторов FA(0) - FA(N) текучей среды массива активаторов 34 текучей среды, и благодаря организации массива элементов памяти 50 в виде цепочки элементов памяти, проходящей в продольном направлении 37, место на кремнии, необходимое в по меньшей мере одном направлении струйной матрицы 40, например направлении ширины, W, уменьшается, что позволяет уменьшить ширину струйной матрицы 40.

[0030] На фиг. 3 показана блок-схема, демонстрирующая пример струйной матрицы 40, в соответствии с настоящим изобретением. В одном примере показано, что массив активаторов 34 текучей среды реализован в виде столбца активаторов текучей среды, проходящих в продольном направлении 37, причем столбец активаторов текучей среды выполнен с возможностью формирования нескольких элементарных компонентов, проиллюстрированных как элементарные компоненты P(0) - P(m). В примере, каждый элементарный компонент P(0) - P(m) имеет несколько активаторов текучей среды, проиллюстрированных как активаторы FA(0) - FA(p) текучей среды. В одном примере, каждый элементарный компонент P(0) - P(m) использует один и тот же набор адресов, причем каждый активатор FA(0) - FA(p) текучей среды каждого элементарного компонента соответствует отличному от других одному из адресов из набора адресов, например, отличному от других адресу из набора адресов A(0) - A(p).

[0031] Первая группа 36-1 функциональных элементов конфигурации включает в себя первый адресный формирователь 38-1 и несколько дополнительных функциональных элементов CF1(0) - CF1(a) конфигурации, и вторая группа 36-2 функциональных элементов конфигурации включает в себя второй адресный формирователь 38-2 и несколько дополнительных функциональных элементов CF2(0) - CF2(b) конфигурации. Первый адресный формирователь 38-1 направляет первую часть адреса из набора адресов в шину 32 адреса на основании первого набора битов 39-1 адреса, и второй адресный формирователь 38-2 направляет оставшуюся часть адреса из набора адресов на основании второго набора битов 39-2 адреса, тогда как шина 32 адреса, в свою очередь, передает адрес на каждый элементарный компонент P(0) - P(m). В одном показанном примере, первая и вторая группы функциональных элементов 36-1 и 36-2 конфигурации располагаются в продольном направлении 37 на противоположных концах массива активаторов 34 текучей среды.

[0032] В одном показанном примере, массив элементов памяти 50 содержит последовательность или цепочку элементов 51 памяти, реализованную как последовательно-параллельный преобразователь данных, причем первая часть 52-1 элементов 51 памяти соответствует первой группе 36-1 функциональных элементов конфигурации, вторая часть элементов 52-2 памяти соответствует вторичной группе 36-2 функциональных элементов конфигурации, и третья часть элементов 54 памяти соответствует массиву активаторов 34 текучей среды, причем каждый элемент 51 памяти третьей части 54 соответствует отличному от других одному из элементарных компонентов P(0) - P(m). В одном примере, массив элементов памяти 50 содержит последовательную логическую схему (например, массивы триггеров, массивы защелок и т.д.). В одном примере последовательная логическая схема способна функционировать как сдвиговый регистр с последовательным входом и параллельным выходом.

[0033] В одном примере цепочка элементов 51 памяти массива 50 проходит в продольном направлении 37, причем первая часть ячеек 52-1 памяти располагается рядом с первой группой 36-1 функциональных элементов конфигурации, вторая часть ячеек 52-2 памяти располагается рядом со второй группой 36-2 функциональных элементов конфигурации, и третья группа ячеек 54 памяти проходит между первым и вторым участками ячеек 52-1 и 52-2 памяти и рядом со столбцами активаторов (FA) текучей среды массива 34.

[0034] Пример работы струйной матрицы 40, например, как показано на фиг. 3, описан ниже со ссылкой на фиг. 4 и 5. На фиг. 4 показана блок-схема, демонстрирующая в целом пример сегмента 60 данных, принятого массивом элементов памяти 50 струйной матрицы 40. Как показано, сегмент 60 данных включает в себя последовательность битов данных, например, проиллюстрированных битом 61 данных, включающую в себя первую часть 62-1 битов данных, иногда именуемую “головой”, вторую часть 62-2 битов данных, иногда именуемую “хвостом”, и третью часть 64 битов данных, иногда именуемую “серединой”. Совместно, первый, второй и третий участки 62-1, 62-2 и 64 битов данных именуются группой импульсов возбуждения.

[0035] Первая часть 62-1 битов данных содержит биты данных для первой группы 36-1 функциональных элементов конфигурации, включая первый набор адресных битов данных 39-1 для первого адресного формирователя 38-1. Вторая часть 62-2 битов данных содержит биты данных для второй группы 36-2 функциональных элементов конфигурации, включая второй набор адресных битов данных 39-2 для второго адресного формирователя 38-2. Третья часть 64 битов данных включает в себя биты данных активации для массива активаторов 34 текучей среды, причем каждый бит 61 данных третьей части 64 битов данных соответствует отличному от других одному из элементарных компонентов P(0) - P(m). Биты данных третьей части 64 битов данных иногда именуются данными элементарного компонента.

[0036] Согласно фиг. 3 (и фиг. 2), каждый сегмент 60 данных из последовательности таких сегментов данных последовательно загружается в массив элементов памяти 50, начиная с первого бита головной части 62-1 и заканчивая последним битом хвостовой части 62-2. Будучи последовательно загружены или перемещены в массив элементов памяти 50, биты 61 данных головной части 62-1 сегмента 60 данных сохраняются в первой части элементов 52-1 памяти, причем первый набор битов 39-1 адреса соответствует первому адресному формирователю 38-1. Аналогично, биты 61 данных хвостовой части 62-2 сегмента 60 данных сохраняются во второй части элементов 52-2 памяти, причем второй набор битов 39-2 адреса соответствует второму адресному формирователю 38-2. Биты 61 данных третьей части 64 сегмента 60 данных сохраняются в третьей части 54 массива элементов памяти 50.

[0037] На фиг. 5 показана блок-схема, демонстрирующая в целом участки компоновки элементарных компонентов, например, элементарный компонент P(0) на фиг. 3. В одном примере, каждый активатор FA текучей среды проиллюстрирован как терморезистор на фиг. 5 и может подключаться между источником питания, Vpp, и опорным потенциалом (например, заземлением) через соответствующий управляемый переключатель, например проиллюстрированный как 70 FET.

[0038] Согласно одному примеру, каждый элементарный компонент, включая элементарный компонент P(0), включает в себя логический вентиль 72 И, принимающий, на первом входе, данные элементарного компонента (например, данные активатора) для элементарного компонента P(0) из соответствующего элемента 51 памяти третьей группы элементов 54 памяти массива элементов памяти 50. На втором входе, логический вентиль 72 И принимает сигнал 74 возбуждения (например, импульс возбуждения), который регулирует длительность активации или возбуждения активатора текучей среды, например, активатора FA(0) текучей среды. В одном примере, сигнал 74 возбуждения задерживается элементом 76 задержки, причем каждый элементарный компонент имеет отличную от других задержку, благодаря чему, возбуждение активаторов текучей среды осуществляется не одновременно для всех элементарных компонентов P(0) - P(m).

[0039] В одном примере, каждый активатор (FA) текучей среды имеет соответствующий декодер 78 адреса, принимающий адрес, направляемый в шину 32 адреса первым и вторым адресными формирователями 38-1 и 38-2, и соответствующий логический вентиль 80 И для управления вентилем 70 FET. Логический вентиль 80 И принимает выходной сигнал соответствующего декодера 78 адреса на первом входе и выходной сигнал логического вентиля 72 И на втором входе. Заметим, что декодер 78 адреса и логический вентиль 80 И повторяются для каждого активатора FA текучей среды, тогда как логический вентиль 72 И и элемент 76 задержки повторяются для каждого элементарного компонента.

[0040] В одном примере, будучи загружены в массив элементов памяти 50, данные группы импульсов возбуждения, представленные битами 61 данных головного, хвостового и серединного участков 62-1, 62-2 и 64 сегмента 60 данных (см. фиг. 4), обрабатываются соответствующими группами функциональных элементов 38-1-38-2 конфигурации и элементарным компонентам P(0) - P(m) для задействования выбранных активаторов (FA) текучей среды для циркуляции текучей среды или выброса капель текучей среды. Например, со ссылкой на фиг. 5, в одном примере, если данные активатора, сохраненные в элементе 51 памяти, соответствующем элементарному компоненту P(0), имеют логически высокое значение (например, “1”), и импульсный возбуждающий сигнал 74 присутствует на входе логического вентиля 72 И, выходной сигнал логического вентиля 72 И устанавливается логически “высоким”. Если адрес, направляемый на шину 32 адреса первым и вторым адресными формирователями 38-1 и 38-2 в ответ на наборы битов 39-1 и 39-2 адреса, принятые от соответствующих элементов памяти первого и второго участков элементов 54-1 и 54-2 памяти представляет адрес “0”, выходной сигнал декодера 78 адреса “0” устанавливается логически “высоким”. Когда выходные сигналы логического вентиля 72 И и декодера 78 адреса “0” установлены логически “высокими”, выходной сигнал логического вентиля 80 И также устанавливается логически “высоким”, таким образом, "включая" соответствующий 70 FET для подачи питания на активатор FA(0) текучей среды для перемещения текучей среды (например, выброса капли текучей среды), где длительность работы каждого активатора FA(0) текучей среды определяется импульсным возбуждающим сигналом 74.

[0041] На фиг. 6 показана блок-схема, демонстрирующая в целом интегральную схему 90 для массива активаторов текучей среды, согласно одному примеру настоящего изобретения. В одном примере, интегральная схема 30 реализована в виде части струйной матрицы. Интегральная схема 90 включает в себя последовательность элементов 100 памяти, включающую в себя первую часть 102-1 элементов памяти, соответствующую первой группе 106-1 функциональных элементов конфигурации матрицы, вторую часть 102-2 элементов памяти, соответствующую второй группе 106-2 функциональных элементов конфигурации матрицы, и третью часть 104 элементов памяти, соответствующую массиву активаторов текучей среды 108, причем элементы памяти третьей части 104 элементов памяти проходят между первой и второй частями 102-1 и 102-2 элементов памяти.

[0042] В одном примере, массив активаторов текучей среды 108 включает в себя несколько активаторов текучей среды, указанных как активаторы FA(0) - FA(n) текучей среды. В одном примере, первая группа 106-1 функциональных элементов конфигурации включает в себя несколько функциональных элементов конфигурации, указанных как CF1(0) - CF1(a), и вторая группа функциональных элементов конфигурации 106-2 включает в себя несколько функциональных элементов конфигурации, указанных как CF2(0) - CF2(b). В примерах, функциональные элементы конфигурации матрицы могут включать в себя такие функциональные элементы, как адресные формирователи для направления адресов, связанных с массивом активаторов текучей среды 108, схему управления импульсами возбуждения для регулировки времени активации или возбуждения активаторов текучей среды массива активаторов текучей среды 108 посредством сигнала возбуждения, и схему управления датчиками для конфигурирования схемы датчиков (например, выбирающей и конфигурирующей тепловые датчики).

[0043] В примерах, последовательность элементов 100 памяти последовательно загружает сегменты данных, включающие в себя последовательность битов данных, например, сегмент 60 данных проиллюстрированный на фиг. 4, благодаря чему, по завершении загрузки сегмента данных, элементы памяти первой части 102-1 элементов памяти сохраняют биты данных для первой группы 106-1 функциональных элементов конфигурации матрицы, вторая часть 102-2 элементов памяти сохраняет биты данных для второй группы 106-2 функциональных элементов конфигурации матрицы, и третья часть 104 элементов памяти сохраняет биты данных для массива активаторов текучей среды 108.

[0044] На фиг. 7 показана блок-схема, демонстрирующая один пример системы 200 выброса текучей среды. Система 200 выброса текучей среды включает в себя агрегат выброса текучей среды, например, агрегат 204 печатающей головки и агрегат подачи текучей среды, например, агрегат 216 подачи чернил. В иллюстрируемом примере, система 200 выброса текучей среды также включает в себя агрегат 208 станции технического обслуживания, агрегат 222 каретки, агрегат 226 транспортировки носителей печати и электронный контроллер 230. Хотя нижеследующее описание обеспечивает примеры систем и агрегатов для обработки текучей среды в отношении чернил, раскрытые системы и агрегаты применимы также к обработке текучих сред, отличных от чернил.

[0045] Агрегат 204 печатающей головки включает в себя по меньшей мере одну печатающую головку 212, которая выбрасывает капли чернил или текучей среды через множество отверстий или сопел 214, где печатающая головка 212 может быть реализована, в одном примере, с использованием интегральной схемы 30, где активаторы FA(0) - FA(N) текучей среды реализованы в виде сопел 214, как описано ранее здесь со ссылкой, например, на фиг. 1. В одном примере, капли направляются к носителю, например, носителю 232 печати, для печати на носителе 232 печати. В одном примере, носители 232 печати включают в себя лист материала любого подходящего типа, например, бумагу, стопку карточек, диапозитивы, майлар, ткань и пр. В другом примере, носители 232 печати включают в себя носители для трехмерной (3D) печати, например, порошковую подушку, или носители для биопечати и/или тестирования для поиска новых лекарств, например, резервуар или контейнер. В одном примере, сопла 214 располагаются в по меньшей мере одном столбце или массиве, благодаря чему, надлежащим образом упорядоченный выброс чернил из сопел 214 обеспечивает печать знаков, символов и/или других графических объектов или изображений на носителях 232 печати, когда агрегат 204 печатающей головки и носители 232 печати перемещаются относительно друг друга.

[0046] Агрегат 216 подачи чернил подает чернила на агрегат 204 печатающей головки и включает в себя резервуар 218 для хранения чернил. Таким образом, в одном примере, чернила текут из резервуара 218 в агрегат 204 печатающей головки. В одном примере, агрегат 204 печатающей головки и агрегат 216 подачи чернил заключены совместно в картридже или печатающем элементе струйной или жидкостно-струйной печати. В другом примере, агрегат 216 подачи чернил отделен от агрегата 204 печатающей головки и подает чернила на агрегат 204 печатающей головки через интерфейсное соединение 220, например, питающую трубку и/или клапан.

[0047] Агрегат 222 каретки позиционирует агрегат 204 печатающей головки относительно агрегата 226 транспортировки носителей печати, и агрегат 226 транспортировки носителей печати позиционирует носители 232 печати относительно агрегата 204 печатающей головки. Таким образом, зона 234 печати задается рядом с соплами 214 в области между агрегатом 204 печатающей головки и носителями 232 печати. В одном примере, агрегат 204 печатающей головки является агрегатом печатающей головки сканирующего типа, благодаря чему, агрегат 222 каретки перемещает агрегат 204 печатающей головки относительно агрегата 226 транспортировки носителей печати. В другом примере, агрегат 204 печатающей головки является агрегатом печатающей головки несканирующего типа, благодаря чему, агрегат 222 каретки фиксирует агрегат 204 печатающей головки в предписанной позиции относительно агрегата 226 транспортировки носителей печати.

[0048] Агрегат 208 станции технического обслуживания обеспечивает обрызгивание, протирку, закупоривание и/или заправку агрегата 204 печатающей головки для поддержания функционала агрегата 204 печатающей головки и, в частности, сопел 214. Например, агрегат 208 станции технического обслуживания может включать в себя резиновый нож или протир, который периодически проходит по агрегату 204 печатающей головки для протирки и очистки сопел 214 от избытка чернил. Кроме того, агрегат 208 станции технического обслуживания может включать в себя колпачок, который покрывает агрегат 204 печатающей головки для защиты сопел 214 от пересыхания в периоды простоя. Кроме того, агрегат 208 станции технического обслуживания может включать в себя контейнер для сбора излишков чернил, куда агрегат 204 печатающей головки выбрасывает чернила в ходе выбросов, чтобы гарантировать, что резервуар 218 поддерживает надлежащий уровень давления и текучести, и чтобы гарантировать, что сопла 214 не засоряются и не текут. Функции агрегата 208 станции технического обслуживания могут включать в себя относительное перемещение между агрегатом 208 станции технического обслуживания и агрегатом 204 печатающей головки.

[0049] Электронный контроллер 230 осуществляет связь с агрегатом 204 печатающей головки по пути 206 связи, агрегатом 208 станции технического обслуживания по пути 210 связи, агрегатом 222 каретки по пути 224 связи и агрегатом 226 транспортировки носителей печати по пути 228 связи. В одном примере, когда агрегат 204 печатающей головки установлен в агрегате 222 каретки, электронный контроллер 230 и агрегат 204 печатающей головки могут осуществлять связь через агрегат 222 каретки по пути связи 202. Электронный контроллер 230 также может осуществлять связь с агрегатом 216 подачи чернил, благодаря чему, в одной реализации, можно обнаружить новый (или использованный) источник чернил.

[0050] Электронный контроллер 230 принимает данные 236 от главной системы, например, компьютера, и может включать в себя память для временного хранения данных 236. Данные 236 могут отправляться на систему 200 выброса текучей среды по электронному, инфракрасному, оптическому или другому пути переноса информации. Данные 236 представляют, например, документ и/или файл, подлежащий печати. Таким образом, данные 236 образуют задание на печать для системы 200 выброса текучей среды и включают в себя по меньшей мере одну команду и/или параметр команды задания на печать.

[0051] В одном примере, электронный контроллер 230 обеспечивает управление агрегатом 204 печатающей головки, включающее в себя управление хронированием для выброса капель чернил из сопел 214. Таким образом, электронный контроллер 230 задает картину выбрасываемых капель чернил, которые образуют знаки, символы, и/или другие графические объекты или изображения на носителях 232 печати. Управление хронированием и, таким образом, картина выбрасываемых капель чернил, определяется командами и/или параметрами команд задания на печать. В одном примере, логическая и возбуждающая схема, образующая часть электронного контроллера 230, располагается на агрегате 204 печатающей головки. В другом примере, логическая и возбуждающая схема, образующая часть электронного контроллера 230, располагается вне агрегата 204 печатающей головки. В другом примере, логическая и возбуждающая схема, образующая часть электронного контроллера 230, располагается вне агрегата 204 печатающей головки. В одном примере, сегменты 33-1-33-n данных, пульсирующий тактовый сигнал 35, сигнал 72 возбуждения и сигнал 79 режима могут обеспечиваться для компонента 30 печати электронным контроллером 230, где электронный контроллер 230 может быть удаленным от компонента 30 печати.

[0052] На фиг. 8 показана блок-схема операций, демонстрирующая в целом способ 300 работы струйной матрицы, согласно одному примеру настоящего изобретения, например, струйной матрицы 40, изображенной на фиг. 3. На этапе 302, способ 300 включает в себя прием сегментов данных, причем каждый сегмент данных имеет головную часть, включающую в себя несколько битов данных конфигурации, хвостовую часть, включающую в себя несколько битов данных конфигурации, и серединную часть, проходящую между головной частью и хвостовой частью и включающую в себя несколько битов данных активации, например, сегмента 60 данных, показанного на фиг. 4, включающего в себя головную часть 62-1, хвостовую часть 62-2 и серединную часть 64.

[0053] На этапе 304, способ 300 включает в себя последовательную загрузку каждого сегмента данных в массив элементов памяти, включающий в себя первую часть элементов памяти, соответствующую первой группе функциональных элементов конфигурации, вторую часть элементов памяти, соответствующую второй группе функциональных элементов конфигурации, и третью часть элементов памяти, соответствующую массиву активаторов текучей среды, благодаря чему, после загрузки сегмента данных в массив элементов памяти, биты конфигурации головной части сохраняются в первой части элементов памяти, биты данных конфигурации хвостовой части элементов памяти сохраняются во второй части элементов памяти, и биты данных активатора серединной части сохраняются в третьей части элементов памяти, такая последовательная загрузка сегмента 60 данных в массив элементов памяти 50, где первая часть элементов 52-1 памяти соответствует первой группе 36-1 функциональных элементов конфигурации, вторая часть элементов 52-2 памяти соответствует второй группе 36-2 функциональных элементов конфигурации, и третья часть элементов 54 памяти соответствует массиву устройств активации 34 текучей среды.

[0054] Хотя здесь были проиллюстрированы и описаны конкретные примеры, для конкретных показанных и описанных примеров можно предложить различные альтернативные и/или эквивалентные реализации, не выходящие за рамки объема настоящего изобретения. Данная заявка призвана охватывать любые адаптации или вариации рассмотренных здесь конкретных примеров. Поэтому предполагается, что это изобретение ограничивается только формулой изобретения и ее эквивалентами.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПЕЧАТАЮЩИЙ КОМПОНЕНТ С МАТРИЦЕЙ ПАМЯТИ, ИСПОЛЬЗУЮЩИЙ ПУЛЬСИРУЮЩИЙ ТАКТОВЫЙ СИГНАЛ | 2019 |

|

RU2780707C1 |

| КРИСТАЛЛ ДЛЯ ПЕЧАТАЮЩЕЙ ГОЛОВКИ | 2019 |

|

RU2778376C1 |

| ПЕЧАТАЮЩИЙ КОМПОНЕНТ СО СХЕМОЙ ПАМЯТИ | 2019 |

|

RU2778211C1 |

| ИНТЕГРАЛЬНЫЕ СХЕМЫ, ВКЛЮЧАЮЩИЕ В СЕБЯ ЗАПОМИНАЮЩИЕ ЯЧЕЙКИ | 2019 |

|

RU2779793C1 |

| УСТРОЙСТВА ВЫБРОСА ТЕКУЧЕЙ СРЕДЫ, ВКЛЮЧАЮЩИЕ В СЕБЯ ПЕРВУЮ ПАМЯТЬ И ВТОРУЮ ПАМЯТЬ | 2019 |

|

RU2779068C1 |

| ОСУЩЕСТВЛЕНИЕ ДОСТУПА К РЕГИСТРАМ УСТРОЙСТВ ВЫБРОСА ТЕКУЧЕЙ СРЕДЫ | 2019 |

|

RU2776431C1 |

| СЕЛЕКТОРЫ ДЛЯ ФОРСУНОК И ЭЛЕМЕНТОВ ПАМЯТИ | 2017 |

|

RU2747446C1 |

| ПЕЧАТАЮЩАЯ ГОЛОВКА, ИСПОЛЬЗУЮЩАЯ ПАКЕТЫ ДАННЫХ, ВКЛЮЧАЮЩИЕ В СЕБЯ АДРЕСНЫЕ ДАННЫЕ | 2018 |

|

RU2692769C1 |

| ПЕЧАТАЮЩАЯ ГОЛОВКА, ИСПОЛЬЗУЮЩАЯ ПАКЕТЫ ДАННЫХ, ВКЛЮЧАЮЩИЕ В СЕБЯ АДРЕСНЫЕ ДАННЫЕ | 2015 |

|

RU2672938C1 |

| АССОЦИАТИВНАЯ ПАМЯТЬ | 2007 |

|

RU2452047C2 |

Интегральная схема для струйной матрицы, включающая в себя шину адреса для передачи набора адресов, первую группу функциональных элементов конфигурации матрицы, включающую в себя первый адресный формирователь для направления первой части адреса из набора адресов в шину адреса, вторую группу функциональных элементов конфигурации матрицы, включающую в себя второй адресный формирователь для направления второй части адреса из набора адресов в шину адреса, и массив устройств активации текучей среды, адресуемых набором адресов, передаваемых по шине адреса. 2 н. и 7 з.п. ф-лы, 8 ил.

1. Интегральная схема для струйной матрицы, содержащая:

шину адреса для передачи набора адресов;

первую группу функциональных элементов конфигурации матрицы, включающую в себя первый адресный формирователь для направления первой части адреса из набора адресов в шину адреса;

вторую группу функциональных элементов конфигурации матрицы, включающую в себя второй адресный формирователь для направления второй части адреса из набора адресов в шину адреса;

массив устройств активации текучей среды, адресуемых набором адресов, передаваемых по шине адреса;

массив элементов памяти, включающий в себя:

первую часть элементов памяти, соответствующую первой группе функциональных элементов конфигурации матрицы;

вторую часть элементов памяти, соответствующую второй группе функциональных элементов конфигурации матрицы; и

третью часть элементов памяти, соответствующую массиву устройств активации текучей среды;

причем в массив элементов памяти последовательно загружаются сегменты данных, благодаря чему, по завершении загрузки сегмента данных, первая часть элементов памяти сохраняет первый набор битов адреса, представляющий первую часть адреса из набора адресов, и вторая часть элементов памяти сохраняет второй набор битов адреса, представляющий оставшуюся часть адреса из набора адресов.

2. Интегральная схема по п. 1, в которой первая часть и вторая часть совместно представляют адрес из набора адресов.

3. Интегральная схема по п. 1 или 2, в которой массив устройств активации текучей среды скомпонован как столбец устройств активации текучей среды, проходящий в продольном направлении между первой и второй группами функциональных элементов конфигурации матрицы.

4. Интегральная схема по п. 3, в которой массив элементов памяти содержит цепочку элементов памяти, чтобы функционировать как последовательно-параллельный преобразователь данных, причем первая часть элементов памяти расположена рядом с первой группой функциональных элементов конфигурации матрицы, вторая часть элементов памяти расположена рядом со второй группой функциональных элементов конфигурации матрицы, и третья часть элементов памяти проходит между первой и второй частями элементов памяти и расположена рядом с массивом устройств активации текучей среды.

5. Интегральная схема по любому из пп. 1-4, в которой в дополнение к первому и второму адресным формирователям функциональные элементы конфигурации матрицы содержат функциональный элемент управления импульсами возбуждения и функциональный элемент конфигурации датчиков.

6. Способ работы струйной матрицы, содержащий этапы, на которых:

принимают сегменты данных, причем каждый сегмент данных включает в себя:

головную часть, включающую в себя несколько битов данных конфигурации;

хвостовую часть, включающую в себя несколько битов данных конфигурации; и

серединную часть, проходящую между головной частью и хвостовой частью и включающую в себя несколько битов данных активации;

последовательно загружают каждый сегмент данных в массив элементов памяти, включающий в себя первую часть элементов памяти, соответствующую первой группе функциональных элементов конфигурации, вторую часть элементов памяти, соответствующую второй группе функциональных элементов конфигурации, и третью часть элементов памяти, соответствующую массиву активаторов текучей среды, благодаря чему, после загрузки сегмента данных в массив элементов памяти, биты конфигурации головной части сохраняются в первой части элементов памяти, биты данных конфигурации хвостовой части сохраняются во второй части элементов памяти, и биты данных активатора серединной части сохраняются в третьей части элементов памяти.

7. Способ по п. 6, в котором головная часть включает в себя первый набор битов адреса, хвостовая часть включает в себя второй набор битов адреса, массив активаторов текучей среды адресуется набором адресов, при этом упомянутый способ включает в себя этапы, на которых:

передают набор адресов массиву активаторов текучей среды через шину адреса;

направляют первую часть адреса из набора адресов в шину адреса на основании первого набора битов адреса с помощью первого адресного формирователя первой группы функциональных элементов конфигурации; и

направляют оставшуюся часть адреса из набора адресов в шину адреса на основании второго набора битов адреса с помощью второго адресного формирователя второй группы функциональных элементов конфигурации.

8. Способ по п. 6 или 7, содержащий этап, на котором:

размещают массив элементов памяти как последовательность элементов памяти, реализованную в виде последовательно-параллельного преобразователя данных, включая расположение последовательности элементов памяти в продольном направлении, причем третья часть элементов памяти проходит между первой и второй частями элементов памяти.

9. Способ по любому из пп. 6-8, включающий в себя этап, на котором:

размещают первую группу функциональных элементов конфигурации рядом с первой частью элементов памяти, вторую группу функциональных элементов конфигурации рядом со второй частью элементов памяти, и размещают массив активаторов текучей среды в столбце, проходящем в продольном направлении между первой и второй группами функциональных элементов конфигурации и рядом с третьей частью элементов памяти.

| EP 1212197 A1, 12.06.2002 | |||

| WO 2019017951 A1, 24.01.2019 | |||

| WO 2019009902 A1, 10.01.2019 | |||

| US 2018147839 A1, 31.05.2018. |

Авторы

Даты

2022-09-22—Публикация

2019-02-06—Подача