Предпосылки изобретения

[0001] Некоторые печатающие компоненты могут включать в себя массив сопел и/или насосов, каждое(ый) из которых включает в себя камеру для текучей среды и активатор текучей среды, причем активатор текучей среды может приводиться в действие, вызывая перемещение текучей среды в камере. Некоторые примерные матрицы для текучей среды могут быть печатающими головками, причем текучая среда может соответствовать чернилам или печатающим агентам. Печатающие компоненты включают в себя печатающие головки для систем 2D- и 3D-печати и/или других высокоточных систем распределения текучей среды.

Краткое описание чертежей

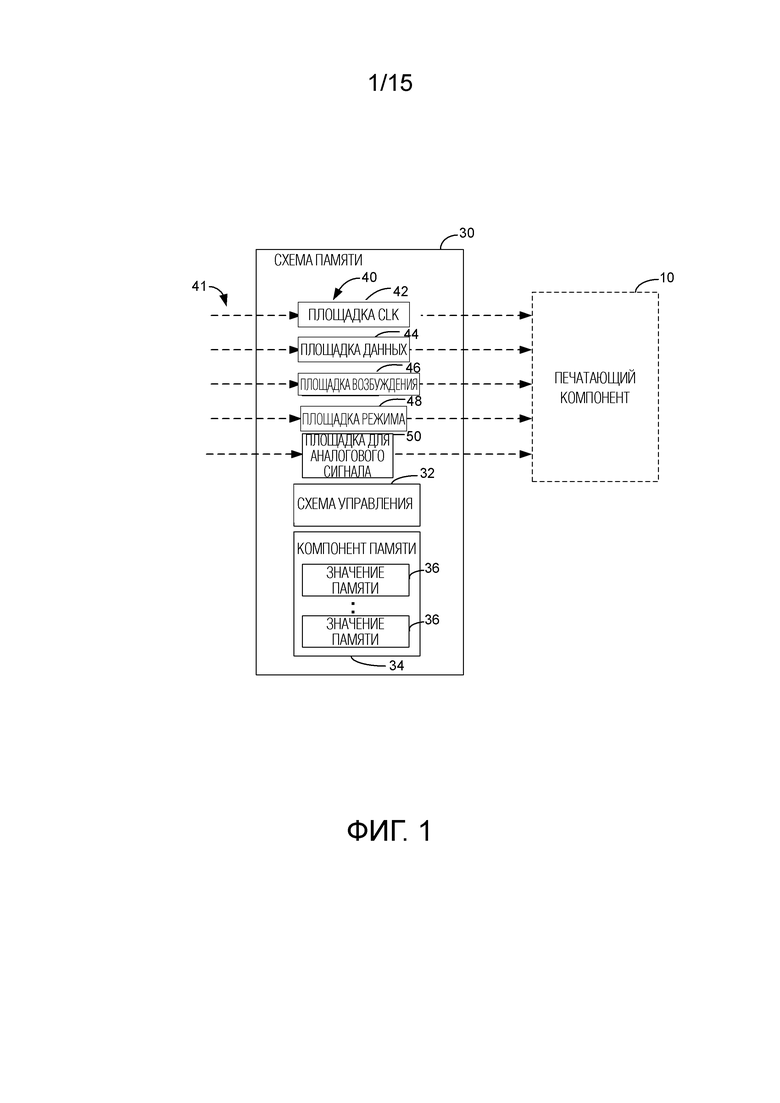

[0002] Фиг. 1 является блочной и принципиальной схемой, иллюстрирующей схему памяти для печатающего компонента согласно одному примеру.

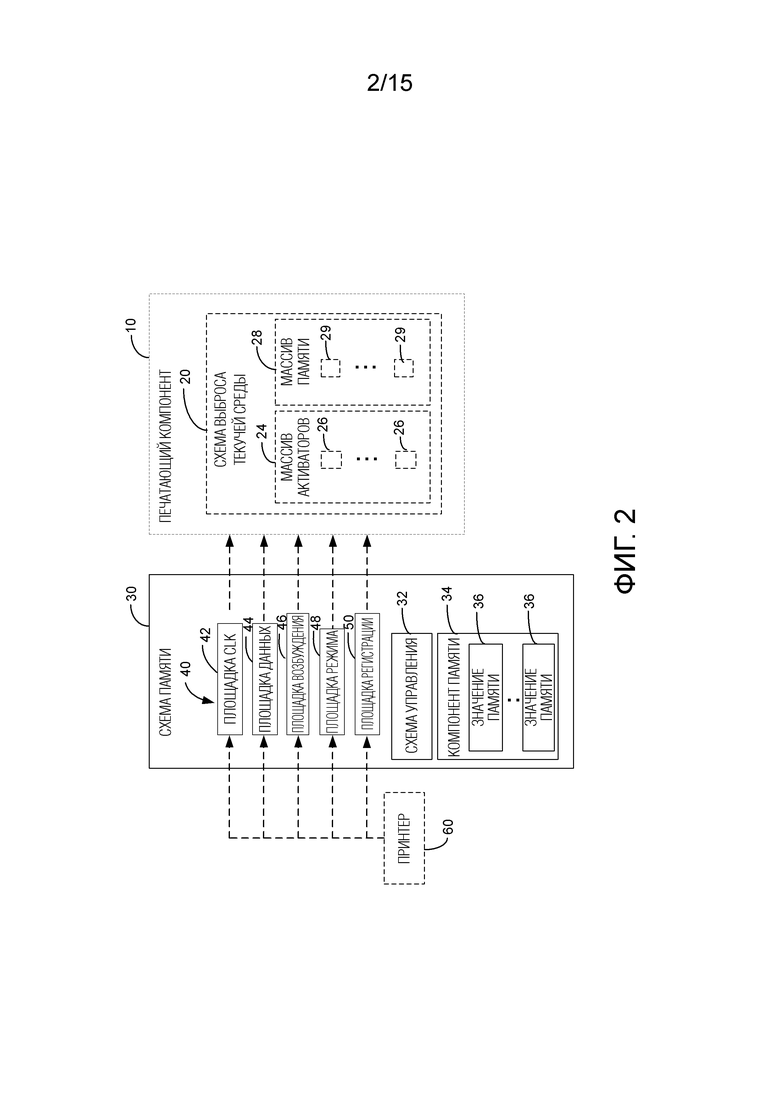

[0003] Фиг. 2 является блочной и принципиальной схемой, иллюстрирующей схему памяти для печатающего компонента согласно одному примеру.

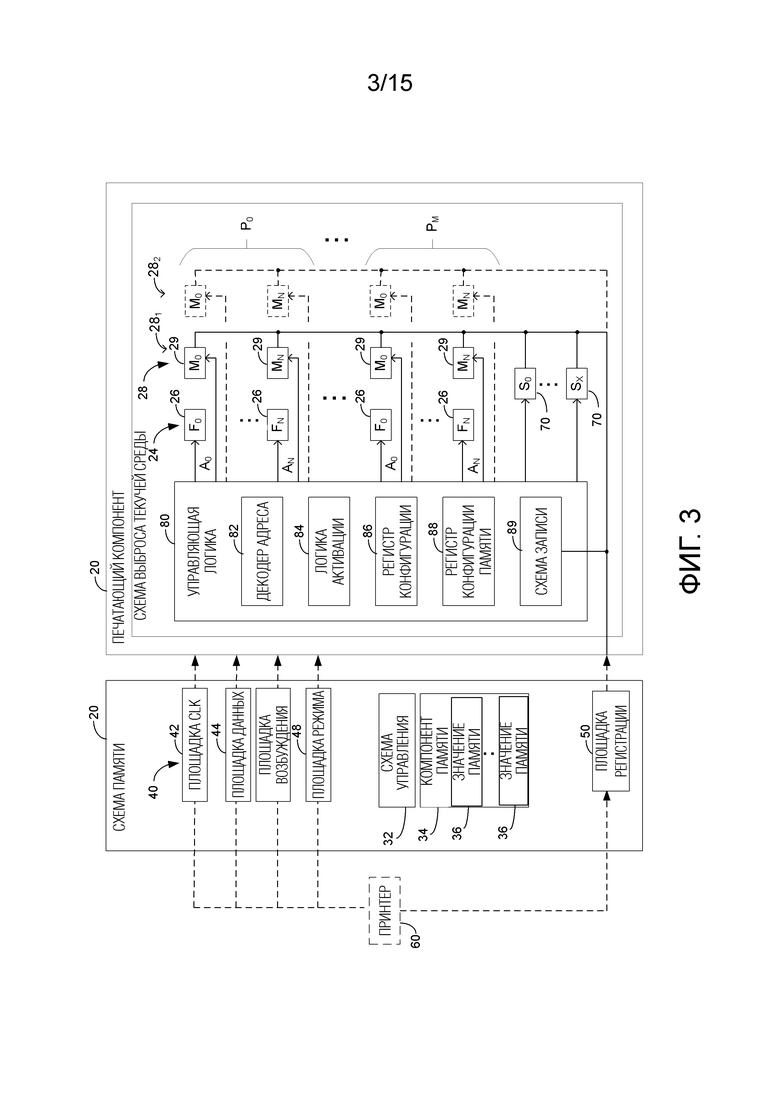

[0004] Фиг. 3 является блочной и принципиальной схемой, иллюстрирующей схему памяти для печатающего компонента согласно одному примеру.

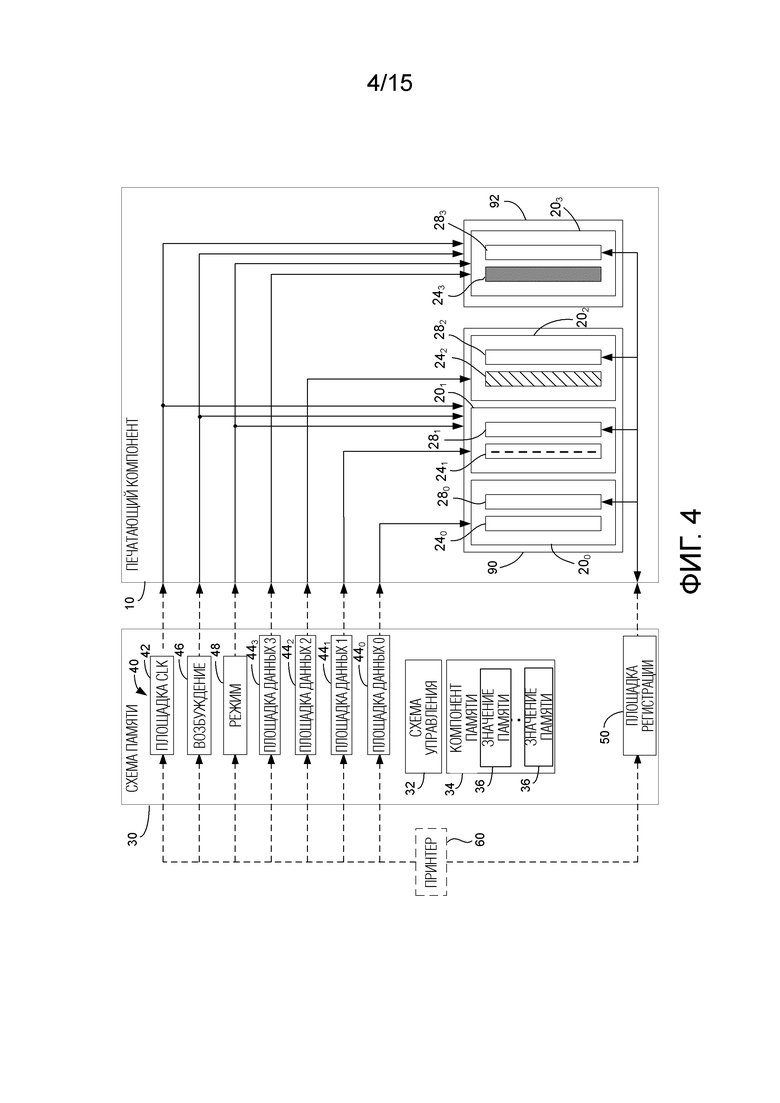

[0005] Фиг. 4 является блочной и принципиальной схемой, иллюстрирующей схему памяти для печатающего компонента согласно одному примеру.

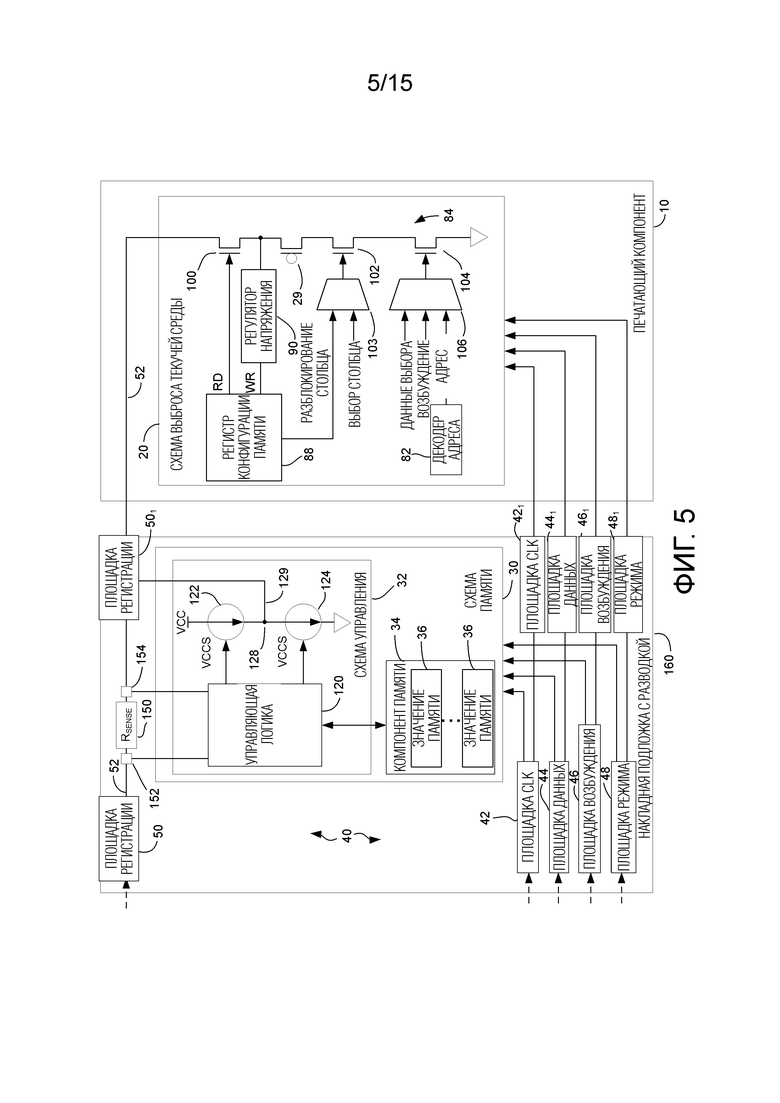

[0006] Фиг. 5 является блочной и принципиальной схемой, иллюстрирующей схему памяти для печатающего компонента согласно одному примеру.

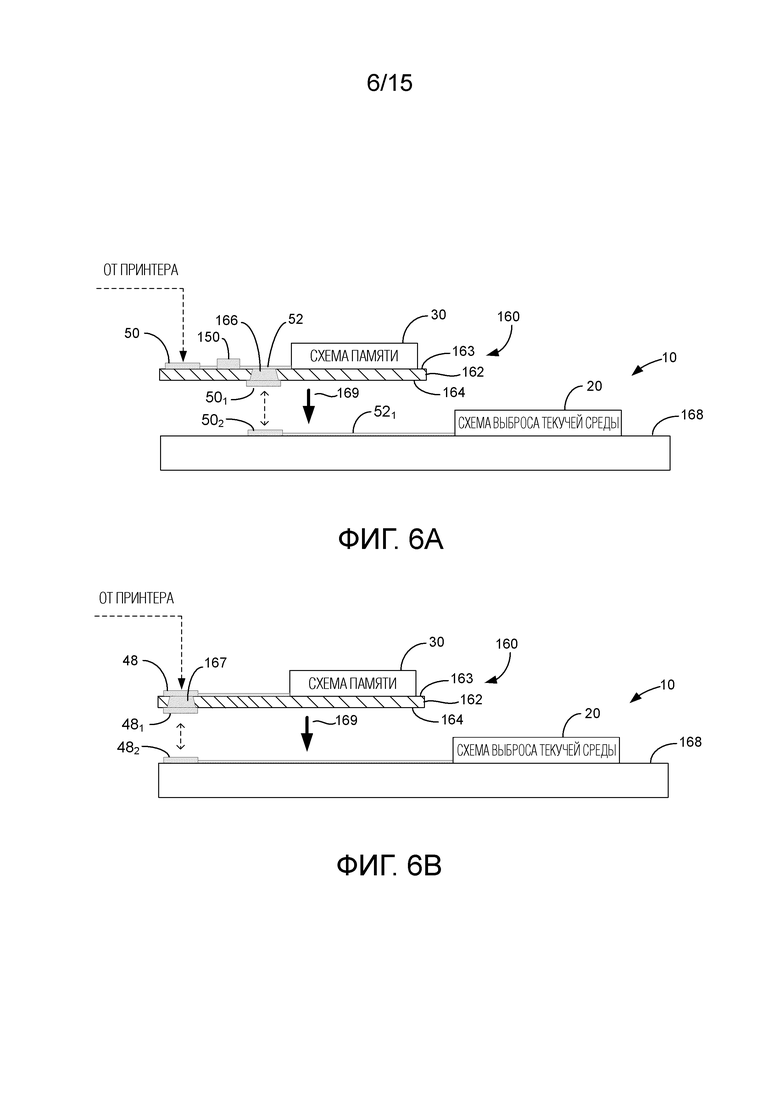

[0007] Фиг. 6A и 6B являются блочными и принципиальными схемами, иллюстрирующими гибкую подложку с разводкой для соединения схемы памяти с печатающим компонентом согласно одному из примеров.

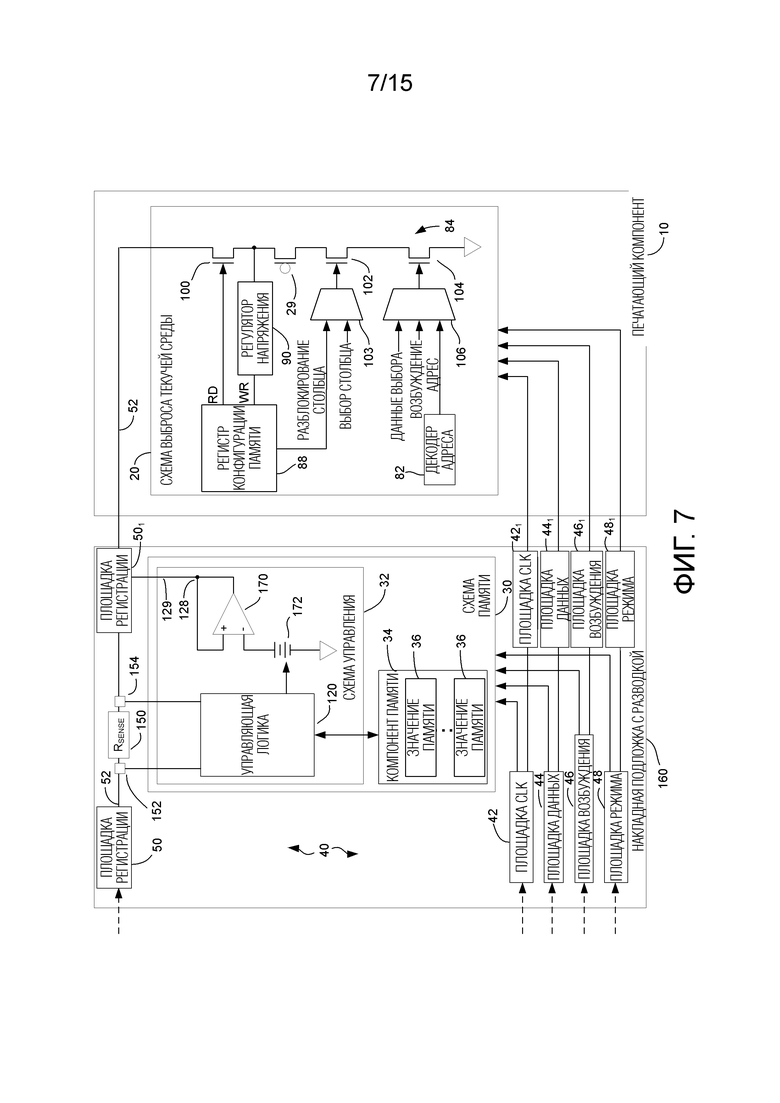

[0008] Фиг. 7 является блочной и принципиальной схемой, иллюстрирующей схему памяти для печатающего компонента согласно одному примеру.

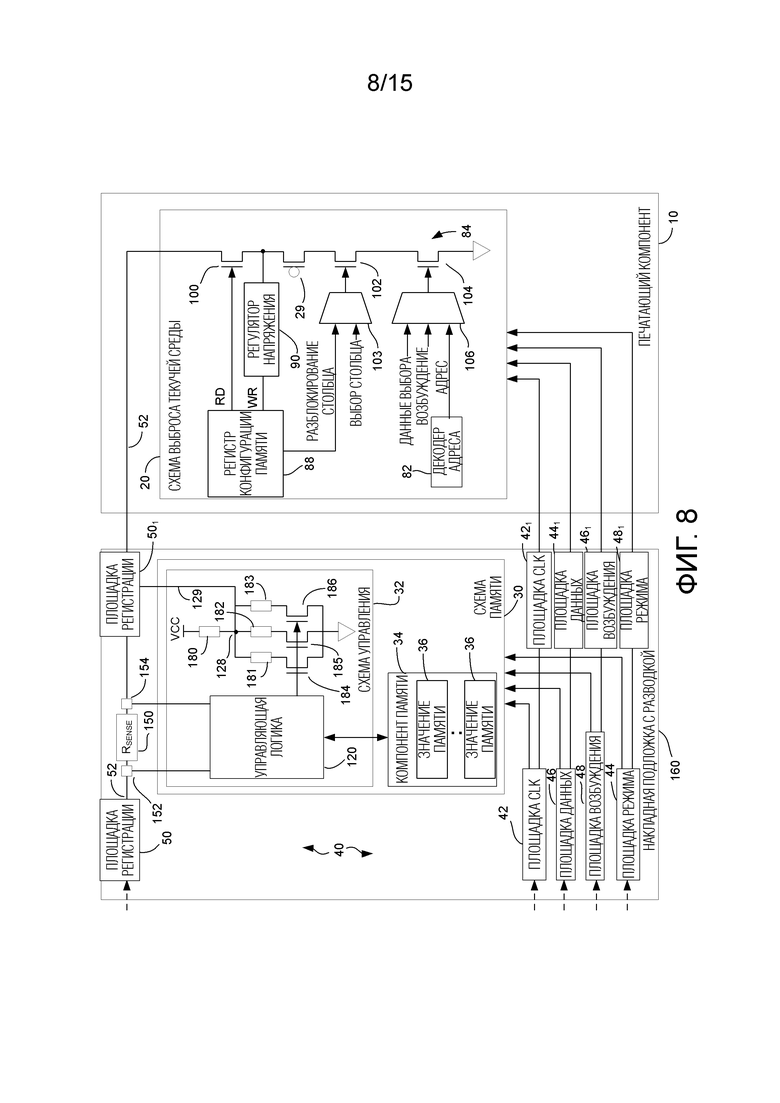

[0009] Фиг. 8 является блочной и принципиальной схемой, иллюстрирующей схему памяти для печатающего компонента согласно одному примеру.

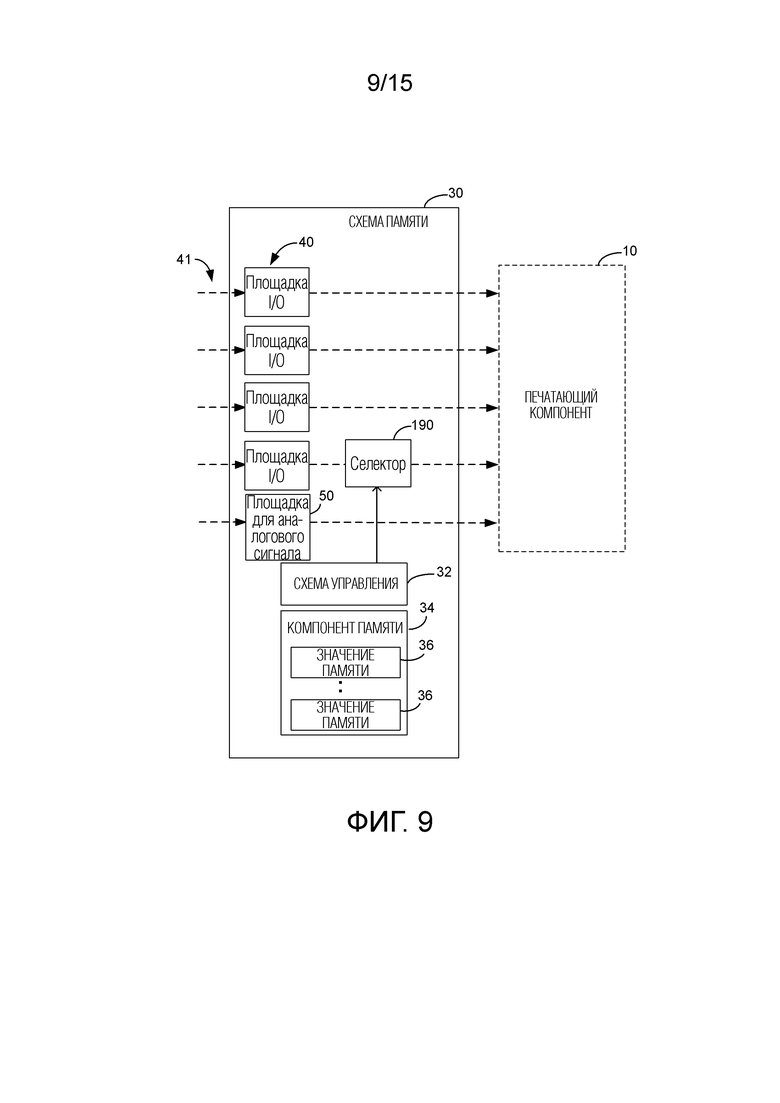

[0010] Фиг. 9 является блочной и принципиальной схемой, иллюстрирующей схему памяти для печатающего компонента согласно одному примеру.

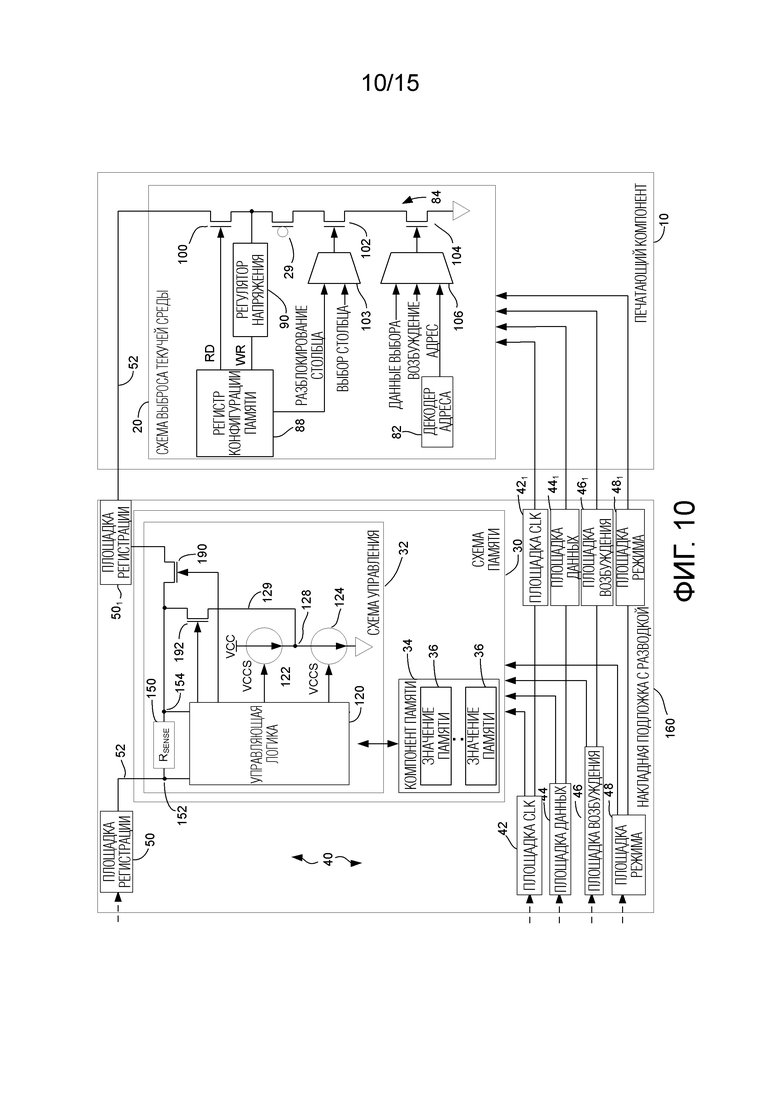

[0011] Фиг. 10 является блочной и принципиальной схемой, иллюстрирующей схему памяти для печатающего компонента согласно одному примеру.

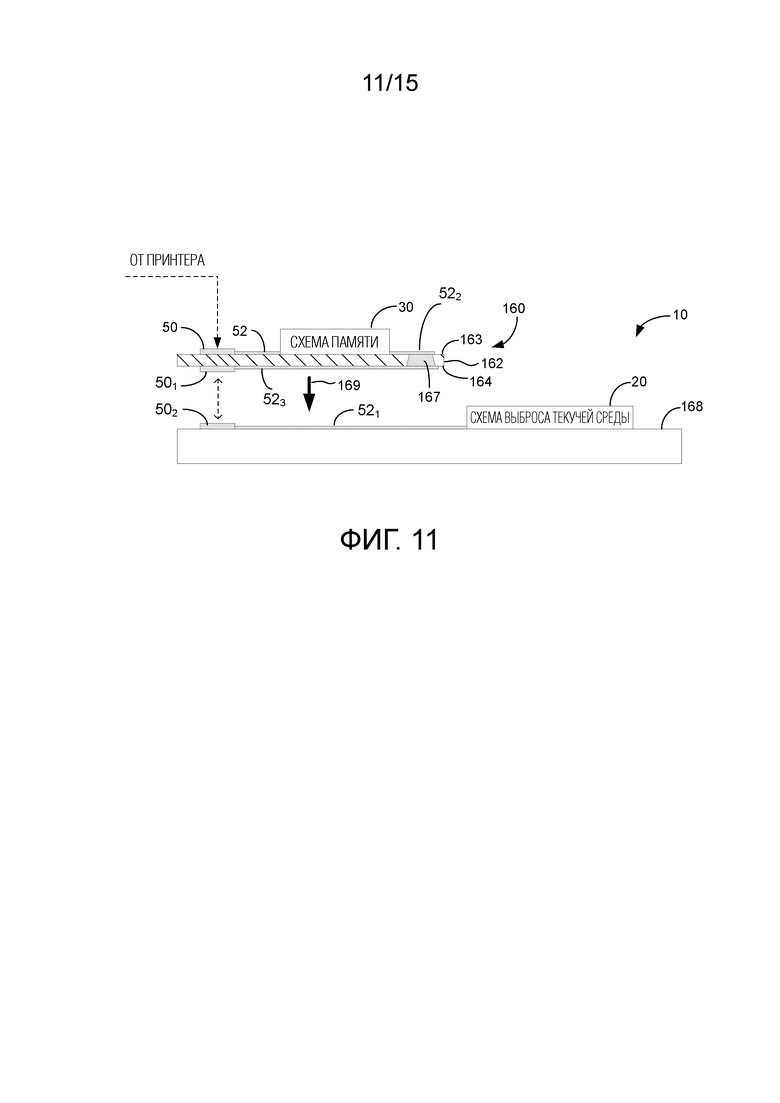

[0012] Фиг. 11 является блочной и принципиальной схемой, иллюстрирующей гибкую подложку с проводкой для соединения схемы памяти с печатающим компонентом согласно одному примеру.

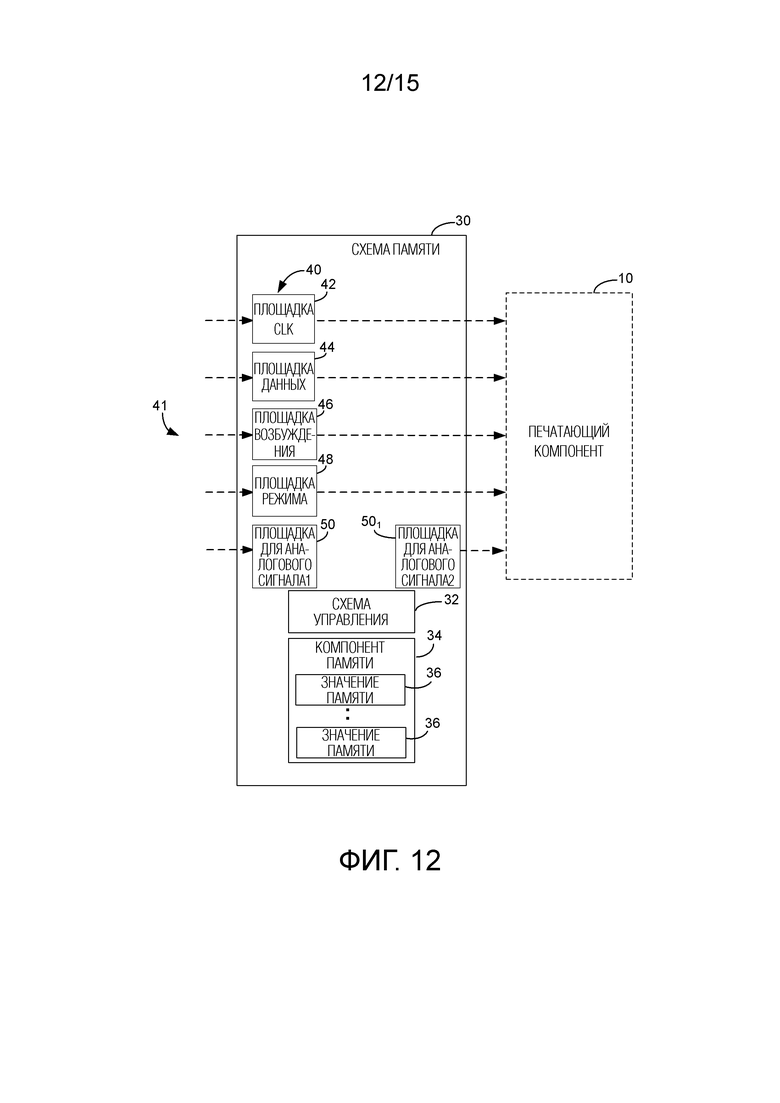

[0013] Фиг. 12 является блочной и принципиальной схемой, иллюстрирующей схему памяти для печатающего компонента согласно одному примеру.

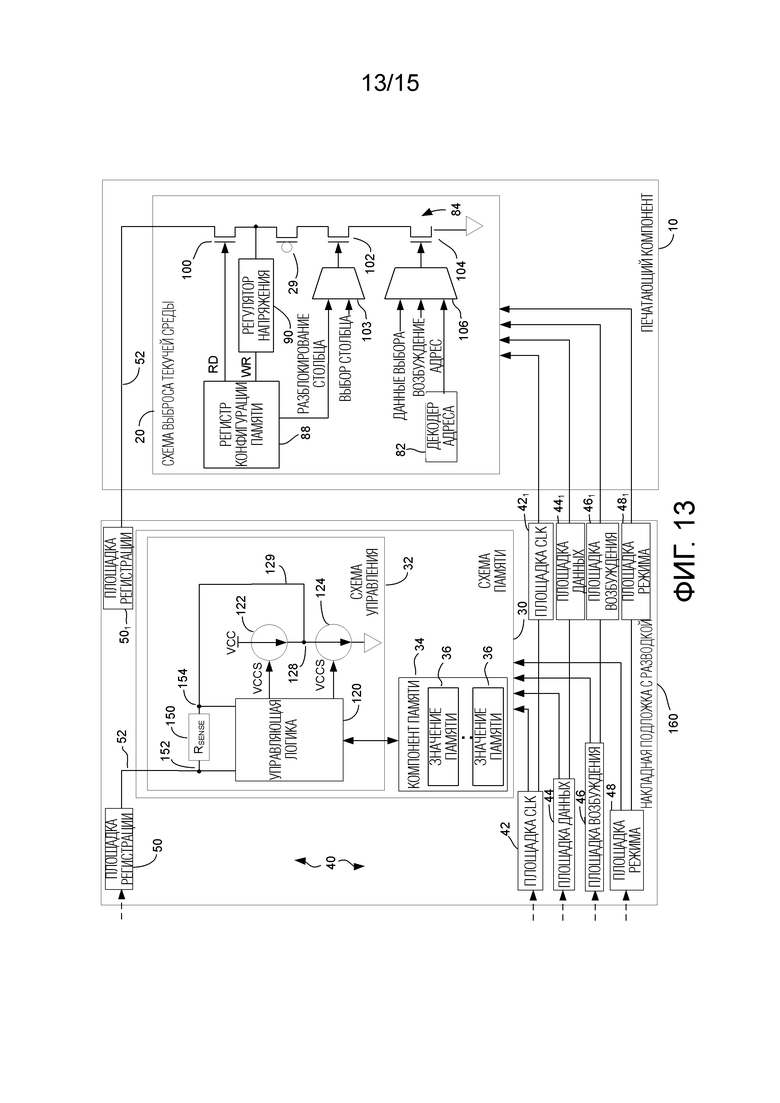

[0014] Фиг. 13 является блочной и принципиальной схемой, иллюстрирующей схему памяти для печатающего компонента согласно одному примеру.

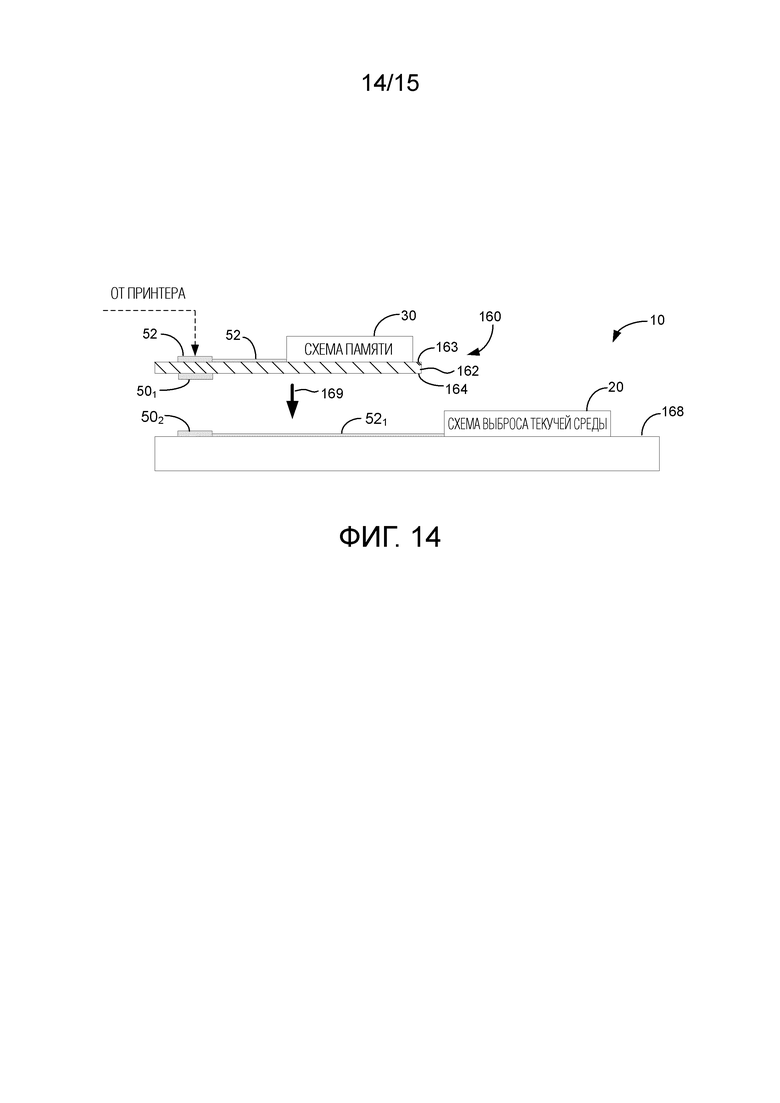

[0015] Фиг. 14 является блочной и принципиальной схемой, иллюстрирующей гибкую подложку с разводкой для соединения схемы памяти с печатающим компонентом согласно одному примеру.

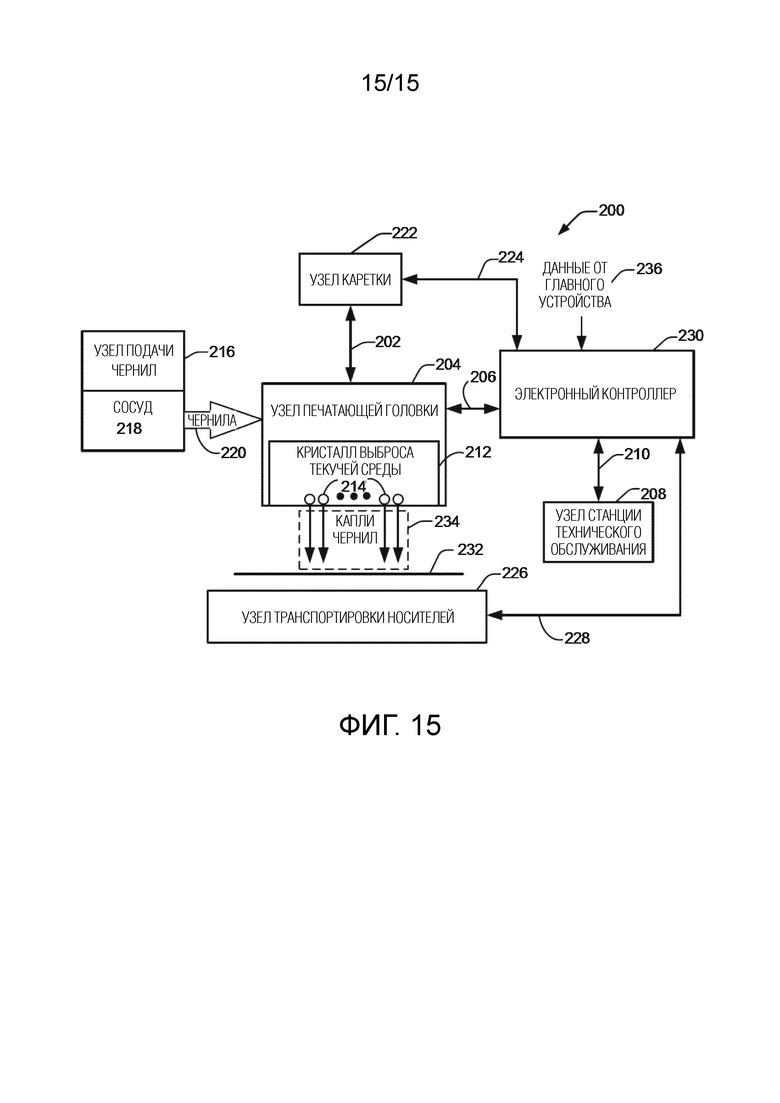

[0016] Фиг. 15 является блочной и принципиальной схемой, иллюстрирующей систему выброса текучей среды согласно одному примеру.

[0017] Повсюду на чертежах идентичные ссылочные позиции обозначают подобные, но не обязательно идентичные, элементы. Фигуры не обязательно выполнены в масштабе, и размер некоторых частей может быть преувеличен, чтобы более ясно проиллюстрировать показанный пример. Кроме того, чертежи предоставляют примеры и/или реализации, согласующиеся с описанием; однако, описание не ограничивается примерами и/или реализациями, предоставленными на чертежах.

Подробное описание изобретения

[0018] В последующем подробном описании выполнена ссылка на сопроводительные чертежи, которые формируют его часть и на которых показаны в качестве иллюстрации конкретные примеры, в которых раскрытие может быть реализовано на практике. Следует понимать, что без выхода за рамки настоящего раскрытия могут быть использованы другие примеры и могут быть сделаны структурные или логические изменения. Поэтому последующее подробное описание не следует воспринимать в ограничивающем смысле, и объем настоящего раскрытия характеризуется прилагаемой формулой изобретения. Следует понимать, что признаки описанных здесь различных примеров могут быть объединены, частично или полностью, друг с другом, пока явно не указано иное.

[0019] Примерные матрицы для текучей среды могут включать в себя активаторы текучей среды (например, для выброса и рециркуляции текучей среды), причем активаторы текучей среды могут включать в себя терморезисторные активаторы, активаторы на основе пьезоэлектрической мембраны, активаторы с электростатической мембраной, мембранные активаторы механического/ударного действия, активаторы с магнитострикционным приводом или другие подходящие устройства, которые могут вызывать перемещение текучей среды в ответ на электрическую активацию. Описываемые здесь матрицы для текучей среды могут включать в себя множество активаторов текучей среды, которые могут называться массивом активаторов текучей среды. Событие активации может называться единичной или одновременной активацией активаторов текучей среды матрицы для текучей среды, вызывающей перемещение текучей среды. Примером события активации является событие возбуждения текучей среды, в результате которого текучая среда выпускается струей через сопло.

[0020] В примерных матрицах для текучей среды массив активаторов текучей среды может быть размещен в наборах активаторов текучей среды, причем каждый такой набор активаторов текучей среды может называться "базовым модулем (примитивом)" или "примитивом возбуждения". Количество активаторов текучей среды в примитиве может называться размером примитива. В некоторых примерах набор активаторов текучей среды каждого примитива является адресуемым с помощью такого же набора адресов активации, при этом каждый активатор текучей среды примитива соответствует различному адресу активации из набора адресов активации, при этом адреса сообщаются по адресной шине. В некоторых примерах, во время события активации, в каждом примитиве активатор текучей среды, соответствующий адресу на адресной шине, будет активироваться (например, возбуждаться) в ответ на сигнал возбуждения (также называемый импульсом возбуждения) на основе состояния данных выбора (например, состояния бита выбора), соответствующих примитиву (иногда также называемых данными сопла или данными примитива).

[0021] В некоторых случаях электрические функциональные ограничения и функциональные ограничения по текучей среде матрицы для текучей среды могут ограничивать количество активаторов текучей среды, которые могут быть активированы одновременно во время события активации. Примитивы обеспечивают выбор поднаборов активаторов текучей среды, которые могут быть одновременно активированы для данного события активации, чтобы соответствовать таким функциональным ограничениям.

[0022] В качестве примера, если матрица для текучей среды включает в себя четыре примитива, при этом каждый примитив имеет восемь активаторов текучей среды (при этом каждый активатор текучей среды соответствует различному адресу из, например, набора адресов от 0 до 7), и когда электрические ограничения и ограничения по текучей среде ограничивают активацию одним активатором текучей среды на каждый примитив, всего четыре активатора текучей среды (один от каждого примитива) могут одновременно активироваться для данного события активации. Например, для первого события активации может быть активирован соответствующий активатор текучей среды каждого примитива, соответствующий адресу "0". Для второго события активации может быть активирован соответствующий активатор текучей среды каждого примитива, соответствующий адресу "5". Как будет понятно, такой пример предоставляется лишь для иллюстративных целей, при этом рассматриваемые здесь матрицы для текучей среды могут содержать больше или меньше активаторов текучей среды на каждый примитив и больше или меньше примитивов на каждую матрицу.

[0023] Примерные матрицы для текучей среды могут включать в себя камеры для текучей среды, отверстия (дюзы) и/или другие элементы, которые могут быть ограничены поверхностями, изготовленными на подложке матрицы для текучей среды путем травления, микрообработки (например, фотолитографии), процессов механической микрообработки или других подходящих процессов или их сочетаний. Некоторые примерные подложки могут включать в себя кремниевые подложки, стеклянные подложки, подложки на основе арсенида галлия и/или другие такие подходящие типы подложек для изготовленных методом микрообработки устройств и структур. Как использовано здесь, камеры для текучей среды могут включать в себя эжекционные камеры в сообщении по текучей среде с сопловыми отверстиями, из которых может быть выброшена текучая среда, и каналы для текучей среды, по которым может транспортироваться текучая среда. В некоторых примерах каналы для текучей среды могут быть микроканалами для текучей среды, причем, как использовано здесь, микроканал для текучей среды может соответствовать каналу достаточно небольшого размера (например, нанометрового масштаба, микрометрового масштаба, миллиметрового масштаба и т.д.), обеспечивая транспортировку небольших объемов текучей среды (например, пиколитрового масштаба, нанолитрового масштаба, микролитрового масштаба, миллилитрового масштаба и т.д.).

[0024] В некоторых примерах активатор текучей среды может быть выполнен как часть сопла, когда, в дополнение к активатору текучей среды, сопло включает в себя эжекционную камеру в сообщении по текучей среде с сопловым отверстием. Активатор текучей среды позиционируется относительно камеры для текучей среды так, что активация активатора текучей среды вызывает перемещение текучей среды в камере для текучей среды, которое может вызывать выброс капли текучей среды из камеры для текучей среды через сопловое отверстие. Соответственно, активатор текучей среды, выполненный как часть сопла, может иногда называться эжектором текучей среды или активатором выброса.

[0025] В некоторых примерах активатор текучей среды может быть выполнен как часть насоса, когда, в дополнение к активатору текучей среды, насос включает в себя канал для текучей среды. Активатор текучей среды расположен относительно канала для текучей среды так, что активация активатора текучей среды создает перемещение текучей среды в канале для текучей среды (например, микроканале для текучей среды), перемещая текучую среду в матрице для текучей среды, такое как, например, между источником текучей среды и соплом. Пример перемещения/нагнетания текучей среды в матрице может иногда называться микрорециркуляцией. Активатор текучей среды, выполненный с возможностью перемещать текучую среду в канале для текучей среды, может иногда называться невыбрасывающим или активатором с микрорециркуляцией.

[0026] В одном примерном сопле активатор текучей среды может содержать термический активатор, когда активация активатора текучей среды (иногда называемая "возбуждением") нагревает текучую среду, формируя в камере для текучей среды газообразный приводящий в действие пузырек, который может вызывать выброс капли текучей среды из соплового отверстия. Как описано выше, активаторы текучей среды могут быть размещены в массивах (таких как столбцы), где активаторы могут быть реализованы как струйные эжекторы и/или насосы, с выборочной работой струйных эжекторов, вызывающей выброс капли текучей среды, и выборочной работой насосов, вызывающей перемещение текучей среды в матрице для текучей среды. В некоторых примерах массив активаторов текучей среды может быть размещен в примитивах.

[0027] Некоторые матрицы для текучей среды принимают данные в виде пакетов данных, иногда называемых группами импульсов возбуждения или пакетами данных групп импульсов возбуждения. В некоторых примерах такие пакеты данных могут включать в себя данные конфигурации и данные выбора. В некоторых примерах данные конфигурации включают в себя данные для конфигурирования функций на матрице (кристалле), такие как биты адреса, представляющие адрес подлежащих активации активаторов текучей среды, в качестве части операции возбуждения, данные импульса возбуждения для конфигурирования характеристик импульса возбуждения и термические данные для конфигурирования термических операций, таких как нагрев и восприятие (регистрация). В некоторых примерах пакеты данных конфигурируются с помощью головных и хвостовых участков, включающих в себя данные конфигурации, и основного участка, включающего в себя данные выбора (примитива). В примерных матрицах для текучей среды в ответ на прием пакета данных схема управления на матрице применяет декодеры/драйверы адреса, предоставляя адрес по адресной линии, логику активации, активируя выбранные активаторы текучей среды (например, на основе адреса, данных выбора и импульса возбуждения), и логику конфигурации, конфигурируя операции функций на матрице, такие как, например, конфигурация импульса возбуждения, регистрация трещины, и термические операции на основе данных конфигурации и сигнала режима.

[0028] В дополнение к активаторам текучей среды, некоторые примерные матрицы для текучей среды включают в себя память на кристалле (например, энергонезависимую память (NVM)) для обмена информацией (например, битами памяти) с внешними устройствами, такими как принтер, чтобы помогать при операции управления устройствами с текучей средой, в том числе операции активаторов текучей среды и других устройств (например, нагревателей, датчиков трещин) для регулирования выброса текучей среды. В примерах такая информация может включать в себя, например, тепловой режим, смещения, информацию о регионе, карту цветов, уровни текучей среды и количество сопел.

[0029] Запоминающие устройства (памяти) типично включают в себя служебные схемы (например, режимы адреса, декодирования, считывания и записи и т.д.), которые являются дорогостоящими для реализации и расходуют относительно большие количества площади кремния на кристалле. Однако, поскольку подобная схема применяется при выборе, активации и передаче данных массиву активаторов текучей среды, некоторые примерные матрицы для текучей среды имеют многоцелевые участки схемы управления для выбора и передачи данных активаторам текучей среды (в том числе, например, участки высокоскоростного канала передачи данных) для выбора также элементов памяти из массива памяти.

[0030] Для дополнительной экономии пространства и уменьшения сложности, связанной с многошинными архитектурами, некоторые примерные матрицы для текучей среды используют однополосную аналоговую шину, которая присоединяется с возможностью обмена информацией параллельно с элементами памяти, чтобы считывать и записывать информацию в/из элементов памяти по совместно используемой однополосной аналоговой шине (которая также иногда называется шиной регистрации). В некоторых примерах однополосная шина способна считывать из/записывать в элементы памяти индивидуально или в различных комбинациях элементов памяти параллельно. Дополнительно, некоторые примерные матрицы для текучей среды включают в себя устройства, такие как датчики трещин, температурные датчики и нагревательные элементы, которые также могут быть соединены с однополосной аналоговой шиной для регистрации и управления.

[0031] В примерных матрицах для текучей среды, имеющих запоминающие устройства на кристалле, в дополнение к сообщению данных выбора для выбора активаторов текучей среды для активации в качестве части операции активации текучей среды пакеты данных могут сообщать данные выбора для выбора элементов памяти, к которым должен быть осуществлен доступ, в качестве части операции доступа к памяти (например, операции считывания/записи). Чтобы отличать различные режимы работы, такие как режим активации текучей среды и режим доступа к памяти, примерные матрицы для текучей среды могут применять различные рабочие протоколы для различных режимов работы. Например, матрица для текучей среды может применять одну последовательность протокола рабочих сигналов, такую как данные (например, пакеты данных), принимаемые через (контактные) площадки данных (DATA), тактовый сигнал, принимаемый через (контактную) площадку тактового сигнала (CLK), сигнал режима, принимаемый через (контактную) площадку режима (MODE), и сигнал возбуждения, принимаемый через (контактную) площадку возбуждения (FIRE), идентифицирующую операцию активатора текучей среды, и другую последовательность таких сигналов, идентифицирующую операции доступа к памяти (например, считывание и запись).

[0032] В примерных матрицах для текучей среды элементы памяти на кристалле могут быть однократно программируемыми (OTP) элементами. Во время изготовления информация может быть записана в элементы памяти в конце производственного процесса, в том числе после того, как матрица для текучей среды может быть размещена как часть печатающей головки или пера. Если обнаружено, что память повреждена (например, имеет один или более сбойных битов, которые не будут запрограммированы правильно), матрица для текучей среды может не функционировать правильно, так что матрица для текучей среды, печатающая головка и перо также являются поврежденными. Дополнительно, даже если служебная схема памяти может быть совместно использована со схемой выбора и активации активатора текучей среды, включение элементов памяти на кристалле потребляет площадь кремния и увеличивает размеры матрицы для текучей среды.

[0033] Настоящее раскрытие, как будет описано здесь более подробно, предоставляет печатающий компонент, такой как печатающая головка или печатающее перо, например, включающее в себя матрицу для текучей среды, имеющую массив активаторов текучей среды. Матрица для текучей среды соединяется с серией контактов (выводов) ввода/вывода (I/O), по которым сообщаются рабочие сигналы для управления работой матрицы для текучей среды, включающей в себя операции выброса активаторов текучей среды, при этом выводы (площадки) I/O включают в себя вывод для регистрации аналогового сигнала. Печатающий компонент включает в себя кристалл памяти, отдельный от матрицы для текучей среды, соединенный с выводами I/O, при этом кристалл памяти предназначен хранить значения памяти, связанные с печатающим компонентом, такие как, например, данные изготовления, тепловой режим, смещения, информацию о регионе, цветовую карту, количество сопел и тип текучей среды. Согласно одному примеру, в ответ на наблюдение рабочих сигналов на выводах I/O, представляющих последовательность доступа к памяти для сохраненных значений памяти, кристалл памяти подает аналоговый сигнал на вывод регистрации на основе сохраненных значений памяти, соответствующих последовательности доступа к памяти.

[0034] Как будет описано здесь более подробно, в одном примере кристалл памяти заменяет или замещает поврежденный массив памяти на матрице для текучей среды, тем самым предоставляя возможность матрице для текучей среды и печатающему компоненту, использующему эту матрицу для текучей среды, такому как, например, печатающее перо, оставаться рабочим. В другом примере кристалл памяти может быть использован вместо массива памяти на матрице для текучей среды, тем самым предоставляя возможность матрице для текучей среды и печатающей головке, использующей матрицу для текучей среды, выполняться меньшими. В другом примере матрица для текучей среды может быть использована для дополнения массива памяти на матрице для текучей среды (например, для расширения емкости памяти).

[0035] Фиг. 1 является блочной и принципиальной схемой, в целом иллюстрирующей схему 30 памяти согласно одному примеру настоящего раскрытия для печатающего компонента, такого как печатающий компонент 10. Схема 30 памяти включает в себя схему 32 управления и компонент 34 памяти, хранящий серию значений 36 памяти, связанных с работой печатающего компонента 10. Компонент 34 памяти может содержать любой подходящий элемент хранения, включающий в себя любое количество, например, энергонезависимых запоминающих устройств (NVM), таких как EPROM, EEPROM, флэш-память, NV RAM, плавкую перемычку. В одном примере значения 36 памяти могут быть значениями, сохраненными в виде поисковой таблицы, когда такая поисковая таблица может быть массивом индексирующих данных, при этом каждый элемент памяти имеет соответствующий адрес или индекс. В примерах каждое значение 36 памяти представляет бит данных, имеющий состояние бита "0" или "1", или аналоговое значение (например, напряжение или ток), соответствующее "0" и "1". В примерах схема 30 памяти является кристаллом (микросхемой на кристалле).

[0036] Схема 30 памяти включает в себя серию площадок 40 ввода/вывода (I/O) для соединения с множеством сигнальных трактов 41, по которым сообщаются рабочие сигналы печатающему компоненту 10. В одном примере множество площадок I/O 40 включает в себя площадку 42 CLK, площадку 44 данных, площадку 46 возбуждения, площадку 48 режима и площадку 50 для аналогового сигнала, которые будут описаны более подробно ниже. В примерах схема 32 управления контролирует рабочие сигналы, передаваемые печатающему компоненту 10 через площадки I/O 40. В одном примере при наблюдении последовательности рабочих сигналов, представляющих считывание памяти (например, протокол "считывания"), схема 32 управления подает аналоговый электрический сигнал на площадку 50 для аналогового сигнала, предоставляя на площадке 50 для аналогового сигнала значение аналогового электрического сигнала, представляющее сохраненные значения 36 памяти, выбранные путем считывания памяти. В примерах аналоговый электрический сигнал, подаваемый на площадку 50 для аналогового сигнала, может быть одним из аналогового сигнала напряжения и аналогового сигнала тока, и аналоговый электрический сигнал может быть одним из уровня напряжения и уровня тока. В примерах площадка 50 для аналогового сигнала может быть площадкой регистрации аналогового сигнала, соединенной со схемой регистрации аналогового сигнала, и иногда называется здесь площадкой 50 регистрации.

[0037] В одном примере при наблюдении последовательности рабочих сигналов, представляющих запись в память (протокол "записи"), схема 32 управления корректирует значения для сохраненных значений памяти.

[0038] Фиг. 2 является блочной и принципиальной схемой, в целом иллюстрирующей кристалл 30 памяти согласно одному примеру для печатающего компонента 10, когда печатающий компонент 10 может быть печатающим пером, печатающим картриджем, печатающей головкой или может включать в себя серию печатающих головок. В примерах печатающий компонент 10 может быть съемным и заменяемым в системе печати. Печатающий компонент может быть пополняемым устройством и может включать в себя бак, камеру или резервуар для текучей среды, такой как чернила. Печатающий компонент может включать в себя заменяемый резервуар для текучей среды.

[0039] В одном примере печатающий компонент 10 включает в себя схему 20 выброса текучей среды, схему 30 памяти и серию площадок 40 ввода/вывода (I/O). Схема 20 выброса текучей среды включает в себя массив 24 активаторов 26 текучей среды. В примерах активаторы 26 текучей среды могут быть выполнены с возможностью формировать серию примитивов, при этом каждый примитив имеет серию активаторов 26 текучей среды. Часть активаторов 26 текучей среды может быть выполнена как часть сопла для выброса текучей среды, а другая часть выполнена как часть насоса для циркуляции текучей среды. В одном примере схема 20 выброса текучей среды содержит матрицу (кристалл).

[0040] В одном примере площадки I/O 40 схемы 30 памяти включают в себя площадку 42 CLK, площадку 44 данных, площадку 46 возбуждения, площадку 48 режима и площадку 50 для аналогового сигнала, которые соединяются с множеством сигнальных трактов, которые передают серию цифровых и аналоговых рабочих сигналов для работы схемы 20 выброса текучей среды между печатающим компонентом 10 и отдельным устройством, таким как принтер 60. Площадка 42 CLK может передавать тактовый сигнал, площадка 44 данных может передавать данные, включающие в себя данные конфигурации и данные выбора, в том числе в виде пакетов данных группы импульсов возбуждения (FPG), площадка возбуждения может передавать сигнал возбуждения, такой как импульс возбуждения, инициирующий работу схемы 20 выброса текучей среды (такую как, например, работа выбранных активаторов 26 текучей среды), площадка 48 режима может указывать различные режимы работы схемы 20 выброса текучей среды, а площадка 50 регистрации может передавать аналоговые электрические сигналы для регистрации и работы элементов регистрации схемы 20 выброса текучей среды (таких как, например, датчики трещин, тепловые датчики, нагреватели) и элементов памяти схемы 20 выброса текучей среды, таких, которые будут описаны более подробно ниже.

[0041] В одном примере значения 36 памяти компонента 34 памяти схемы 30 памяти являются значениями памяти, связанными с печатающим компонентом 10, включающими в себя значения памяти, связанные с работой схемы 20 выброса текучей среды, такие как, например, количество сопел, уровни чернил, рабочие температуры, информация об изготовлении. В примерах, подобно описанному выше, при наблюдении последовательности рабочих сигналов, представляющих считывание памяти (например, протокол "считывания"), схема 32 управления подает аналоговый электрический сигнал на площадку 50 для аналогового сигнала, предоставляя на площадке 50 для аналогового сигнала значение аналогового электрического сигнала, представляющее сохраненные значения 36 памяти, выбранные путем считывания памяти.

[0042] В примере, когда схема 20 выброса текучей среды реализуется в виде матрицы для текучей среды, за счет размещения схемы 30 памяти отдельно от схемы 20 выброса текучей среды, такая матрица для текучей среды может быть выполнена с меньшими размерами, так что печатающая головка, включающая в себя матрицу 20 для текучей среды, может иметь меньшие размеры.

[0043] В одном примере схема 20 выброса текучей среды может включать в себя схему 28 памяти, включающую в себя серию элементов 29 памяти, хранящих значения памяти, связанные с работой печатающего компонента 10 и схемой 20 выброса текучей среды. В одном случае, когда массив 28 памяти включает в себя поврежденные элементы 29 памяти, схема 30 памяти может служить в качестве подстановочной памяти (заменяющей памяти) для массива 28 памяти с сохраненными значениями 36 памяти, заменяющими значения, хранимые элементами 29 памяти. В другом случае схема 30 памяти может дополнять массив 28 памяти (увеличивать емкость хранения, связанную со схемой 20 выброса текучей среды). В одном примере, как будет описано более подробно ниже, таком, как когда применяется для замены или замещения поврежденного массива 28 памяти на кристалле, схема 30 памяти может быть соединена с печатающим компонентом 10 через накладную подложку с разводкой (например, гибкую накладку), которая включает в себя (контактные) площадки, которые покрывают и контактируют с серией площадок I/O 40.

[0044] Фиг. 3 является блочной и принципиальной схемой, в целом иллюстрирующей схему 30 памяти, соединенную с печатающим компонентом 10, включающим в себя схему 20 выброса текучей среды, имеющую массив 28 памяти, и схему 30 памяти (например, кристалл памяти) согласно одному примеру настоящего раскрытия. В одном случае, как будет описано более подробно ниже, схема 30 памяти заменяет массив 28 памяти схемы 20 выброса текучей среды, например, когда массив 28 памяти является поврежденным.

[0045] Схема 20 выброса текучей среды включает в себя массив 24 активаторов 26 текучей среды и массив 28 элементов 29 памяти. В одном примере массив 24 активаторов 26 текучей среды и массив 28 элементов 29 памяти, каждый, размещаются, формируя столбец, при этом каждый столбец, размещенный в группах, называется примитивом, при этом каждый примитив P0-PM включает в себя серию активаторов текучей среды, указанных как активаторы F0-FN текучей среды, и серию элементов памяти, указанных как элементы M0-MN памяти. Каждый примитив P0-PM использует одинаковый набор адресов, проиллюстрированных как адреса A0-AN. В одном примере каждый активатор 26 текучей среды имеет соответствующий элемент 29 памяти, адресуемый на один и тот же адрес, например, каждый из активатора F0 текучей среды и элемента M0 памяти примитива P0 соответствует адресу A0.

[0046] В одном примере каждый активатор 26 текучей среды может иметь более одного соответствующего элемента 29 памяти, например, два соответствующих элемента 29 памяти, как указано штриховыми элементами 29 памяти, когда массив 28 элементов памяти размещается, формируя два столбца элементов 29 памяти, таких как столбцы 281 и 282, при этом каждый дополнительный элемент памяти совместно использует соответствующий адрес. В других примерах каждый активатор 26 текучей среды может иметь более двух соответствующих элементов 29 памяти, когда каждый дополнительный элемент 29 памяти размещается как часть дополнительного столбца элементов 29 памяти массива 28 памяти. Согласно одному примеру, как будет описано более подробно ниже, когда используется более одного столбца элементов 29 памяти, так что более одного элемента 29 памяти совместно используют один и тот же адрес, каждый столбец элементов 29 памяти может быть отдельно адресован (или к нему осуществлен доступ) с помощью битов столбца в пакете данных группы импульсов возбуждения, идентифицирующих столбец, к которому должен быть осуществлен доступ.

[0047] В одном примере схема 20 выброса текучей среды может включать в себя серию датчиков 70, проиллюстрированных как датчики S0-SX, регистрирующих состояние схемы 30 выброса текучей среды, таких как, например, датчики температуры и датчики трещин. В одном примере, как будет описано более подробно ниже, элементы 29 памяти и датчики 70 могут быть выборочно соединены с площадкой 50 регистрации, например, через линию 52 регистрации, для доступа, например, принтером 60. В одном примере обмен информацией с принтером 60, такой как показатели измерения трещин и температур в областях схемы 20 выброса текучей среды, и информацией, хранимой элементами 29 памяти (например, тепловой режим, смещения, цветовая карта, количество сопел и т.д.), предоставляет возможность вычисления и корректировки инструкций для работы схемы 20 выброса текучей среды (включая выброс текучей среды) согласно обнаруженным условиям.

[0048] В одном примере схема 20 выброса текучей среды включает в себя схему 80 управления для управления работой массива 24 активаторов 26 текучей среды, массива 28 элементов 29 памяти и датчиков 70. В одном примере схема 80 управления включает в себя декодер/драйвер 82 адреса, логику 84 активации/выбора, регистр 86 конфигурации, регистр 88 конфигурации памяти и схему 89 записи, при этом декодер/драйвер 82 адреса и логика 84 активации/выбора совместно используются для управления доступом к массиву 24 активаторов 26 текучей среды и массиву 28 элементов 29 памяти.

[0049] В одном примере во время события активации текучей среды управляющая логика 80 принимает пакет данных группы импульсов возбуждения (FPG) через площадку 44 данных, например, от принтера 60. В одном случае пакет FPG-данных имеет головной участок, включающий в себя данные конфигурации, такие как адресные данные, и основной участок, включающий в себя данные выбора активатора, причем каждый бит данных выбора имеет состояние выбора (например, "1" или "0"), и каждый бит данных выбора соответствует различному из примитивов P0-PM. Декодер/драйвер 82 адреса декодирует и предоставляет адрес, соответствующий данным адреса пакета данных, например, по адресной шине. В одном примере в ответ на прием импульса возбуждения через площадку 46 возбуждения (например, от принтера 60), в каждом примитиве P0-PM логика 84 активации возбуждает (активирует) активатор текучей среды, соответствующий адресу, предоставленному декодером/драйвером 82 адреса, когда соответствующий бит выбора задан (например, имеет состояние "1").

[0050] Подобным образом, согласно примерам, во время операции доступа к памяти управляющая логика 80 принимает пакет данных группы импульсов возбуждения (FPG) через площадку 44 данных, например, от принтера 60. Однако, вместо включения в себя данных выбора активатора, во время операции доступа к памяти основной участок пакета FPG-данных включает в себя данные выбора памяти, при этом каждый бит данных выбора имеет состояние выбора (например, "0" или "1") и соответствует различному из примитивов P0-PM. В одном примере в ответ на прием импульса возбуждения через площадку 46 возбуждения в каждом примитиве P0-PM логика 84 активации инициирует соединение элемента 29 памяти, соответствующего адресу, предоставленному декодером/драйвером 82 адреса, с линией 52 регистрации, когда соответствующий бит выбора задан (например, имеет состояние "1").

[0051] В случае, когда операция доступа к памяти является операцией "считывания", аналоговый ответный сигнал элемента 29 памяти (или элементов 29), соединенного с линией 52 регистрации, на аналоговый сигнал регистрации (например, сигнал тока регистрации или сигнал напряжения регистрации), поданный по линии 52 регистрации, например, принтером 60, через площадку 50 регистрации, указывает состояние элемента 29 (или элементов) памяти. В случае, когда операция доступа к памяти является операцией "записи", элементы 29 памяти, соединенные с линией 52 регистрации, могут быть запрограммированы в заданное состояние (например, на "1" из "0") аналоговым программным сигналом, поданным по линии 52 регистрации, например, принтером 60, через площадку 50 регистрации, или схемой 89 записи, объединенной со схемой 20 выброса текучей среды.

[0052] Во время операции считывания единственный элемент 29 памяти может быть соединен с линией 52 регистрации и быть считан, или комбинация (или подмножество) элементов 29 памяти может быть подсоединена параллельно с линией 52 регистрации и считана одновременно на основе ожидаемого аналогового ответного сигнала на аналоговый сигнал регистрации. В примерах каждый элемент 29 памяти может иметь известные электрические характеристики при нахождении в запрограммированном состоянии (например, задан на значение "1") и незапрограммированном состоянии (например, имеет значение "0"). Например, в одном случае элементы 29 памяти могут быть полевыми транзисторами со структурой металл-оксид-полупроводник с плавающим затвором (MOSFET), имеющими относительно высокое сопротивление, когда не запрограммированы, и относительно низкое сопротивление, когда запрограммированы. Такие электрические свойства предоставляют возможность известных ответных сигналов на известные сигналы регистрации, предназначенные указывать состояние памяти элемента 29 (или элементов) памяти, во время операции считывания.

[0053] Например, если фиксированный ток регистрации подается на линию 52 регистрации, может быть измерен ответный сигнал напряжения, который указывает состояние памяти для выбранного элемента 29 памяти или элементов 29 памяти. Когда более одного элемента 29 памяти соединяется параллельно с линией 52 регистрации, каждый дополнительный элемент памяти уменьшает сопротивление, что уменьшает ответный сигнал напряжения регистрации на площадке 50 регистрации на прогнозируемую величину. По существу, информация (например, программное состояние) может быть определена относительно комбинации выбранных элементов 29 памяти на основе измеренного напряжения регистрации. В примерах для приложения тока регистрации может быть использован источник тока, внутренний по отношению к схеме 20 выброса текучей среды. В других примерах может быть использован источник тока, внешний по отношению к схеме 20 выброса текучей среды (например, принтер 60 через площадку 50 регистрации).

[0054] Соответствующим образом, если приложено фиксированное напряжение регистрации, может быть измерен ответный сигнал тока, который указывает состояние памяти для выбранного элемента 29 памяти (или элементов 29 памяти). Когда более одного элемента 29 памяти соединяется параллельно с линией 52 регистрации, каждый дополнительный элемент памяти уменьшает сопротивление, что увеличивает ток регистрации на площадке 50 регистрации на прогнозируемую величину. По существу, информация (например, программное состояние) может быть определена относительно комбинации выбранных элементов 29 памяти на основе измеренного тока регистрации. В примерах для приложения напряжения регистрации может быть использован источник напряжения, внутренний по отношению к схеме 20 выброса текучей среды. В других примерах может быть использован источник напряжения, внешний по отношению к схеме 20 выброса текучей среды (например, принтер 60 через площадку 50 регистрации).

[0055] В одном случае для предоставления возможности схеме 20 выброса текучей среды идентифицировать операцию доступа к памяти так, чтобы информация не записывалась непреднамеренно в массив 29 памяти во время других операций, таких как операция активации текучей среды, используется уникальный протокол доступа к памяти, который включает в себя особую последовательность рабочих сигналов, принимаемых через площадки I/O 40. В одном примере протокол доступа к памяти начинается с того, что площадка 44 данных повышается (например, повышается до относительно более высокого напряжения). С площадкой 44 данных, все еще являющейся повышенной, повышается площадка 48 режима (например, повышается сигнал режима на площадке 48 режима). С помощью повышенных площадки 44 данных и площадки 48 режима управляющая логика 80 распознает, что должен произойти доступ в регистр 86 конфигурации. Серия битов данных затем сдвигается в регистр 86 конфигурации из площадки 44 данных с тактовым сигналом на площадке 42 CLK. В одном примере регистр 86 конфигурации удерживает серию битов, такую как, например, 11 битов. В других примерах регистр 86 конфигурации может включать в себя больше или меньше 11 битов. В одном примере один из битов в регистре 86 управления является битом доступа к памяти.

[0056] Пакет FPG-данных затем принимается через площадку 44 данных, при этом биты выбора в основном участке пакета данных представляют биты выбора элемента 29 памяти. В одном примере пакет FPG-данных дополнительно включает в себя бит конфигурации (например, в головном или хвостовом участке пакета данных), который, когда задан, указывает, что FPG является FPG доступа к памяти. Когда управляющая логика 80 распознает, что как бит разблокирования памяти в регистре 86 конфигурации, так и бит данных конфигурации доступа к памяти в принятом FPG-пакете "заданы", управляющая логика 80 предоставляет возможность регистру конфигурации памяти (MCR) 88 принимать данные через площадку 44 данных способом, подобным способу, по которому регистр 86 конфигурации принимал биты данных (как описано выше). Согласно одному примеру, при распознавании того, что как бит разблокирования памяти в регистре 86 конфигурации, так и бит данных конфигурации доступа к памяти в принятом пакете FPG-данных "заданы", в регистр 88 конфигурации памяти из площадки 44 данных сдвигается серия битов данных, включающая в себя бит разблокирования столбца, позволяющий (разблокирующий) доступ к столбцу 28 битов памяти, и бит разблокирования считывания/записи, указывающий является ли доступ к памяти доступом на считывание или запись (например, "0" указывает считывание памяти, а "1" указывает запись в память). В одном примере, когда схема 20 выброса текучей среды имеет массив 28 памяти, имеющий более одного столбца элементов 29 памяти, таких как столбцы 281 и 282, данные конфигурации пакета FPG-данных, сообщающие данные выбора памяти, включают в себя биты выбора столбца, идентифицирующие, к какому столбцу 28 элементов данных осуществляется доступ. Бит разблокирования столбца регистра 88 конфигурации памяти и бит выбора столбца пакета FPG-данных вместе позволяют осуществлять доступ к выбранному столбцу 28 для операции с памятью.

[0057] После загрузки данных в регистр 88 конфигурации памяти импульс возбуждения на площадке возбуждения 44 повышается, и каждый элемент 29 памяти, соответствующий адресу, представленному в заголовке FPG, и имеющий соответствующий бит выбора памяти в основном участке FPG, который задан (например, имеет значение "1"), соединяется с шиной 52 регистрации для доступа на считывание или запись, как указано состоянием бита считывания/записи регистра конфигурации памяти.

[0058] В одном примере операция считывания для датчика 70 трещины схемы 30 выброса текучей среды имеет протокол, подобный протоколу операции считывания для элементов 29 памяти. Площадка 44 данных повышается с последующим повышением сигнала режима на площадке 48 режима. Серия битов данных затем сдвигается в регистр 86 конфигурации. Однако вместо бита данных конфигурации, соответствующего операции считывания для элемента 29 памяти, заданного в регистре 86 конфигурации, задается бит данных конфигурации, соответствующий операции считывания датчика 70 трещин. После того как данные были сдвинуты в регистр 86 конфигурации, FPG принимается управляющей логикой 80, когда все биты данных основной части FPG имеют значение без выбора (например, значение "0"). Сигнал импульса возбуждения на площадке 46 возбуждения затем повышается, и датчик 70 трещины соединяется с линией 52 регистрации. Аналоговый ответный сигнал датчика 70 трещин на аналоговый сигнал регистрации на линии 52 регистрации указывает, обнаруживает ли датчик 70 трещин трещину (например, аналоговый сигнал регистрации напряжения уменьшает аналоговый ответный сигнал тока, а аналоговый сигнал регистрации тока создает аналоговый ответный сигнал напряжения).

[0059] В одном примере операция считывания теплового датчика 70 выполняется во время операции выброса текучей среды. В одном случае бит данных конфигурации, соответствующий конкретному тепловому датчику, задается в головном или хвостовом участке пакета FPG-данных, в то время как основной участок FPG включает в себя биты данных выбора активатора, один для каждого примитива P0-PM, и имеет состояние, указывающее, какие активаторы 26 текучей среды должны быть активированы. Когда сигнал импульса возбуждения на площадке 46 возбуждения повышается, выбранные активаторы 26 текучей среды возбуждаются, и выбранный тепловой датчик (например, термодиод) соединяется с линией 52 регистрации. Аналоговый сигнал регистрации, приложенный к выбранному тепловому датчику через линию 52 регистрации, приводит в результате к аналоговому ответному сигналу на линии 52 регистрации, указывающему температуру теплового датчика.

[0060] В одном примере, когда массив 28 памяти схемы 20 выброса текучей среды может включать в себя поврежденные элементы 29 памяти, хранящие некорректные значения памяти, схема 30 памяти может быть подключена параллельно со схемой 20 выброса текучей среды к выводам I/O 40 со значениями 36 памяти компонента 34 памяти, чтобы служить в качестве подменной памяти для массива 28 памяти и хранить корректные значения памяти. В одном примере схема 32 управления контролирует рабочие сигналы, принимаемые через площадки I/O 42. В одном случае, после распознавания последовательности доступа к памяти, такой как описанная выше, схема 32 управления проверяет состояние бита считывания/записи, предоставленного в регистр 88 конфигурации памяти через площадку 44 данных.

[0061] В одном примере, когда доступ к памяти является операцией "записи", схема 32 управления проверяет состояние битов выбора памяти в основном участке FPG, принятом через площадку 44 данных, для определения, какие элементы 29 памяти указываются в качестве запрограммированных (например, имеют соответствующий бит выбора, который задан (например, имеет значение "1"). Схема 32 управления затем обновляет соответствующие значения 36 памяти компонента 34 памяти, отражая какие-либо изменения в значениях 36 памяти вследствие операции записи.

[0062] В одном примере, когда доступ к памяти является операцией "считывания", схема 32 управления проверяет состояние битов выбора памяти в основном участке FPG, предоставленном через площадку 44 данных, для определения того, какие элементы 29 памяти указываются в качестве запрограммированных. Схема 32 управления затем проверяет соответствующие значения 36 памяти в компоненте 34 памяти и определяет тип аналогового сигнала регистрации, присутствующего на площадке 50 регистрации. В одном примере в ответ на обнаруженный аналоговый сигнал регистрации и на основе считываемых значений памяти схема 32 управления возбуждает аналоговый ответный сигнал на линии 52 регистрации и площадке 50 регистрации, указывающий значения для значений 36 памяти.

[0063] Например, в случае, когда аналоговый ток регистрации подан по линии 52 регистрации через площадку 50 регистрации, например, принтером 60, и считывается единственное значение памяти, схема управления подает аналоговый ответный сигнал напряжения на линию 52 регистрации, который указывает значение для считанного единственного значения памяти. Например, если считывается единственное значение памяти, аналоговый ответный сигнал напряжения, подаваемый по линии 52 регистрации схемой 32 управления, может быть относительно высоким напряжением для незапрограммированного значения памяти и может быть относительно низким напряжением для запрограммированного значения памяти. В одном примере схема 32 управления подает по линии 52 регистрации аналоговый ответный сигнал напряжения, имеющий значение, равное ожидаемому ответному сигналу с учетом известных характеристик элементов 29 памяти, количества элементов 29 памяти, считываемых параллельно, и аналогового сигнала регистрации.

[0064] С помощью контроля рабочих сигналов на площадках I/O 40, идентифицирующих операцию доступа к памяти (например, операции считывания/записи), для того, чтобы поддерживать и обновлять значения 36 памяти, и подавать ожидаемые аналоговые ответные сигналы по линии 52 регистрации в ответ на операции считывания памяти, схема 30 памяти является неотличимой от массива 28 памяти схемы 20 выброса текучей среды для устройства, осуществляющего доступ к печатающему компоненту 10, такому как принтер 60.

[0065] Фиг. 4 является блочной и принципиальной схемой, иллюстрирующей схему 30 памяти, соединенную с печатающим компонентом 10, согласно одному примеру. В примере по фиг. 4 печатающий компонент 10 включает в себя серию схем 20 выброса текучей среды, проиллюстрированных как схемы 200, 201, 202 и 203 выброса текучей среды, причем каждая включает в себя массив активаторов 24 текучей среды, проиллюстрированный как массивы 240, 241, 242 и 243 активаторов, и каждая включает в себя массив 28 памяти, проиллюстрированный как массивы 280, 281, 282 и 283 памяти. В одном примере каждая схема 20 выброса текучей среды содержит отдельную матрицу выброса текучей среды, при этом каждая матрица выдает различные цветные чернила. Например, матрица 200 выброса текучей среды может быть матрицей для голубого цвета, матрица 201 выброса текучей среды может быть матрицей для пурпурного цвета, матрица 202 выброса текучей среды может быть матрицей для желтого цвета, а матрица 203 выброса текучей среды может быть матрицей для черного цвета. В примере матрицы 200, 201 и 202 выброса текучей среды выполнены как часть пера 90 цветной печати, а матрица 203 выброса текучей среды выполнена как часть пера 92 монохромной печати.

[0066] В одном примере каждая матрица 200-203 выброса текучей среды принимает данные от соответствующей из площадок 440-443 данных и каждая совместно использует площадку 42 CLK, площадку 46 возбуждения, площадку 48 режима и площадку 50 регистрации. В примерах, к каждому из массивов 280, 281, 282 и 283 памяти может быть отдельно осуществлен доступ во время операции доступа к памяти. В других примерах к любой комбинации массивов 280, 281, 282 и 283 памяти может быть одновременно осуществлен доступ во время операции доступа к памяти. Например, к элементам памяти из каждого из массивов 280, 281, 282 и 283 памяти может быть одновременно осуществлен доступ (например, операция считывания) через линию 52 регистрации, например, принтером 60.

[0067] Схема 30 памяти соединяется с площадкой 42 CLK, площадкой 46 возбуждения, площадкой 48 режима и площадкой 50 регистрации и соединяется с каждой из площадок 440-443 данных для соединения параллельно с каждой из матриц 200, 201, 202 и 203 выброса текучей среды. В примерах схема 30 памяти может служить в качестве заменяющей памяти для какой-либо комбинации массивов 280, 281, 282 и 283 памяти. Например, в одном случае схема 30 памяти может служить в качестве заменяющей памяти для массива 241 памяти, тогда как в другом примере схема 30 памяти может служить в качестве замены для каждого из массивов 280, 281, 282 и 283 памяти.

[0068] В одном примере схема 30 памяти может служить в качестве дополнительной памяти для схемы 20 выброса текучей среды. В таком случае для операций доступа к памяти элементы 29 памяти схемы 20 выброса текучей среды и значения 36 памяти схемы 30 памяти могут быть отдельно идентифицированы с помощью битов выбора столбца в данных конфигурации пакетов FPG-данных, сообщающих данные выбора памяти. Например, схема 203 выброса текучей среды пера 92 монохромной печати может включать в себя схему 283 памяти, имеющую серию столбцов элементов 29 памяти, например, три столбца. В таком случае столбцы элементов памяти схемы 203 выброса текучей среды могут быть идентифицированы по битам выбора столбца данных конфигурации пакета FPG-данных в качестве столбцов 1-3, и дополнительные столбцы значений 36 памяти компонента 34 памяти, действующие в качестве дополнительной памяти, могут быть идентифицированы как дополнительные столбцы, начинающиеся со столбца 4.

[0069] В одном примере, подобном тому, который описан выше относительно фиг. 3, схема 30 памяти контролирует рабочие сигналы на серии площадок I/O 40, обнаруживая последовательность доступа к памяти для любого из массивов 280, 281, 282 и 283 памяти, для которых схема 30 памяти служит в качестве заменяющей памяти.

[0070] В одном примере, когда схема 30 памяти служит в качестве заменяющей памяти для менее чем всех матриц 200, 201, 202 и 203 выброса текучей среды печатающего компонента 10, элементы 29 памяти матриц 20 выброса текучей среды, для которых схема 30 памяти не служит в качестве заменяющей памяти, не способны считывать параллельно с элементами памяти матриц 20 выброса текучей среды, для которых схема памяти служит в качестве заменяющей памяти.

[0071] Фиг. 5 является блочной и принципиальной схемой, в целом иллюстрирующей схему 30 памяти, соединенную с компонентом 10 памяти, согласно одному примеру, где также показаны части компонента 10 памяти. Как будет описано более подробно ниже, согласно примеру по фиг. 5, схема 30 памяти соединяется параллельно с устройством 20 выброса текучей среды с площадкой 50 регистрации во время операций доступа к памяти. В примере, согласно иллюстрации по фиг. 5, схема 30 памяти может служить в качестве заменяющей памяти для массива 28 элементов 29 памяти схемы 20 выброса текучей среды (когда один или более элементов 29 памяти могут быть поврежденными).

[0072] В одном примере логика 84 активации схемы 20 выброса текучей среды включает в себя переключатель 100 разрешения (разблокировки) считывания, переключатель 102 активации столбца, управляемый через логический элемент И 103, и переключатель 104 выбора элемента памяти, управляемый через логический элемент И 106. Согласно одному примеру, как описано выше, во время операции считывания схема 20 выброса текучей среды принимает группу импульсов возбуждения, включающую в себя данные конфигурации (например, в головном и/или хвостовом участке), и данные выбора памяти (например, в основном участке). В одном примере данные конфигурации включают в себя бит выбора столбца и данные адреса. Бит выбора столбца указывает конкретный столбец элементов 29 памяти, к которым осуществляется доступ, когда массив 28 памяти включает в себя более одного столбца элементов памяти, такие как столбцы 281 и 282 на фиг. 3. Данные адреса декодируются декодером 82 адреса и предоставляются схеме 84 активации. В одном примере данные выбора включают в себя серию битов выбора памяти, когда каждый бит выбора памяти соответствует различному примитиву (P0-PM) столбца элементов 29 памяти, когда столбец выбора, который задан (например, имеет значение "1"), предоставляет возможность осуществления доступа к элементам 29 памяти столбца 28 для считывания (или записи).

[0073] Дополнительно, в качестве части протокола операции считывания, регистр 88 конфигурации памяти загружается битом разблокировки столбца и битом разблокировки считывания. Бит разблокировки считывания регистра 88 конфигурации памяти включает переключатель 100 разблокировки считывания. Когда сигнал возбуждения повышается, бит разблокировки считывания регистра 88 конфигурации вместе с битом выбора столбца данных конфигурации группы импульсов возбуждения побуждают логический элемент И 1083 включать переключатель 102 активации столбца для выбранного столбца, и данные выбора и адрес (через декодер 86 адреса) группы импульсов возбуждения и сигнал возбуждения вместе побуждают логический элемент И 106 включать переключатель 104 выбора элемента памяти, тем самым соединяя элемент 29 памяти с линией 52 регистрации. Отметим, что в некоторых примерах бит выбора столбца может не составлять часть данных конфигурации группы импульсов возбуждения, когда схема 20 выброса текучей среды включает в себя единственный столбец элементов памяти.

[0074] После соединения с линией 52 регистрации элемент 29 памяти подает аналоговый выходной сигнал в ответ на аналоговый сигнал регистрации на линии 52 регистрации, когда значение аналогового выходного сигнала зависит от программного состояния элемента памяти (когда такое программное состояние может быть поврежденным). В одном примере, как описано выше, элемент 29 памяти может иметь относительно более высокое электрическое сопротивление, когда имеет незапрограммированное состояние (например, значение "0"), по сравнению с тем, когда имеет запрограммированное состояние (например, значение "1"). Соответственно, когда аналоговый сигнал регистрации является фиксированным аналоговым током (так называемый "режим вынужденного тока"), аналоговое выходное напряжение, выдаваемое элементом 29 памяти, будет иметь относительно более высокий уровень напряжения, когда элемент 29 памяти имеет незапрограммированное состояние, и относительно более низкий уровень тока, когда элемент 29 памяти имеет запрограммированное состояние. Подобным образом, когда аналоговый сигнал регистрации является фиксированным напряжением (так называемый "режим вынужденного напряжения"), аналоговый выходной ток, выдаваемый элементом 29 памяти, будет иметь относительно более низкий уровень тока, когда элемент 29 памяти имеет незапрограммированное состояние, и относительно более высокий уровень тока, когда элемент 29 памяти имеет запрограммированное состояние.

[0075] Отметим, что во время операции записи переключатель 100 разблокировки считывания поддерживается в разомкнутом положении, отсоединяя элемент 29 памяти от линии 52 регистрации, в то время как переключатель 102 разблокировки столбца и переключатель 104 выбора элемента памяти замкнуты. Бит разрешения записи регистра конфигурации памяти соединяет регулятор 90 напряжения с элементом 29 памяти для приложения к нему программного напряжения.

[0076] Схема 32 управления схемы 30 памяти, согласно одному примеру, включает в себя управляющую логику 120, первый управляемый напряжением источник 122 тока, работающий в качестве источника тока для узла 128, и второй управляемый напряжением источник тока, работающий в качестве токоотвода от узла 128, при этом узел 128 соединяется с линией 52 регистрации на второй площадке 501 регистрации через линию 129 управления. В примере по фиг. 4 во время операции доступа к памяти схема 20 памяти соединяется с линией 152 регистрации параллельно схеме 20 выброса текучей среды на второй площадке 501 регистрации.

[0077] В одном примере схема 30 памяти подключается параллельно со схемой 20 выброса текучей среды к площадкам I/O 40 через накладную подложку 160 с разводкой, которая описывается более подробно ниже (например, см. фиг. 6A). В одном примере подложка 160 с разводкой включает в себя пару площадок I/O для каждого сигнального тракта, при этом сигнальный тракт маршрутизируется через накладную 160 подложку с разводкой к печатающему компоненту 10 от первой площадки I/O из пары ко второй площадке I/O из пары. Например, подложка 160 с разводкой включает в себя пару площадок 42 и 421 CLK, пару площадок 44 и 441 данных, пару площадок 46 и 461 возбуждения, пару площадок 48 и 481 режима и пару площадок 50 и 501 регистрации. В одном примере в каждом случае первая площадка из пары площадок соединяется с входящей сигнальной линией, а вторая площадка из пары площадок соединяет исходящую сигнальную линию с печатающим компонентом 10.

[0078] В одном примере накладная подложка 160 с разводкой дополнительно включает в себя резистор 150 регистрации, соединенный последовательно с линией 52 регистрации, когда управляющая логика 120 контролирует напряжение на выводах 152 и 154 высокой и низкой стороны резистора 150 регистрации. В других примерах резистор 150 регистрации может быть выполнен как часть схемы 32 управления (например, см. фиг. 10).

[0079] Хотя проиллюстрировано как соединенное с сигнальными трактами и печатающим компонентом 10 через подложку 160 с разводкой, любое число других реализаций может быть применено для обеспечения такого соединения. Например, в одном примере функциональность подложки 160 с разводкой может быть объединена в схему 30 памяти.

[0080] Компонент 34 памяти включает в себя серию значений 36 памяти. В одном примере каждое значение 36 памяти соответствует различному из элементов 29 памяти схемы 20 выброса текучей среды. Однако в то время как один или более элементов 29 памяти схемы 20 выброса текучей среды могут быть поврежденными и хранить некорректные значения, каждое из значений 36 памяти компонента 34 памяти представляет корректное значение памяти. Отметим, что в примерах компонент 34 памяти может включать в себя в дополнение к значениям 36 памяти значения 36 памяти, соответствующие элементам 29 памяти.

[0081] В одном примере схема 32 управления контролирует рабочие сигналы, сообщаемые схеме 20 выброса текучей среды на площадках I/O 40, например, от принтера 60. В одном примере при обнаружении рабочих сигналов, представляющих последовательность доступа к памяти, указывающую операцию считывания элемента 29 памяти, управляющая логика 120 контролирует напряжение на выводе 152 высокой стороны (или выводе 154 низкой стороны) резистора 150 регистрации, определяя, выполняется ли операция считывания в режиме вынужденного тока или режиме вынужденного напряжения. Если применяется режим вынужденного тока, уровень напряжения на выводе 152 высокой стороны будет повышаться (например, линейное повышение) в течение периода времени, следующего за повышением площадки 46 возбуждения, когда линия 52 регистрации заряжается. Если применяется режим вынужденного напряжения, напряжение на выводе 152 высокой стороны будет оставаться относительно устойчивым на фиксированном уровне напряжения входного сигнала регистрации.

[0082] В одном примере при обнаружении операции считывания управляющая логика 120 считывает значение 36 памяти, соответствующее элементу 29 памяти, идентифицированному как элемент, к которому осуществляется доступ путем операции считывания. На основе значения 36 памяти управляющая логика 120 способна определять ожидаемый уровень выходного ответного сигнала напряжения, который должен присутствовать на площадке 50 регистрации во время операции считывания в режиме вынужденного тока, и ожидаемый уровень выходного ответного сигнала тока, который должен присутствовать на площадке 50 регистрации во время операции считывания в режиме вынужденного напряжения, через контур обратной связи, сформированный с резистором 150 регистрации.

[0083] Поскольку схема 30 памяти подключается параллельно со схемой 20 выброса текучей среды к линии 52 регистрации, во время операции считывания, в ответ на аналоговый сигнал регистрации, вынуждаемый на линии 52 регистрации, на второй площадке 501 регистрации присутствует аналоговый выходной ответный сигнал (например, напряжение или ток) от элемента 29 памяти. В одном примере управляющая логика 120 регулирует управляемые напряжением источники 122 и 124 тока, подавая ток на вторую площадку 501 регистрации или отбирая ток со второй площадки 501 регистрации, так что комбинация выходного ответного сигнала от элемента 29 памяти схемы 20 выброса текучей среды и выходного ответного сигнала схемы 32 управления на второй площадке 50 регистрации создает ожидаемый уровень аналогового выходного ответного сигнала (напряжения или тока) на площадке 50 регистрации.

[0084] В одном примере, при нахождении в режиме вынужденного тока, управляющая логика 120 контролирует напряжение на выводе 152 высокой стороны резистора 150 регистрации и регулирует управляемые напряжением источники 122 и 124 тока для регулирования величины тока, подаваемого на вторую площадку 501 регистрации (либо подает ток на вторую площадку 501 регистрации, либо отбирает ток со второй площадки 501 регистрации), так что объединенный ответный сигнал схемы 30 памяти и схемы 20 выброса текучей среды предоставляет ожидаемый уровень выходного ответного сигнала напряжения на площадке 50 регистрации.

[0085] Подобным образом, в одном примере, при нахождении в режиме вынужденного напряжения, управляющая логика контролирует напряжение на резисторе 150 датчика через выводы 152 и 154 высокой стороны и низкой стороны, определяя уровень выходного ответного сигнала тока на площадке 50 регистрации. Схема управления 120 затем регулирует управляемые напряжением источники 122 и 124 тока для регулирования величины тока, подаваемого на вторую площадку 501 регистрации (либо подает ток на вторую площадку 501 регистрации, либо отбирает ток со второй площадки 501 регистрации), так что объединенный ответный сигнал схемы 30 памяти и схемы 20 выброса текучей среды предоставляет ожидаемый уровень выходного ответного сигнала тока на площадке 50 регистрации.

[0086] С помощью регулирования управляемых напряжением источников 122 и 124 тока для предоставления ожидаемого значения аналогового выходного ответного сигнала на площадке 50 регистрации на основе корректных значений памяти для схемы 20 выброса текучей среды, которые сохранены в качестве значений 36 памяти компонентом 34 памяти, схема 30 памяти способна заменять поврежденный массив 28 памяти на схеме 20 выброса текучей среды, так что печатающий компонент 10 способен оставаться рабочим, тем самым уменьшая число поврежденных печатающих компонентов во время изготовления. Дополнительно, при подключении схемы 30 памяти параллельно со схемой выброса текучей среды к площадкам I/O 40 датчики 70 схемы 20 выброса текучей среды остаются доступными все время для контроля через площадку 50 регистрации, например, принтером 60.

[0087] Фиг. 6A является видом в разрезе, иллюстрирующим части накладной подложки 160 с разводкой для соединения схемы 20 памяти с выводами I/O 40. В частности, фиг. 6A представляет вид в разрезе, проходящем через площадку 50 регистрации по фиг. 5, когда схема 30 памяти подключена параллельно со схемой 20 выброса текучей среды к площадке 50 регистрации. В одном примере накладная подложка 160 с разводкой включает в себя гибкую подложку 162, имеющую первую поверхность 163 и противоположную вторую поверхность 164. Схема 30 памяти и площадка 50 регистрации размещаются на первой поверхности 163, при этом токопроводящая дорожка, представляющая линию 52 регистрации, соединяет площадку 50 регистрации со схемой 30 памяти. В одном примере, как проиллюстрировано, резистор 150 регистрации размещается последовательно с линией 52 регистрации между площадкой 50 регистрации и схемой 30 памяти. В одном примере токопроводящее сквозное межсоединение 166 проходит от линии 52 регистрации на первой поверхности 163 сквозь гибкую подложку 163 ко второй площадке 501 регистрации на второй поверхности 164.

[0088] Печатающий компонент 10 включает в себя подложку 168, на которой установлена схема 20 выброса текучей среды, и включает в себя площадку 502 регистрации, соединенную со схемой 20 выброса текучей среды линией 521 регистрации. Когда гибкая подложка 160 с разводкой соединяется с печатающим компонентом 10, как указано направленной стрелкой 169, вторая площадка 501 регистрации совмещается с площадкой 502 регистрации, соединяя линию 52 регистрации с площадкой 502 регистрации между резистором 150 регистрации и схемой 30 памяти.

[0089] Фиг. 6B является блок-схемой, в целом иллюстрирующей вид в разрезе накладной подложки 160 с разводкой, показывающей соединения площадок I/O 40, отличных от площадки 50 регистрации, таких как, например, площадка 48 режима. Как проиллюстрировано, площадка 48 режима размещается на верхней поверхности 163 подложки 162. Сквозное межсоединение 167 проходит сквозь подложку 162, соединяя первую площадку 48 режима со второй площадкой 481 режима на второй поверхности 164. Когда гибкая подложка 160 с разводкой соединяется с печатающим компонентом 10, площадка 481 режима совмещается с площадкой 482 режима, соединяя площадку 48 режима со схемой 20 выброса текучей среды.

[0090] Фиг. 7 является блочной и принципиальной схемой, в целом иллюстрирующей схему 10 памяти согласно одному примеру. Также в целом проиллюстрированы части печатающего компонента 10. Пример по фиг. 7 подобен примеру по фиг. 5, когда схема 30 памяти присоединяется параллельно с устройством 20 выброса текучей среды к площадке 50 регистрации во время операций доступа к памяти. Однако, в примере по фиг. 7 схема 32 управления схемы 30 памяти включает в себя операционный усилитель 170 и источник 172 регулируемого напряжения вместо управляемых напряжением источников 122 и 124 тока.

[0091] Первый вход операционного усилителя 170 соединяется с опорным потенциалом (например, землей) через источник 172 регулируемого напряжения. Второй вход и выход операционного усилителя 170 соединяются с узлом 128, при этом узел 128 соединен с площадкой 501 регистрации через линию 129.

[0092] В одном примере во время операции считывания памяти, при нахождении в режиме вынужденного тока управляющая логика 120 контролирует напряжение на выводе 152 высокой стороны резистора 150 регистрации и регулирует выходное напряжение операционного усилителя 170 путем регулирования уровня напряжения источника 172 регулируемого напряжения (когда выходное напряжение приблизительно соответствует напряжению источника 172 регулируемого напряжения) для регулирования величины тока, подаваемого на вторую площадку 501 регистрации (либо подает ток на вторую площадку 501 регистрации, либо отбирает ток со второй площадки 501 регистрации), так что объединенный ответный сигнал схемы 30 памяти и схемы 20 выброса текучей среды предоставляет ожидаемый уровень выходного ответного сигнала напряжения на площадке 50 регистрации.

[0093] Подобным образом, в одном примере, при нахождении в режиме вынужденного напряжения управляющая логика контролирует напряжение на резисторе 150 датчика через выводы 152 и 154 высокой стороны и низкой стороны, определяя уровень выходного ответного сигнала тока на площадке 50 регистрации. Схема управления 120 затем регулирует выходное напряжение операционного усилителя 170 путем регулирования уровня напряжения источника 172 регулируемого напряжения (когда выходное напряжение приблизительно соответствует напряжению источника 172 регулируемого напряжения) для регулирования величины тока, подаваемого на вторую площадку 501 регистрации (либо подает ток на вторую площадку 501 регистрации, либо отбирает ток со второй площадки 501 регистрации), так что объединенный ответный сигнал схемы 30 памяти и схемы 20 выброса текучей среды предоставляет ожидаемый уровень выходного ответного сигнала тока на площадке 50 регистрации.

[0094] Фиг. 8 является блочной и принципиальной схемой схемы 30 памяти для печатающего компонента 10 согласно одному примеру. Пример по фиг. 8 подобен примеру по фиг. 5, когда схема 30 памяти присоединяется параллельно с устройством 20 выброса текучей среды к площадке 50 регистрации во время операций доступа к памяти. Однако, в примере по фиг. 8 схема 32 управления схемы 30 памяти включает в себя серию резисторов 180-183, которые могут быть соединены, формируя регулируемый делитель напряжения между источником VCC напряжения и опорным напряжением (например, землей) вместо управляемых напряжением источников 122 и 124 тока.

[0095] В примере резистор 180 источника подсоединяется между источником VCC напряжения и узлом 128. Резисторы 181-183 токоотвода соединяются параллельно друг с другом между узлом 128 и опорным напряжением (например, землей) через соответствующие переключатели 184-186. Отметим, что схемой 32 управления может быть использовано количество резисторов, отличное от количества, проиллюстрированного на фиг. 8.

[0096] В одном примере во время операции считывания памяти, при нахождении в режиме вынужденного тока, управляющая логика 120 контролирует напряжение на выводе 152 высокой стороны резистора 150 регистрации и регулирует количество резисторов 181-183 токоотвода, которые подсоединяются между узлом 128 и землей, путем управления переключателями 184-186 для регулирования величины тока, подаваемого на вторую площадку 501 регистрации, так что объединенный ответный сигнал схемы 30 памяти и схемы 20 выброса текучей среды предоставляет ожидаемый уровень выходного ответного сигнала напряжения на площадке 50 регистрации.

[0097] Подобным образом, в одном примере, при нахождении в режиме вынужденного напряжения, управляющая логика контролирует напряжение на резисторе 150 датчика через выводы 152 и 154 высокой стороны и низкой стороны, определяя уровень выходного ответного сигнала тока на площадке 50 регистрации. Схема управления 120 затем регулирует количество резисторов 181-183 токоотвода, которые подсоединяются между узлом 128 и землей, путем управления переключателями 184-186 для регулирования величины тока, подаваемого на вторую площадку 501 регистрации (либо подает ток на вторую площадку 501 регистрации, либо отбирает ток со второй площадки 501 регистрации), так что объединенный ответный сигнал схемы 30 памяти и схемы 20 выброса текучей среды предоставляет ожидаемый уровень выходного ответного сигнала тока на площадке 50 регистрации.

[0098] Фиг. 9 является блочной и принципиальной схемой, в целом иллюстрирующей схему 30 памяти согласно одному примеру. Схема 30 памяти включает в себя множество площадок I/O 40, включающих в себя площадку 50 для аналогового сигнала, соединяющихся с множеством сигнальных трактов 41, по которым сообщаются рабочие сигналы печатающему компоненту 10. В одном примере управляемый селектор 190 соединяется в один ряд с одним из сигнальных трактов 41 через площадки I/O 40, при этом управляемый селектор 190 является управляемым, чтобы размыкать соответствующую сигнальную линию с печатающим компонентом 10 (прерывать или разрывать соединение с печатающим компонентом 10). В одном примере в ответ на последовательность рабочих сигналов, принимаемых площадками I/O 40, представляющую считывание памяти, схема 32 управления размыкает управляемый селектор 190, прерывая сигнальный тракт до печатающего компонента 10, блокируя считывание памяти компонента 10 памяти, и подает аналоговый сигнал на площадку 50 для аналогового сигнала, предоставляя на площадке 50 для аналогового сигнала значение аналогового электрического сигнала, представляющее сохраненные значения 36 памяти, выбранные путем считывания памяти. За счет прерывания сигнального тракта во время считывания памяти печатающий компонент 10 не способен подавать аналоговый сигнал на площадку 50 для аналогового сигнала во время операций считывания памяти. В примерах печатающему компоненту 10 предоставляется возможность подавать аналоговый сигнал на площадку 50 во время функций считывания не памяти, которые осуществляют доступ к площадке 50 для аналогового сигнала, таких как считывание аналогового компонента. В примерах такой аналоговый компонент может быть схемой регистрации (например, тепловым датчиком).

[0099] Фиг. 10 является блочной и принципиальной схемой, иллюстрирующей схему 30 памяти согласно одному примеру настоящего раскрытия, когда управляемый селектор 190 является управляемым переключателем 190. В примере по фиг. 10 площадки I/O 40 включают в себя первую площадку 50 для аналогового сигнала и вторую площадку 501 для аналогового сигнала, соединенные с линией 52 для аналоговых сигналов, когда управляемый переключатель 90 подсоединяется между площадками 50 и 501 для аналогового сигнала с соединением в один ряд с линией 52 для аналоговых сигналов. В одном примере, как проиллюстрировано, схема 32 управления дополнительно включает в себя второй управляемый переключатель 192, соединенный с первой площадкой 50 для аналогового сигнала. Пример по фиг. 10 подобен примеру по фиг. 5, за исключением того, что переключатели 190 и 192 управляемого селектора предоставляют возможность схеме 32 управления выборочно присоединять к и отсоединять схему 30 памяти и схему 20 выброса текучей среды от линии 52 выбора таким образом, что в одном примере схема 30 памяти не подключается параллельно со схемой 20 выброса текучей среды во время операции доступа к памяти. Дополнительно, согласно одному примеру, резистор 150 регистрации вместе с выводами 152 и 154 высокой стороны и низкой стороны размещаются в схеме 32 памяти.

[00100] В одном примере, когда управляющая логика 120 идентифицирует операцию доступа не к памяти, управляющая логика размыкает переключатель 190 управляемого селектора, отсоединяя управляемые напряжением источники 122 и 124 тока от линии 52 регистрации, и замыкает переключатель 192 селектора, соединяя схему 20 выброса текучей среды с линией 52 регистрации для предоставления возможности контроля за датчиками 70 (см. фиг. 3), например, с помощью принтера 60, без потенциала для помехи в выходных сигналах датчиков 70 за счет схемы 32 управления.

[00101] В одном примере, когда управляющая логика 120 идентифицирует операцию доступа к памяти, управляющая логика может замыкать переключатель 192 селектора, соединяя узел 128 и управляемые напряжением источники 122 и 124 тока с линией 52 регистрации, и размыкать переключатель 190 селектора, отсоединяя схему 20 выброса текучей среды от линии 52 регистрации так, чтобы схема 20 выброса текучей среды больше не была подключена параллельно со схемой 32 управления ко второй площадке 501 регистрации, так что схема 20 выброса текучей среды блокируется от реагирования на операцию считывания памяти. Схема 32 управления может затем регулировать управляемые напряжением источники 122 и 124 тока, предоставляя ожидаемый аналоговый ответный сигнал напряжения на площадке 50 регистрации, как описано выше относительно фиг. 5, но без вклада аналогового выходного ответного сигнала от схемы 20 выброса текучей среды. За счет отсоединения схемы 20 выброса текучей среды от линии 52 регистрации во время операций доступа к памяти может быть устранено потенциальное загрязнение от поврежденных элементов 29 памяти в аналоговом выходном ответном сигнале на площадке 50 регистрации.

[00102] В других примерах переключатель 190 управляемого селектора может быть подсоединен подобным образом для нахождения в один ряд с трактом сигнала возбуждения через площадку возбуждения так, чтобы сигнал возбуждения блокировался от схемы 20 выброса текучей среды во время операции считывания памяти, так что схема 20 выброса текучей среды не способна реагировать на такую операцию считывания памяти. В другом примере управляемый селектор 190 может быть мультиплексором, подсоединенным в один ряд с линией 52 регистрации (или трактом 52 для аналогового сигнала), когда схема 32 управления работает, мультиплексор работает, отсоединяя линию 52 регистрации от схемы 20 выброса текучей среды во время считывания памяти, а в ином случае работает, соединяя линию 52 регистрации со схемой 20 выброса текучей среды, например, во время операций считывания не памяти, которые осуществляют доступ к площадке 50 регистрации аналогового сигнала и линии 52 регистрации.

[00103] Отметим, что конфигурации схемы 32 управления, описанные на фиг. 6 и 7, и любое число других подходящих конфигураций управления, могут быть использованы в примерном печатающем компоненте 10 по фиг. 10.

[00104] Фиг. 11 является видом в разрезе, иллюстрирующим части накладываемой подложки 160 с разводкой для соединения схемы 30 памяти с выводами I/O 40, как проиллюстрировано на фиг. 10, согласно одному примеру. В частности, фиг. 11 представляет вид в разрезе, проходящем через площадку 50 регистрации. В одном примере схема 30 памяти и площадка 50 регистрации размещаются на первой поверхности 163 гибкой подложки 162, при этом токопроводящая дорожка представляет линию 52 регистрации, соединяющую площадку 50 регистрации со схемой 30 памяти. Согласно одному примеру, резистор 150 регистрации и переключатели 190 и 192 селектора размещаются внутренне по отношению к схеме 30 памяти. Токопроводящее сквозное межсоединение 167 проходит сквозь гибкую подложку 162, при этом схема 30 памяти электрически соединяется с площадкой 502 регистрации на второй поверхности 164 гибкой подложки 162 токопроводящими дорожками 522 и 523 (представляющими части линии 52 регистрации) посредством сквозного межсоединения 167. Когда гибкая подложка 160 с разводкой соединяется с печатающим компонентом 10, как указано стрелкой 169, площадка 502 регистрации совмещается с площадкой 501 регистрации так, чтобы площадка 50 регистрации соединялась со схемой 20 выброса текучей среды через переключатель 192 селектора в схеме 30 памяти.

[00105] Фиг. 12 является блочной и принципиальной схемой, в целом иллюстрирующей схему 30 памяти согласно одному примеру. Схема 30 памяти включает в себя множество площадок I/O 40, включающих в себя первую и вторую площадки 1 и 2 для аналогового сигнала, указанные как 50 и 501, соединяющие множество сигнальных трактов 41 с печатающим компонентом 10, в том числе тракт 52 для аналоговых сигналов, соединенный с площадками 50 и 501 для аналогового сигнала. В одном примере первая площадка 50 для аналогового сигнала электрически изолируется от второй площадки 501 для аналогового сигнала, прерывая тракт для аналоговых сигналов до печатающего компонента 10. В ответ на последовательность рабочих сигналов на площадках I/O 40, представляющих считывание памяти, схема 32 управления подает аналоговый сигнал на первую площадку 50 для аналогового сигнала, предоставляя значение аналогового электрического сигнала на первой площадке 50 для аналогового сигнала, представляющее сохраненные значения 36 памяти, выбранные путем считывания памяти.

[00106] За счет прерывания тракта 52 для аналоговых сигналов во время считывания памяти печатающий компонент 10 отсоединяется от тракта 52 для аналоговых сигналов во время операций считывания памяти. Как будет описано более подробно ниже, в дополнение к предоставлению значений 36 памяти, соответствующих элементам памяти печатающего компонента 10, значения 36 памяти могут представлять значения для других функций, которые осуществляют доступ к печатающему компоненту 10 через тракт 52 для аналоговых сигналов, таких как команды считывания датчика (например, для считывания тепловых датчиков).

[00107] Фиг. 13 является блочной и принципиальной схемой схемы 30 памяти согласно одному примеру и в целом иллюстрирует части печатающего компонента 10. Пример по фиг. 13 подобен примеру по фиг. 10, но вместо включения в себя переключателя селектора (например, переключателя 192 селектора), выборочно управляющего соединением схемы 30 выброса текучей среды с линией 52 регистрации, схема 30 выброса текучей среды физически отсоединена от линии 52 регистрации. В одном примере со ссылкой на фиг. 14 ниже накладная подложка 160 с разводкой размещается для подключения схемы 30 памяти к линии 52 выбора и для подключения схемы 30 памяти к площадкам I/O 42-48 параллельно со схемой 20 выброса текучей среды при отсоединении схемы 20 выброса текучей среды от площадки 50 регистрации.