Изобретение относится к техническим средствам информатики и вычислительной техники и может быть использовано для создания быстродействующих, специализированных и высокопроизводительных цифровых модулей, выполняющих арифметические операции сложение и вычитание. Достоинством предлагаемого устройства являются широкие функциональные возможности, простая конструкции, устройство выполнено на нейроподобных и пороговых элементах, которые обеспечивают высокое быстродействие и надёжность.

Известен “Сумматор-вычитатель по модулю” (№ 1075259 от 23.02.84), который вычисляет сумму и разность по модулю двоичных чисел.

Известен “Четырехвходовый одноразрядный сумматор” (№ 1429108 от 07.10.88), который вычисляет сумму двоичных чисел.

В качестве прототипа выбран “Одноразрядный сумматор-вычитатель”

(№ 1368875, от 23.01.88 г.), который выполняет операции суммирования и вычитания двоичных чисел.

Недостатком предложенных технических решений является сложная структура одноразрядных сумматоров-вычитателей, низкая скорость выполнения операций суммирования и вычитания, сложный алгоритм работы.

В представленном устройстве при выполнении арифметических операций суммирования и вычитания двоичных разрядов все элементы работают в полную силу. Обеспечивается максимальное быстродействие, сумматор-вычитатель не содержат аппаратурной избыточности. Эффективность конструирования подобных устройств проявляется при использовании нейроподобных элементов.

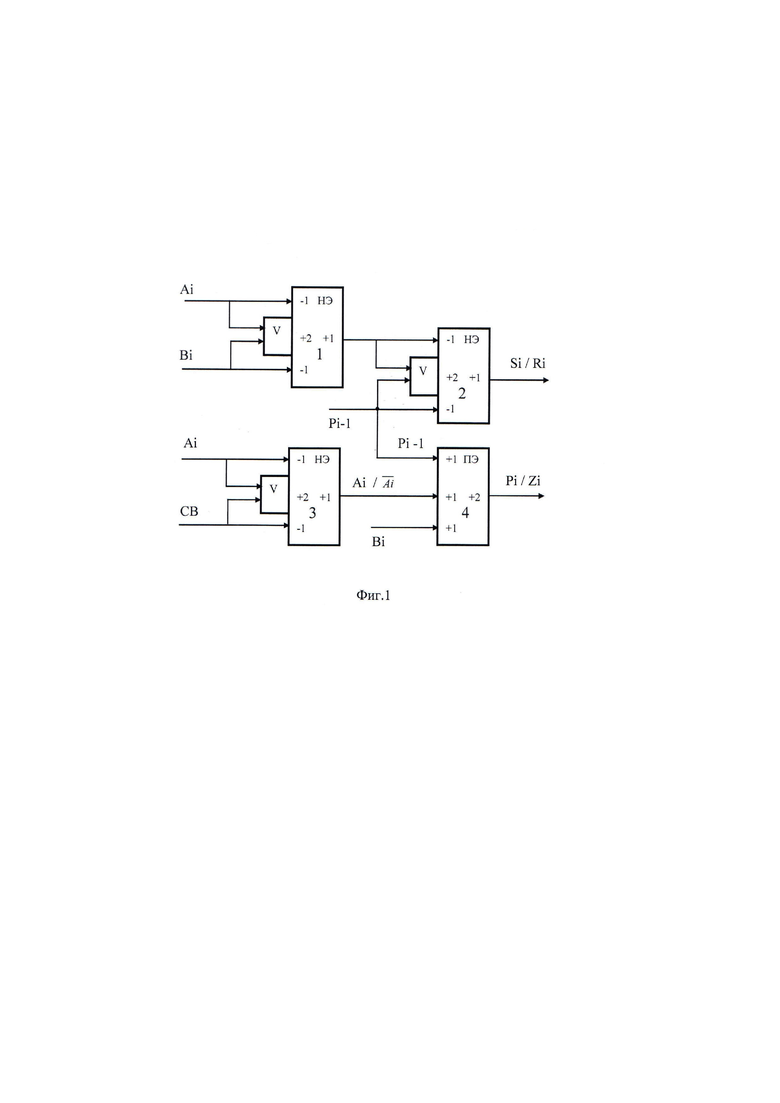

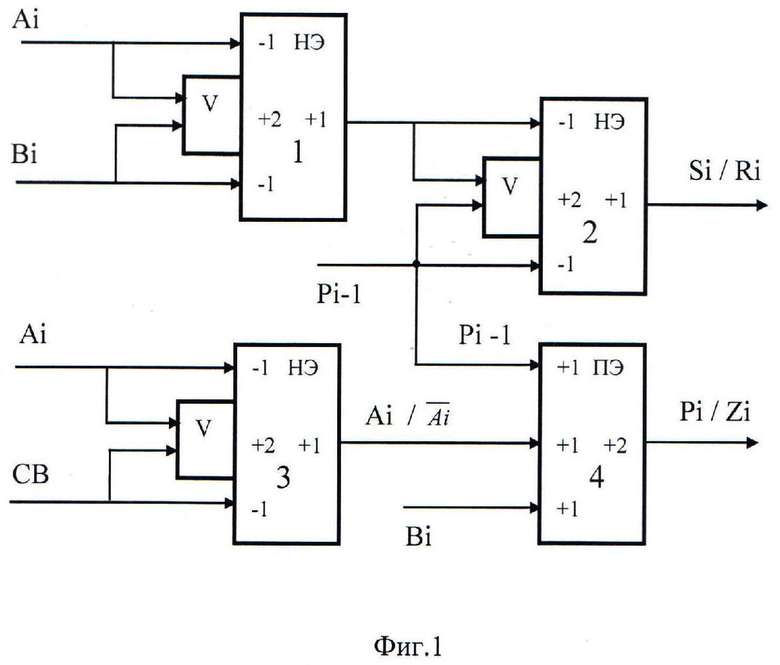

Решение задачи осуществляется тем, что сумматор-вычитатель на элементах нейронной логики, содержащий элемент РАВНОЗНАЧНОСТЬ 1, элемент РАВНОЗНАЧНОСТЬ 2, элемент РАВНОЗНАЧНОСТЬ 3, выполненные на нейропободных элементах НЭ 1-3, отличающий тем, что дополнительно введен пороговый элемент 4, причем входной двоичный разряд первого числа поступает на первый вход логического элемента ИЛИ и на первый вход первого нейропободного элемента, на второй вход, которого поступает входной двоичный разряд второго числа и на второй вход логического элемента ИЛИ, выход первого нейропободного элемента соединен с первым входом второго логического элемента ИЛИ и с первым входом второго нейропободного элемента, на второй вход логического элемента ИЛИ и на второй вход второго нейропободного элемента поступает входной двоичный разряд переноса из младшего разряда в старший, который поступает на первый вход четвертого порогового элемента, на третий вход, которого поступает входной двоичный разряд второго числа, входной двоичный разряд первого числа поступает на первый вход логического элемента ИЛИ и на первый вход третьего нейропободного элемента, на второй вход, которого поступает сигнал признака операции и на второй вход логического элемента ИЛИ, выход третьего нейропободного элемента соединен со вторым входом четвертого порогового элемента.

Предложенное устройство отличается от известных тем, что его схема построена на нейроподобных и пороговых элементах. Одноразрядный сумматор-вычитатель вычисляет сумму Si, перенос Pi из младшего разряда в старший, разность Ri и Zi заём из старшего разряда в младший одноразрядных двоичных чисел.

НЭ1 – первый нейроподобный элемент устройства.

НЭ2 – второй нейроподобный элемент устройства.

НЭ3 – третий нейроподобный элемент устройства.

ПЭ4 – четвертый пороговый элемент устройства.

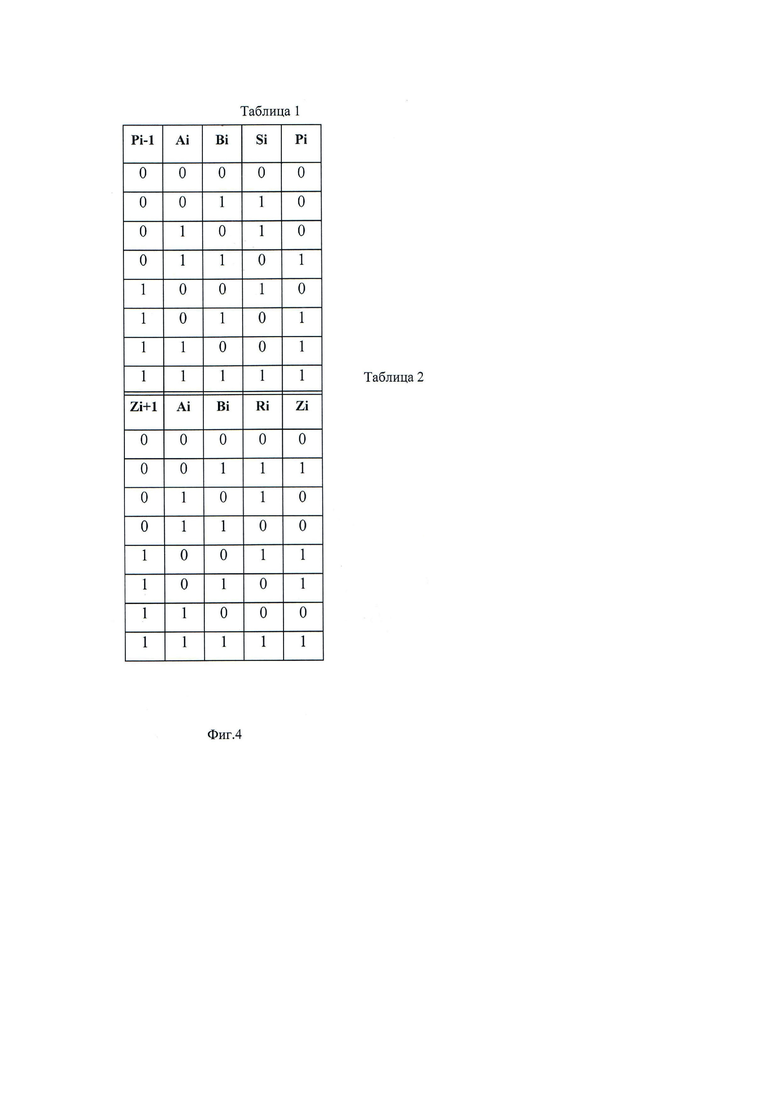

Полный одноразрядный сумматор предназначен для сложения трёх одноразрядных двоичных чисел. Устройство имеет три входа: двоичные разряды Ai, Bi и результат переноса Pi-1 предыдущего сумматора и два выхода: результата сложения Si и сигнала переноса в старший разряд Pi.

Таблица 1 истинности отображает функционирования полного одноразрядного сумматора.

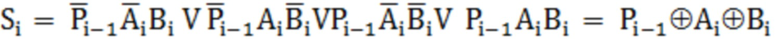

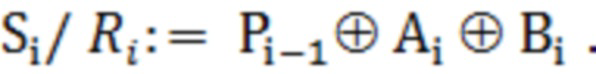

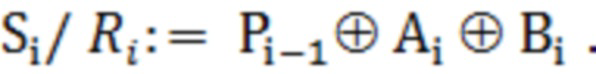

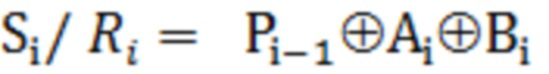

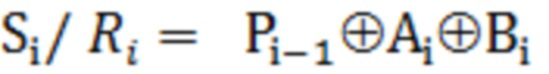

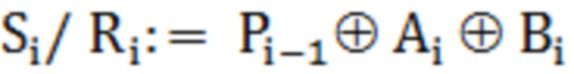

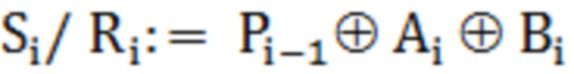

Из таблицы 1 сумма Si чисел определяется формулой

(1)

(1)

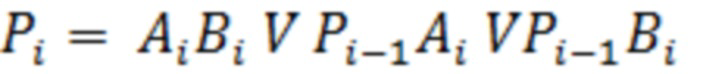

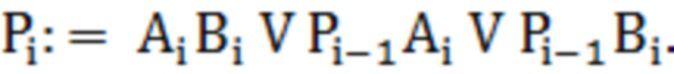

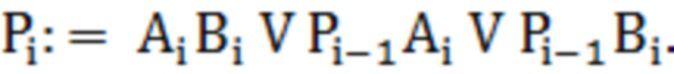

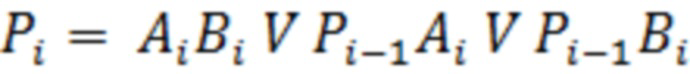

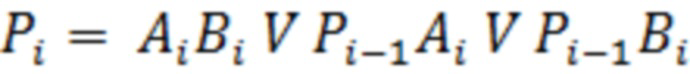

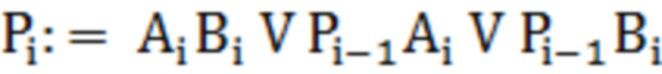

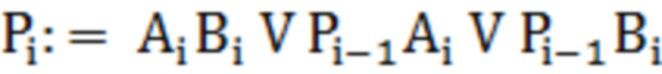

Перенос Pi из младшего разряда в старший при сложении чисел определяется формулой

(2)

(2)

Работа полного одноразрядного вычитателя описывается таблицей 2 истинности, в которой отображены: заём Zi+1, поступающий из соседнего более младшего разряда, уменьшаемое Аi, вычитаемое Вi, разность Ri, заём Zi, возникающий в данном i-том разряде.

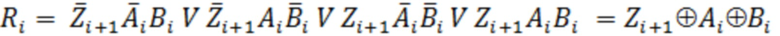

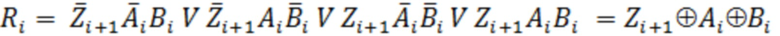

Из таблицы 2 разность чисел

определяется формулой

определяется формулой

(3)

(3)

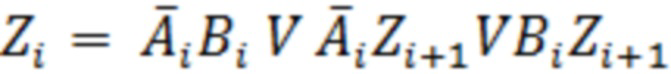

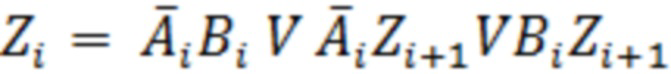

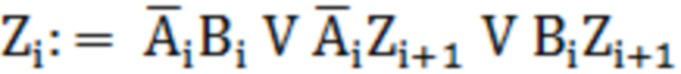

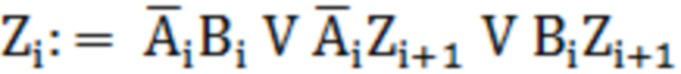

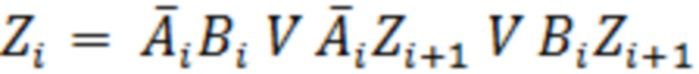

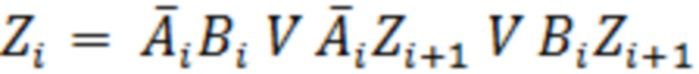

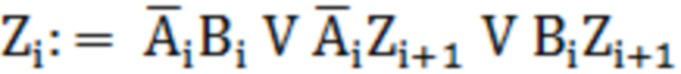

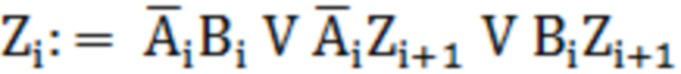

Заём Zi из старшего разряда в младший определяется формулой

(4)

(4)

Формулы, по которым вычисляются сумма

и разность

и разность

одинаковые, два сумматора по модулю два, выполнены на нейропободных элементах 1 и 2 (фиг.1). При выполнении операции сложение перенос

одинаковые, два сумматора по модулю два, выполнены на нейропободных элементах 1 и 2 (фиг.1). При выполнении операции сложение перенос

из младшего разряда в старший выполнен на нейропободном элементе 3 и пороговом элементе 4. Нейропободный элемент 3 выполняет функцию повторителя двоичного разряда

из младшего разряда в старший выполнен на нейропободном элементе 3 и пороговом элементе 4. Нейропободный элемент 3 выполняет функцию повторителя двоичного разряда

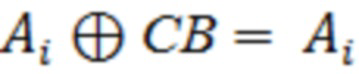

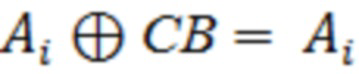

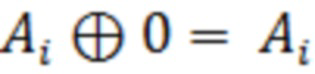

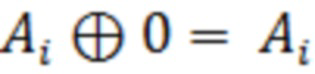

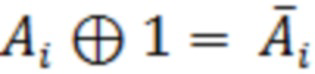

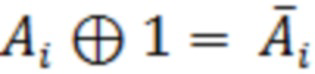

, который подаётся на первый вход элемента. На второй вход нейропободного элемента 3 подаётся признак операции СВ. Если выполняется операция суммирование, сигнал СВ равен нулю. На выходе нейропободного элемента 3 будет значение

, который подаётся на первый вход элемента. На второй вход нейропободного элемента 3 подаётся признак операции СВ. Если выполняется операция суммирование, сигнал СВ равен нулю. На выходе нейропободного элемента 3 будет значение

. Перенос

. Перенос

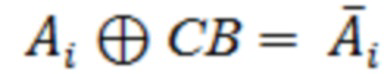

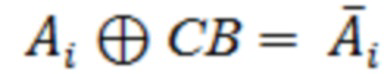

вычисляется пороговым элементом 4. При выполнении операции вычитание двоичных разрядов сигнал СВ равен единице. Нейропободный элемент 3 выполняет операцию инвертора, на выходе которого выполняется функция

вычисляется пороговым элементом 4. При выполнении операции вычитание двоичных разрядов сигнал СВ равен единице. Нейропободный элемент 3 выполняет операцию инвертора, на выходе которого выполняется функция

. Заём

. Заём

из старшего разряда в младший вычисляется на пороговом элементе 4.

из старшего разряда в младший вычисляется на пороговом элементе 4.

На фиг.1 изображена функциональная схема сумматора-вычитателя, выполняющий операции суммирование или вычитание.

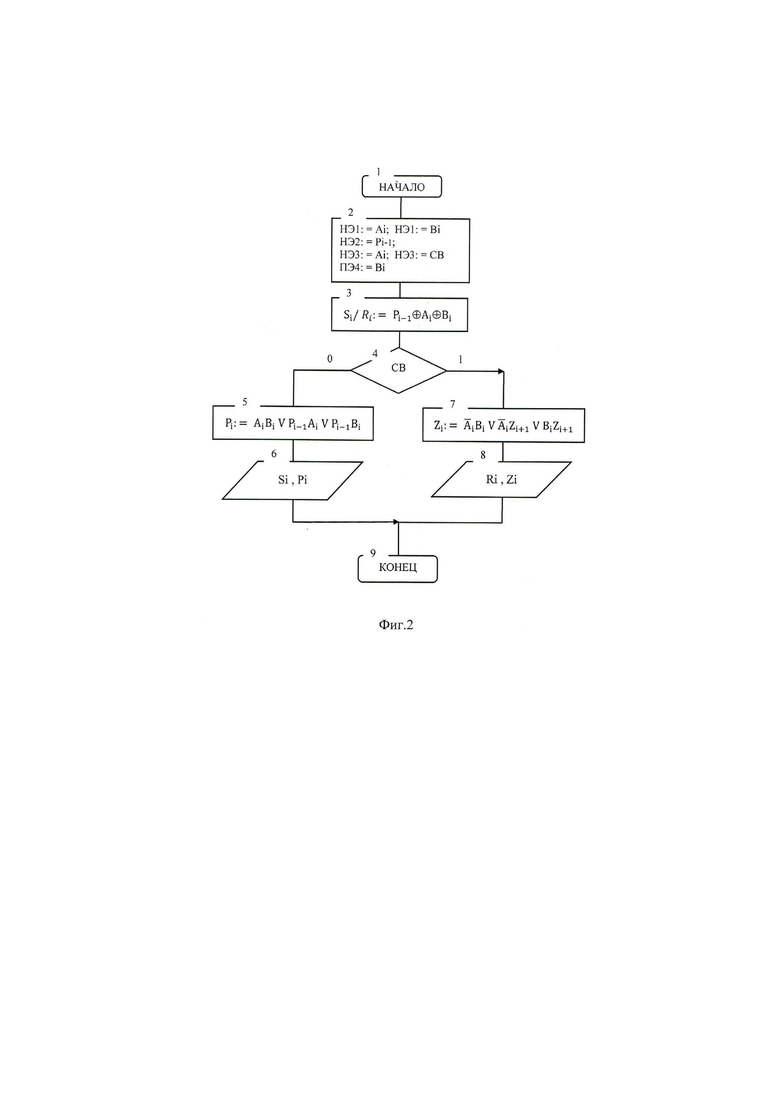

На фиг.2 представлена содержательная ГСА работы устройства.

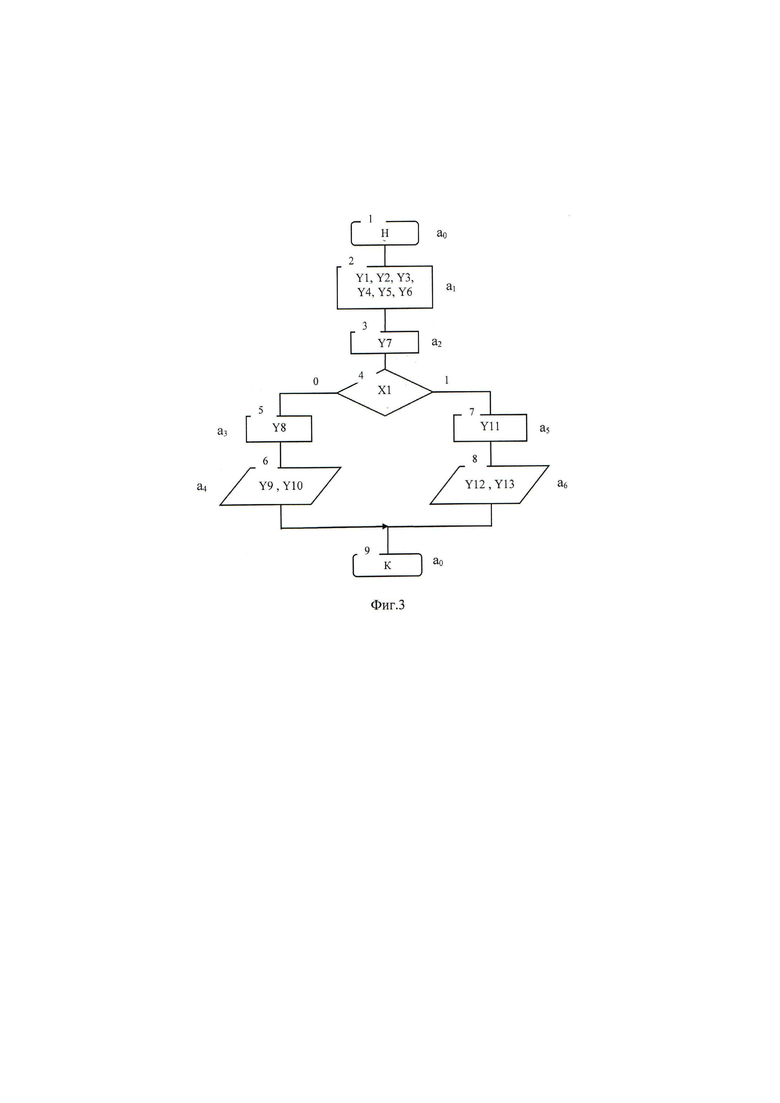

На фиг.3 представлена размеченная ГСА работы устройства.

На фиг.4 таблицы работы полного одноразового вычитателя

Для описания алгоритма работы сумматора-вычитателя используются следующие идентификаторы.

1. Ai – двоичный разряд числа.

2.

– инверсный разряд числа.

– инверсный разряд числа.

3. Bi – двоичный разряд числа.

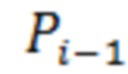

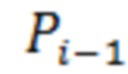

4. Pi-1 – перенос из младшего разряда в старший.

5. Zi+1 – заём из старшего разряда в младший.

6. СВ – признак выполнения операций суммирования или вычитания.

7. Si – сумма двоичных чисел.

8. Pi – перенос в старший разряд.

9. Ri – разность двоичных чисел.

10. Zi – заём из старшего разряда.

Блок-схема алгоритма работы сумматора-вычитателя.

Содеpжательная ГСА упpавления пpиведена на фиг. 2 и она отpажает pаботу сумматора-вычитателя.

Блок 1 алгоритма является начальным.

В блоке 2 алгоритма на вход сумматора-вычитателя поступают двоичные разряды чисел по командам: НЭ1: = Ai, НЭ1: = Bi происходит подача двоичного разряда Ai на первый вход первого нейроподобного элемента, на второй вход первого нейроподобного элемента подаётся двоичный разряд числа Bi, НЭ2: = Pi-1 перенос из младшего разряда в старший подаётся на второй вход второго нейроподобного элемента, НЭ3: = Ai; НЭ3: = СВ происходит подача двоичного разряда Ai на первый вход третьего нейроподобного элемента, на второй вход третьего нейроподобного элемента подаётся признак выполнения операций суммирования или вычитания сигнал СВ, ПЭ4: = Bi на третий вход четвертого порогового элемента подаётся двоичный разряд числа Bi.

В блоке 3 алгоритма вычисляется сумма Si или разность Ri двоичных чисел по формуле

В блоке 4 алгоритма анализируется признак выполнения операций суммирования или вычитания сигнал СВ. Если сигнал

равен нулю, то выполняется операция суммирование двоичных чисел, происходит переход из блока 4 по выходу ДА на блок 5 алгоритма. Если сигнал

равен нулю, то выполняется операция суммирование двоичных чисел, происходит переход из блока 4 по выходу ДА на блок 5 алгоритма. Если сигнал

равен единице, то выполняется операция вычитания двоичных чисел, происходит переход из блока 4 по выходу НЕТ на блок 7 алгоритма.

равен единице, то выполняется операция вычитания двоичных чисел, происходит переход из блока 4 по выходу НЕТ на блок 7 алгоритма.

В блоке 5 алгоритма вычисляется перенос в старший разряд чисел по формуле

В блоке 6 алгоритма выдаётся результат сложения Si и перенос Pi в старший разряд двоичных чисел.

В блоке 7 алгоритма вычисляется заём из старшего разряда чисел по формуле

.

.

В блоке 8 алгоритма выдаётся результат вычитания Ri и заём Zi в младший разряд двоичных чисел.

Блок 9 алгоритма является конечным.

Работа сумматора-вычитателя заключается в следующем. На входы первого нейроподобного элемента подаются двоичные разряды

и

и

. Первый нейроподобный элемент выполняет операцию суммирования входных двоичных разрядов. На выходе первого сумматора вычисляется сумма двоичных разрядов

. Первый нейроподобный элемент выполняет операцию суммирования входных двоичных разрядов. На выходе первого сумматора вычисляется сумма двоичных разрядов

и

и

. Результат суммы поступает на первый вход второго нейроподобного элемента. На второй вход этого элемента поступает двоичный разряд переноса

. Результат суммы поступает на первый вход второго нейроподобного элемента. На второй вход этого элемента поступает двоичный разряд переноса

из младшего разряда в старший. На выходе второго нейроподобного элемента вычисляется сумма

из младшего разряда в старший. На выходе второго нейроподобного элемента вычисляется сумма

и разность

и разность

входных двоичных разрядов

входных двоичных разрядов

и

и

по формуле

по формуле

. На входы третьего нейроподобного элемента подается двоичный разряд

. На входы третьего нейроподобного элемента подается двоичный разряд

и признак выполнения арифметической операции суммирования или вычитания сигнал

и признак выполнения арифметической операции суммирования или вычитания сигнал

. Если сигнал

. Если сигнал

равен нулю, то выполняется операция суммирование двоичных чисел. Если сигнал

равен нулю, то выполняется операция суммирование двоичных чисел. Если сигнал

равен единице, то выполняется операция вычитания двоичных чисел. При выполнении операции суммирование третий нейроподобный элемент выполняет операцию повторителя, на выходе формируется сигнал

равен единице, то выполняется операция вычитания двоичных чисел. При выполнении операции суммирование третий нейроподобный элемент выполняет операцию повторителя, на выходе формируется сигнал

по формуле

по формуле

. При выполнении операции вычитания третий нейроподобный элемент выполняет операцию отрицание, на выходе инвертора формируется сигнал

. При выполнении операции вычитания третий нейроподобный элемент выполняет операцию отрицание, на выходе инвертора формируется сигнал

по формуле

по формуле

. Пороговый элемент 4 вычисляет перенос

. Пороговый элемент 4 вычисляет перенос

из младшего разряда в старший по формуле

из младшего разряда в старший по формуле

. При выполнении операции вычитания на пороговом элементе 4 вычисляется заём

. При выполнении операции вычитания на пороговом элементе 4 вычисляется заём

из старшего разряда в младший по формуле

из старшего разряда в младший по формуле

(фиг.1).

(фиг.1).

Размеченная ГСА pаботы устройства пpиведена на фиг.3 где обозначено:

Логические условия:

Х1 : “СВ”

Опеpатоpы:

У1 : “НЭ1: = Ai” У7 : “

”

”

У2 : “НЭ1: = Bi” У8 : “

”

”

У3 : “НЭ2: = Pi-1” У9 : “ Si , Pi”

У4 : “НЭ3: = Ai ” У10 : “

”

”

У5 : “НЭ3: = СВ У11 : “ Ri , Zi”

У6 : “ПЭ4: = Bi”

| название | год | авторы | номер документа |

|---|---|---|---|

| Параллельный сумматор-вычитатель на элементах нейронной логики | 2020 |

|

RU2780299C2 |

| Устройство поразрядного вычисления логических и арифметических операций | 2020 |

|

RU2739343C1 |

| Параллельно-последовательный сумматор-вычитатель старшими разрядами вперед на нейронах | 2019 |

|

RU2708501C1 |

| Параллельный сумматор-вычитатель на нейроподобных элементах | 2023 |

|

RU2805774C1 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР-ВЫЧИТАТЕЛЬ НА НЕЙРОНАХ | 2003 |

|

RU2246752C1 |

| ДЕЛИТЕЛЬ НА НЕЙРОНАХ | 2003 |

|

RU2249846C1 |

| АРИФМЕТИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2004 |

|

RU2292580C2 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР-ВЫЧИТАТЕЛЬ НА НЕЙРОНАХ СО СКВОЗНЫМ ПЕРЕНОСОМ | 2012 |

|

RU2523942C2 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР-ВЫЧИТАТЕЛЬ В ТРОИЧНОЙ СИСТЕМЕ СЧИСЛЕНИЯ НА НЕЙРОНАХ | 2010 |

|

RU2453900C2 |

| ПОСЛЕДОВАТЕЛЬНЫЙ ДЕЛИТЕЛЬ ТРОИЧНЫХ ЦЕЛЫХ ЧИСЕЛ | 2023 |

|

RU2810609C1 |

Изобретение относится к техническим средствам информатики и вычислительной техники. Технический результат заключается в расширении арсенала средств того же назначения. Сумматор-вычитатель на элементах нейронной логики включает элемент РАВНОЗНАЧНОСТЬ 1, элемент РАВНОЗНАЧНОСТЬ 2, элемент РАВНОЗНАЧНОСТЬ 3, выполненные на нейропободных элементах НЭ 1-3, также дополнительно введен пороговый элемент 4, причем входной двоичный разряд первого числа поступает на первый вход логического элемента ИЛИ и на первый вход первого нейропободного элемента, на второй вход которого поступает входной двоичный разряд второго числа, и на второй вход логического элемента ИЛИ, выход первого нейропободного элемента соединен с первым входом второго логического элемента ИЛИ и с первым входом второго нейропободного элемента, а выход третьего нейроподобного элемента соединен со вторым входом четвертого порогового элемента. 4 ил.

Сумматор-вычитатель на элементах нейронной логики, содержащий элемент РАВНОЗНАЧНОСТЬ 1, элемент РАВНОЗНАЧНОСТЬ 2, элемент РАВНОЗНАЧНОСТЬ 3, выполненные на нейропободных элементах НЭ 1-3, отличающийся тем, что дополнительно введен пороговый элемент 4, причем входной двоичный разряд первого числа поступает на первый вход логического элемента ИЛИ и на первый вход первого нейропободного элемента, на второй вход которого поступает входной двоичный разряд второго числа, и на второй вход логического элемента ИЛИ, выход первого нейропободного элемента соединен с первым входом второго логического элемента ИЛИ и с первым входом второго нейропободного элемента, на второй вход логического элемента ИЛИ и на второй вход второго нейропободного элемента поступает входной двоичный разряд переноса из младшего разряда в старший, который поступает на первый вход четвертого порогового элемента, на третий вход которого поступает входной двоичный разряд второго числа, входной двоичный разряд первого числа поступает на первый вход логического элемента ИЛИ и на первый вход третьего нейропободного элемента, на второй вход которого поступает сигнал признака операции, и на второй вход логического элемента ИЛИ, выход третьего нейропободного элемента соединен со вторым входом четвертого порогового элемента.

| А.В | |||

| САВЕЛЬЕВ "НЕЙРОЛОГИЧЕСКИЕ АСПЕКТЫ КЛЕТОЧНОЙ НЕЙРОМАТЕМАТИКИ", журнал "ИСКУССТВЕННЫЙ ИНТЕЛЛЕКТ" N4 2008 | |||

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| US 795140 B2, 22.01.2011. | |||

Авторы

Даты

2020-02-25—Публикация

2019-06-13—Подача