Область техники, к которой относится изобретение

Изобретение относится к области передачи информации и может быть использовано при передаче сообщений в широкополосных системах радиосвязи с кодовым разделением каналов.

Уровень техники

Известно устройство, позволяющее передавать информацию в системах с кодовым разделением каналов (Способ передачи информации в системах с кодовым разделением каналов и устройство для его осуществления, патент РФ № 2234191, опубл. 10.08.2004), которое использует операцию одновременной передачи сложных широкополосных сигналов на основе нелинейных последовательностей де Брейна со сменой формы последовательности в процессе передачи сообщения от одного информационного символа к другому.

Последовательности де Брейна так же, как и словари Уолша, обладают свойством ортогональности в точке, а большое разнообразие словарей де Брейна и наличие нелинейных операций в алгоритме формирования данного класса последовательностей позволяет использовать их в системах с многостанционным доступом для кодового уплотнения канала передачи.

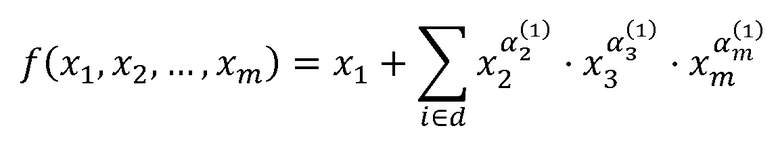

Отличительным признаком этого устройства является применение для каналов передачи сообщений, сменяемых от одного информационного символа к другому, ортогональных кодовых словарей де Брейна, каждое кодовое слово которых может быть построено путем суммирования по модулю двух сигналов, снимаемых с разрядов регистра сдвига с нелинейными обратными связями по одному, по два и так далее до m включительно, где m - число разрядов регистра сдвига, функция обратных связей, которого задается соотношением:

где  - разрешенный набор двоичных чисел, определяющий порядок подключения прямых и инверсных выходов элементов памяти регистра сдвига;

- разрешенный набор двоичных чисел, определяющий порядок подключения прямых и инверсных выходов элементов памяти регистра сдвига;

- число разрешенных двоичных наборов, необходимых для генерирования максимального периода последовательности

- число разрешенных двоичных наборов, необходимых для генерирования максимального периода последовательности  равного

равного

Недостатком данного устройства является то, что хотя количество ортогональных сигналов, формируемых на основе кодовых словарей де Брейна, больше числа ортогональных сигналов Уолша размерности  однако их количество является строго фиксированным для любой размерности

однако их количество является строго фиксированным для любой размерности  что позволяет сделать вывод об их низкой структурной скрытности.

что позволяет сделать вывод об их низкой структурной скрытности.

Наиболее близким по технической сущности к предлагаемой системе является устройство передачи информации с кодовым разделением каналов за счет использования ансамблей ортогональных сигналов (Способ передачи информации на основе хаотически формируемых ансамблей дискретных многоуровневых ортогональных сигналов: патент РФ № 2428795, опубл. 10.09.2011), которое повышает структурную скрытность системы передачи информации с кодовым разделением каналов за счет использования ансамблей ортогональных сигналов, хаотически формируемых на основе собственных векторов диагональной положительно определенной симметрической матрицы размерностью

Отличительным признаком этого устройства является то, что для передачи сообщений, сменяемых от одного информационного символа к другому, применяют ортогональные кодовые комбинации, в качестве которых используют ансамбли дискретных ортогональных сигналов, формируемые путем расчета собственных чисел и собственных векторов диагональной положительно определенной симметрической матрицы, диагональными коэффициентами которой являются хаотически формируемые числовые последовательности.

Недостатком данного устройства является ограниченный набор формируемых ансамблей дискретных ортогональных сигналов, возникающий в силу использования только положительных псевдослучайных чисел, что ограничивает его функциональные возможности. Это связано с тем, что используемые в устройстве вычислители могут работать только с положительно определёнными числами.

Целью изобретения является разработка устройства, позволяющего в процессе передачи информации расширить количество неповторяющихся формируемых ансамблей стохастических ортогональных кодов (СОК) за счёт использования не только положительных, но и отрицательных псевдослучайных чисел (ПСЧ), задаваемых в качестве исходных данных для этого устройства.

Раскрытие изобретения

Задачей предлагаемого изобретения является разработка системы передачи информации с повышенной структурной скрытностью.

Техническим результатом является повышение уровня структурной скрытности широкополосных систем радиосвязи с кодовым разделением каналов, достигаемое за счёт использования в процессе передачи информации увеличенного количества ансамблей стохастических ортогональных кодов.

Технический результат, который может быть достигнут с помощью предлагаемого изобретения, заключается в том, что для передачи сообщений, сменяемых от одного информационного символа к другому, предлагается использовать сформированные псевдослучайным образом ансамбли стохастических ортогональных кодов, описываемые собственными векторами диагональных положительно определенных симметрических матриц размерностью N. При этом используется свойство ортогональности собственных векторов симметрических матриц, заключающееся в том, что собственные векторы, соответствующие различным собственным значениям нормального оператора, попарно ортогональны (см. Г. Корн, Т.Корн. Справочник по математике (для научных работников и инженеров). – М.: Издательство «Наука», 1974. - С.436).

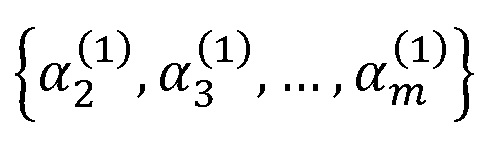

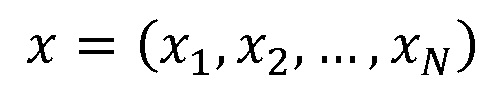

Известно, что всякий ненулевой вектор  называется собственным вектором матрицы

называется собственным вектором матрицы  , если найдется такое число

, если найдется такое число  , что будет выполняться равенство:

, что будет выполняться равенство:

Это число  называется собственным значением матрицы

называется собственным значением матрицы  , соответствующим собственному вектору

, соответствующим собственному вектору  .

.

Если в пространстве выбран определенный базис, то уравнение (1) для собственных векторов и собственных значений линейного преобразования можно записать в матричной форме:

Всякий ненулевой столбец  , для которого выполняется равенство (2), называется собственным вектором матрицы

, для которого выполняется равенство (2), называется собственным вектором матрицы  , соответствующим собственному значению

, соответствующим собственному значению  .

.

Собственный вектор матрицы  - это столбец вида (3) составленный из координат собственного вектора

- это столбец вида (3) составленный из координат собственного вектора  линейного преобразования

линейного преобразования  в выбранном базисе.

в выбранном базисе.

Собственные векторы вещественной диагональной симметрической матрицы, отвечающие различным собственным значениям, ортогональны, т.е. их скалярное произведение равно нулю (см. Клиот-ДашинскийМ.И.Алгебра матриц и векторов. 3-е изд.,стер.,/ - СПб.: Издательство «Лань», 2001. – 160с. – (Учебники для вузов. Специальная литература)).

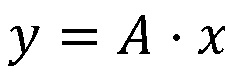

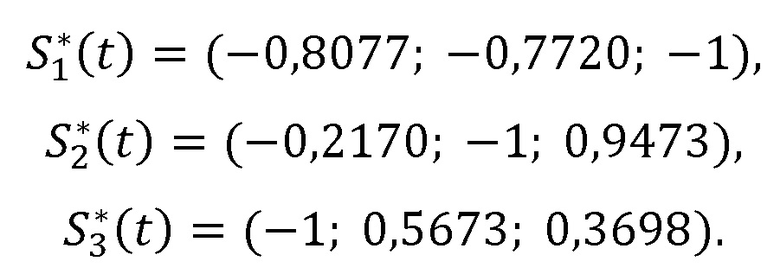

Из всего выше сказанного следует, что для любой вещественной диагональной симметрической матрицы  (4) существует набор собственных значений

(4) существует набор собственных значений  и каждому собственному значению соответствует собственный вектор

и каждому собственному значению соответствует собственный вектор  , который попарно ортогонален с любым из векторов ансамбля.

, который попарно ортогонален с любым из векторов ансамбля.

При реализации информационного обмена в предлагаемой системе передачи информации расширение информационной последовательности происходит таким образом, что, если информационный бит, равен единице то используется ортогональный сигнал инверсной структуры, а если информационный бит, равен нулю, то используется ортогональный сигнал прямой структуры (см. Столингс В. Беспроводные линии связи и сети.: Пер. с англ. – М.: Издательский дом «Вильямс», 2003. - С.213).

Нелинейность формируемых структур сигналов достигается за счет того, что на каждом такте передачи информации расширяющая последовательность в виде одного из ансамблей СОК, описываемых собственными векторами диагональных положительно определенных симметрических матриц, формируется путем стохастического задания набора диагональных коэффициентов положительно определенной симметрической матрицы  вида (4) генератором случайных положительных чисел.

вида (4) генератором случайных положительных чисел.

Так как по условию матрица  вида (4)заполняется только положительными числами, то для использования отрицательных чисел над ними будет проводится инвертирование при их подаче в блок памяти, а также обратное инвертирование в отношении уже полученных ансамблей, для формирования которых они и использовались. Справедливость использования прямого инвертирования входных отрицательных псевдослучайных чисел и обратного инвертирования ансамбля стохастических ортогональных кодов основана на том, что знаки координат собственных векторов симметрической матрицы

вида (4)заполняется только положительными числами, то для использования отрицательных чисел над ними будет проводится инвертирование при их подаче в блок памяти, а также обратное инвертирование в отношении уже полученных ансамблей, для формирования которых они и использовались. Справедливость использования прямого инвертирования входных отрицательных псевдослучайных чисел и обратного инвертирования ансамбля стохастических ортогональных кодов основана на том, что знаки координат собственных векторов симметрической матрицы  вида (4) определяются знаками диагональных элементов этой матрицы. Следовательно, можно заключить, что изменение знаков диагональных элементов симметрической матрицы

вида (4) определяются знаками диагональных элементов этой матрицы. Следовательно, можно заключить, что изменение знаков диагональных элементов симметрической матрицы  вида (4)приводит к однозначному изменению знаков координат собственных векторов этой матрицы. Это свойство используется в изобретении [Пашинцев В.П., Малофей О.П., Жук А.П. и др. Развитие теории синтеза и методов формирования ансамблей дискретных сигналов для перспективных систем радиосвязи различных диапазонов радиоволн. М.: Физматлит, 2010].

вида (4)приводит к однозначному изменению знаков координат собственных векторов этой матрицы. Это свойство используется в изобретении [Пашинцев В.П., Малофей О.П., Жук А.П. и др. Развитие теории синтеза и методов формирования ансамблей дискретных сигналов для перспективных систем радиосвязи различных диапазонов радиоволн. М.: Физматлит, 2010].

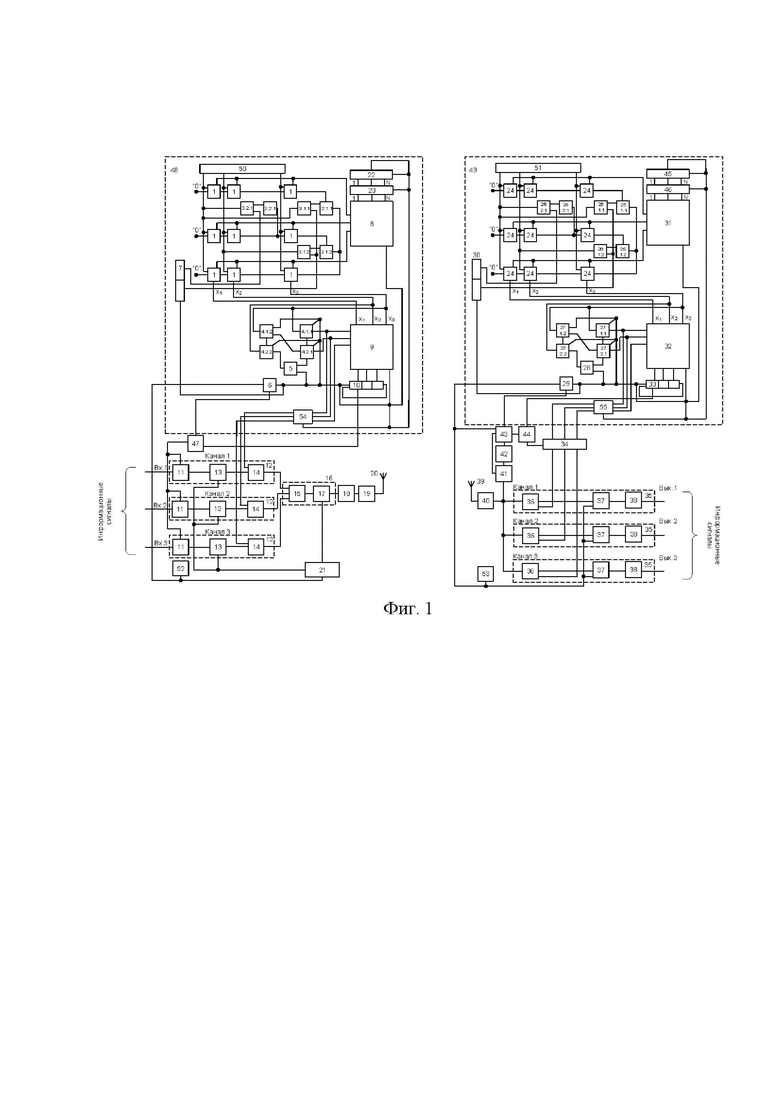

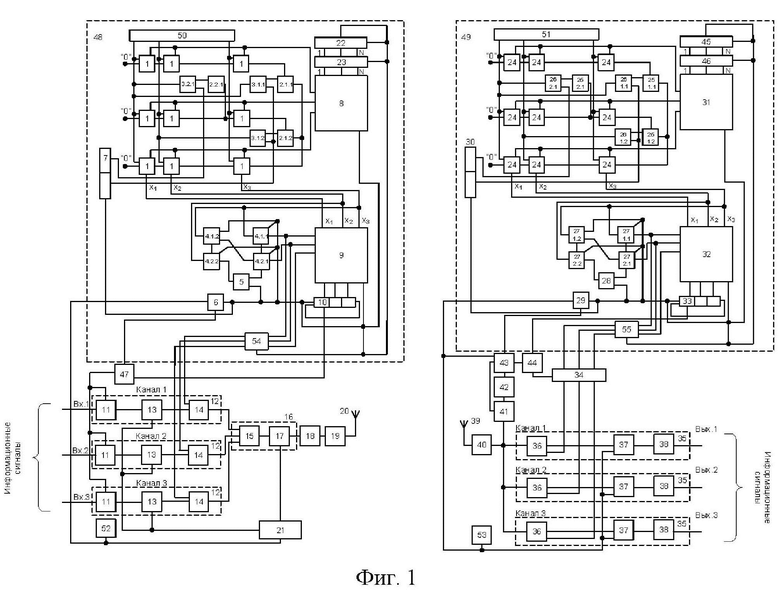

Для достижения названного технического результата в передающую аппаратуру базовой станции наиболее близкого технического решения (патент РФ № 2428795, опубл. 10.09.2011), состоящую из блока 48 формирования хаотических ансамблей ортогональных сигналов, состоящего из вычислителей 1, блоков 2.1.1, 2.1.2, 2.2.1 деления, блоков 3.1.1, 3.1.2, 3.2.1 элементов «И», операционных блоков 4.1.1,4.1.2,4.2.1,4.2.2, элемента 5 задержки, блока 6 синхронизации, первого разряда регистра 7 сдвига, второго разряда регистра 7 сдвига, блоков 8, 9 памяти, первого разряда кольцевого регистра 10 сдвига, второго разряда кольцевого регистра 10 сдвига, третьего разряда кольцевого регистра 10 сдвига, генератора 22 случайных положительных чисел и запоминающего устройства 23, а также состоящую из блока 47 элемента «И», каналов 12 передачи, состоящих из запоминающего устройства 11, блока 13 цифровой информации и модулятора 14, блока 16 формирования группового сигнала, состоящего из объединителя 15 входов и модулятора 17, блока 18 фазовой модуляции, усилителя 19 мощности, передающей антенны 20, генератора 21 сигналов синхронизации, блока 50 генерации сигналов управления итерационным процессом и генератора 52 тактовых импульсов, дополнительно введён блок 54 управляемого инвертирования, состоящий из блоков 56.2 – 56.4 переключения и блоков 59.2 – 59.4 инвертирования; причём генератор 22 случайных положительных чисел заменён на генератор 22 положительных и отрицательных псевдослучайных чисел (ПСЧ), состоящий из блока 56.1 переключения, генератора 57 положительных псевдослучайных чисел, генератора 58 отрицательных псевдослучайных чисел и блока 59.1 инвертирования, а также добавлены связи между первым выходом блока 6 синхронизации и вторым входом переключения выводов блока переключения генератора 22 положительных и отрицательных псевдослучайных чисел и входом переключения выводов блока переключения блока 54 управляемого инвертирования для переключения выводов в блоках 56.1 – 56.4 переключения; приёмную аппаратуру базовой станции, состоящую из блока 49 формирования копий ансамблей хаотических ортогональных сигналов, состоящего из вычислителей 24, блоков 25.1.1, 25.1.2, 25.2.1 деления, блоков 26.1.1, 26.1.2, 26.2.1 элементов «И», операционных блоков 27.1.1, 27.1.2, 27.2.1, 27.2.2, элемента 28 задержки, блока 29 синхронизации, первого разряда регистра 30 сдвига, второго разряда регистра 30 сдвига, блоков 31, 32 памяти, первого разряда кольцевого регистра 33 сдвига, второго разряда кольцевого регистра 33 сдвига, третьего разряда кольцевого регистра 33 сдвига, генератора 45 случайных положительных чисел и запоминающего устройства 46, а также состоящую из запоминающего устройства 34, каналов 35 связи, состоящих из блока 36 корреляционной обработки, блока 37 выделения информации и блока 38 приёма информации, приёмной антенны 39, блока 40 высокочастотной селекции, блока 41 обнаружения сигнала синхронизации, блока 42 поиска, генератора 43 копий сигналов синхронизации, блока 44 элемента «И», блока 51 генерации сигналов управления итерационным процессом и генератора 53 тактовых импульсов, дополнительно введён блок 55 управляемого инвертирования, состоящий из блоков 60.2 – 60.4 переключения и блоков 63.2 – 63.4 инвертирования; причём генератор 45 случайных положительных чисел заменён на генератор 45 положительных и отрицательных псевдослучайных чисел (ПСЧ), состоящий из блока 60.1 переключения, генератора 61 положительных псевдослучайных чисел, генератора 62 отрицательных псевдослучайных чисел и блока 63.1 инвертирования, а также добавлены связи между первым выходом блока 29 синхронизации и вторым входом переключения выводов блока переключения генератора45 положительных и отрицательных псевдослучайных чисел и входом переключения выводов блока переключения блока 55 управляемого инвертирования для переключения выводов в блоках 60.1 – 60.4 переключения.

Краткое описание чертежей

На фиг. 1 показана структурная схема системы передачи информации с использованием стохастических ортогональных кодов.

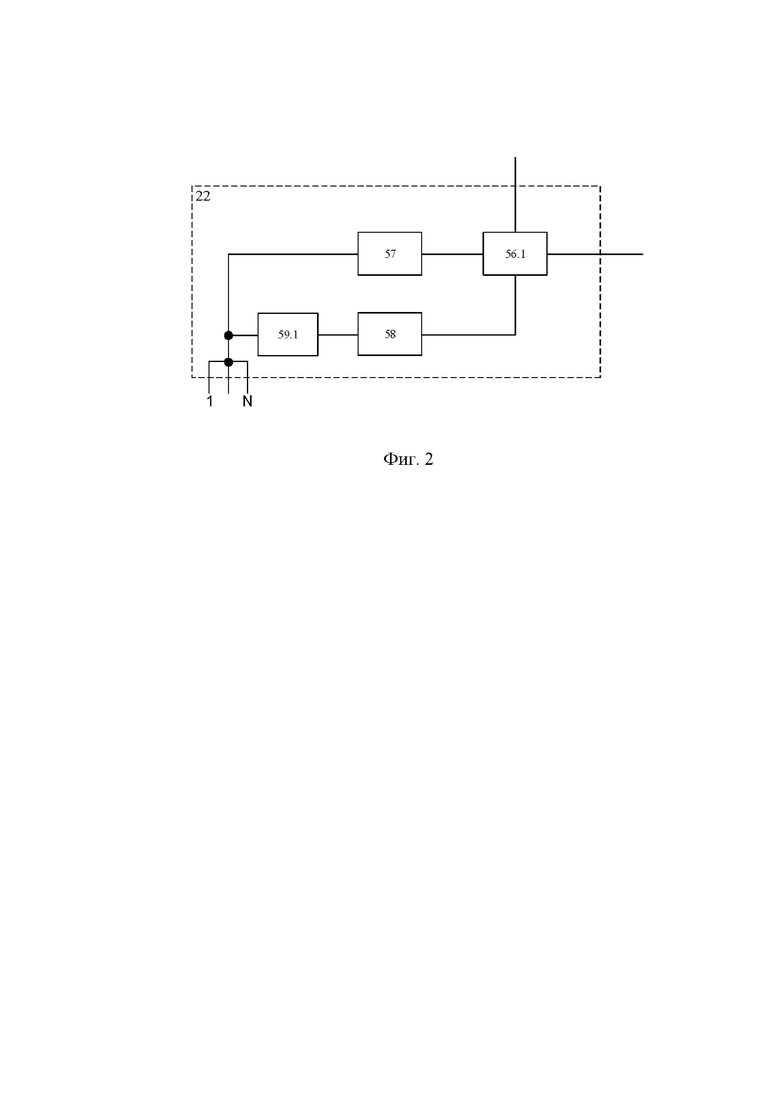

На фиг. 2 показана структурная схема генератора 22 положительных и отрицательных ПСЧ, позволяющего получать наборы положительных или отрицательных ПСЧ, а также позволяющего проводить операцию прямого инвертирования сгенерированных ПСЧ на передающей стороне.

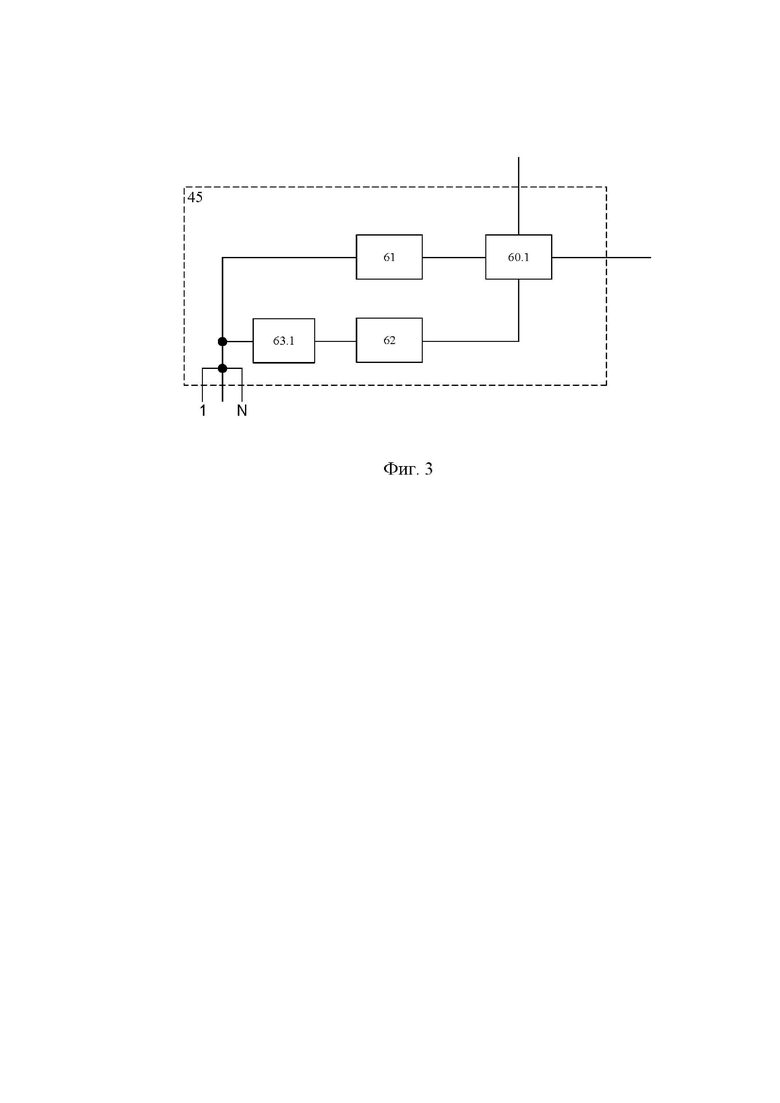

На фиг. 3 показана структурная схема генератора 45 положительных и отрицательных ПСЧ, позволяющего получать наборы положительных или отрицательных ПСЧ, а также позволяющего проводить операцию прямого инвертирования сгенерированных ПСЧ на приёмной стороне.

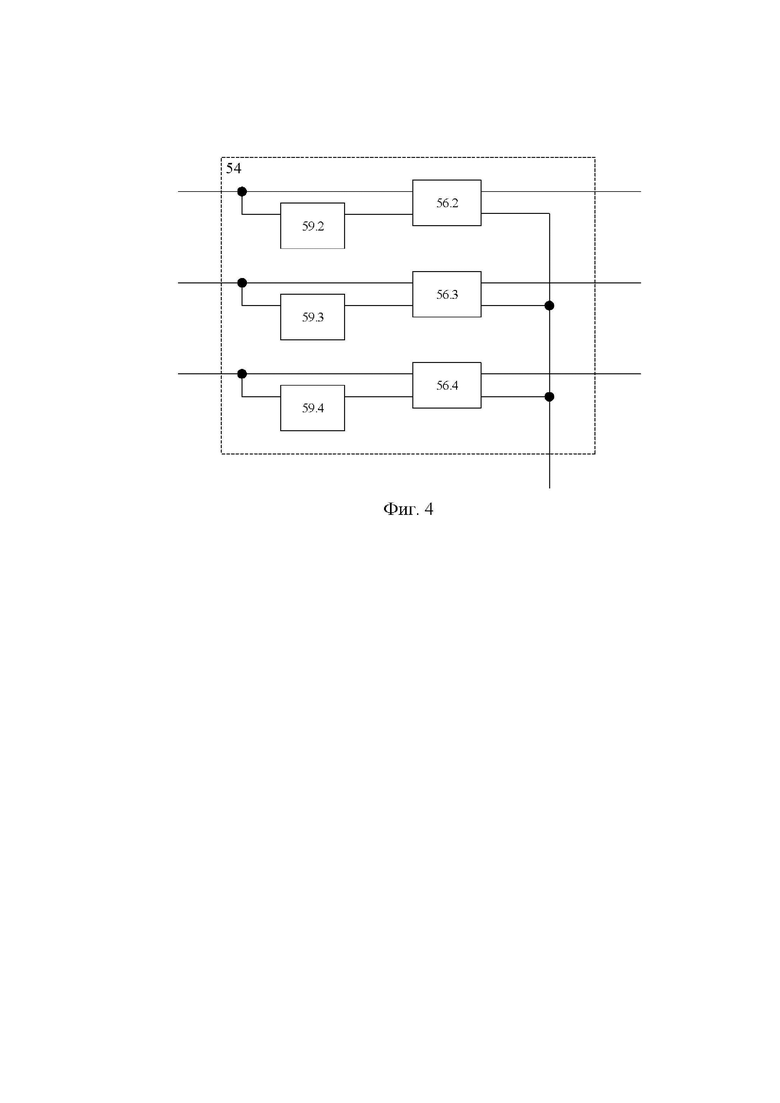

На фиг. 4 показана структурная схема блока 54 управляемого инвертирования, позволяющего провести обратное инвертирование полученных ансамблей стохастических ортогональных кодов при помощи блоков 59.2 – 59.4 инвертирования в том случае, если ПСЧ формировались при помощи генератора 58 отрицательных ПСЧ на передающей стороне.

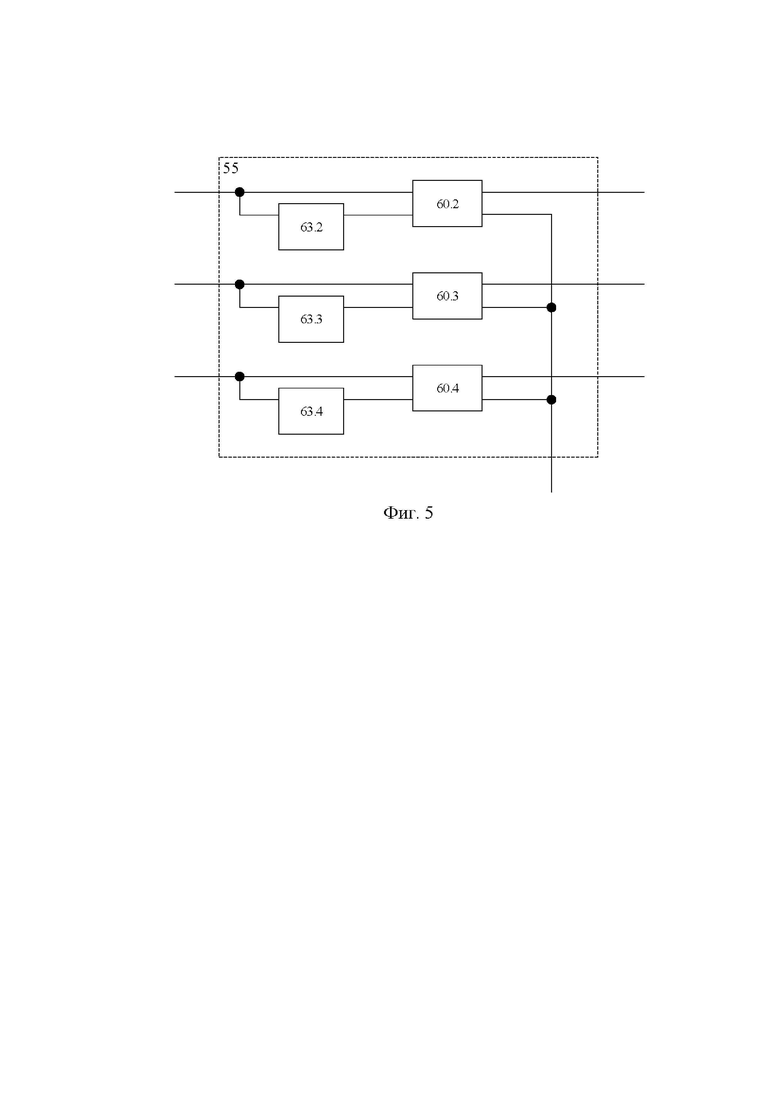

На фиг. 5 показана структурная схема блока 55 управляемого инвертирования, позволяющего провести обратное инвертирование полученных ансамблей стохастических ортогональных кодов при помощи блоков 63.2 – 63.4 инвертирования в том случае, если ПСЧ формировались при помощи генератора 62 отрицательных ПСЧ на приёмной стороне.

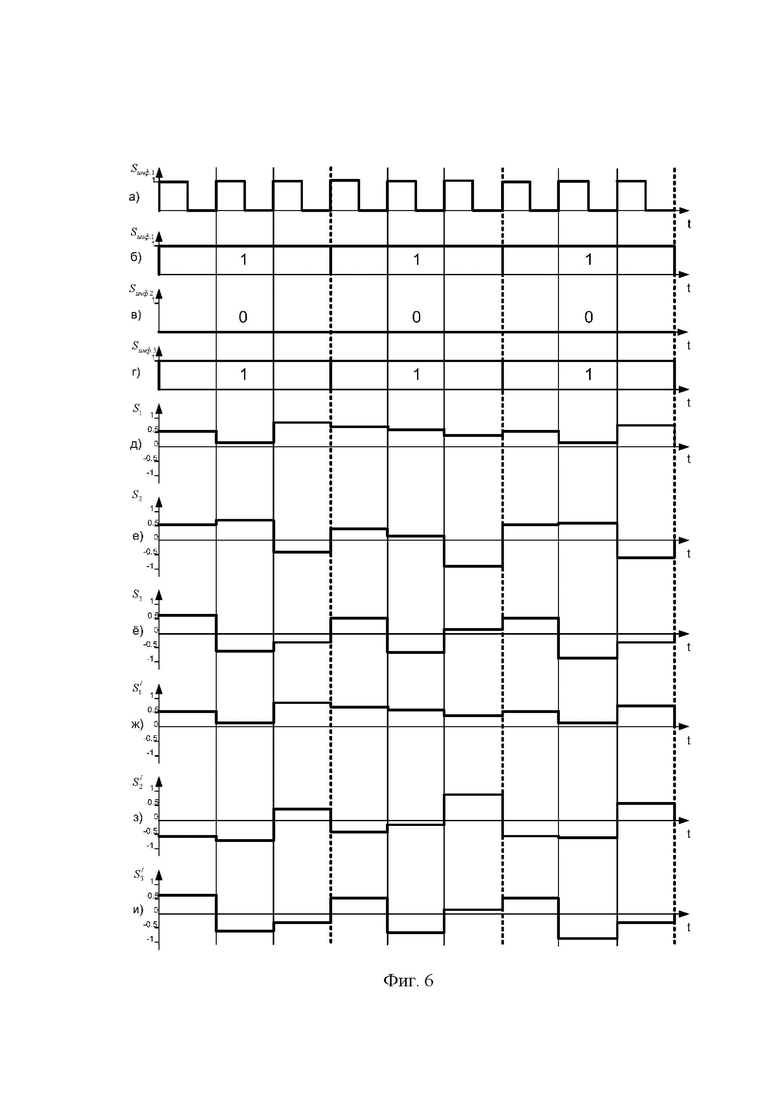

На фиг. 6 показаны временные диаграммы, поясняющие принцип функционирования системы передачи информации с использованием стохастических ортогональных кодов, где: а) сигналы генератора тактовых импульсов, б) сигнал, поступающий в первый канал связи  , в) сигнал, поступающий во второй канал связи

, в) сигнал, поступающий во второй канал связи  , г) сигнал, поступающий в третий канал связи

, г) сигнал, поступающий в третий канал связи  , д) ортогональный хаотический сигнал, поступающий в первый канал связи

, д) ортогональный хаотический сигнал, поступающий в первый канал связи  , е) ортогональный хаотический сигнал, поступающий во второй канал связи

, е) ортогональный хаотический сигнал, поступающий во второй канал связи  , ё) ортогональный хаотический сигнал, поступающий в третий канал связи

, ё) ортогональный хаотический сигнал, поступающий в третий канал связи  , ж) промодулированный информационный сигнал

, ж) промодулированный информационный сигнал на выходе первого канала связи, з) промодулированный информационный сигнал

на выходе первого канала связи, з) промодулированный информационный сигнал на выходе второго канала связи, и) промодулированный информационный сигнал

на выходе второго канала связи, и) промодулированный информационный сигнал  на выходе третьего канала связи.

на выходе третьего канала связи.

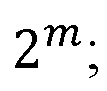

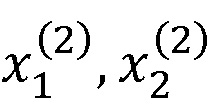

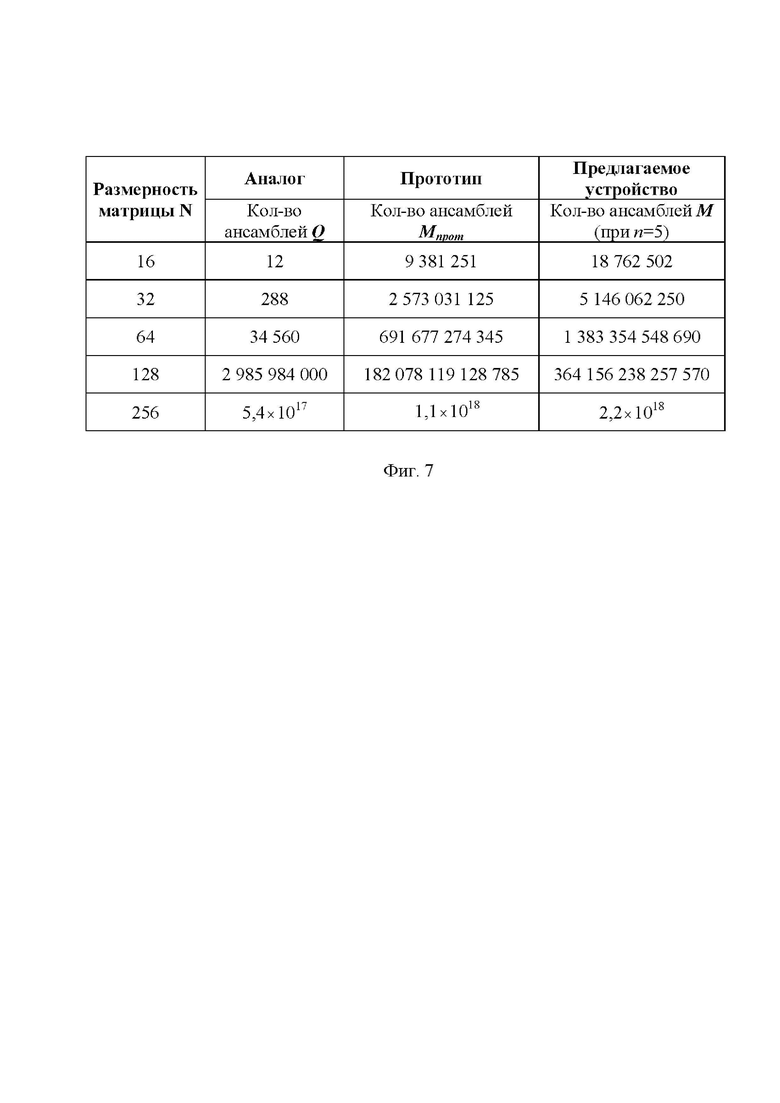

На фиг. 7 представлен сравнительный анализ количества ансамблей стохастических ортогональных кодов, формируемых предлагаемым устройством, прототипом и аналогом.

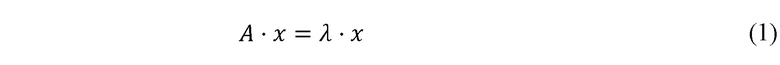

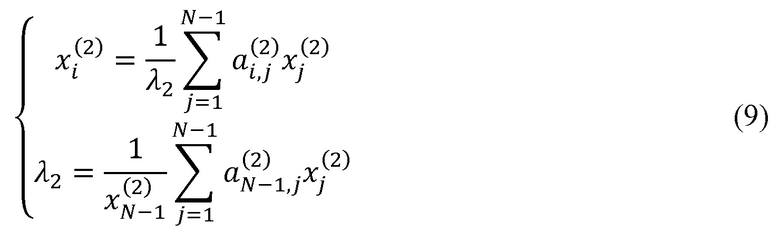

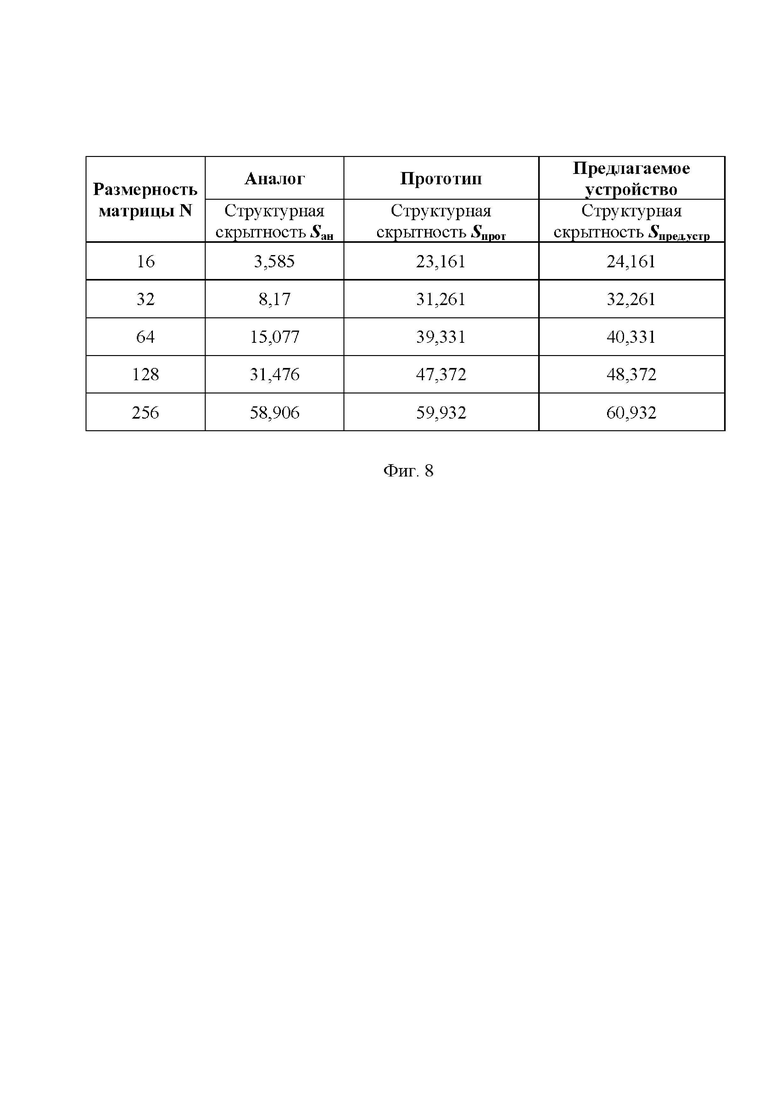

На фиг. 8 представлен сравнительный анализ структурной скрытности сигналов, формируемых предлагаемым устройством, прототипом и аналогом.

Осуществление изобретения

Процесс передачи информации в предлагаемой системе передачи информации с использованием ансамблей стохастических ортогональных кодов осуществляется в следующей последовательности: сначала с помощью вспомогательного синхронизирующего сложного сигнала передающая аппаратура базовой станции и приемная аппаратура каждой из  абонентских станций вводится в цикловую фазу. Затем посредством манипуляции вспомогательного сигнала синхронизации на каждый канал передается служебная информация (единый начальный блок для всех абонентских станций). После выполнения указанной процедуры начинается одновременная передача всем абонентам цифровой информации, при этом каждому биту информации фиксированного канала ставится в соответствие сложный сигнал, структура которого зависит от значений коэффициентов диагональной положительно определенной симметрической матрицы, которые формируются генератором положительных и отрицательных ПСЧ (ГПиО ПСЧ), причем расширение информационной последовательности происходит в случае, если информационный бит равен единице за счет использования ортогонального кода инверсной структуры, в случае если информационный бит равен нулю за счет использования ортогонального кода прямой структуры (см. Столингс В. Беспроводные линии связи и сети. : Пер. с англ. – М. : Издательский дом «Вильямс», 2003.- С.213).

абонентских станций вводится в цикловую фазу. Затем посредством манипуляции вспомогательного сигнала синхронизации на каждый канал передается служебная информация (единый начальный блок для всех абонентских станций). После выполнения указанной процедуры начинается одновременная передача всем абонентам цифровой информации, при этом каждому биту информации фиксированного канала ставится в соответствие сложный сигнал, структура которого зависит от значений коэффициентов диагональной положительно определенной симметрической матрицы, которые формируются генератором положительных и отрицательных ПСЧ (ГПиО ПСЧ), причем расширение информационной последовательности происходит в случае, если информационный бит равен единице за счет использования ортогонального кода инверсной структуры, в случае если информационный бит равен нулю за счет использования ортогонального кода прямой структуры (см. Столингс В. Беспроводные линии связи и сети. : Пер. с англ. – М. : Издательский дом «Вильямс», 2003.- С.213).

После передачи очередного информационного бита на передающей и приемной стороне производится синхронная смена коэффициентов диагональной положительно определенной симметрической матрицы, поступающих от идентичных ГПиО ПСЧ в приемной и передающей стороне, на основе которых происходит расчет сформированных стохастическим образом ансамблей стохастических ортогональных кодов, описываемых собственными векторами диагональных положительно определенных симметрических матриц. При этом кодовая последовательность, используемая на приемной стороне для корреляционной обработки, будет иметь структуру, совпадающую с кодовой последовательностью, излучаемой передатчиком, и, следовательно, может быть использована для обработки информационного потока, адресованного получателю цифровой информации.

Если для формирования коэффициентов диагональной положительно определенной симметрической матрицы использовались отрицательные ПСЧ, то они подвергаются процедуре прямого инвертирования, чтобы обеспечить корректную работу вычислителей. После вычисления ансамблей СОК, для получения которых использовались отрицательные ПСЧ, над ними осуществляется процедура обратного инвертирования для всего ансамбля. Корректность проведения процедур обеспечивается поступающим управляющим сигналом.

Рассмотрим для упрощения описания пример реализации системы передачи информации с использованием стохастических ортогональных кодов для  при

при

Устройство содержит в передающей аппаратуре (фиг. 1)  канала 12 передачи, каждый из которых состоит из запоминающего устройства 11, на первый вход которого поступают информационные сигналы, второй вход запоминающего устройства 11связан с выходом блока 47 элемента «И», второй вход которого подключен к второму выходу блока 6 синхронизации, причем первый вход блока элемента «И» 47 связан с первым управляющим выходом старшего разряда кольцевого регистра 10 сдвига, первый вход которого связан с первым выходом блока 6 синхронизации, который также подключен к входу регистра 7 сдвига, выходы которого, в свою очередь связаны с вторыми входами блоков 3.1.1, 3.1.2, 3.2.1 элемента «И», а выходы первого блока 8 памяти являются первыми входами вычислителей 1, причем на вторые входы вычислителей 1 с первого по N-й столбцов матрицы вычислителей (N - размерность матрицы коэффициентов) подается сигнал с первого по N-й выходов блока 50 генерации сигналов управления итерационным процессом соответственно, а третьи входы вычислителей первого столбца матрицы вычислителей 1 соединены с входом логического нуля блока формирования хаотических ансамблей ортогональных сигналов, с первых выходов вычислителей первого столбца матрицы вычислителей 1 сигналы поступают третьи входы вычислителей второго столбца матрицы вычислителей 1, с первых выходов которых сигналы поступают на третьи входы вычислителей третьего столбца матрицы вычислителей 1, сигнал с выхода второго вычислителя второго столбца матрицы вычислителей поступает также на первый вход блока 2.2.1 деления, сигналы с первых выходов первого и второго вычислителей третьего столбца матрицы вычислителей 1 поступают на первые входы блоков 2.1.1 и 2.1.2 деления, сигнал с выхода третьего вычислителя третьего столбца матрицы вычислителей 1 поступает на вторые входы блоков 2.1.1 и 2.1.2 деления, выходы блоков 2.1.1, 2.1.2, 2.2.1 деления соединены с первыми входами блоков 3.1.1, 3.1.2, 3.2.1 элемента «И», с выхода которых сигналы поступают на вторые входы вычислителей первого и второго столбцов матрицы вычислителей 1, вторые выходы третьих вычислителей первого, второго и третьего столбца матрицы вычислителей 1 подключены к информационным с 1-го по N-й входам второго блока 9 памяти;

канала 12 передачи, каждый из которых состоит из запоминающего устройства 11, на первый вход которого поступают информационные сигналы, второй вход запоминающего устройства 11связан с выходом блока 47 элемента «И», второй вход которого подключен к второму выходу блока 6 синхронизации, причем первый вход блока элемента «И» 47 связан с первым управляющим выходом старшего разряда кольцевого регистра 10 сдвига, первый вход которого связан с первым выходом блока 6 синхронизации, который также подключен к входу регистра 7 сдвига, выходы которого, в свою очередь связаны с вторыми входами блоков 3.1.1, 3.1.2, 3.2.1 элемента «И», а выходы первого блока 8 памяти являются первыми входами вычислителей 1, причем на вторые входы вычислителей 1 с первого по N-й столбцов матрицы вычислителей (N - размерность матрицы коэффициентов) подается сигнал с первого по N-й выходов блока 50 генерации сигналов управления итерационным процессом соответственно, а третьи входы вычислителей первого столбца матрицы вычислителей 1 соединены с входом логического нуля блока формирования хаотических ансамблей ортогональных сигналов, с первых выходов вычислителей первого столбца матрицы вычислителей 1 сигналы поступают третьи входы вычислителей второго столбца матрицы вычислителей 1, с первых выходов которых сигналы поступают на третьи входы вычислителей третьего столбца матрицы вычислителей 1, сигнал с выхода второго вычислителя второго столбца матрицы вычислителей поступает также на первый вход блока 2.2.1 деления, сигналы с первых выходов первого и второго вычислителей третьего столбца матрицы вычислителей 1 поступают на первые входы блоков 2.1.1 и 2.1.2 деления, сигнал с выхода третьего вычислителя третьего столбца матрицы вычислителей 1 поступает на вторые входы блоков 2.1.1 и 2.1.2 деления, выходы блоков 2.1.1, 2.1.2, 2.2.1 деления соединены с первыми входами блоков 3.1.1, 3.1.2, 3.2.1 элемента «И», с выхода которых сигналы поступают на вторые входы вычислителей первого и второго столбцов матрицы вычислителей 1, вторые выходы третьих вычислителей первого, второго и третьего столбца матрицы вычислителей 1 подключены к информационным с 1-го по N-й входам второго блока 9 памяти;

первый выход второго блока 9 памяти подключен к первому входу операционного блока 4.1.1, а также подключен к первому входу блока 54 управляемого инвертирования, первый выход которого выводит элементы первого собственного вектора ортогонального базиса матрицы А вида (4). Второй выход второго блока 9 памяти подключен к первому входу операционного блока 4.2.1, а также подключен к второму входу блока 54 управляемого инвертирования, второй выход которого выводит элементы второго собственного вектора ортогонального базиса матрицы А вида (4). Третий выход второго блока 9 памяти подключен к третьему входу блока 54 управляемого инвертирования, третий выход которого выводит элементы третьего собственного вектора ортогонального базиса матрицы А вида (4);

первый вход блока 54 управляемого инвертирования (фиг. 4) соединён с первым входом блока 56.2 переключения, второй вход блока 54 управляемого инвертирования соединён с первым входом блока 56.3 переключения, третий вход блока 54 управляемого инвертирования соединён с первым входом блока 56.4 переключения, вход переключения выводов блока переключения блока 54 управляемого инвертирования подключен ко вторым входам блоков 56.2, 56.3, 56.4 переключения, второй выход блока 56.2 переключения подключен к входу блока 59.2 инвертирования, второй выход блока 56.3 переключения подключен к входу блока 59.3 инвертирования, второй выход блока 56.4 переключения подключен к входу блока 59.4 инвертирования. Первый выход блока 56.2 переключения и выход блока 59.2 инвертирования соединены с первым выходом блока 54 управляемого инвертирования, первый выход блока 56.3 переключения и выход блока 59.3 инвертирования соединены с вторым выходом блока 54 управляемого инвертирования, первый выход блока 56.4 переключения и выход блока 59.4 инвертирования соединены с третьим выходом блока 54 управляемого инвертирования;

первый выход операционного блока 4.1.1 подключен к третьему входу операционного блока 4.2.1, второй выход операционного блока 4.1.1 подключен к N-му входу второго блока 9 памяти, второй выход операционного блока 4.2.1 подключен к первому входу операционного блока 4.1.2, первый выход операционного блока 4.2.1 подключен к первому входу элемента 5 задержки, второй вход которого связан с первым выходом блока 6 синхронизации, а выход элемента 5 задержки подключён к первому входу операционного блока 4.2.2, выход операционного блока 4.2.2 подключен к (N-1)-му входу блока 9 памяти, первый выход операционного блока 4.1.2 подключен к третьему входу операционного блока 4.2.2, второй выход операционного блока 4.1.2 подключён к N-му входу блока 9 памяти, вторые входы операционных блоков 4.1.1, 4.1.2, 4.2.1, 4.2.2 связаны с первым выходом блока 6 синхронизации, при этом синхроимпульсы с первого выхода блока 6 синхронизации одновременно поступают на первый вход кольцевого регистра 10 сдвига, управляющие входы блоков 8 и 9 памяти, первый управляющий вход и второй вход переключения выводов блока переключения генератора 22 положительных и отрицательных псевдослучайных чисел, вход переключения выводов блока переключения блока 54 управляемого инвертирования и N+1-й вход запоминающего устройства 23, информационные входы которого с 1-го по N-й подключены к информационным с 1-го по N-й выходам генератора 22 положительных и отрицательных ПСЧ, а информационные с 1-го по N-е выходы запоминающего устройства 23 подключены к информационным входам блока 8 памяти;

первый управляющий вход генератора 22 положительных и отрицательных ПСЧ (фиг. 2) подключен к первому входу блока 56.1 переключения, первый выход которого подключен к входу генератора 57 положительных ПСЧ, второй вход переключения выводов блока переключения генератора 22 положительных и отрицательных ПСЧ подключен к второму входу блока 56.1 переключения, второй выход которого подключен к входу генератора 58 отрицательных ПСЧ, выход которого соединен с входом блока 59.1 инвертирования, выход генератора 57 положительных ПСЧ и выход блока 59.1 инвертирования соединены с 1-го по N-й выходами генератора 22 положительных и отрицательных ПСЧ;

при этом первый управляющий выход кольцевого регистра 10 сдвига подключен к первому входу блока 47 элемента «И», а вторые с 1-го по N-й управляющие выходы связаны с 1-го по N-й управляющими входами второго блока 9 памяти, третий выход кольцевого регистра 10 сдвига подключен к второму входу кольцевого регистра 10 сдвига, причем выход запоминающего устройства 11каждого из каналов 12 передачи подключен к первому входу соответствующего блока 13 цифровой информации, второй вход которого связан с вторым выходом генератора 21 сигналов синхронизации, выход блока 13 цифровой информации подключен к первому входу модулятора 14 каждого из каналов 12 передачи, а вторые входы модуляторов 14 с первого по N-й каналов передачи связаны с первого по N-й выходами блока 54 управляемого инвертирования, выход каждого с первого по N-й модулятора 14 является выходом каждого с первого по N-й канала 12 передачи и подключен к входам с первого по N-й объединителя 15 входов блока 16 формирования группового сигнала, выход объединителя 15 подключен к первому входу модулятора 17 блока 16 формирования группового сигнала, второй вход которого соединен с первым выходом генератора 21 сигналов синхронизации, а выход модулятора 17 является выходом блока 16 формирования группового сигнала, который подключен к входу блока 18 фазовой модуляции, выход которого подключен к входу усилителя 19 мощности, выход которого подключен к передающей антенне 20, причем вход генератора 21 сигналов синхронизации подключен к выходу генератора тактовых импульсов 52, который параллельно подключен к тактовому входу блока 6 синхронизации;

приемной аппаратуре (фиг. 1) блок 40 высокочастотной селекции, вход которого соединен с приемной антенной 39, а выход подключен к первому входу блока 41 обнаружения сигнала синхронизации и первым входам блоков 36 корреляционной обработки каждого из  каналов 35 связи, причем выход блока 36 корреляционной обработки подключен к первому входу блока 37 выделения информации, второй вход которого связан с выходом генератора 53 тактовых импульсов, причем выход блока 41 обнаружения сигнала синхронизации подключен к входу блока 42 поиска, выход которого соединен с первым входом генератора 43 копий сигналов синхронизации, первый выход которого подключен к второму входу блока 41 обнаружения сигнала синхронизации, второй выход генератора 43 копий сигналов синхронизации подключен к первому входу блока 29 синхронизации, выход которого связан с управляющим входом регистра 30 сдвига, выходы которого являются вторыми входами соответствующих блоков 26.1.1, 26.1.2, 26.2.1 элемента «И», а третий выход генератора 43 копий сигналов синхронизации соединен с первым входом блока 44 элемента «И», выход которого подключен к первому управляющему входу запоминающего устройства 34, вторые информационные с 1-го по N-й входы которого подключены к информационным с 1-го по N-й выходам блока 55 управляемого инвертирования, причем выход блока 29 синхронизации подключен к первому управляющему входу первого блока 31 памяти, информационные с 1-го по N-й выходы которого являются первыми входами вычислителей 24, причем на вторые входывычислителей 24 с первого по N-й столбцов матрицы вычислителей (N - размерность матрицы коэффициентов) подается сигнал с первого по N-й выходы блока 51 генерации сигналов управления итерационным процессом соответственно, который полностью идентичен сигналу, вырабатываемому блоком 50 генерации сигналов управления итерационным процессом на передающей стороне, а третьи входы вычислителей 24 первого столбца матрицы вычислителей соединены с входом логического нуля блока формирования копий хаотических ансамблей ортогональных сигналов, с первых выходов вычислителей первого столбца матрицы вычислителей 24 сигналы поступают на третьи входы вычислителей второго столбца матрицы вычислителей 24, с выходов которых сигналы поступают на третьи входы вычислителей третьего столбца матрицы вычислителей 24, сигнал с выхода второго вычислителя второго столбца матрицы вычислителей 24 также поступает на вход блока 25.2.1 деления, сигналы с первых выходов первого и второго вычислителей третьего столбца матрицы вычислителей 24 поступают на первые входы блоков 25.1.1 и 25.1.2 деления, сигнал с первого выхода третьего вычислителя третьего столбца матрицы вычислителей 24 поступает на вторые входы блоков 25.1.1 и 25.1.2 деления, выходы блоков 25.1.1, 25.1.2, 25.2.1 деления соединены с первыми входами соответствующих блоков 26.1.1, 26.1.2, 26.2.1 элемента «И», с выхода которых сигналы поступают на вторые входы вычислителей первого и второго столбцов матрицы вычислителей 24, вторые выходы третьих вычислителей первого, второго и третьего столбца матрицы вычислителей 24 подключены к информационным с 1-го по N-й входам второго блока 32 памяти;

каналов 35 связи, причем выход блока 36 корреляционной обработки подключен к первому входу блока 37 выделения информации, второй вход которого связан с выходом генератора 53 тактовых импульсов, причем выход блока 41 обнаружения сигнала синхронизации подключен к входу блока 42 поиска, выход которого соединен с первым входом генератора 43 копий сигналов синхронизации, первый выход которого подключен к второму входу блока 41 обнаружения сигнала синхронизации, второй выход генератора 43 копий сигналов синхронизации подключен к первому входу блока 29 синхронизации, выход которого связан с управляющим входом регистра 30 сдвига, выходы которого являются вторыми входами соответствующих блоков 26.1.1, 26.1.2, 26.2.1 элемента «И», а третий выход генератора 43 копий сигналов синхронизации соединен с первым входом блока 44 элемента «И», выход которого подключен к первому управляющему входу запоминающего устройства 34, вторые информационные с 1-го по N-й входы которого подключены к информационным с 1-го по N-й выходам блока 55 управляемого инвертирования, причем выход блока 29 синхронизации подключен к первому управляющему входу первого блока 31 памяти, информационные с 1-го по N-й выходы которого являются первыми входами вычислителей 24, причем на вторые входывычислителей 24 с первого по N-й столбцов матрицы вычислителей (N - размерность матрицы коэффициентов) подается сигнал с первого по N-й выходы блока 51 генерации сигналов управления итерационным процессом соответственно, который полностью идентичен сигналу, вырабатываемому блоком 50 генерации сигналов управления итерационным процессом на передающей стороне, а третьи входы вычислителей 24 первого столбца матрицы вычислителей соединены с входом логического нуля блока формирования копий хаотических ансамблей ортогональных сигналов, с первых выходов вычислителей первого столбца матрицы вычислителей 24 сигналы поступают на третьи входы вычислителей второго столбца матрицы вычислителей 24, с выходов которых сигналы поступают на третьи входы вычислителей третьего столбца матрицы вычислителей 24, сигнал с выхода второго вычислителя второго столбца матрицы вычислителей 24 также поступает на вход блока 25.2.1 деления, сигналы с первых выходов первого и второго вычислителей третьего столбца матрицы вычислителей 24 поступают на первые входы блоков 25.1.1 и 25.1.2 деления, сигнал с первого выхода третьего вычислителя третьего столбца матрицы вычислителей 24 поступает на вторые входы блоков 25.1.1 и 25.1.2 деления, выходы блоков 25.1.1, 25.1.2, 25.2.1 деления соединены с первыми входами соответствующих блоков 26.1.1, 26.1.2, 26.2.1 элемента «И», с выхода которых сигналы поступают на вторые входы вычислителей первого и второго столбцов матрицы вычислителей 24, вторые выходы третьих вычислителей первого, второго и третьего столбца матрицы вычислителей 24 подключены к информационным с 1-го по N-й входам второго блока 32 памяти;

первый выход второго блока 32 памяти подключен к первому входу операционного блока 27.1.1, а также подключен к первому входу блока 55 управляемого инвертирования, первый выход которого выводит элементы первого собственного вектора ортогонального базиса матрицы А вида (4), второй выход второго блока 32 памяти подключен к первому входу операционного блока 27.2.1, а также подключен к второму входу блока 55 управляемого инвертирования, второй выход которого выводит элементы второго собственного вектора ортогонального базиса матрицы А вида (4), третий выход второго блока 32 памяти подключен к третьему входу блока 55 управляемого инвертирования, третий выход которого выводит элементы третьего собственного вектора ортогонального базиса матрицы А вида (4);

первый вход блока 55 управляемого инвертирования (фиг. 5) соединён с первым входом блока 60.2 переключения, второй вход блока 55 управляемого инвертирования соединён с первым входом блока 60.3 переключения, третий вход блока 55 управляемого инвертирования соединён с первым входом блока 60.4 переключения, вход переключения выводов блока переключения блока 55 управляемого инвертирования подключен ко вторым входам блоков 60.2, 60.3, 60.4 переключения, второй выход блока 60.2 переключения подключен к входу блока 63.2 инвертирования, второй выход блока 60.3 переключения подключен к входу блока 63.3 инвертирования, второй выход блока 60.4 переключения подключен к входу блока 63.4 инвертирования. Первый выход блока 60.2 переключения и выход блока 63.2 инвертирования соединены с первым выходом блока 55 управляемого инвертирования, первый выход блока 60.3 переключения и выход блока 63.3 инвертирования соединены с вторым выходом блока 55 управляемого инвертирования, первый выход блока 60.4 переключения и выход блока 63.4 инвертирования соединены с третьим выходом блока 55 управляемого инвертирования;

первый выход операционного блока 27.1.1 подключен к третьему входу операционного блока 27.2.1, второй выход операционного блока 27.1.1 подключен к N-му входу второго блока 32 памяти, второй выход операционного блока 27.2.1 подключен к первому входу операционного блока 27.1.2, первый выход операционного блока 27.2.1 подключен к первому входу элемента 28 задержки, второй вход которого связан с выходом блока 29 синхронизации, выход элемента 28 задержки подключён к первому входу операционного блока 27.2.2, выход операционного блока 27.2.2 подключен к (N-1)-у входу блока 32 памяти, первый выход операционного блока 27.1.2 подключен к третьему входу операционного блока 27.2.2, второй выход операционного блока 27.1.2 подключён к N-у входу блока 32 памяти, вторые входы операционных блоков 27.1.1, 27.1.2, 27.2.1, 27.2.2 связаны с выходом блока 29 синхронизации, при этом синхроимпульсы с выхода блока 29 синхронизации одновременно поступают на первый вход кольцевого регистра 33 сдвига, на управляющие входы блоков 31 и 32 памяти, первый управляющий вход и второй вход переключения выводов блока переключения генератора 45 положительных и отрицательных ПСЧ, вход переключения выводов блока переключения блока 55 управляемого инвертирования и N+1-й вход запоминающего устройства 46, информационные входы которого с 1-го по N-й подключены к информационным с 1-го по N-й выходам генератора 45 положительных и отрицательных ПСЧ, а информационные выходы запоминающего устройства 46 с 1-го по N-й подключены к информационным с 1-го по N-й входам блока 31 памяти;

первый управляющий вход генератора 45 положительных и отрицательных ПСЧ (фиг. 3) подключен к первому входу блока 60.1 переключения, первый выход которого подключен к входу генератора 61 положительных ПСЧ, второй вход переключения выводов блока переключения генератора 45 положительных и отрицательных ПСЧ подключен к второму входу блока 60.1 переключения, второй выход которого подключен к входу генератора 62 отрицательных ПСЧ, выход которого соединен с входом блока 63.1 инвертирования, выход генератора 61 положительных ПСЧ и выход блока 63.1 инвертирования соединены с N выходами генератора 45 положительных и отрицательных ПСЧ;

при этом первый управляющий выход кольцевого регистра 33 сдвига подключен к второму входу блока 44 элемента «И», выход которого связан с первым управляющим входом запоминающего устройства 34, выходы которого с 1 по N-й подключены к вторым входам с 1 по N-й блоков 36 корреляционной обработки каждого из каналов 35 связи, вторые управляющие выходы кольцевого регистра 33 сдвига с 1-го по N-й связаны с 1-го по N-й управляющими входами блока 32 памяти, третий выход кольцевого регистра 33 сдвига подключен к второму входу кольцевого регистра 33 сдвига, причем выход каждого из блоков 36 корреляционной обработки подключен к первому входу блока 37 выделения информации, второй вход которого подключен к выходу генератора 53 тактовых импульсов, который параллельно подключен к второму тактовому входу блока 29 синхронизации и второму тактовому входу генератору 43 копий сигналов синхронизации, при этом выход блока 37 выделения информации связан с входом блока 38 приема информации, выход которого является выходом каждого канала 35 связи и выводит принятые информационные сигналы.

Устройство работает следующим образом. Информационные сигналы поступают в запоминающее устройство 11 каждого из каналов 12 передачи и хранятся в нем до момента получения управляющего сигнала с блока 47 элемента «И», свидетельствующего о завершении этапа формирования стохастическим образом ортогональной системы сигналов, описываемых собственными векторами диагональных положительно определенных симметрических матриц размерностью Nв блоке 48 формирования хаотических ансамблей ортогональных сигналов. Затем информационный бит каждого из каналов 12 передачи через блок 13 цифровой информации, на который поступают сигналы синхронизации с генератора 21 сигналов синхронизации, подается в модулятор 14, где он модулируется расширяющей последовательностью, поступающей с блока 54 управляемого инвертирования блока 48 формирования хаотических ансамблей ортогональных сигналов. Сигналы, снимаемые с выхода модулятора 14 каждого канала 12 передачи, одновременно подаются в объединитель входов 15 блока 16 формирования группового сигнала, где после их объединения и наложения в модуляторе 17 сигнала синхронизации, поступающего с выхода генератора 21 сигналов синхронизации, на вход которого поступают импульсы с генератора 52 тактовых импульсов, происходит формирование группового сигнала, спектр которого после переноса в область несущей частоты в блоке 18 фазовой модуляции и усилителе 19 мощности через передающую антенну 20 излучается в эфир. На приемной стороне поступающий сигнал принимается приемной антенной 39 и подвергается предварительной обработке в блоке 40 высокочастотной селекции. С выхода блока 40 высокочастотной селекции сигнал одновременно подается в блок 41 обнаружения сигнала синхронизации и блоки 36 корреляционной обработки каждого канала 35 связи. При этом блок 41 обнаружения сигнала синхронизации совместно с блоком 42 поиска вводят в синхронизм генератор 43 копии сигналов синхронизации. После чего с генератора 43 копий сигналов синхронизации подается управляющий сигнал на блок 29 синхронизации блока 49 формирования копий ансамблей хаотических ортогональных сигналов, свидетельствующий о начале формирования копий хаотических ансамблей ортогональных сигналов блоком 49 формирования копий хаотических ансамблей ортогональных сигналов. Подача управляющего сигнала на блок 44 элемента «И» с кольцевого регистра 33 сдвига блока 49 формирования копий хаотических ансамблей ортогональных сигналов говорит о завершении этапа формирования стохастических ортогональных кодов и записи их в запоминающее устройство 34. После чего под воздействием управляющего сигнала с блока 44 элемента «И» копии ансамблей стохастических ортогональных кодов подаются с запоминающего устройства 34 на блоки 36 корреляционной обработки каждого из каналов 35 связи, и пройдя через первый вход блока 37 выделения информации, на второй вход которого подается копия сигнала синхронизации с генератора 53 тактовых импульсов, направляется на вход блока 38 приема информации.

При этом на передающей стороне блок 48 формирования хаотических ансамблей ортогональных сигналов функционирует следующим образом: при подаче питания в систему передачи информации активируется генератор 52 тактовых импульсов, импульсы с выхода которого поступают на вход блока 6 синхронизации блока 48 формирования хаотических ансамблей ортогональных сигналов и активируют его, с первого выхода блока 6 синхронизации подается управляющий сигнал на первый управляющий вход генератора 22 положительных и отрицательных ПСЧ и запоминающее устройство 23, в результате чего происходит генерация и запись случайных коэффициентов матрицы А в блок 8 памяти.

Генерация псевдослучайных коэффициентов матрицы А происходит следующим образом. Сигнал с первого выхода блока 6 синхронизации подаётся на первый вход блока 56.1 переключения генератора 22 положительных и отрицательных ПСЧ, положение выхода которого определяет сигнал управления U, поступающий через второй вход генератора 22 положительных и отрицательных ПСЧ на второй вход блока 56.1 переключения. При первом проходе сигнал с первого выхода блока 56.1 переключения подаётся на вход генератора 57 положительных ПСЧ, с выхода которого поступают положительные ПСЧ. Если же сигнал подаётся с второго выхода блока 56.1 переключения на вход генератора 58 отрицательных ПСЧ, например, при втором проходе, то сформированные отрицательные ПСЧ с выхода генератора 58 отрицательных ПСЧ поступают на вход блока 59.1 инвертирования. Сигнал с выхода генератора 57 положительных ПСЧ или выхода блока 59.1 инвертирования поступает на выход генератора 22 положительных и отрицательных ПСЧ, который передает ПСЧ на входы запоминающего устройства 23.

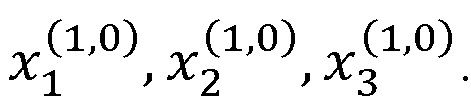

После этого начинается вычисление 1-го собственного значения и соответствующего ему собственного вектора, которое осуществляется в течение времени нахождения «1» в 1-м разряде регистра 7 сдвига, поэтому период поступления тактовых импульсов на тактовый вход регистра 7 сдвига равен времени сходимости итерационного процесса и вычисления оставшейся части компонент собственного вектора.

В течение первого периода работы «1» с выхода первого разряда регистра 7 сдвига поступает на вторые входы блоков 3.1.1 и 3.1.2 элементов «И». На второй вход блока 3.2.1 элемента «И» поступает «0» с выхода второго разряда первого регистра 7 сдвига, в результате на выходе блока 3.2.1 элемента «И» формируется «0».

С поступлением последовательности синхроимпульсов с блока 6 синхронизации коэффициенты, находящиеся в первом блоке 8 памяти, последовательно поступают на первые входы вычислителей 1 и запоминаются в них. Вычислители 1 также выполняют функцию накопления каждый раз в случае подачи на их вход нового слагаемого.

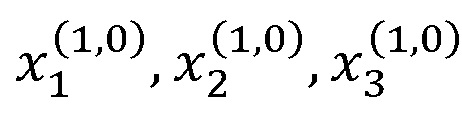

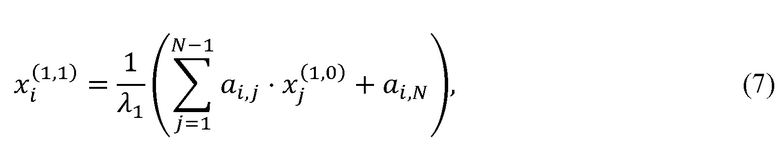

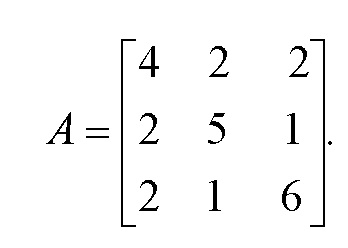

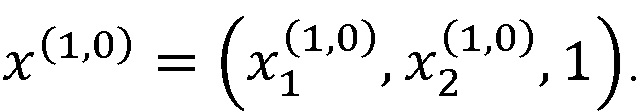

На вторые входы вычислителей 1, кроме последнего столбца матрицы вычислителей, подаются произвольные сигналы  с блока 50 генерации сигналов управления итерационным процессом.

с блока 50 генерации сигналов управления итерационным процессом.

На вторых входах вычислителей 1 последнего столбца матрицы вычислителей присутствует сигнал «1».

Следовательно, для реализации итерационной процедуры отыскания собственного числа  матрицы А в качестве начального приближения выбирается вектор

матрицы А в качестве начального приближения выбирается вектор

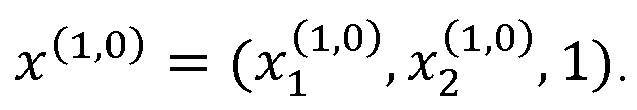

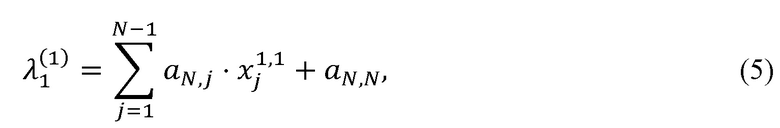

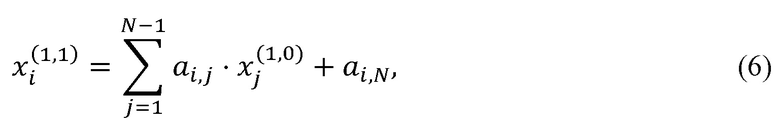

На выходе последнего вычислителя 1 последней строки матрицы при этом образуется сигнал (соотношение (5)), который является первым приближением собственного числа  .

.

На выходе последнего вычислителя 1 1-й строки (i = 1…n-1) образуется сигнал (соотношение (6)):

где

Этот сигнал является i-м компонентом первого ненормированного приближения первого собственного вектора матрицы коэффициентов А

Нормирование первого приближения первого вектора осуществляется путем деления всех его компонентов на величину последнего компонента  . Так как в результате нормирования последняя компонента равна 1, то ее деление не производится и «1» поступает на вторые входы последнего столбца матрицы вычислителей 1. Нормирование остальных компонент осуществляется при помощи блоков 2.1.1 и 2.1.2 путем деления компонент на величину последней компоненты

. Так как в результате нормирования последняя компонента равна 1, то ее деление не производится и «1» поступает на вторые входы последнего столбца матрицы вычислителей 1. Нормирование остальных компонент осуществляется при помощи блоков 2.1.1 и 2.1.2 путем деления компонент на величину последней компоненты  . Сигнал с выхода блока 2.1.1 деления через первый вход блока 3.1.1 поступает на вторые входы второго и третьего вычислителей первого столбца матрицы вычислителей 1. Сигнал с выхода блока деления 2.1.2 через первый вход блока 3.1.2 поступает на второй вход третьего вычислителя второго столбца матрицы вычислителей 1.

. Сигнал с выхода блока 2.1.1 деления через первый вход блока 3.1.1 поступает на вторые входы второго и третьего вычислителей первого столбца матрицы вычислителей 1. Сигнал с выхода блока деления 2.1.2 через первый вход блока 3.1.2 поступает на второй вход третьего вычислителя второго столбца матрицы вычислителей 1.

Таким образом, в соответствии с соотношением (7):

где  после окончания первой итерации на вторых выходахтретьих вычислителей первого, второго и третьего столбца матрицы вычислителей 1 присутствуют сигналы, соответствующие компонентам первого нормированного приближения первого собственного вектора:

после окончания первой итерации на вторых выходахтретьих вычислителей первого, второго и третьего столбца матрицы вычислителей 1 присутствуют сигналы, соответствующие компонентам первого нормированного приближения первого собственного вектора:

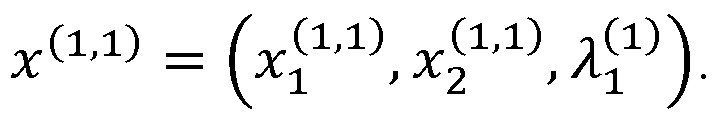

Затем итерационный процесс повторяется и после окончания второй итерации на вторых выходах третьих вычислителей первого, второго и третьего столбца матрицы вычислителей 1 присутствуют сигналы, соответствующие компонентам второго нормированного приближения первого собственного вектора:

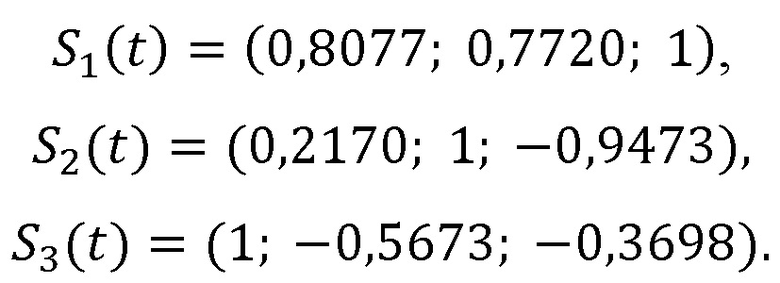

Повторение итераций будет осуществляться до полной сходимости итерационного процесса. В результате на вторых выходах третьих вычислителей первого, второго и третьего столбца матрицы вычислителей 1 присутствуют сигналы, соответствующие компонентам нормированного первого собственного вектора:

а на выходе третьего вычислителя третьего столбца матрицы вычислителей 1 присутствует сигнал, соответствующий собственному значению  .

.

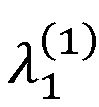

Таким образом, для матрицы А система уравнений, решаемая методом итерации, в соответствии с соотношениями (5) и (7) следующая (соотношение 8):

После реализации сходимости итерационного процесса на вторых выходах третьих вычислителей первого, второго и третьего столбца матрицы вычислителей 1 будут получены значения компонент первого собственного вектора, а на первом выходе третьего вычислителя третьего столбца матрицы вычислителей 1 будет получено первое собственное значение.

По окончании времени, необходимого для реализации сходимости итерационного процесса, по средствам тактовых импульсов, подаваемых с блока 6 синхронизации во второй блок 9 памяти, записываются компоненты первого собственного вектора. В следующий момент времени на тактовый вход регистра 7 сдвига поступает тактовый импульс, под воздействием которого «1» из первого разряда регистра 7 сдвига сдвигается во второй разряд.

Таким образом, «1» с выхода второго разряда регистра 7 сдвига поступает на второй вход второго сомножителя блока 3.2.1 элемента «И». На вторые входы вторых сомножителей блоков 3.1.1 и 3.1.2 элементов «И» поступает «0» с выхода первого разряда регистра 7 сдвига, в результате на выходах блоков 3.1.1 и 3.1.2 элементов «И» формируется «0».

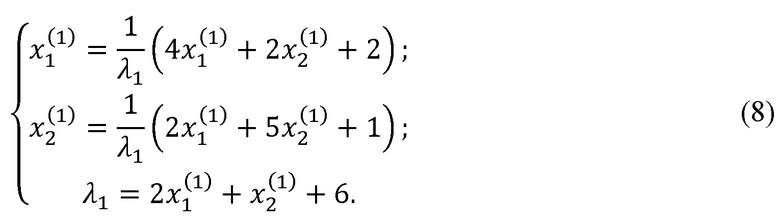

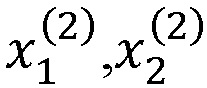

Для определения второго собственного значения и компонент  второго собственного вектора необходимо методом итерации решить систему уравнений (соотношение (9)):

второго собственного вектора необходимо методом итерации решить систему уравнений (соотношение (9)):

Для матрицы А вторая система уравнений, решаемая методом итерации, определяется из условия ортогональности векторов  и

и  Полученную систему уравнений необходимо решить методом итерации, но для этого нужно предварительно сформировать коэффициенты

Полученную систему уравнений необходимо решить методом итерации, но для этого нужно предварительно сформировать коэффициенты  Для этого используются коэффициенты

Для этого используются коэффициенты  записанные в блоке 8 памяти.

записанные в блоке 8 памяти.

После подачи на входы первого и второго вычислителей первого столбца матрицы вычислителей 1 произвольного сигнала  , а на входы первого и второго вычислителей второго столбца матрицы вычислителей 1 сигнала «1» начнется реализация итерационного процесса. После достижения сходимости итерационного процесса на выходе блока 2.2.1 деления, а соответственно на выходе второго вычислителя первого столбца матрицы вычислителей 1 будет получено значение

, а на входы первого и второго вычислителей второго столбца матрицы вычислителей 1 сигнала «1» начнется реализация итерационного процесса. После достижения сходимости итерационного процесса на выходе блока 2.2.1 деления, а соответственно на выходе второго вычислителя первого столбца матрицы вычислителей 1 будет получено значение  , на выходе второго вычислителя второго столбца матрицы вычислителей 1 будет присутствовать сигнал

, на выходе второго вычислителя второго столбца матрицы вычислителей 1 будет присутствовать сигнал  , a также значение

, a также значение  .

.

По окончании времени, необходимого для реализации сходимости итерационного процесса за счет поступления синхроимпульсов компоненты  и

и  второго собственного вектора окажутся записанными в элементах памяти блока 9 памяти.

второго собственного вектора окажутся записанными в элементах памяти блока 9 памяти.

Компонента  определяется за счет решения уравнения с одним неизвестным с использованием известного устройства для операций над матрицами, способного решать уравнения или системы из n уравнений с n неизвестными по методу Гаусса-Жордана. В его состав входят операционные блоки 4.1.1, 4.1.2, 4.1.3, 4.1.4, элемент 5 задержки. В нем выполняется обработка матрицы размерности

определяется за счет решения уравнения с одним неизвестным с использованием известного устройства для операций над матрицами, способного решать уравнения или системы из n уравнений с n неизвестными по методу Гаусса-Жордана. В его состав входят операционные блоки 4.1.1, 4.1.2, 4.1.3, 4.1.4, элемент 5 задержки. В нем выполняется обработка матрицы размерности  (N = 1, 2), которая представляет собой матрицу коэффициентов при неизвестных системы линейных уравнений, к которой справа дописана матрица размерности

(N = 1, 2), которая представляет собой матрицу коэффициентов при неизвестных системы линейных уравнений, к которой справа дописана матрица размерности  свободных членов.

свободных членов.

Таким образом, например, для решения системы из двух линейных уравнений на входы устройства будет поступать матрица В вида (соотношение 10):

где  - коэффициенты при неизвестных, а

- коэффициенты при неизвестных, а  - свободные члены.

- свободные члены.

Элементы матрицы B поступают на первые входы операционных блоков 4 построчно со сдвигом на один такт под воздействием синхроимпульсов с выходов блока 6 синхронизации, подаваемых на вторые входы операционных блоков 4, т.е. первая строка поступает на первый вход операционного блока 4.1.1, начиная с первого такта, вторая строка поступает на первый вход операционного блока 4.2.1, начиная с второго такта, и т.д. На выходах операционных блоков 4.i.j (i=1…n, j=n) получается семейство решений системы линейных уравнений.

Таким образом, решения системы из двух уравнений получаются на выходах операционных блоков 4.1.2 и 4.2.2. Решение уравнения с одним неизвестным - на выходе операционного блока 4.1.1.

Следовательно, при вычислении значения  будет задействован только операционный блок 4.1.1. Коэффициент при неизвестном и свободный член будут вычислены блоком 9 памяти.

будет задействован только операционный блок 4.1.1. Коэффициент при неизвестном и свободный член будут вычислены блоком 9 памяти.

Значение  с выхода операционного блока 4.1.1 поступает на третий информационный вход блока 9 памяти и с поступлением синхроимпульса оказывается записанным в элементе блока 9 памяти.

с выхода операционного блока 4.1.1 поступает на третий информационный вход блока 9 памяти и с поступлением синхроимпульса оказывается записанным в элементе блока 9 памяти.

Таким образом, в блок 9 памяти будут записаны компоненты второго собственного вектора матрицы А.

По окончании времени, необходимого для вычисления компонент второго собственного вектора, на тактовый вход регистра 7 сдвига поступает тактовый импульс, в результате чего второй разряд регистра 7 сдвига обнуляется. Так как на второй вход второго сомножителя блока 3.2.1 элемента «И» поступает «0» с выхода второго разряда регистра 7 сдвига, то на выходе блока 3.2.1 элемента «И» формируется «0».

Вычисление компонент третьего собственного вектора производится следующим образом. На вторые входы первого, второго и третьего вычислителя третьего столбца матрицы вычислителей 1 подается сигнал «1». С выхода третьего вычислителя первого столбца матрицы вычислителей 1 значение  поступает на информационный вход блока 9 памяти.

поступает на информационный вход блока 9 памяти.

После этого осуществляется вычисление компонент  и

и

Так как значение  вычислено и записано в элементе памяти, то полученная система линейных уравнений легко решается методом Гаусса-Жордана.

вычислено и записано в элементе памяти, то полученная система линейных уравнений легко решается методом Гаусса-Жордана.

В соответствии с алгоритмом работы операционных блоков 4 на выходах операционных блоков 4.1.2 и 4.2.2 будут сформированы соответственно значения  и

и  поступающие на входы блока 9 памяти.

поступающие на входы блока 9 памяти.

Таким образом, в элементах блока 9 памяти будут записаны компоненты третьего собственного вектора матрицы А. На этом процесс вычисления компонент собственных векторов матрицы А заканчивается. Значения компонент собственных векторов хранятся в блоке 9 памяти.

Синхроимпульсы с блока 6 синхронизации одновременно поступают на первый вход кольцевого регистра 10 сдвига, первый управляющий вход и второй вход переключения выводов блока переключения генератора 22 положительных и отрицательных ПСЧ, где происходит случайное формирование коэффициентов матрицы А и их подача на информационные входы запоминающего устройства 23, которое под воздействием управляющего сигнала, подаваемого на его N+1 вход, записывает сформированные коэффициенты в блок 8 памяти.

В кольцевом регистре 10 сдвига перед началом работы записывается код вида «10...0», причем «1» в первом разряде кольцевого регистра 10 сдвига. Поскольку на первый вход кольцевого регистра 10 сдвига поступает периодическая последовательность импульсов, то «1», перемещаясь из разряда в разряд кольцевого регистра 10 сдвига, управляет формированием дискретных базисных функций на выходах блока 9 памяти. При этом считывание производится по столбцам.

Ортогональные последовательности с выхода блока 9 памяти поступают на входы блока 54 управляемого инвертирования. В случае, если ПСЧ формировались на генераторе 58 отрицательных ПСЧ, то сформированные стохастические ортогональные коды, поступающие на первые входы блоков 56.2 - 56.4 переключения, через вторые выходы блоков 56.2 - 56.4 переключения поступают на входы блоков 59.2 - 59.4 инвертирования, где подвергаются процедуре обратного инвертирования, а затем с выходов блоков 59.2 - 59.4 инвертирования поступают на выходы блока 54 управляемого инвертирования. В случае, если ПСЧ формировались на генераторе 57 положительных ПСЧ, то сформированные стохастические ортогональные коды, поступающие на первые входы блоков 56.2 - 56.4 переключения, процедуре обратного инвертирования не подвергаются и через первые выходы блоков 56.2 - 56.4 переключения поступают на выходы блока 54 управляемого инвертирования. Таким образом, на выходе блока 54 управляемого инвертирования формируются набор ансамблей стохастических ортогональных кодов.

Вместе с подачей синхроимпульса на кольцевой регистр 10 сдвига на блок 47 элемента «И» подается информационный сигнал «1», в результате чего на выходе блока 47 элемента «И» формируется управляющий сигнал.

Аналогичным образом функционирует блок 49 формирования копий хаотических ансамблей ортогональных сигналов на приемной стороне, который запускается генератором 43 копии сигналов синхронизации.

Рассмотрим принцип работы предлагаемой СПИ на примере.

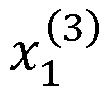

Предположим, что для передачи последовательности информационных бит используются 3 канала связи, в которых бит информации модулируется хаотической расширяющей последовательностью (N=3 выбрана для упрощения расчетов). Допустим, что на входы запоминающих устройств 11 каждого из каналов 12 передачи подается информационная последовательность «1 0 1» и в блок 8 памяти заранее введена случайная последовательность коэффициентов матрицы А размерностью 3x3 вырабатываемая генератором 22 положительных и отрицательных ПСЧ.

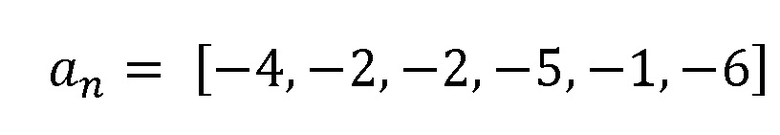

Пусть исходная действительная симметрическая положительно определённая матрица А имеет вид (4).

Предположим, что генератор 22 положительных и отрицательных ПСЧ использовал для формирования коэффициентов симметрической матрицы А вида (4) генератор 58 отрицательных ПСЧ, который сгенерировал следующие ПСЧ:

.

.

Для того чтобы сформированные генератором 58 отрицательные ПСЧ числа могли быть использованы в качестве коэффициентов симметрической матрицы А вида (4) над ними производится прямое инвертирование с помощью блока 59.1 инвертирования генератора 22 положительных и отрицательных ПСЧ. Итог формирования псевдослучайных коэффициентов симметрической матрицы А вида (4) генератором 22 положительных и отрицательных ПСЧ следующий:

В регистре 7 сдвига записан код вида «10», причем "1" записана в первом разряде регистра 7 сдвига.

Последовательности информационных бит, представленные на фиг. 6 б, в, г, побитно поступают на первые входы запоминающих устройств 11 соответствующих каналов 12 передачи. Далее биты записываются в запоминающие устройства 11 каждого из каналов 12 передачи и ожидают управляющего сигнала с блока 47 элемента «И» для дальнейшей передачи их в блок 13 цифровой информации и модуляции расширяющей последовательностью в модуляторе 14.

Активация генератора 52 тактовых импульсов свидетельствует о начале формирования стохастическим образом ортогональных систем сигналов, описываемых собственными векторами диагональных положительно определенных симметрических матриц, в результате чего начинает функционировать блок 6 синхронизации, с первого выхода которого подается управляющий сигнал на первый управляющий вход генератора 22 положительных и отрицательных ПСЧ и запоминающее устройство 23, в результате чего происходит генерация и запись случайных коэффициентов матрицы А в блок 8 памяти, после этого начинается вычисление 1-го собственного значения и соответствующего ему собственного вектора (первой расширяющей последовательности) которое осуществляться в течение времени нахождения «1» в 1-м разряде регистра 7 сдвига, поэтому период поступления тактовых импульсов на тактовый вход регистра 7 сдвига равен времени сходимости итерационного процесса и вычисления оставшейся части компонент собственного вектора.

В течение первого периода работы, «1» с выхода первого разряда регистра 7 сдвига поступает на вторые входы блоков 3.1.1 и 3.1.2 элементов «И». На второй вход блока 3.2.1 элемента «И» поступает «0» с выхода второго разряда первого регистра 7 сдвига, в результате на выходе блока 3.2.1элемента «И» формируется «0».

С поступлением последовательности синхроимпульсов коэффициенты, находящиеся в первом блоке 8 памяти, последовательно поступают на первые входы вычислителей 1 и запоминаются в них. Причем вычислитель осуществляет так же функцию накопления каждый раз при подаче на его вход нового слагаемого.

На вторые входы вычислителей 1, кроме последнего столбца матрицы вычислителей, подаются произвольные сигналы  На вторых входах вычислителей 1 последнего столбца присутствует сигнал «1».

На вторых входах вычислителей 1 последнего столбца присутствует сигнал «1».

Следовательно, для реализации итерационной процедуры отыскания собственного числа  матрицы А в качестве начального приближения выбирается вектор

матрицы А в качестве начального приближения выбирается вектор

На втором выходе последнего вычислителя 1 последней строки матрицы при этом образуется сигнал в соответствии с соотношением (5), который является первым приближением собственного числа

На выходе последнего вычислителя 1 1-й строки (i = 1…n-1) образуется сигнал, формируемый на основе соотношения (6). Этот сигнал является i-м компонентом первого ненормированного приближения первого собственного вектора матрицы коэффициентов А

Нормирование первого приближения первого вектора осуществляется путем деления всех его компонентов на величину последнего компонента Так как в результате нормирования последняя компонента равна «1», то ее деление не производится и «1» поступает на вторые входы последнего столбца матрицы вычислителей 1. Нормирование остальных компонент осуществляется при помощи блоков 2.1.1 и 2.1.2 деления путем деления компонент на величину последней компоненты

Так как в результате нормирования последняя компонента равна «1», то ее деление не производится и «1» поступает на вторые входы последнего столбца матрицы вычислителей 1. Нормирование остальных компонент осуществляется при помощи блоков 2.1.1 и 2.1.2 деления путем деления компонент на величину последней компоненты  Сигнал с выхода блока 2.1.1 деления через блок 3.1.1 поступает на вторые входы второго и третьего вычислителей первого столбца матрицы вычислителей 1. Сигнал с выхода блока 2.1.2 деления через блок 3.1.2 поступает на второй вход третьего вычислителя второго столбца матрицы вычислителей 1.

Сигнал с выхода блока 2.1.1 деления через блок 3.1.1 поступает на вторые входы второго и третьего вычислителей первого столбца матрицы вычислителей 1. Сигнал с выхода блока 2.1.2 деления через блок 3.1.2 поступает на второй вход третьего вычислителя второго столбца матрицы вычислителей 1.

Таким образом, в соответствии с соотношением (7) после окончания первой итерации на выходах третьих вычислителей первого, второго и третьего столбца матрицы вычислителей 1 присутствуют сигналы, соответствующие компонентам первого нормированного приближения первого собственного вектора

Затем итерационный процесс повторяется и после окончания второй итерации на вторых выходах третьих вычислителей первого, второго и третьего столбца матрицы вычислителей 1 присутствуют сигналы, соответствующие компонентам второго нормированного приближения первого собственного вектора

Повторение итераций будет осуществляться до полной сходимости итерационного процесса. В результате на вторых выходах третьих вычислителей первого, второго и третьего столбца матрицы вычислителей 1 присутствуют сигналы, соответствующие компонентам нормированного первого собственного вектора  а на втором выходе третьего вычислителя третьего столбца матрицы вычислителей 1 присутствует сигнал, соответствующий собственному значению

а на втором выходе третьего вычислителя третьего столбца матрицы вычислителей 1 присутствует сигнал, соответствующий собственному значению

Таким образом, для матрицы А система уравнений, решаемая методом итерации, представлена в соотношении (8).

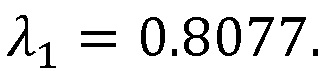

После реализации сходимости итерационного процесса на вторых выходах третьих вычислителей первого, второго и третьего столбца матрицы вычислителей 1 будут получены значения компонент первого собственного вектора  а на первом выходе третьего вычислителя третьего столбца матрицы вычислителей 1 будет получено первое собственное значение

а на первом выходе третьего вычислителя третьего столбца матрицы вычислителей 1 будет получено первое собственное значение

По окончании времени, необходимого для реализации сходимости итерационного процесса, по средствам тактового импульса во второй блок 9 памяти записываются компоненты первого собственного вектора, который представлен на фиг. 6, д. В следующий момент времени на тактовый вход регистра 7 сдвига поступает тактовый импульс, под воздействием которого «1» из первого разряда регистра 7 сдвига сдвигается во второй разряд.

Таким образом, «1» с выхода второго разряда регистра 7 сдвига поступает на вход второго сомножителя блока 3.2.1 элемента «И». На входы вторых сомножителей блоков 3.1.1 и 3.1.2 элемента «И» поступает «0» с выхода первого разряда регистра 7 сдвига, в результате на выходах блоков 3.1.1 и 3.1.2 элемента «И» формируется «0».

Для определения второго собственного значения и компонент  второго собственного вектора необходимо методом итерации решить систему уравнений в соответствии с соотношением (9).

второго собственного вектора необходимо методом итерации решить систему уравнений в соответствии с соотношением (9).

Для матрицы А вторая система уравнений, решаемая методом итерации, определяется из условия ортогональности векторов  и

и  Так как

Так как

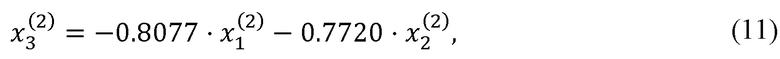

то (соотношение (11)):

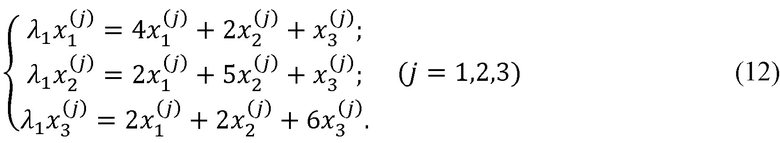

Подставляя это выражение в систему вида (соотношение (12)):

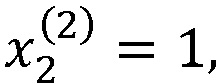

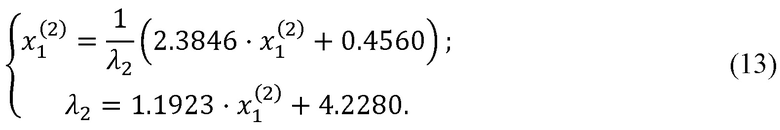

и полагая  получим (соотношение (13)):

получим (соотношение (13)):

Систему (13) необходимо решить методом итерации, но для этого нужно предварительно сформировать коэффициенты  с использованием соотношения (9). Для этого используются коэффициенты

с использованием соотношения (9). Для этого используются коэффициенты  записанные в блоке 8 памяти.

записанные в блоке 8 памяти.

После подачи на входы первого и второго вычислителей первого столбца матрицы вычислителей 1 произвольного сигнала  , а на входы первого и второго вычислителей второго столбца матрицы вычислителей 1 сигнала «1» начнется реализация итерационного процесса. После достижения сходимости итерационного процесса на выходе блока 2.2.1 деления, а соответственно на выходе второго вычислителя первого столбца матрицы вычислителей 1 будет получено значение

, а на входы первого и второго вычислителей второго столбца матрицы вычислителей 1 сигнала «1» начнется реализация итерационного процесса. После достижения сходимости итерационного процесса на выходе блока 2.2.1 деления, а соответственно на выходе второго вычислителя первого столбца матрицы вычислителей 1 будет получено значение  на выходе второго вычислителя второго столбца матрицы вычислителей 1 будет присутствовать сигнал

на выходе второго вычислителя второго столбца матрицы вычислителей 1 будет присутствовать сигнал  a также второе собственное значение

a также второе собственное значение

По окончании времени, необходимого для реализации сходимости итерационного процесса за счет поступления синхроимпульсов компоненты  и

и  второго собственного вектора окажутся записанными в элементах памяти блока 9 памяти.

второго собственного вектора окажутся записанными в элементах памяти блока 9 памяти.

Компонента  определяется из соотношения (12), т.е. уравнения с одним неизвестным с использованием известного устройства для операций над матрицами, способного решать уравнения с одним неизвестным или системы из n уравнений с n неизвестными по методу Гаусса-Жордана. В его состав входят операционные блоки 4.1.1, 4.1.2, 4.1.3, 4.1.4, элемент 5 задержки, блок 6 синхронизации. В нем выполняется обработка матрицы размерности

определяется из соотношения (12), т.е. уравнения с одним неизвестным с использованием известного устройства для операций над матрицами, способного решать уравнения с одним неизвестным или системы из n уравнений с n неизвестными по методу Гаусса-Жордана. В его состав входят операционные блоки 4.1.1, 4.1.2, 4.1.3, 4.1.4, элемент 5 задержки, блок 6 синхронизации. В нем выполняется обработка матрицы размерности  (N = 1, 2), которая представляет собой матрицу коэффициентов при неизвестных системы линейных уравнений, к которой справа дописана матрица размерности

(N = 1, 2), которая представляет собой матрицу коэффициентов при неизвестных системы линейных уравнений, к которой справа дописана матрица размерности  свободных членов.

свободных членов.

Таким образом, например, для решения системы из двух линейных уравнений на входы устройства будет поступать матрица В (соотношение (10)).

Элементы матрицы B поступают на входы операционных блоков 4 построчно со сдвигом на один такт под воздействием синхроимпульсов с выходов блока 6 синхронизации, т.е. первая строка поступает на первый вход операционного блока 4.1.1, начиная с первого такта, вторая строка поступает на первый вход операционного блока 4.2.1, начиная с второго такта, и т.д. На выходах операционных блоков 4.i.j (i=1…n, j=n) получается семейство решений системы линейных уравнений.

Таким образом, решения системы из двух уравнений получаются на выходах операционных блоков 4.1.2 и 4.2.2. Решение уравнения с одним неизвестным - на выходе операционного блока 4.1.1.

Следовательно, при вычислении значения  будет задействован только операционный блок 4.1.1. Коэффициент при неизвестном и свободный член будут вычислены блоком 9 памяти.

будет задействован только операционный блок 4.1.1. Коэффициент при неизвестном и свободный член будут вычислены блоком 9 памяти.

Значение  с выхода операционного блока 4.1.1 поступает на информационный вход блока 9 памяти и с поступлением синхроимпульса оказывается записанным в блоке 9 памяти.

с выхода операционного блока 4.1.1 поступает на информационный вход блока 9 памяти и с поступлением синхроимпульса оказывается записанным в блоке 9 памяти.

Таким образом, в блок 9 памяти будут записаны компоненты второго собственного вектора матрицы А:  который представлен на фиг. 6, е.

который представлен на фиг. 6, е.

По окончании времени, необходимого для вычисления компонент второго собственного вектора на тактовый вход регистра 7 сдвига поступает тактовый импульс, в результате чего второй разряд регистра 7 сдвига обнуляется. Так как на вход второго сомножителя блока 3.2.1 элемента «И» поступает «0» с выхода второго разряда регистра 7 сдвига, то на выходе блока 3.2.1 элемента «И» формируется «0».

Вычисление компонент третьего собственного вектора производится следующим образом. На вторые входы первого, второго и третьего вычислителя первого столбца матрицы вычислителей 1 подается сигнал «1». С выхода третьего вычислителя первого столбца матрицы вычислителей 1 значение  поступает на информационный вход блока 9 памяти. С поступлением синхроимпульса на вход блока 9 памяти значение

поступает на информационный вход блока 9 памяти. С поступлением синхроимпульса на вход блока 9 памяти значение  записывается в элемент памяти.

записывается в элемент памяти.

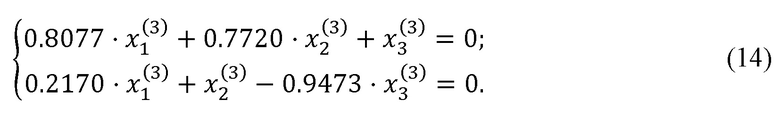

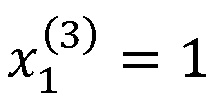

После этого осуществляется вычисление компонент  и

и  с использованием соотношений ортогональности (соотношение (14)):

с использованием соотношений ортогональности (соотношение (14)):

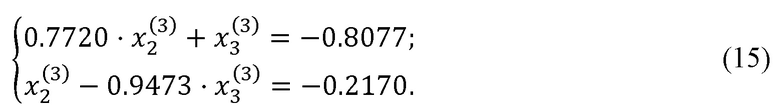

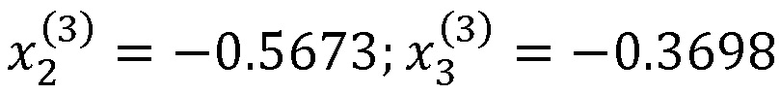

Так как значение  вычислено и записано в элементе памяти, то систему уравнений (14) можно представить в виде (соотношение (15)):

вычислено и записано в элементе памяти, то систему уравнений (14) можно представить в виде (соотношение (15)):

Эта система линейных уравнений легко решается методом Гаусса-Жордана. Поскольку коэффициенты при неизвестных и свободные члены записаны в блоке 9 памяти, то соотношение (15) решается следующим образом.

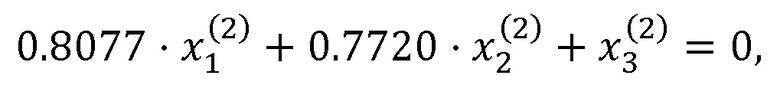

При поступлении синхроимпульса значение 0,7720 считывается и поступает на вход операционного блока 4.1.1.

При поступлении синхроимпульса значение «1» считывается и поступает на вход операционного блока 4.2.1.

Аналогичным образом считываются все оставшиеся значения.

В соответствии с алгоритмом работы операционных блоков 4 на выходах операционных блоков 4.1.2 и 4.2.2 будут сформированы соответственно значения  , поступающие на входы блока 9 памяти.

, поступающие на входы блока 9 памяти.

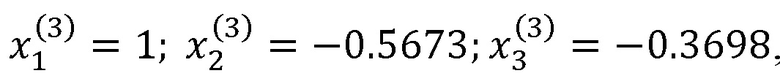

Таким образом, в элементах блока 9 памяти будут записаны компоненты третьего собственного вектора матрицы А:  которые представлены на фиг. 6, ё. На этом процесс вычисления компонент собственных векторов матрицы А заканчивается. Значения компонент собственных векторов хранятся в блоке 9 памяти.

которые представлены на фиг. 6, ё. На этом процесс вычисления компонент собственных векторов матрицы А заканчивается. Значения компонент собственных векторов хранятся в блоке 9 памяти.

После того как расширяющие последовательности сформированы, с блока 6 синхронизации поступают тактовые импульсы на первый вход кольцевого регистра 10 сдвига и, как следствие, на второй вход блока 47 элемента «И».

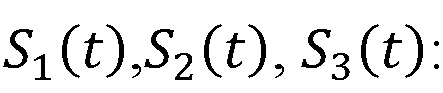

Таким образом, на выходах блока 9 памяти будет формироваться, периодически повторяясь, система кусочно-постоянных дискретных базисных функций (ансамбль стохастических ортогональных кодов)

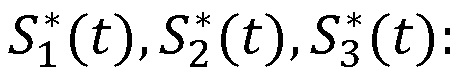

Поскольку коэффициенты симметрической матрицы А вида (1) в данном примере формировались с помощью генератора 58 отрицательных ПСЧ и процесса прямого инвертирования на блоке 59.1, то необходимо провести обратное инвертирование полученных ансамблей стохастических ортогональных кодов в блоке 54 управляемого инвертирования при помощи блоков 59.2 – 59.4 инвертирования. Таким образом, на выходах блока 54 управляемого инвертирования будет формироваться, периодически повторяясь, система кусочно-постоянных дискретных базисных функций (ансамбль стохастических ортогональных кодов)