Изобретение относится к автоматике и вычислительной техники и может быть использовано для определения степени зараженности объекта в условиях, присущих реальному процессу его функционирования - в условиях непрерывной динамики и постоянных изменений параметров (одни из которых не могут быть выше допустимых, а другие не могут быть ниже допустимых) внешних условий и с учетом влияющих факторов, а также предупреждения обслуживающего персонала об угрозе заражения объекта.

Известно устройство управления для определения степени зараженности объекта [1], которое позволяет определить степень зараженности объекта в условиях, присущих реальному процессу его функционирования.

Недостатком данного устройства является невозможность определения степени зараженности объекта в условиях, присущих реальному процессу его функционирования в динамике работы сложного объекта, при котором одни параметры не могут быть выше допустимых, а другие не могут быть ниже допустимых.

Работа устройства основана на том, что обслуживание объекта в замкнутом пространстве сопряжено с влиянием на обслуживающий персонал вредоносных испарений и выделений от объекта, затрудняющих эффективную работу обслуживающего персонала. В таких условиях обслуживающий персонал должен быть своевременно предупрежден об опасности.

Задача изобретения - создать устройство, обеспечивающее определение степени зараженности объекта и выдачу сигнала об опасности для обслуживающего персонала в условиях, когда одни параметры не могут быть выше допустимых, а другие не могут быть ниже допустимых значений.

Это решение достигается тем, что в устройство для определения степени зараженности объекта, содержащее датчики загрязнения объекта (1j) (j=1,…n), преобразователи аналог-код (2j) (j=1,…n), первые регистры (7j) (j=1,…n), группу первых схем сравнения (4j) (j=1,…n), вторые регистры (10j) (j=1,…n), третий регистр (21), группу блоков умножения (11j) (j=1,…n), группу первых элементов задержки (8j) (j=1,…n), группу первых элементов И (9j) (j=1,…n), второй элемент И (14), дешифратор (12), счетчик (13), второй элемент задержки (15), третий элемент задержки (16), четвертый элемент задержки (17), сумматор (19), вторую группу схем сравнения (20), генератор тактовых импульсов (23), выход которого подсоединен к первому входу второго элемента И (14), второй вход которого подсоединен к входу (24) устройства, а выход - к входу второго элемента задержки (15) и к первому входу счетчика (13), выход которого подсоединен к входу дешифратора (12), каждый выход которого подсоединен к входу первого элемента задержки (8j) (j=1,…n) и к управляющему входу блока умножения (11j) (j=1,…n), второй вход которого подсоединен к выходу второго регистра (10j) (j=1,…n), третий вход - к выходу преобразователя аналог-код (2j) (j=1,…n), а выход - к первому входу первой группы элементов И (9j) (j=1,…n), второй вход которого подсоединен к выходу первого элемента задержки (8j) (j=1,…n), а выход - к одноименному входу первого элемента ИЛИ (18), выход первого элемента задержки (8n) подсоединен к входу третьего элемента задержки (16), выход которого подсоединен к управляющему входу второй группы схем сравнения (20) и входу четвертого элемента задержки (17), выход которого подсоединен к входу сброса счетчика (13) и к входу сброса сумматора (19) в ноль, управляющий вход сумматора (19) подсоединен к выходу второго элемента задержки (15), второй вход - к выходу первого элемента ИЛИ (18), выход сумматора (19) подсоединен к первому входу второй группы схем сравнения (20), второй вход которой подсоединен к выходу третьего регистра (21), а выход - к первому входу второго элемента ИЛИ (22), выход которого является выходом (25) устройства, первый вход первой группы схем сравнения (4j) (j=1,…n), подсоединен к выходу первого регистра (7j) (j=1,…n), второй вход - к выходу преобразователя аналог-код (2j) (j=1,…n), выход датчика (1j) (j=1,…n) подсоединен к входу одноименного преобразователя аналог-код (2j) (j=1,…n), введены группа четвертых регистров (6j) (j=1,…n), третья группа схем сравнения (5j) (j=1,…n), третья группа элементов ИЛИ (3j) (j=1,…n), выход группы четвертых регистров (6j) (j=1,…n) подсоединен к первому входу третьей группы схемы сравнения (5j) (j=1,…n), второй вход которой подсоединен к выходу преобразователя аналог-код (2j) (j=1,…n), а выход - к первому входу третьего элемента ИЛИ (3j) (j=1,…n), второй вход которой подсоединен к выходу первой группы схемы сравнения (4j) (j=1,…n), а выход - к одноименному входу второго элемента ИЛИ (22).

Проведенный поиск в известной научно-технической литературе не выявил наличие подобных технических решений.

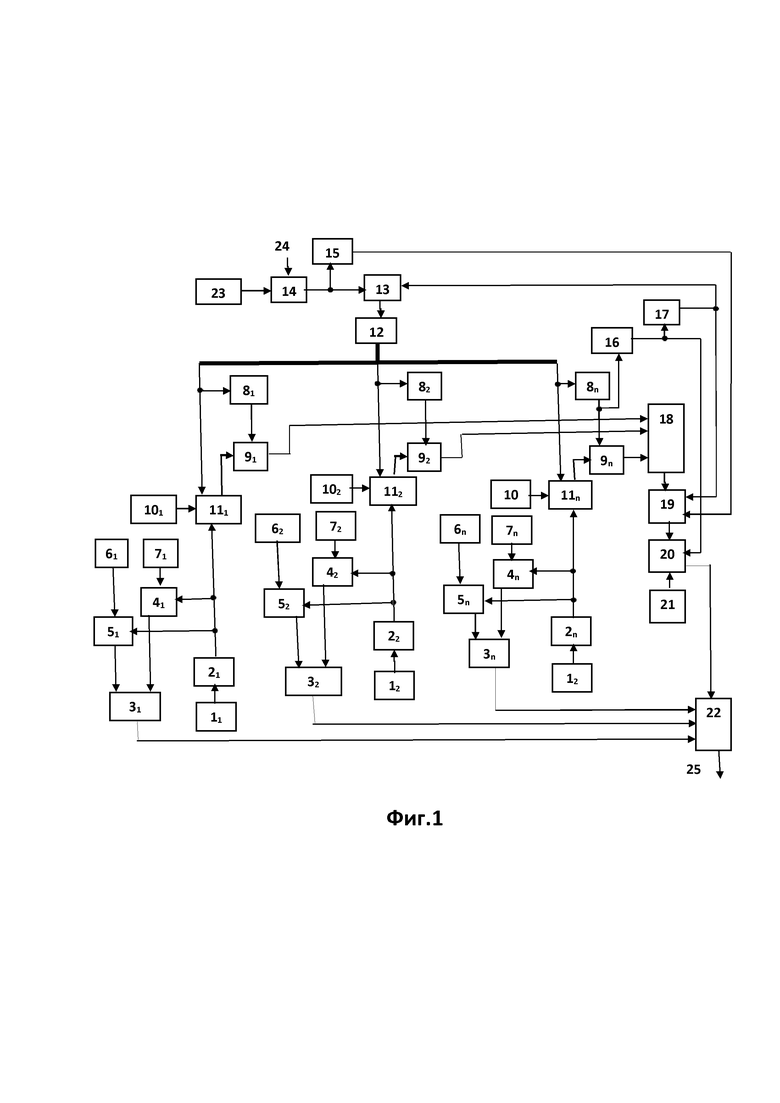

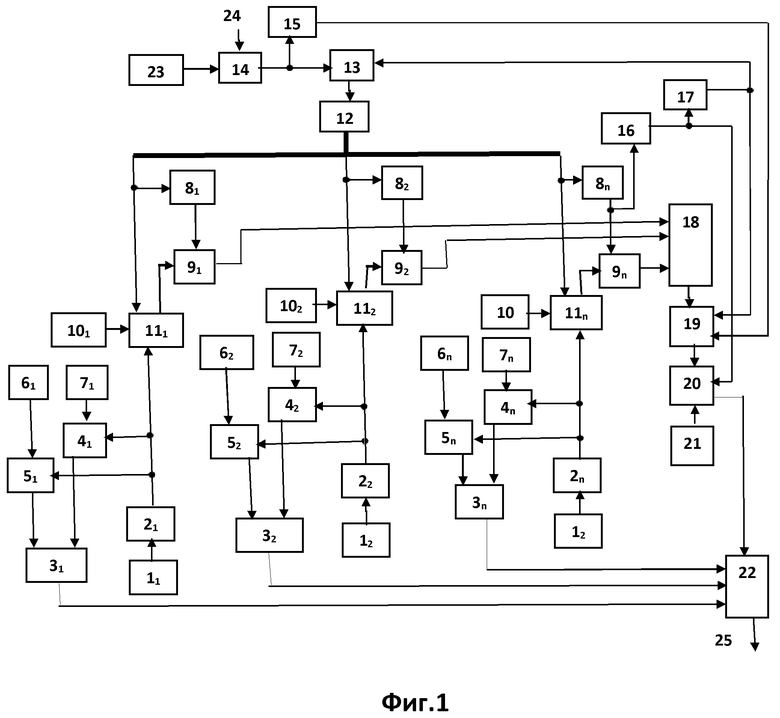

Сущность изобретения поясняется чертежом.

Устройство для определения степени зараженности объекта (фиг. 1) содержит датчики загрязнения объекта (1j) (j=1,…n), преобразователи аналог-код (2j) (j=1,…n), элементы ИЛИ (3j) (j=1,…n), схемы сравнения (4j) (j=1,…n), схемы сравнения (5j) (j=1,…n), регистры допустимых верхних уровней загрязнения по j-му параметру (6j) (j=1,…n), регистры допустимых нижних уровней загрязнения по j-му параметру (7j) (j=1,…n), элементы задержки (8j) (j=1,…n), группа элементов И (9j) (j=1,…n), регистры коэффициентов нормализации (10j) (j=1,…n), блоки умножения (11j) (j=1,…n), дешифратор (12), счетчик (13), элемент И (14), элемент задержки (15), элемент задержки (16), элемент задержки (17), группа элементов ИЛИ (18), сумматор (19), схема сравнения (20), регистр допустимого уровня суммарного загрязнения объекта (21), элемент ИЛИ (22), генератор тактовых импульсов (23), вход (24), выход (25) устройства.

В исходном состоянии счетчик (13), сумматор (19) находятся в нулевом состоянии. На регистрах (6j) (j=1,…n) хранятся коды допустимых верхних уровней загрязнения j-го параметра. На регистрах (7j) (j=1,…n) хранятся коды допустимых нижних уровней загрязнения j-го параметра. На регистрах (10j) (j=1,…n) хранятся коды коэффициентов нормализации, на регистре (21) хранится код допустимого уровня суммарного загрязнения объекта.

После подачи пускового сигнала по входу (24) на управляющий вход элемента И (14) импульсы с выхода генератора (23) через открытый элемент И (14) начинают поступать на вход элемента задержки (15) и на вход счетчика (13), с выхода которого код поступает на вход дешифратора (12). Каждый выход дешифратора (12j) (j=1,…n) подсоединен к входу элемента задержки (8j) (j=1,…n) и к управляющему входу блока умножения (11j) (j=1,…n), где происходит перемножение кода с выхода регистра (10j) (j=1,…n) коэффициента нормализации на значение кода с выхода преобразователя аналог-код (2j) (j=1,…n). Под нормализацией здесь понимается приведение различных входных данных в самых разных единицах измерения и диапазонах значений к единому виду, который позволит сравнивать их между собой или использовать для расчета схожести объектов.

Код с выхода блока умножения (11j) (j=1,…n) поступает на первый вход группы элементов И (9j) (j=1,…n), на второй вход которой поступает сигнал с выхода элемента задержки (8j) (j=1,…n). Элемент задержки (8j) (j=1,…n) задерживает сигнал на время надежного срабатывания блока умножения (11j) (j=i,…n).

Код с выхода группы элементов И (9j) (j=1,…n) поступает на одноименный вход группы элементов ИЛИ (18), с выхода которого код поступает на первый вход сумматора (19), на управляющий вход которого поступает сигнал с выхода элемента задержки (15). Элемент задержки (15) задерживает сигнал на время надежного срабатывания блока умножения (11j) (j=1,…n), группы элементов И (9j) (j=1,...n) и элемента ИЛИ (18).

Код с выхода сумматора (19) поступает на первый вход схемы сравнения (20), на второй вход которой поступает код с выхода регистра (21). В случае превышения кода на выходе сумматора (19) над кодом с выхода регистра (21), на выходе схемы сравнения (20) появляется единичный сигнал тревоги, который через элемент ИЛИ (22) поступает на выход (25) устройства. Кроме того сигнал тревоги может появиться также на выходе схемы сравнения (4j) (j=1,…n) или схемы сравнения (5j) (j=1,…n), на первые входы которых поступают коды с выходов регистров (7j (j=1,…n) и регистров (6j) (j=1,…n) соответственно, а на их вторые входы - коды с выхода преобразователя аналог-код (2j) (j=1,…n). Сигнал с выхода схемы сравнения (4j) (j=1,…n) или схемы сравнения (5j) (j=1,…n) через элемент ИЛИ (3j) (j=1,…n) поступает на одноименный вход элемента ИЛИ (22), а далее на выход (25) устройства.

При достижении счетчиком (13) числа n на выходе элемента задержки (8П) появляется единичный сигнал, который поступает на вход элемента задержки (16), который задерживает сигнал на время надежного срабатывания элемента ИЛИ (18) и сумматора (19). Единичный сигнал с выхода элемента задержки (16) поступает на вход элемента задержки (17), который задерживает сигнал на время надежного срабатывания сумматора (19) и схемы сравнения (20), после чего единичный сигнал с выхода элемента задержки (17) сбрасывает в ноль сумматор (19) и счетчик (13).

Частота сигналов ГТИ (23) выбирается с учетом последовательности надежного срабатывания элемента И (14), счетчика (13), дешифратора (12), блока умножения (11), элементов И (9), ИЛИ (18), сумматора (19), схемы сравнения (20), элемента ИЛИ (22).

Предлагаемое устройство для определения степени зараженности объекта в составе элементов 1-22 (см. фиг. 1) может бать построено на известных стандартных микросхемах, выпускаемых отечественной промышленностью.

Таким образом, технический результат заявленного изобретения достигается при помощи технических средств (блоков и элементов), упомянутых в описании работы устройства.

Данное устройство обеспечивает определение степени зараженности объекта в условиях, присущих реальному процессу его функционирования, выдачу сигнала тревоги при выходе из области допустимых значений отдельных параметров зараженности среды или суммарного значения зараженности среды в условиях непрерывной динамики и постоянных изменений параметров внешних условий и с учетом влияющих факторов, что существенно расширяет область применения устройства.

Литература

1. SU №2704736, 2019.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство непрерывного контроля параметров объекта системы внутреннего электроснабжения | 2023 |

|

RU2805217C1 |

| Устройство для определения степени зараженности объекта | 2019 |

|

RU2704736C1 |

| УСТРОЙСТВО ДЛЯ КОЛИЧЕСТВЕННОЙ ОЦЕНКИ КАЧЕСТВЕННОГО ПОКАЗАТЕЛЯ | 2013 |

|

RU2520390C1 |

| УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ ПРОЦЕССА ПРИНЯТИЯ РЕШЕНИЯ В УСЛОВИЯХ НЕОПРЕДЕЛЕННОСТИ | 2011 |

|

RU2468423C1 |

| УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ ГРАФИКА РАБОТЫ СОТРУДНИКОВ УЧРЕЖДЕНИЯ | 2010 |

|

RU2434273C1 |

| УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ ГРАФИКА РАБОТЫ СОТРУДНИКОВ УЧРЕЖДЕНИЯ | 2011 |

|

RU2480827C1 |

| Устройство для вычисления логических производных многозначных данных | 1990 |

|

SU1837277A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕРАСПРЕДЕЛЕНИЯ ЗАДАЧ МЕЖДУ ПРОЦЕССОРАМИ | 1991 |

|

RU2023292C1 |

| УСТРОЙСТВО ДЛЯ ОЦЕНКИ ПРЕДПОЧТИТЕЛЬНОГО УРОВНЯ УНИФИКАЦИИ ТЕХНИЧЕСКИХ СРЕДСТВ | 2014 |

|

RU2586573C1 |

| Устройство для распределения заданий процессорам | 1988 |

|

SU1837286A1 |

Изобретение относится к автоматике и вычислительной технике. Технический результат заключается в повышении надежности работы устройства в условиях непрерывной динамики и постоянного изменения внешних факторов. Технический результат достигается за счет того, что в устройство для определения степени зараженности объекта введены группа четвертых регистров, третья группа схем сравнения, третья группа элементов ИЛИ, выход группы четвертых регистров подсоединен к первому входу третьей группы схемы сравнения, второй вход которой подсоединен к выходу преобразователя аналог-код, а выход - к первому входу третьего элемента ИЛИ, второй вход которой подсоединен к выходу первой группы схемы сравнения, а выход - к одноименному входу второго элемента ИЛИ. 1 ил.

Устройство для определения степени зараженности объекта, содержащее датчики загрязнения объекта (1j) (j=1,…n), преобразователи аналог-код (2j) (j=1,…n), первые регистры (7j) (j=1,…n), группу первых схем сравнения (4j) (j=1,…n), вторые регистры (10j) (j=1,…n), третий регистр (21), группу блоков умножения (11j) (j=1,…n), группу первых элементов задержки (8j) (j=1,…n), группу первых элементов И (9j) (j=1,…n), второй элемент И (14), дешифратор (12), счетчик (13), второй элемент задержки (15), третий элемент задержки (16), четвертый элемент задержки (17), сумматор (19), вторую группу схем сравнения (20), генератор тактовых импульсов (23), выход которого подсоединен к первому входу второго элемента И (14), второй вход которого подсоединен к входу (24) устройства, а выход – к входу второго элемента задержки (15) и к первому входу счетчика (13), выход которого подсоединен к входу дешифратора (12), каждый выход которого подсоединен к входу первого элемента задержки (8j) (j=1,…n) и к управляющему входу блока умножения (11j) (j=1,…n), второй вход которого подсоединен к выходу второго регистра (10j) (j=1,…n), третий вход – к выходу преобразователя аналог-код (2j) (j=1,…n), а выход – к первому входу первой группы элементов И (9j) (j=1,…n), второй вход которого подсоединен к выходу первого элемента задержки (8j) (j=1,…n), а выход – к одноименному входу первого элемента ИЛИ (18), выход первого элемента задержки (8n) подсоединен к входу третьего элемента задержки (16), выход которого подсоединен к управляющему входу второй группы схем сравнения (20) и входу четвертого элемента задержки (17), выход которого подсоединен к входу сброса счетчика (13) и к входу сброса сумматора (19) в ноль, управляющий вход сумматора (19) подсоединен к выходу второго элемента задержки (15), второй вход – к выходу первого элемента ИЛИ (18), выход сумматора (19) подсоединен к первому входу второй группы схем сравнения (20), второй вход которой подсоединен к выходу третьего регистра (21), а выход – к первому входу второго элемента ИЛИ (22), выход которого является выходом (25) устройства, первый вход первой группы схем сравнения (4j) (j=1,…n) подсоединен к выходу первого регистра (7j) (j=1,…n), второй вход – к выходу преобразователя аналог-код (2j) (j=1,…n), выход датчика (1j) (j=1,…n) подсоединен к входу одноименного преобразователя аналог-код (2j) (j=1,…n), отличающееся тем, что в него дополнительно введены группа четвертых регистров (6j) (j=1,…n), третья группа схем сравнения (5j) (j=1,…n), третья группа элементов ИЛИ (3j) (j=1,…n), выход группы четвертых регистров (6j) (j=1,…n) подсоединен к первому входу третьей группы схемы сравнения (5j) (j=1,…n), второй вход которой подсоединен к выходу преобразователя аналог-код (2j) (j=1,…n), а выход - к первому входу третьего элемента ИЛИ (3 j) (j=1,…n), второй вход которой подсоединен к выходу первой группы схемы сравнения (4j) (j=1,…n), а выход – к одноименному входу второго элемента ИЛИ (22).

| Устройство для определения степени зараженности объекта | 2019 |

|

RU2704736C1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ВРЕДНЫХ ВЕЩЕСТВ В ВОЗДУХЕ | 2013 |

|

RU2539867C1 |

| Устройство для закрепления лыж на раме мотоциклов и велосипедов взамен переднего колеса | 1924 |

|

SU2015A1 |

| US 7487662 B2, 10.02.2009 | |||

| Адаптивная система электроснабжения автономного объекта | 2018 |

|

RU2681380C1 |

Авторы

Даты

2022-11-16—Публикация

2021-12-17—Подача