Изобретение относится к вычислительной технике и может быть использовано для построения средств автоматики, функциональных узлов систем управления и др.

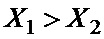

Известны компараторы двоичных чисел (см., например, патент РФ 2393526, кл. G06F7/02, 2010г.), построенные на основе булевого операционного базиса (на основе логических операций И, ИЛИ, НЕ) и формирующие признак соотношения  , где

, где  есть n-разрядные двоичные числа, задаваемые двоичными сигналами.

есть n-разрядные двоичные числа, задаваемые двоичными сигналами.

К причине, препятствующей достижению указанного ниже технического результата при использовании известных компараторов двоичных чисел, относится схемная сложность, обусловленная тем, что цена по Квайну комбинационной части, в частности, упомянутого аналога равна 14.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является принятый за прототип компаратор двоичных чисел (патент РФ 2330322, кл. G06F7/00, 2008г.), который содержит D-триггер, элемент И и формирует признак соотношения  , где

, где  есть n-разрядные двоичные числа, задаваемые двоичными сигналами. При этом прототип построен на основе булевого операционного базиса.

есть n-разрядные двоичные числа, задаваемые двоичными сигналами. При этом прототип построен на основе булевого операционного базиса.

К причине, препятствующей достижению указанного ниже технического результата при использовании прототипа, относится схемная сложность, обусловленная тем, что цена по Квайну его комбинационной части равна 9.

Техническим результатом изобретения является схемное упрощение за счет уменьшения цены по Квайну комбинационной части компаратора двоичных чисел при сохранении функциональных возможностей и логического операционного базиса прототипа.

Указанный технический результат при осуществлении изобретения достигается тем, что в компараторе двоичных чисел, содержащем элемент И и D-триггер, вход сброса, тактовый вход и вход данных D-триггера подключены соответственно к первому, второму управляющим входам и выходу компаратора двоичных чисел, первый информационный вход которого соединен с первым входом элемента И, особенность заключается в том, что в него дополнительно введены три элемента ИЛИ-НЕ, первый, второй входы и выход первого элемента ИЛИ-НЕ подключены соответственно к первому, второму входам элемента И и второму входу второго элемента ИЛИ-НЕ, а второй вход и выход элемента И соединены соответственно с инвертирующим выходом D-триггера и вторым входом третьего элемента ИЛИ-НЕ, подключенного первым входом и выходом соответственно к выходу второго элемента ИЛИ-НЕ и выходу компаратора двоичных чисел, второй информационный вход которого соединен с первым входом второго элемента ИЛИ-НЕ.

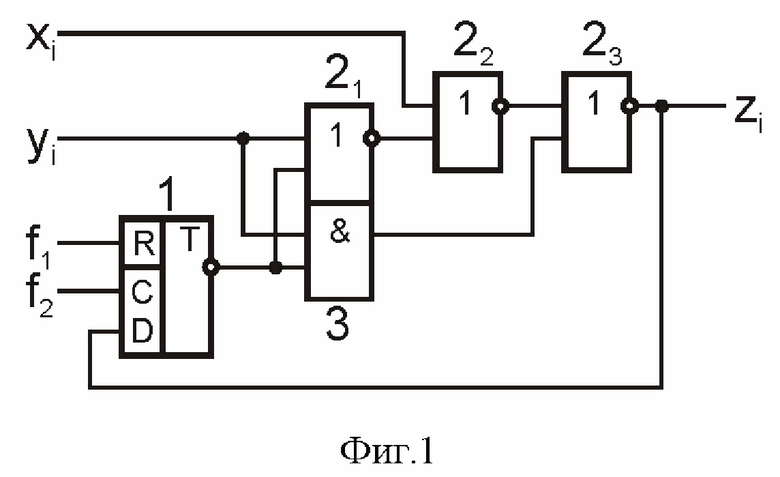

На фиг.1 и фиг.2 представлены соответственно схема предлагаемого компаратора двоичных чисел и временные диаграммы, поясняющие принцип его работы.

Компаратор двоичных чисел содержит D-триггер 1, элементы ИЛИ-НЕ 21, 22, 23, элемент И 3, причем первый, второй входы и выход элемента 21 соединены соответственно с первым, вторым входами элемента 3 и вторым входом элемента 22, инвертирующий выход D-триггера 1, подключенного входом данных к выходу элемента 23, и выходы элементов 22, 3 соединены соответственно с вторым входом элемента 3 и первым, вторым входами элемента 23, а первые входы элементов 21, 22 и выход элемента 23 подключены соответственно к первому, второму информационным входам и выходу компаратора двоичных чисел, первый и второй управляющие входы которого соединены соответственно с входом сброса и тактовым входом D-триггера 1.

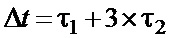

Работа предлагаемого компаратора двоичных чисел осуществляется следующим образом. На его первый, второй управляющие входы подаются соответственно импульсные сигналы  (фиг.2), причем период T сигнала

(фиг.2), причем период T сигнала  должен удовлетворять условию

должен удовлетворять условию  , где

, где  , а

, а  и

и  есть длительности задержек, вносимых D-триггером и элементом ИЛИ-НЕ. Синхронно с передним фронтом импульса сигнала

есть длительности задержек, вносимых D-триггером и элементом ИЛИ-НЕ. Синхронно с передним фронтом импульса сигнала  , передними фронтами первого,…,(

, передними фронтами первого,…,( )-го импульсов сигнала

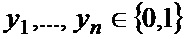

)-го импульсов сигнала  на первый и второй информационные входы предлагаемого компаратора последовательно подаются двоичные сигналы

на первый и второй информационные входы предлагаемого компаратора последовательно подаются двоичные сигналы  и

и  соответственно (фиг.2), которые задают подлежащие сравнению n-разрядные двоичные числа

соответственно (фиг.2), которые задают подлежащие сравнению n-разрядные двоичные числа  и

и  (

( ,

,  задают значения старших, а

задают значения старших, а  ,

,  - младших разрядов). Тогда сигнал на выходе предлагаемого компаратора будет определяться рекуррентным выражением

- младших разрядов). Тогда сигнал на выходе предлагаемого компаратора будет определяться рекуррентным выражением

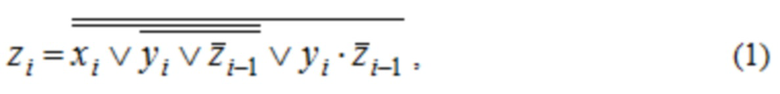

где  есть номер момента времени

есть номер момента времени  (фиг.2); ⋅,

(фиг.2); ⋅,  - есть символы логических операций И, ИЛИ, НЕ;

- есть символы логических операций И, ИЛИ, НЕ;  . В представленной ниже таблице приведены значения реализуемой выражением (1) функции на всех возможных наборах значений ее аргументов.

. В представленной ниже таблице приведены значения реализуемой выражением (1) функции на всех возможных наборах значений ее аргументов.

Анализ данных, приведенных в таблице, позволяет заключить, что: 1) если  или

или  и

и  , то

, то  ; 2) если

; 2) если  или

или  и

и  , то

, то  . Таким образом, при

. Таким образом, при  на выходе предлагаемого компаратора получим

на выходе предлагаемого компаратора получим

.

.

Вышеизложенные сведения позволяют сделать вывод, что предлагаемый компаратор двоичных чисел построен на основе булевого операционного базиса и формирует признак соотношения  , где

, где  есть n-разрядные двоичные числа, задаваемые двоичными сигналами, при этом схема предлагаемого компаратора двоичных чисел проще чем у прототипа, поскольку цена по Квайну комбинационной части предлагаемого компаратора равна 8.

есть n-разрядные двоичные числа, задаваемые двоичными сигналами, при этом схема предлагаемого компаратора двоичных чисел проще чем у прототипа, поскольку цена по Квайну комбинационной части предлагаемого компаратора равна 8.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО СРАВНЕНИЯ ДВОИЧНЫХ ЧИСЕЛ | 2024 |

|

RU2841043C1 |

| УСТРОЙСТВО СРАВНЕНИЯ ДВОИЧНЫХ ЧИСЕЛ | 2020 |

|

RU2757823C1 |

| ЛОГИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2016 |

|

RU2641446C2 |

| ЛОГИЧЕСКИЙ МОДУЛЬ | 2023 |

|

RU2812687C1 |

| ЛОГИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ | 2023 |

|

RU2803625C1 |

| ЛОГИЧЕСКИЙ МОДУЛЬ | 2023 |

|

RU2809209C1 |

| КОМПАРАТОР ДВОИЧНЫХ ЧИСЕЛ | 2022 |

|

RU2791455C1 |

| КОМПАРАТОР ДВОИЧНЫХ ЧИСЕЛ | 2017 |

|

RU2649296C1 |

| ПОРОГОВЫЙ МОДУЛЬ ДЛЯ РЕАЛИЗАЦИИ ПОРОГОВОЙ ФУНКЦИИ С ЕДИНИЧНЫМИ ВЕСАМИ АРГУМЕНТОВ И ПОРОГОМ ТРИ | 2023 |

|

RU2809206C1 |

| КОМПАРАТОР ДВОИЧНЫХ ЧИСЕЛ | 2022 |

|

RU2787333C1 |

Изобретение относится к вычислительной технике и может быть использовано для построения средств автоматики и функциональных узлов систем управления. Технический результат заключается в упрощении схемы компаратора двоичных чисел за счет уменьшения цены по Квайну комбинационной части компаратора двоичных чисел при сохранении функциональных возможностей и логического операционного базиса. Компаратор двоичных чисел содержит элемент И и D-триггер, причем вход сброса, тактовый вход и вход данных D-триггера подключены соответственно к первому, второму управляющим входам и выходу компаратора двоичных чисел, первый информационный вход которого соединен с первым входом элемента И, три элемента ИЛИ-НЕ, первый, второй входы и выход первого элемента ИЛИ-НЕ подключены соответственно к первому, второму входам элемента И и второму входу второго элемента ИЛИ-НЕ, а второй вход и выход элемента И соединены соответственно с инвертирующим выходом D-триггера и вторым входом третьего элемента ИЛИ-НЕ, подключенного первым входом и выходом соответственно к выходу второго элемента ИЛИ-НЕ и выходу компаратора двоичных чисел, второй информационный вход которого соединен с первым входом второго элемента ИЛИ-НЕ. 2 ил., 1 табл.

Компаратор двоичных чисел, содержащий элемент И и D-триггер, причем вход сброса, тактовый вход и вход данных D-триггера подключены соответственно к первому, второму управляющим входам и выходу компаратора двоичных чисел, первый информационный вход которого соединен с первым входом элемента И, отличающийся тем, что в него дополнительно введены три элемента ИЛИ-НЕ, первый, второй входы и выход первого элемента ИЛИ-НЕ подключены соответственно к первому, второму входам элемента И и второму входу второго элемента ИЛИ-НЕ, а второй вход и выход элемента И соединены соответственно с инвертирующим выходом D-триггера и вторым входом третьего элемента ИЛИ-НЕ, подключенного первым входом и выходом соответственно к выходу второго элемента ИЛИ-НЕ и выходу компаратора двоичных чисел, второй информационный вход которого соединен с первым входом второго элемента ИЛИ-НЕ.

| КОМПАРАТОР ДВОИЧНЫХ ЧИСЕЛ | 2020 |

|

RU2757832C1 |

| КОМПАРАТОР ДВОИЧНЫХ ЧИСЕЛ | 2017 |

|

RU2649296C1 |

| US 20030023654 A1, 30.01.2003 | |||

| KR 101081327 B1, 09.11.2011 | |||

| US 3479644 A1, 18.11.1969. | |||

Авторы

Даты

2023-01-09—Публикация

2022-03-18—Подача