Предлагаемое изобретение относится к элементам вычислительной техники, устройствам автоматики и может быть использовано в быстродействующих схемах вычислительной техники и автоматики при построении сумматоров, реверсивных счетных устройств, в устройствах поразрядного суммирования по модулю два двоичных импульсных сигналов и т.д.

Известно устройство логического элемента «Исключающее ИЛИ» (АС СССР № 250995, МПК H03K. Опубл. 26.08.1969. БИ № 27), включающее шесть транзисторов n-p-n-типа и одиннадцать резисторов. В этом устройстве транзисторы объединены в две группы по три транзистора в каждой (первый, второй, третий транзисторы) и (четвертый, пятый, шестой транзисторы). В каждой группе эмиттеры транзисторов объединены между собой и через шестой и девятый резисторы соединены с шиной источника отрицательного напряжения питания. Второй и восьмой резисторы своими выводами соединены с коллектором первого транзистора. К этому узлу подключена и база пятого транзистора. Пятый и одиннадцатый резисторы своими выводами соединены с коллектором четвертого транзистора. К этому узлу подключена и база второго транзистора. Первый и седьмой резисторы своими выводами соединены с коллектором второго транзистора. К этому узлу подключена и база третьего транзистора. Десятый и третий резисторы своими выводами соединены с коллектором пятого транзистора. К этому узлу подключена и база шестого транзистора. Первые выводы второго, пятого, седьмого, девятого и десятого резисторов подключены к шине источника отрицательного напряжения питания. Вторые выводы первого, восьмого, третьего, четвертого и одиннадцатого резисторов подключены к общей шине. Коллектора третьего и шестого транзисторов соединены с первым выводом четвертого резистора. Этот узел соединения является выходом устройства. База первого транзистора является первым входом устройства, а база четвертого транзистора является вторым входом устройства.

Признаками аналога, совпадающими с признаками заявляемого технического решения, являются наличие пяти транзисторов n-p-n-типа, и четырех резисторов, где эмиттеры первого и второго транзисторов соединены между собой, эмиттеры четвертого и пятого транзисторов также соединены между собой. База первого транзистора является первым входом устройства, а база четвертого транзистора является вторым входом устройства. Коллектор второго транзистора соединен с первым выводом первого резистора. Коллектор пятого транзистора соединен с первым выводом третьего резистора. Вторые выводы первого и третьего резисторов подключены к общей шине. Первый вывод второго резистора соединен с шиной источника отрицательного напряжения питания. Коллектор третьего транзистора соединен с первым выводом четвертого резистора. Этот узел соединения является выходом устройства. Второй вывод четвертого резистора соединен с общей шиной.

К недостаткам аналога можно отнести следующее. В этом устройстве второй и пятый транзисторы при обеспечении запирания третьего и шестого транзисторов могут переходить в режим насыщения. Это приводит к накоплению большого заряда в областях p-n-переходов коллектор-база второго и пятого транзисторов, что вызовет существенное снижение быстродействия устройства, поскольку при переключении устройства потребуется время на рассасывание этого заряда. Кроме этого логический элемент «Исключающее ИЛИ» не имеет резко выраженного порога переключения, что снижает его чувствительность и надежность функционирования.

Известно устройство логического элемента «Исключающее ИЛИ» (Будинский Я. Логические цепи в цифровой технике. М.: «Связь». 1977, С.372, рис. 7.87). В этом логическом элементе имеются восемь биполярных транзисторов n-p-n-типа и три резистора. Эмиттеры первого и второго транзисторов соединены между собой и с коллектором шестого транзистора. Эмиттеры пятого и четвертого транзисторов соединены между собой и с коллектором седьмого транзистора. Эмиттеры шестого и седьмого транзисторов соединены между собой и с коллектором восьмого транзистора. Коллекторы первого и пятого транзисторов соединены с базой третьего транзистора и со вторым выводом первого резистора. Первый вывод первого резистора и коллекторы второго, четвертого и третьего транзисторов соединены с общей шиной. Базы первого и четвертого транзисторов соединены между собой и представляют первый вход устройства. База шестого транзистора является вторым входом устройства. Эмиттер восьмого транзистора соединен с первым выводом второго резистора. Эмиттер третьего транзистора соединен с первым выводом третьего резистора. Этот узел соединения является выходом устройства. Вторые выводы второго и третьего резисторов соединены с шиной источника отрицательного напряжения питания. Базы второго и пятого транзисторов соединены между собой и на них подается первое опорное напряжение E01. На базу седьмого транзистора подается второе опорное напряжение E02. На базу восьмого транзистора подается третье опорное напряжение E03.

Признаками аналога, совпадающими с признаками заявляемого технического решения, являются наличие пяти биполярных транзисторов n-p-n-типа и трех резисторов, где эмиттеры первого и второго транзисторов соединены между собой. Эмиттеры четвертого и пятого транзисторов соединены между собой. Базы второго и пятого транзисторов соединены между собой и на них подается опорное напряжение. Первый вывод первого резистора и коллектора третьего и четвертого транзисторов соединены с общей шиной. Эмиттер третьего транзистора соединен с шиной, представляющей выход устройства.

К недостаткам аналога следует отнести следующее. Схема логического элемента «Исключающее ИЛИ» представляет собой трехярусное включение транзисторов. В этом случае можно отметить, что при учете падения напряжения на первом резисторе 0,8 В (ЭСЛ-логика) и втором резисторе не менее одного вольта (этот резистор обеспечивает термостабилизацию тока в цепи), на каждом из трех последовательно включенных транзисторах (между коллектором и эмиттером транзистора) будет падать напряжение не более 1,1 В. Пусть контактная разность потенциала p-n-перехода равна 0,75 В. Тогда напряжение обратного смещения p-n-перехода база-коллектор транзисторов будет равно 1,1 – 0,75 = 0,35 В. В этом случае при подаче высокого уровня сигнала на базу транзистора p-n-переход база-коллектор транзистора (напрнимер, первый транзистор) получит прямое смещение величиной 0,05 В. Это говорит о том, что в этом устройстве барьерная емкость p-n-перехода база-коллектор транзистора будет иметь максимальную величину, что приводит к снижению быстродействия устройства. Следует отметить, что наличие трех опорнях напряжений, необходимых для нормального функционирования аналога, потребует наличия трех источников опорного напряжения. Подобное усложнение аналога будет снижать его надежность. Кроме этого можно отметить, что в аналоге отсутствует возможность увеличения амплитуды выходного сигнала, по причинам отмеченным выше, а это снижает его функциональные возможности.

Из известных технических решений наиболее близким по технической сущности к заявляемому является логический элемент исключительное ИЛИ (АС СССР 1045397, МПК H03K 19/21, Аврамов В.Г., Рогов Ю.Н., опубл. 30 сентября 1983, Бюл. № 36). В этом устройстве имеются семь транзистора n-p-n-типа, девять резисторов и два диода Шоттки. Эмиттеры первого и второго транзисторов соединены между собой, с катодом первого диода и с первым выводом второго резистора. Эмиттеры четвертого и пятого транзисторов соединены между собой, с катодом второго диода и с первым выводом восьмого резистора. База второго транзистора соединена со вторым выводом седьмого резистора и анодом второго диода. База пятого транзистора соединена со вторым выводом девятого резистора и анодом первого диода. Коллекторы второго и пятого транзисторов соединены с базой третьего транзистора и со вторым выводом третьего резистора. База шестого транзистора соединена с коллектором первого транзистора и со вторым выводом первого резистора. База седьмого транзистора соединена с коллектором четвертого транзистора и со вторым выводом пятого резистора. Коллекторы третьего, шестого и седьмого транзисторов соединены с общей шиной. Первые выводы первого, седьмого, третьего, девятого и пятого резисторов соединены с общей шиной. База первого транзистора является первым входом устройства. База четвертого транзистора является вторым входом устройства. Эмиттеры шестого и седьмого транзисторов соединены с первым выводом шестого резистора. На выходе данного узла соединения появляется сигнал, отвечающий функции «Исключающее ИЛИ». Эмиттер третьего транзистора соединен с первым выводом четвертого резистора. На выходе данного узла соединения появляется сигнал, отвечающий функции «Исключающее ИЛИ с инверсией». Вторые выводы шестого, второго, восьмого и четвертого резисторов соединены с шиной источника отрицательного напряжения питания.

Признаками прототипа, совпадающими с признаками заявляемого технического решения, являются наличие пяти транзисторов n-p-n-типа и четырех резисторов. Эмиттеры первого и второго транзисторов соединены между собой. Эмиттеры четвертого и пятого транзисторов соединены между собой. Первые выводы первого и третьего резисторов и коллектор третьего транзистора соединены с общей шиной. Вторые выводы второго и четвертого резисторов соединены с шиной источника отрицательного напряжения питания. Эмиттер третьего транзистора соединен с первым выводом четвертого резистора. База первого транзистора является первым входом устройства. База четвертого транзистора является вторым входом устройства. Второй вывод третьего резистора соединен с коллектором пятого транзистора.

Прототипу свойственны следующие недостатки. Наличие диодов Шоттки в прототипе приводит к тому, что например, при низких потенциалах на первом и втором входах прототипа (логические нули) ток, протекающий через второй резистор, должен переключиться с первого транзистора на второй. Однако часть тока будет замыкаться через диоды Шоттки в седьмой и девятый резисторы. В зависимости от величины сопротивлений седьмого и девятого резисторов эта часть тока при малых сопротивлениях может быть существенной, что приведет к малому размаху логических уровней выходного сигнала (не будет соответствовать ЭСЛ логике). Это снижает надежность функционирования прототипа. Для снижения степени влияния этого недостатка на функционирование прототипа сопротивления резисторов, включенных между базами второго и пятого транзисторов и общей шиной, имели бы большую величину с целью снижения части тока, которая ответвляется в диоды Шоттки. Однако, наличие больших сопротивлений резисторов, подключенных к базам второго и пятого транзисторов приведет к росту постоянных времени узлов баз второго и пятого транзисторов и соответственно к снижению быстродействия прототипа.

Технический результат логического элемента «Исключающее ИЛИ» состоит в том, что он позволяет повысить надежность функционирования и расширить функциональные возможности логических элементов подобного типа.

Доказательство наличия причинно-следственной связи между заявляемой совокупностью признаков и достигаемым техническим результатом приводится далее.

Для достижения технического результата в известное устройство дополнительно введены: два транзистора p-n-p-типа и два источника тока.

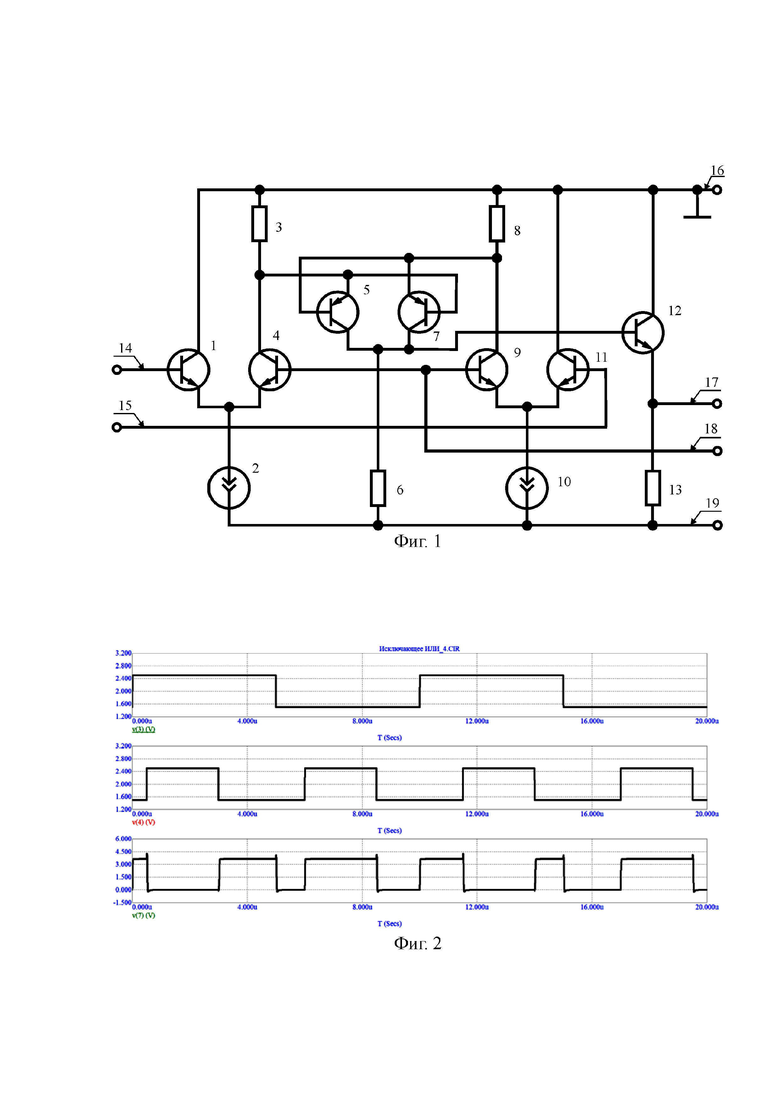

Технический результат достигается тем, что в логический элемент «Исключающее ИЛИ», содержащий первый 1, второй 4, третий 12, четвертый 11 и пятый 9 транзисторы n-p-n-типа и первый 3, второй 6, третий 8 и четвертый 13 резисторы, где эмиттеры первого 1 и второго 4 транзисторов соединены между собой. Эмиттеры четвертого 11 и пятого 9 транзисторов соединены между собой. Первые выводы первого 3 и третьего 8 резисторов и коллектор третьего 12 транзистора соединены с общей шиной 16. Вторые выводы второго 6 и четвертого 13 резисторов соединены с шиной источника отрицательного напряжения питания 19. Эмиттер третьего 12 транзистора соединен с первым выводом четвертого 13 резистора. База первого 1 транзистора является первым входом 14 устройства. База четвертого 11 транзистора является вторым входом 15 устройства. Второй вывод третьего 8 резистора соединен с коллектором пятого 9 транзистора, введены шестой 5 и седьмой 7 транзисторы p-n-p-типа, первый 2 и второй 10 источники тока, причем эмиттер шестого 5 транзистора соединен с базой седьмого 7 транзистора, с коллектором второго 4 транзистора и со вторым выводом первого 3 резистора. Эмиттер седьмого 7 транзистора соединен с базой шестого 5 транзистора и с узлом соединения коллектора пятого 9 транзистора и второго вывода третьего 8 резистора. Коллекторы первого 1 и четвертого 11 транзисторов соединены с общей шиной 16. Коллекторы шестого 5 и седьмого 7 транзисторов соединены с базой третьего 12 транзистора и с первым выводом второго 6 резистора. Первый вывод первого источника тока 2 соединен с узлом соединения эмиттеров первого 1 и второго 4 транзисторов. Первый вывод второго источника тока 10 соединен с узлом соединения эмиттеров четвертого 11 и пятого 9 транзисторов. Вторые выводы первого 2 и второго 10 источников тока соединены с шиной 19 источника отрицательного напряжения питания. Базы второго 4 и пятого 9 транзисторов соединены между собой и с шиной 18 подачи опорного напряжения. Узел соединения эмиттера третьего 12 транзистора и первого вывода четвертого 13 резистора является выходом 17 логического элемента «Исключающее ИЛИ».

Сущность предлагаемого устройства поясняется чертежами.

На фиг. 1 представлена схема электрическая принципиальная логического элемента «Исключающее ИЛИ».

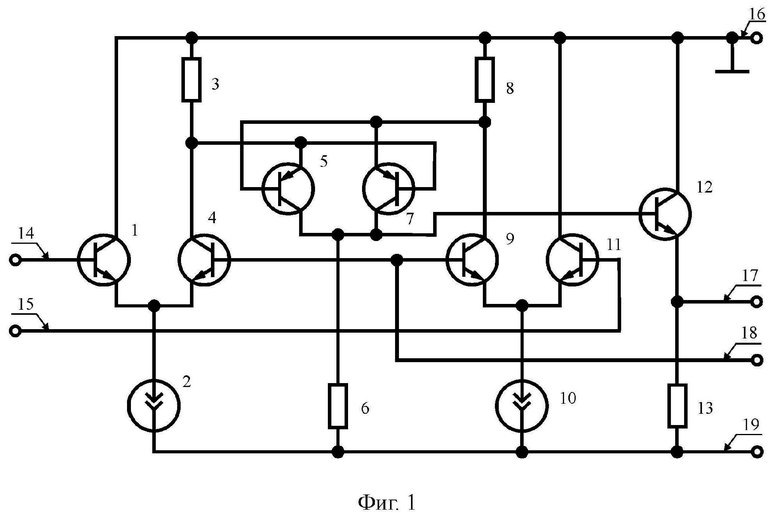

На фиг. 2 представлены диаграммы первого входного сигнала (верхняя диаграмма), второго входного сигнала (средняя диаграмма) и сигнала на выходе логического элемента «Исключающее ИЛИ» (нижняя диаграмма).

Диаграммы, представленные на фиг. 2, получены путем моделирования логического элемента «Исключающее ИЛИ» (фиг. 1). Моделирование выполнено с использованием программы схемотехнического моделирования Micro-Cap 9.

Логический элемент «Исключающее ИЛИ», содержит первый 1, второй 4, третий 12, четвертый 11 и пятый 9 транзисторы n-p-n-типа, шестой 5 и седьмой 7 транзисторы p-n-p-типа, первый 3, второй 6, третий 8 и четвертый 13 резисторы, первый 2 и второй 10 источники тока. Эмиттеры первого 1 и второго 4 транзисторов и первый вывод первого 2 источника тока соединены между собой. Эмиттеры четвертого 11 и пятого 9 транзисторов и первый вывод второго 10 источника тока соединены между собой. Первые выводы первого 3 и третьего 8 резисторов и коллекторы первого 1, третьего 12 и четвертого 11 транзисторов соединены с общей шиной 16. Вторые выводы второго 6 и четвертого 13 резисторов и вторые выводы первого 2 и второго 10 источников тока соединены с шиной источника отрицательного напряжения питания 19. Эмиттер третьего 12 транзистора соединен с первым выводом четвертого 13 резистора и является выходом 17 устройства. База первого 1 транзистора является первым входом 14 устройства. База четвертого 11 транзистора является вторым входом 15 устройства. Второй вывод третьего 8 резистора, коллектор пятого 9 транзистора, эмиттер седьмого 7 транзистора и база шестого 5 транзистора соединены между собой. Коллектор второго 4 транзистора, второй вывод первого 3 резистора, эмиттер шестого 5 транзистора и база седьмого 7 транзистора соединены между собой. Коллекторы шестого 5 и седьмого 7 транзисторов соединены с базой третьего 12 транзистора и с первым выводом второго 6 резистора. Базы второго 4 и пятого 9 транзисторов соединены между собой и с шиной 18 подачи опорного напряжения.

Работает логический элемент «Исключающее ИЛИ» следующим образом. К базам второго 4 и пятого 9 транзисторов по шине 18 прикладывается опорное напряжение – E0, имеющее отрицательный знак.

Поскольку рассматриваем работу логического элемента «Исключающее ИЛИ», то учитываем, что логический элемент имеет первый 14 и второй 15 входы, на которые могут прикладываться сигналы, имеющие уровень «логический нуль», величина которого ниже (по модулю больше) опорного напряжения - E0, и «логическая единица», величина которого выше (по модулю меньше) опорного напряжения - E0.

Пусть на первый 14 и второй 15 входы логического элемента прикладываются сигналы «логический нуль». В этом случае ток первого источника тока 2 будет протекать через второй транзистор 4, обеспечивая падение напряжения на первом резисторе 3. Ток второго источника тока 10 будет протекать через пятый транзистор 9, обеспечивая падение напряжения на третьем резисторе 8. Токи первого 2 и второго 10 источников тока одинаковы, а также сопротивления первого 3 и третьего 8 резисторов одинаковы. В результате этого шестой 5 и седьмой 7 транзисторы будут заперты, поскольку потенциалы на p-n-переходах база-эмиттер этих транзисторов будут равны нулю. В результате этого на выходе 17 логического элемента появится сигнал, имеющий уровень «логического нуля».

При подаче на первый 14 и второй 15 входы логического элемента сигналов «логическая единица» ток первого источника тока 2 будет протекать через первый транзистор 1. В этом случае падение напряжения на первом резисторе 3 будет отсутствовать. Ток второго источника тока 10 будет протекать через четвертый транзистор 11. Падение напряжения на третьем резисторе 8 будет отсутствовать. В результате этого шестой 5 и седьмой 7 транзисторы будут заперты, поскольку потенциалы на p-n-переходах база-эмиттер этих транзисторов будут равны нулю. В результате этого на выходе 17 логического элемента появится сигнал, имеющий уровень «логического нуля».

При подаче на первый 14 вход логического элемента сигнала «логический нуль», а на второй 15 вход логического элемента сигнала «логическая единица» ток первого источника тока 2 будет протекать через второй транзистор 4. В этом случае на первом резисторе 3 будет обеспечено падение напряжения. Ток второго источника тока 10 будет протекать через четвертый транзистор 11. Падение напряжения на третьем резисторе 8 будет отсутствовать. В результате этого шестой 5 транзистор будет заперт, а седьмой транзистор 7 откроется и через него начнет протекать ток, обеспечивая падение напряжения на сопротивлении второго резистора 6. В этом случае на выходе логического элемента 17 установится сигнал «логическая единица».

При подаче на первый 14 вход логического элемента сигнала «логическая единица», а на второй 15 вход логического элемента сигнала «логический нуль» ток первого источника тока 2 будет протекать через первый транзистор 1. В этом случае на первом резисторе 3 падение напряжения будет отсутствовать. Ток второго источника тока 10 будет протекать через пятый транзистор, что приведет к падению напряжения на третьем резисторе 8. В результате этого седьмой 7 транзистор будет заперт, а шестой транзистор 5 откроется и через него начнет протекать ток, обеспечивая падение напряжения на сопротивлении второго резистора 6. В этом случае на выходе логического элемента 17 установится сигнал «логическая единица».

В заявляемом логическом элементе «Исключающее ИЛИ» сигналы к первому и второму входам прикладываются относительно уровня опорного напряжения, прикладываемого к базам второго и пятого транзисторов, где уровень «логический нуль» будет ниже уровня опорного напряжения, а уровень «логическая единица» будет выше уровня опорного напряжения. Кроме этого, к узлам соединения базы шестого и эмиттера седьмого транзисторов и базы седьмого и эмиттера шестого транзисторов будут прикладываться разноуровневые сигналы при приложении к первому входу уровня «логический нуль» («логическая единица»), а ко второму входу уровня «логическая единица» («логический нуль»), что повышает надежность функционирования логического элемента. При этом уровни сигналов, прикладываемых к входным зажимам, и уровни сигналов на выходе логического элемента «Исключающее ИЛИ» могут соответствовать логическим элементам, изготавливаемых по различным технологиям (ЭСЛ, ТТЛ, ТТЛШ и др.), что расширяет функциональные возможности логических элементов «Исключающее ИЛИ».

Таким образом, доказана практическая реализуемость заявляемого устройства логического элемента «Исключающее ИЛИ».

Промышленная применимость этого устройства возможна в технике быстродействующих схем вычислительной техники и автоматики при построении сумматоров, реверсивных счетных устройств, в устройствах поразрядного суммирования по модулю два двоичных импульсных сигналов и т.д.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ «ИСКЛЮЧАЮЩЕЕ ИЛИ» | 2022 |

|

RU2795286C1 |

| ТРОИЧНЫЙ ТРИГГЕР | 2003 |

|

RU2237968C1 |

| КЛЮЧ ПЕРЕМЕННОГО ТОКА | 2018 |

|

RU2685694C1 |

| ТРИГГЕРНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ 2И-ИЛИ/2И-ИЛИ-НЕ | 2024 |

|

RU2829649C1 |

| Транзисторный инвертор | 1991 |

|

SU1815775A1 |

| ПИКОВЫЙ ДЕТЕКТОР | 2009 |

|

RU2409818C1 |

| Триггерный логический элемент ИЛИ/ИЛИ-НЕ | 2021 |

|

RU2767177C1 |

| Источник вторичного электропитания для сети постоянного напряжения | 1990 |

|

SU1786476A1 |

| Высоковольтный логический элемент | 1989 |

|

SU1690189A1 |

| БЕСКОНТАКТНЫЙ СЛЕДЯЩИЙ ЭЛЕКТРОПРИВОД | 2001 |

|

RU2187195C2 |

Изобретение относится к вычислительной технике. Технический результат заключается в расширении арсенала технических средств. Технический результат достигается за счет того, что дополнительно введены шестой и седьмой транзисторы p-n-p-типа, первый и второй источники тока, причем эмиттер шестого транзистора соединен с базой седьмого транзистора, с коллектором второго транзистора и со вторым выводом первого резистора. 2 ил.

Логический элемент «Исключающее ИЛИ», содержащий первый, второй, третий, четвертый и пятый транзисторы n-p-n-типа и первый, второй, третий и четвертый резисторы, где эмиттеры первого и второго транзисторов соединены между собой, эмиттеры четвертого и пятого транзисторов соединены между собой, первые выводы первого и третьего резисторов и коллектор третьего транзистора соединены с общей шиной, вторые выводы второго и четвертого резисторов соединены с шиной источника отрицательного напряжения питания, эмиттер третьего транзистора соединен с первым выводом четвертого резистора, база первого транзистора является первым входом устройства, база четвертого транзистора является вторым входом устройства, второй вывод третьего резистора соединен с коллектором пятого транзистора, отличающийся тем, что в него дополнительно введены шестой и седьмой транзисторы p-n-p-типа, первый и второй источники тока, причем эмиттер шестого транзистора соединен с базой седьмого транзистора, с коллектором второго транзистора и со вторым выводом первого резистора, эмиттер седьмого транзистора соединен с базой шестого транзистора и с узлом соединения коллектора пятого транзистора и второго вывода третьего резистора, коллекторы первого и четвертого транзисторов соединены с общей шиной, коллекторы шестого и седьмого транзисторов соединены с базой третьего транзистора и с первым выводом второго резистора, первый вывод первого источника тока соединен с узлом соединения эмиттеров первого и второго транзисторов, первый вывод второго источника тока соединен с узлом соединения эмиттеров четвертого и пятого транзисторов, вторые выводы первого и второго источников тока соединены с шиной источника отрицательного напряжения питания, базы второго и пятого транзисторов соединены между собой и с шиной подачи опорного напряжения, узел соединения эмиттера третьего транзистора и первого вывода четвертого резистора является выходом логического элемента «Исключающее ИЛИ».

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ "ИСКЛЮЧАЮЩЕЕ ИЛИ" С МНОГОЗНАЧНЫМ ВНУТРЕННИМ ПРЕДСТАВЛЕНИЕМ СИГНАЛОВ | 2012 |

|

RU2506695C1 |

| US 6727728 B1, 27.04.2004 | |||

| US 7088138 B2, 08.08.2006 | |||

| Логический элемент Исключающее ИЛИ | 1982 |

|

SU1072264A1 |

| Логический элемент И-Исключающее ИЛИ | 1981 |

|

SU1008910A1 |

Авторы

Даты

2023-03-22—Публикация

2022-12-14—Подача