Изобретение относится к области компьютерной технике и может быть использовано в автоматизированных системах для выполнения комплексных математических операций с целью выделения сигналов на фоне пассивных помех с априорно неизвестной доплеровской фазой.

Известно радиолокационное устройство для обнаружения движущейся цели [1], содержащее последовательно включенные блоки задержки, перемножитель комплексных чисел и вычитатель. Однако это устройство обладает низкой эффективностью выделения сигнала движущейся цели.

Другим известным устройством является корреляционный автокомпенсатор [2], который содержит ряд блоков задержки, два перемножителя, сумматор и блок оценки параметров коррелированной помехи. Недостатком этого устройства является плохое подавление кромок протяженной помехи из-за большой постоянной времени цепи адаптивной обратной связи.

Наиболее близкое к данному изобретению цифровое устройство для подавления пассивных помех [3], выбранное в качестве прототипа, содержит весовой блок, комплексный сумматор и блоки задержки. Однако данное устройство имеет потери в эффективности режекции помех.

Задачей, решаемой в изобретении, является повышение эффективности компенсации пассивной помехи и выделения сигналов движущихся целей при обработке сигналов от цели на фоне пассивных помех с априорно неизвестной доплеровской фазой.

Для решения поставленной задачи в вычислитель для компенсации помех, содержащий первый блок задержки, комплексный сумматор и синхрогенератор, введены второй и третий блоки задержки, комплексный перемножитель, комплексный инвертор и измеритель доплеровской фазы, соединенные между собой определенным образом.

Сущность изобретения как технического решения характеризуется совокупностью существенных признаков, изложенных в формуле изобретения и обеспечивающих решение поставленной задачи путем оптимальной и согласованной обработки поступающих импульсов.

Технический результат изобретения состоит в повышении эффективности компенсации пассивной помехи с априорно неизвестной доплеровской фазой и выделения сигналов движущихся целей.

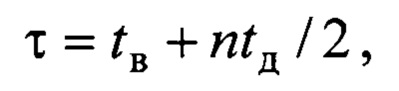

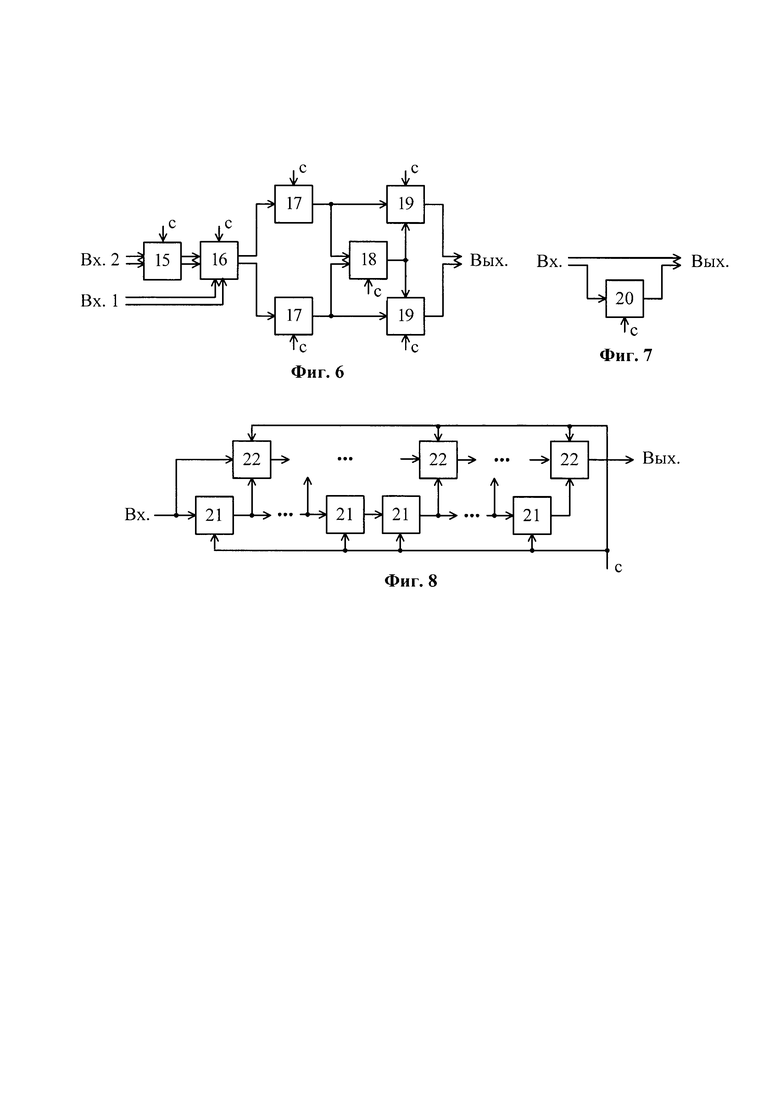

На фиг. 1 представлена структурная электрическая схема вычислителя для компенсации помех; на фиг. 2 - блока задержки; на фиг. 3 - комплексного сумматора; на фиг. 4 - комплексного перемножителя; фиг. 5 - комплексного инвертора; на фиг. 6 - измерителя доплеровской фазы; на фиг. 7 - блока комплексного сопряжения; на фиг. 8 - накопителя.

Вычислитель для компенсации помех (фиг. 1) содержит, блоки 1, 4, 5 задержки, комплексный сумматор 2, синхрогенератор 3, комплексный перемножитель 6, комплексный инвертор 7 и измеритель 8 доплеровской фазы.

Блоки 1, 4, 5 задержки (фиг. 2) содержат две линии 9 задержки; комплексный сумматор 2 (фиг. 3) содержит два сумматора 10; комплексные перемножители 6, 16 (фиг. 4) содержат два канала (I, II), каждый из которых включает первый и второй перемножители 11, 12 и сумматор 13; комплексный инвертор 7 (фиг. 5) содержат два инвертора знака 14; измеритель 8 доплеровской фазы (фиг. 6) содержит блок 15 комплексного сопряжения, комплексный перемножитель 16, два накопителя 17, блок 18 вычисления модуля и два делителя 19; блок 15 комплексного сопряжения (фиг. 7) содержит инвертор знака 20; каждый накопитель 17 (фиг. 8) содержит n элементов 21 задержки на интервал tд и n сумматоров 22.

Вычислитель для компенсации помех может быть осуществлен следующим образом.

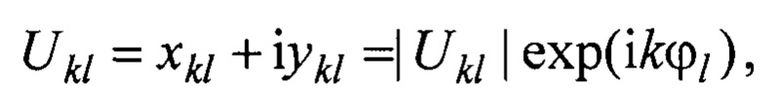

Поступающие на вход заявляемого устройства (фиг. 1) цифровые отсчеты (xkl, ykl) следуют через период повторения T и в каждом элементе разрешения по дальности (кольце дальности) каждого периода повторения образуют последовательность комплексных чисел

где k - номер текущего периода, l - номер текущего кольца дальности, ϕl - доплеровский сдвиг фазы за период повторения (доплеровская фаза), обычно помехи, ввиду ее значительного превышения над сигналом.

Цифровые отсчеты в заявляемом устройстве (фиг. 1) поступают на соединенные входы второго блока 4 задержки (фиг. 2) на интервал τ и первые входы измерителя 8 доплеровской фазы (фиг. 6). На вторые входы измерителя 8 доплеровской фазы поступают отсчеты с выхода первого блока 1 задержки на интервал Т - τ. Отсчеты на первых и вторых входах измерителя 8 доплеровской фазы разделены на интервал Т.

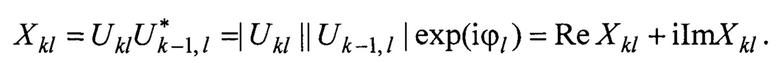

В инверторе 20 (фиг. 7) блока 15 комплексного сопряжения измерителя 8 (фиг. 6) происходит инвертирование знака мнимых проекций задержанных отсчетов. В комплексном перемножителе 16 происходит перемножение соответствующих комплексных чисел, реализуемое путем операций с проекциями этих чисел в соответствии с фиг. 4 и приводящее к образованию величин

В накопителях 17 (фиг. 6) с помощью элементов 21 задержки и сумматоров 22 (фиг. 8) осуществляется скользящее вдоль дальности в каждом периоде повторения суммирование проекций Re Xkl и Im Xkl с n+1 смежных элементов разрешения по дальности временного строба, кроме элемента с номером n/2+1, для чего выходные величины элемента 21 задержки с номером n/2 поступают только на последующий элемент 21 задержки (фиг. 8). В результате накопления образуются величины

где  - оценка доплеровского сдвига фазы помехи за период повторения Т, усредненная по n смежным элементам разрешения по дальности.

- оценка доплеровского сдвига фазы помехи за период повторения Т, усредненная по n смежным элементам разрешения по дальности.

В блоке 18 вычисления модуля определяются величины  , а затем на выходах делителей 19 (фиг. 6) - величины

, а затем на выходах делителей 19 (фиг. 6) - величины  , поступающие на вторые входы комплексного перемножителя 6. Накопление n отсчетов обеспечивает высокоточное измерение величины

, поступающие на вторые входы комплексного перемножителя 6. Накопление n отсчетов обеспечивает высокоточное измерение величины  .

.

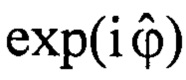

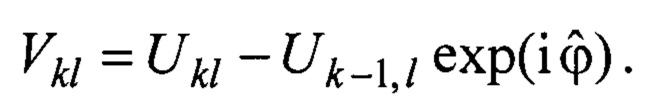

Третий блок 5 задержки на интервал τ совместно с первым блоком 1 задержки на интервал Т-τ образуют результирующую задержку на интервал Т. В результате на входы комплексного сумматора 2 отсчеты поступают синхронно. С учетом комплексного перемножения с величиной  , инвертирования знаков в инверторах 14 (фиг. 5) задержанных отсчетов и синфазных суммирований в комплексном сумматоре 2 на выходе последнего отсчеты остатков помехи имеют вид

, инвертирования знаков в инверторах 14 (фиг. 5) задержанных отсчетов и синфазных суммирований в комплексном сумматоре 2 на выходе последнего отсчеты остатков помехи имеют вид

Двумерный поворот задержанных отсчетов в комплексном перемножителе 6 на угол  обеспечивает необходимую для компенсации помехи синфазность суммируемых отсчетов. Отсчеты сигнала от движущейся цели из-за сохранения доплеровских сдвигов фазы сигнала не подавляются.

обеспечивает необходимую для компенсации помехи синфазность суммируемых отсчетов. Отсчеты сигнала от движущейся цели из-за сохранения доплеровских сдвигов фазы сигнала не подавляются.

Введение второго блока 4 задержки на интервал τ обеспечивает соответствие оценок  среднему элементу обучающей выборки, исключенному в накопителях 17 (фиг. 8). Величина τ определяется выражением

среднему элементу обучающей выборки, исключенному в накопителях 17 (фиг. 8). Величина τ определяется выражением

где tв - время вычисления оценки  , n - количество элементов обучающей выборки, tд - интервал (период) временной дискретизации.

, n - количество элементов обучающей выборки, tд - интервал (период) временной дискретизации.

При этом достигается соответствие вводимой в комплексный перемножитель 6 оценки  среднему элементу, исключенному из обучающей выборки. Тогда в случае сигнала, соизмеримого по величине с помехой, или разрывной помехи при компенсации отсчетов помехи с элемента разрешения, содержащего сигнал, исключается возможность ослабления или подавления сигнала за счет его влияния на используемые оценки. Кроме того, уменьшаются ошибки за счет рассогласования между оцениваемой и действительной величинами доплеровской фазы помехи.

среднему элементу, исключенному из обучающей выборки. Тогда в случае сигнала, соизмеримого по величине с помехой, или разрывной помехи при компенсации отсчетов помехи с элемента разрешения, содержащего сигнал, исключается возможность ослабления или подавления сигнала за счет его влияния на используемые оценки. Кроме того, уменьшаются ошибки за счет рассогласования между оцениваемой и действительной величинами доплеровской фазы помехи.

Синхронизация вычислителя для компенсации помех осуществляется подачей на все блоки заявляемого устройства последовательности синхронизирующих импульсов от синхрогенератора 3 (фиг. 1).

Достигаемый технический результат состоит в повышении эффективности компенсации пассивной помехи с априорно неизвестной доплеровской фазой и выделения сигналов движущихся целей, что обеспечивается повышением точности оценивания доплеровской фазы помехи и уменьшением рассогласования между получаемыми усреднением отсчетов обучающей выборки оценками и соответствующими среднему элементу обучающей выборки.

Таким образом, вычислитель для компенсации помех позволяет повысить эффективность компенсации пассивной помехи и выделения сигналов движущихся целей на фоне пассивных помех с априорно неизвестной доплеровской фазой.

Библиография

1. Патент №63-49193 (Япония), МПК G01S 13/52. Радиолокационное устройство для обнаружения движущейся цели / К.К. Тосиба. Опубл. 03.10.1988. - Изобретения стран мира. - 1989. - Выпуск 109. - №15. - С. 52.

2. Радиоэлектронные системы: основы построения и теория. Справочник / Я.Д. Ширман, С.Т. Багдасарян, А.С. Маляренко, Д.И. Леховицкий [и др.]; под ред Я.Д. Ширмана. - 2-е изд., перераб. и доп. - М: Радиотехника, 2007; с. 439, рис. 25.22.

3. А.с. 743208 СССР, МПК G01S 7/36. Цифровое устройство для подавления пассивных помех / Д.И. Попов. - №2540079/09; заявл. 03.11.1977; опубл. 25.06.1980, Бюл. №23. - 4 с.

| название | год | авторы | номер документа |

|---|---|---|---|

| ВЫЧИСЛИТЕЛЬ-КОМПЕНСАТОР ПАССИВНЫХ ПОМЕХ | 2022 |

|

RU2802738C1 |

| ВЫЧИСЛИТЕЛЬ-РЕЖЕКТОР ПОМЕХ | 2024 |

|

RU2831755C1 |

| ВЫЧИСЛИТЕЛЬ ДЛЯ РЕЖЕКЦИИ ПОМЕХ | 2022 |

|

RU2797653C1 |

| ФИЛЬТР ПОДАВЛЕНИЯ ПОМЕХ | 2024 |

|

RU2835058C1 |

| ВЫЧИСЛИТЕЛЬ ДЛЯ ПОДАВЛЕНИЯ ПОМЕХ | 2023 |

|

RU2819294C1 |

| ФИЛЬТР КОМПЕНСАЦИИ ПОМЕХ | 2024 |

|

RU2834699C1 |

| РЕЖЕКТОРНЫЙ ФИЛЬТР | 2024 |

|

RU2825253C1 |

| ВЫЧИСЛИТЕЛЬ-ПОДАВИТЕЛЬ ПОМЕХ | 2024 |

|

RU2835118C1 |

| ВЫЧИСЛИТЕЛЬ-КОМПЕНСАТОР ПОМЕХ | 2024 |

|

RU2825197C1 |

| ВЫЧИСЛИТЕЛЬ РЕЖЕКЦИИ ПОМЕХ | 2024 |

|

RU2834767C1 |

Изобретение относится к вычислительным устройствам для компенсации пассивных помех. Технический результат заключается в повышении эффективности компенсации пассивной помехи с априорно неизвестной доплеровской фазой. Технический результат достигается за счет того, что в вычислитель введены второй и третий блок задержки, комплексный перемножитель, комплексный инвертор и измеритель доплеровской фазы, при этом входы второго блока задержки соединены с первыми входами измерителя доплеровской фазы, выходы второго блока задержки соединены с входами первого блока задержки, выходы которого соединены с входами третьего блока задержки и вторыми входами измерителя доплеровской фазы, выходы которого соединены со вторыми входами комплексного перемножителя, выходы третьего блока задержки соединены с первыми входами комплексного перемножителя, выходы которого соединены с входами комплексного инвертора, выходы которого соединены со вторыми входами комплексного сумматора, выход синхрогенератора соединен с синхровходами второго блока задержки, третьего блока задержки, комплексного перемножителя, комплексного инвертора и измерителя доплеровской фазы, входами вычислителя являются входы второго блока задержки, а выходами – выходы комплексного сумматора. 8 ил.

Вычислитель для компенсации помех, содержащий первый блок задержки, комплексный сумматор и синхрогенератор, при этом входы первого блока задержки соединены с первыми входами комплексного сумматора, выход синхрогенератора соединен с синхровходами первого блока задержки и комплексного сумматора, отличающийся тем, что введены второй блок задержки, третий блок задержки, комплексный перемножитель, комплексный инвертор и измеритель доплеровской фазы, при этом входы второго блока задержки соединены с первыми входами измерителя доплеровской фазы, выходы второго блока задержки соединены с входами первого блока задержки, выходы которого соединены с входами третьего блока задержки и вторыми входами измерителя доплеровской фазы, выходы которого соединены со вторыми входами комплексного перемножителя, выходы третьего блока задержки соединены с первыми входами комплексного перемножителя, выходы которого соединены с входами комплексного инвертора, выходы которого соединены со вторыми входами комплексного сумматора, выход синхрогенератора соединен с синхровходами второго блока задержки, третьего блока задержки, комплексного перемножителя, комплексного инвертора и измерителя доплеровской фазы, причем входами вычислителя для компенсации помех являются входы второго блока задержки, а выходами - выходы комплексного сумматора.

| УСТРОЙСТВО для РАЗМЕТКИ | 0 |

|

SU207402A1 |

| ВЫЧИСЛИТЕЛЬ ДЛЯ РЕЖЕКТОРНОЙ ФИЛЬТРАЦИИ ПОМЕХ | 2017 |

|

RU2686633C1 |

| ФИЛЬТР КОМПЕНСАЦИИ ПОМЕХ | 2021 |

|

RU2758877C1 |

| US 8121236 B1, 21.02.2012 | |||

| US 20090109083 A1, 30.04.2009. | |||

Авторы

Даты

2023-07-05—Публикация

2022-11-29—Подача