Область техники, к которой относится изобретение

Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных устройствах, а также в устройствах цифровой обработки сигналов, в криптографических приложениях и в системах управления.

Уровень техники

Известен последовательный многоразрядный сумматор, который содержит n-разрядные сдвиговые регистры операндов X и Y, регистр результата, одноразрядный сумматор и двухступенчатый D-триггер для запоминания переноса [1].

Недостатком данного сумматора является ограниченные функциональные возможности, а именно невозможность суммирования по произвольному модулю.

Также известен многоразрядный параллельный сумматор с последовательным переносом, содержащий n одноразрядных параллельных сумматоров с соответствующими связями [2].

Недостатком данного сумматора является ограниченные функциональные возможности, а именно невозможность суммирования по произвольному модулю.

Наиболее близким по технической сущности к заявляемому изобретению является многоразрядный параллельный сумматор по модулю с последовательным переносом, содержащий (n+1) одноразрядных параллельных сумматоров по модулю с соответствующими связями, осуществляющий суммирование чисел A и B по произвольному модулю P [3].

Недостатком данного устройства является низкое быстродействие, вызванное последовательным поразрядным суммированием, а также наличием в каждом одноразрядном сумматоре по модулю двух последовательно соединенных параллельных одноразрядных сумматоров.

Техническим результатом изобретения является повышение быстродействия.

Раскрытие сущности изобретения

Для достижения технического результата в многоразрядный сумматор по модулю, содержащий n полных одноразрядных сумматоров, где n - разрядность устройства, RS-триггер, элемент «2И», элемент «НЕ», элемент задержки, входы первого числа суммирования, входы второго числа суммирования, вход модуля устройства, информационные выходы устройства, вход установки устройства в начальное состояние, причем входы первого числа суммирования соединены с первыми информационными входами n полных одноразрядных сумматоров, входы второго числа суммирования соединены со вторыми информационными входами n полных одноразрядных сумматоров, вход модуля устройства соединён со входами переноса n полных одноразрядных сумматоров, вход установки устройства в начальное состояние соединен со входом установки в единичное состояние RS-триггера, вход установки в нулевое состояние которого соединен с выходом элемента «2И», первый информационный вход которого соединен с выходом элемента «НЕ», а второй информационный вход соединен с выходом элемента задержки, введены два (n+1)-разрядных мультиплексора и (n+1)-разрядный параллельный сумматор, (1…n)-й разряды первых информационных входов первого (n+1)-разрядного мультиплексора соединены с информационными выходами n полных одноразрядных сумматоров соответственно, а на (n+1)-й разряд подается сигнал логической единицы, (1…n)-й разряды вторых информационных входов соединены со входами первого числа суммирования, а на (n+1)-й разряд подается сигнал логического ноля, на первый разряд первых информационных входов второго (n+1)-разрядного мультиплексора подается логический ноль, а (2…(n+1))-й разряды соединены с выходами переноса (1…n)-го одноразрядных сумматоров, (1…n)-й разряды вторых информационных входов соединены со входами второго числа суммирования, на (n+1)-й разряд подается сигнал логического ноля, первые информационные входы (n+1)-разрядного сумматора соединены с информационными выходами первого (n+1)-разрядного мультиплексора, вторые информационные входы соединены с выходами второго (n+1)-разрядного мультиплексора, (1…n)-й разряды информационных выходов являются информационными выходами устройства, выход переноса соединён со входом элемента «НЕ», а информационный выход RS-триггера соединён со входом переноса (n+1)-разрядного сумматора, а также с управляющими входами (n+1)-разрядных мультиплексоров, причём вход установки устройства в начальное состояние соединён со входом элемента задержки.

Сущность изобретения заключается в реализации следующего способа суммирования чисел A и B по модулю P.

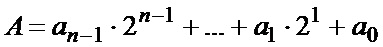

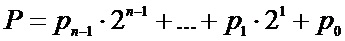

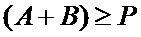

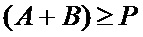

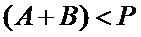

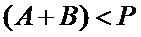

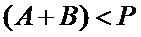

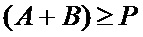

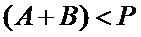

Пусть

В результате выполнения операции суммирования по модулю необходимо получить сумму

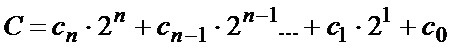

При сложении двух чисел, представленных в виде двоичных кодов A(an−1, …, a0) и B(bn−1, …, b0) образуется сумма С(сn, …, с0), равная

Краткое описание чертежей

На фиг. 1 представлена схема многоразрядного сумматора по модулю. Многоразрядный сумматор по модулю содержит n полных одноразрядных сумматоров 1.1 ÷ 1.n, первый (n+1)-разрядный мультиплексор 2, второй (n+1)-разрядный мультиплексор 3, (n+1)-разрядный параллельный сумматор 4, где n -разрядность устройства, RS-триггер 5, элемент «2И» 6, элемент «НЕ» 7, элемент задержки 8, вход 9 модуля устройства, входы 10 и 11 второго и первого чисел суммирования соответственно, информационные выходы 12 устройства, вход 13 установки устройства в начальное состояние. Входы первого числа суммирования 11 соединены с первыми информационными входами n полных одноразрядных сумматоров 1.1 ÷ 1.n. Входы второго числа суммирования 10 соединены со вторыми информационными входами n полных одноразрядных сумматоров 1.1 ÷ 1.n. Вход модуля устройства 9 соединён со входами переноса n полных одноразрядных сумматоров 1.1 ÷ 1.n. Вход установки устройства в начальное состояние 13 соединен со входом установки в единичное состояние RS-триггера 5 и со входом элемента задержки 8, вход установки в нулевое состояние которого соединен с выходом элемента «2И» 6, первый информационный вход которого соединен с выходом элемента «НЕ» 7, а второй информационный вход соединен с выходом элемента задержки 8. Первые информационные входы первого (n+1)-разрядного мультиплексора 2, а именно (1…n)-й разряды, соединены с информационными выходами n полных одноразрядных сумматоров 1.1 ÷ 1.n соответственно, а на (n+1)-й разряд подается сигнал логической единицы. Вторые информационные входы первого (n+1)-разрядного мультиплексора 2, а именно (1…n)-й разряды, соединены со входами первого числа суммирования 11, а на (n+1)-й разряд подается сигнал логического ноля. На первый разряд первых информационных входов второго (n+1)-разрядного мультиплексора 3 подается сигнал логического ноля, а (2…(n+1))-й разряды соединены с выходами переноса (1…n)-го одноразрядных сумматоров 1.1 ÷ 1.n, (1…n)-й разряды вторых информационных входов соединены со входами второго числа суммирования, на (n+1)-й разряд подается сигнал логического ноля, первые информационные входы (n+1)-разрядного сумматора 4 соединены с информационными выходами первого (n+1)-разрядного мультиплексора 2, вторые информационные входы соединены с информационными выходами второго (n+1)-разрядного мультиплексора 3, (1…n)-й разряды информационных выходов являются информационными выходами устройства 12, выход переноса соединён со входом элемента «НЕ» 7, а информационный выход RS-триггера 5 соединён со входом переноса (n+1)-разрядного сумматора 4, а также с управляющими входами первого (n+1)-разрядного мультиплексора 2 и второго (n+1)-разрядного мультиплексора 3.

На информационные входы 11, 10 и 9 устройства подают соответственно коды чисел A, B и инверсного модуля P, поступающие далее на первый информационный вход A, второй информационный вход B и вход переноса Pi соответствующего j-го полного одноразрядного сумматора 1.1 ÷ 1.n, где j=1, …, n. На вход 13 установки в начальное состояние подаётся сигнал начала вычислений.

Осуществление изобретения

Многоразрядный сумматор по модулю работает следующим образом (см. Фиг. 1).

Перед началом работы устройство устанавливается в начальное состояние подачей на вход 13 управляющего сигнала. На выходе RS-триггера 5 устанавливается единичный сигнал. На информационные входы 11, 10 и 9 устройства подаются в двоичном виде коды операндов суммирования A (an−1, …, a0) и B (bn−1, …, b0) и инверсный код модуля P(pn−1, …, p0) соответственно. В результате на информационных выходах полных одноразрядных сумматоров 1.1 ÷ 1.n образуются поразрядные сигналы суммы, а на выходах переноса образуются поразрядные сигналы переноса. Сигналы с информационных выходов полных одноразрядных сумматоров 1.1 ÷ 1.n поступают на (1…n)-й разряды первых информационных входов первого (n+1)-разрядного мультиплексора 2, на его (1…n)-й разряды вторых информационных входов поступают коды операнда суммирования A (an−1, …, a0). На последние разряды Xn+1 и Yn+1 первых и вторых информационных входов первого (n+1)-разрядного мультиплексора 2 поступают сигналы логической единицы и логического ноля соответственно. Сигналы с выходов переноса полных одноразрядных сумматоров 1.1 ÷ 1.n поступают на (2…(n+1))-й разряды первых информационных входов второго (n+1)-разрядного мультиплексора 3, на его (1…n)-й разряды вторых информационных входов поступают коды операнда суммирования B (bn−1, …, b0). На первый разряд X1 первых информационных входов и последний разряд Yn+1 вторых информационных входов второго (n+1)-разрядного мультиплексора 3 подается сигнал логического ноля. На управляющие входы первого (n+1)-разрядного мультиплексора 2, второго (n+1)-разрядного мультиплексора 3 и вход переноса Pi (n+1)-разрядного параллельного сумматора 4 с выхода RS-триггера 5 подается сигнал логической единицы. В результате на выходах (n+1)-разрядного сумматора 4 образуется значение

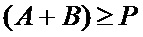

В случае, если

В случае, если

После получения результата суммирования чисел A и B по модулю P на выходе устройства, процесс суммирования может быть возобновлён с другими исходными данными.

Рассмотрим работу устройства на практическом примере, когда

В исходном состоянии RS-триггер 5 находится в нулевом состоянии, на все входы устройства воздействуют логические нули.

Пусть A=310=00112, B=410=01002, P=510=01012,

На входы A, B и Pi четырех полных одноразрядных сумматоров 1.1 ÷ 1.4 подаются коды чисел A=310=00112, B=410=01002,

Непосредственной проверкой устанавливаем: 3+4=7, 7≡2 mod 5.

Рассмотрим работу устройства на примере, когда

В исходном состоянии RS-триггер 5 находится в нулевом состоянии, на все входы устройства воздействуют логические нули.

Пусть A=310=00112, B=210=00102, P=610=01102,

На входы A, B и Pi четырех одноразрядных сумматоров 1.1 ÷ 1.4 подаются коды чисел A=310=00112, B=210=00102,

Таким образом, на входах 5-разрядного сумматора 4 образуются числа: С=000112 и D=001102. После суммирования на информационных выходах 5-разрядного сумматора (S1…S4), а значит и на выходах устройства, формируется число E=01012=510, а на выходе переноса Po=0.

Непосредственной проверкой устанавливаем: 3+2=5, 5≡5 mod 6.

Оценим технический результат, достигаемый при использовании предлагаемого устройства по сравнению с устройством прототипом.

Оценим быстродействие Tпр устройства прототипа как:

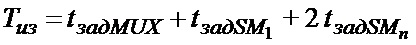

Быстродействие Tиз предлагаемого устройства будет равно:

А для случая, когда

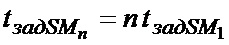

Если (n+1)-разрядный параллельный сумматор 4 выполнен по схеме с последовательным переносом, то тогда

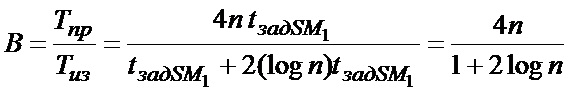

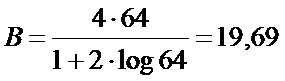

Выигрыш B в быстродействии предлагаемого устройства по сравнению с устройством прототипом при выполнении сумматора 4 в виде сумматора с последовательным переносом составит

Для случая

Для случая

Выигрыш B в быстродействии предлагаемого устройства по сравнению с устройством прототипом при выполнении сумматора 4 в виде префиксного сумматора составит

Для случая

Для случая

Рассчитаем выигрыш B при выполнении сумматора 4 в виде сумматора с последовательным переносом, при

Для случая

Для случая

Рассчитаем выигрыш B при выполнении сумматора 4 в виде префиксного сумматора, при

Для случая

Для случая

Источники информации

1. Бабич Н.П., Жуков И.А. Основы цифровой схемотехники: Учебное пособие. - М.: Издательский дом «Додэка - XXI», Киев: «МК-Пресс», 2007. - рисунок 4.45 с. 176.

2. Пухальский Г.И., Новосельцева Т.Я. Проектирование дискретных устройств на интегральных микросхемах: Справочник. - М.: Радио и связь, 1990. Рисунок 3.45, с.133.

3. Многоразрядный параллельный сумматор по модулю с последовательным переносом // Патент России № 2724597. Опубл. 25.06.2020. Бюл. № 18. / Петренко В.И., Степанян Н.Э., Нелидин Ю.Р.

| название | год | авторы | номер документа |

|---|---|---|---|

| СУММАТОР ПО ПРОИЗВОЛЬНОМУ МОДУЛЮ | 2024 |

|

RU2835074C1 |

| СУММАТОР ГРУППОВОЙ СТРУКТУРЫ ПО ПРОИЗВОЛЬНОМУ МОДУЛЮ С ПОСЛЕДОВАТЕЛЬНЫМ ПЕРЕНОСОМ | 2024 |

|

RU2822292C1 |

| МНОГОРАЗРЯДНЫЙ СУММАТОР ПО МОДУЛЮ | 2022 |

|

RU2790638C1 |

| НАКАПЛИВАЮЩИЙ СУММАТОР ГРУППОВОЙ СТРУКТУРЫ ПО ПРОИЗВОЛЬНОМУ МОДУЛЮ С ПОСЛЕДОВАТЕЛЬНЫМ ПЕРЕНОСОМ | 2024 |

|

RU2833212C1 |

| УСТРОЙСТВО ДЛЯ КОНВЕЙЕРНОГО СУММИРОВАНИЯ ЧИСЕЛ ПО ПРОИЗВОЛЬНОМУ МОДУЛЮ | 2023 |

|

RU2805939C1 |

| Многоразрядный сумматор по модулю | 2024 |

|

RU2831626C1 |

| НАКАПЛИВАЮЩИЙ СУММАТОР ПО ПРОИЗВОЛЬНОМУ МОДУЛЮ | 2024 |

|

RU2835073C1 |

| АРИФМЕТИКО-ЛОГИЧЕСКОЕ УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ, ВЫЧИТАНИЯ И УМНОЖЕНИЯ ЧИСЕЛ ПО МОДУЛЮ | 2019 |

|

RU2711051C1 |

| УМНОЖИТЕЛЬ ПО МОДУЛЮ | 2024 |

|

RU2829089C1 |

| Устройство для умножения @ -разрядных двоичных чисел | 1990 |

|

SU1783519A1 |

Изобретение относится к вычислительной технике. Технический результат заключается в повышении быстродействия устройства. Многоразрядный сумматор по модулю содержит n полных одноразрядных сумматоров, два (n+1)-разрядных мультиплексора, (n+1)-разрядный параллельный сумматор, где n является разрядностью устройства, элемент задержки, RS-триггер, элемент «НЕ» и элемент «2И». 1 ил.

Многоразрядный сумматор по модулю, содержащий n полных одноразрядных сумматоров, где n – разрядность устройства, RS-триггер, элемент «2И», элемент «НЕ», элемент задержки, входы первого числа суммирования, входы второго числа суммирования, вход модуля устройства, информационные выходы устройства, вход установки устройства в начальное состояние, причем входы первого числа суммирования соединены с первыми информационными входами n полных одноразрядных сумматоров, входы второго числа суммирования соединены со вторыми информационными входами n полных одноразрядных сумматоров, вход модуля устройства соединён со входами переноса n полных одноразрядных сумматоров, вход установки устройства в начальное состояние соединен со входом установки в единичное состояние RS-триггера, вход установки в нулевое состояние которого соединен с выходом элемента «2И», первый информационный вход которого соединен с выходом элемента «НЕ», а второй информационный вход соединен с выходом элемента задержки, отличающийся тем, что в него введены два (n+1)-разрядных мультиплексора и (n+1)-разрядный параллельный сумматор, (1…n)-й разряды первых информационных входов первого (n+1)-разрядного мультиплексора соединены с информационными выходами n полных одноразрядных сумматоров соответственно, а на (n+1)-й разряд подается сигнал логической единицы, (1…n)-й разряды вторых информационных входов соединены со входами первого числа суммирования, а на (n+1)-й разряд подается сигнал логического ноля, на первый разряд первых информационных входов второго (n+1)-разрядного мультиплексора подается логический ноль, а (2…(n+1))-й разряды соединены с выходами переноса (1…n)-го одноразрядных сумматоров, (1…n)-й разряды вторых информационных входов соединены со входами второго числа суммирования, на (n+1)-й разряд подается сигнал логического ноля, первые информационные входы (n+1)-разрядного сумматора соединены с информационными выходами первого (n+1)-разрядного мультиплексора, вторые информационные входы соединены с выходами второго (n+1)-разрядного мультиплексора, (1…n)-й разряды информационных выходов являются информационными выходами устройства, выход переноса соединён со входом элемента «НЕ», а информационный выход RS-триггера соединён со входом переноса (n+1)-разрядного сумматора, а также с управляющими входами (n+1)-разрядных мультиплексоров, причём вход установки устройства в начальное состояние соединён со входом элемента задержки.

| МНОГОРАЗРЯДНЫЙ СУММАТОР ПО МОДУЛЮ | 2022 |

|

RU2790638C1 |

| Накапливающий сумматор по модулю | 2022 |

|

RU2791441C1 |

| Многоразрядный параллельный сумматор по модулю с последовательным переносом | 2019 |

|

RU2724597C1 |

| МНОГОЗНАЧНЫЙ СУММАТОР ПО МОДУЛЮ k | 2014 |

|

RU2546082C1 |

| Способ обработки целлюлозных материалов, с целью тонкого измельчения или переведения в коллоидальный раствор | 1923 |

|

SU2005A1 |

Авторы

Даты

2023-09-28—Публикация

2023-05-24—Подача