Область техники, к которой относится изобретение

Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных устройствах конвейерного типа для построения однородных вычислительных сред, а также в устройствах цифровой обработки сигналов и в криптографических приложениях.

Уровень техники

Из существующего уровня техники известно техническое решение однородной вычислительной структуры для выполнения операций по заданному модулю, которая содержит N2 полных сумматоров, N/2(N-1)2 элементов И, (N-2)(N-1) элементов ИЛИ, N/2(N-1)2 управляющих входов [1], предназначенное для выполнения арифметических операций по заданному модулю. Технической проблемой, которая не может быть решена при использовании данного технического решения, является низкая производительность арифметических операций по произвольному модулю, так как основной арифметической операции при работе устройства предшествует дополнительный режим коммутации, который определяет структуру устройства в зависимости от выбранного модуля.

Наиболее близким к заявленному техническому решению по технической сущности и достигаемому техническому результату является устройство для конвейерных арифметических вычислений по заданному модулю, выбранное в качестве прототипа, содержащее однородную вычислительную среду, три таблицы подстановок, информационные входы и информационные выходы, тактовый вход, позволяющее выполнять суммирование чисел по произвольным простым модулям [2, фиг. 5]. Технической проблемой, которая не может быть решена при использовании данного технического решения при конвейерной обработке информации, является ограниченность функциональных возможностей устройства, так как устройство позволяет выполнять операции суммирования чисел только по модулям простых чисел. Кроме того, использование таблиц подстановки требует при каждой смене модуля менять содержимое таблиц подстановки, что не позволяет оперативно менять модуль при организации конвейерных вычислений.

Техническим результатом, обеспечиваемым приведенной совокупностью признаков, является расширение функциональных возможностей устройства при конвейерной обработке информации.

Раскрытие сущности изобретения

Указанный технический результат при осуществлении изобретения достигается тем, что в устройство для конвейерного суммирования чисел по произвольному модулю, содержащее первую однородную вычислительную среду разрядности n, где n - разрядность обрабатываемых чисел, первые, вторые и третьи информационные входы, информационные выходы и тактовый вход, который соединен со входом синхронизации первой однородной вычислительной среды, введены вторая однородная вычислительная среда разрядности (n+1), группа полных одноразрядных сумматоров и мультиплексор разрядности n, причем первые информационные входы устройства соединены с первыми информационными входами первой однородной вычислительной среды и с первыми информационными входами группы полных одноразрядных сумматоров, вторые информационные входы устройства соединены со вторыми информационными входами первой однородной вычислительной среды и со вторыми информационными входами группы полных одноразрядных сумматоров, третьи информационные входы устройства соединены с третьими информационными входами группы полных одноразрядных сумматоров, первые информационные выходы которой соединены с младшими n разрядами первых информационных входов второй однородной вычислительной среды, вторые информационные выходы соединены со вторыми информационными входами второй однородной вычислительной среды со сдвигом на один разряд в сторону старшего, на (n+1)-й разряд первых информационных входов и на первый разряд вторых информационных входов второй вычислительной среды подается сигнал логической единицы, вход синхронизации второй однородной вычислительной среды соединен с тактовым входом устройства, младшие n разрядов информационных выходов соединены со вторыми информационными входами мультиплексора, а выход разряда переноса соединен с управляющим входом мультиплексора, первые информационные входы которого соединены с информационными выходами первой однородной вычислительной среды, а выходы соединены с информационными выходами устройства.

Сущность изобретения заключается в реализации следующего способа суммирования чисел по произвольному модулю. Пусть S - сумма двух чисел A и B по произвольному модулю P

S

(A+B) mod P, (1)

(A+B) mod P, (1)

где A и B - целые положительные числа, называемые соответственно первым и вторым слагаемым, причем

0≤A, B<P, (2)

P - целое положительное число, называемое модулем;

S - целое положительное число, являющееся суммой чисел A и B, приведенной по модулю P, при этом 0≤S<P.

Все числа представлены в позиционной двоичной системе счисления.

A =

B =

P =

S=

где ai,  - коэффициенты, принимающие значение 0 или 1 в зависимости от значения числа A;

- коэффициенты, принимающие значение 0 или 1 в зависимости от значения числа A;

bi,  - коэффициенты, принимающие значение 0 или 1 в зависимости от значения числа B;

- коэффициенты, принимающие значение 0 или 1 в зависимости от значения числа B;

pi,  - коэффициенты, принимающие значение 0 или 1 в зависимости от значения модуля P;

- коэффициенты, принимающие значение 0 или 1 в зависимости от значения модуля P;

si,  - коэффициенты, принимающие значение 0 или 1 в зависимости от значения суммы S;

- коэффициенты, принимающие значение 0 или 1 в зависимости от значения суммы S;

n - количество разрядов в представлении чисел.

Задача состоит в том, чтобы по известным A и B отыскать сумму S по модулю P.

Ввиду выполнения ограничения (2), сумма чисел A и B всегда будет находиться в диапазоне значений от 0 до 2P-2. Диапазон значений от 0 до 2P-2 может быть разделен на первый диапазон от 0 до P-1 и второй диапазон от P до 2P-2. Если сумма чисел A и B попадает в первый диапазон, то она и будет являться результатом суммирования чисел A и B по модулю P. Если сумма чисел A и B попадает во второй диапазон, то для приведения ее по модулю P достаточно вычесть из нее модуль P. Операция вычитания может быть выполнена путем суммирования уменьшаемого с вычитаемым, представленном в дополнительном коде. При этом индикатором попадания суммы чисел A и B в первый или второй диапазон будет являться отсутствие или наличие сигнала на выходе переноса сумматора, реализующего операцию вычитания. Этот сигнал управляет мультиплексором, который выбирает нужный результат.

В качестве сумматора в конвейерном режиме суммирования может выступать однородная вычислительная среда [2, фиг. 3] со структурой ячеек, представленной в [2, фиг. 1].

Выполняя с помощью одной однородной вычислительной среды операцию суммирования потоков чисел Aj и Bj, j=1,2,3,…, а с помощью второй однородной вычислительной среды операцию (Aj+Bj-Pj), можно по результатам вычисления второй однородной вычислительной среды выбирать корректное значение для суммы Sj

Sj

(Aj+Bj) mod Pj. (7)

(Aj+Bj) mod Pj. (7)

Краткое описание чертежей

Сущность изобретения поясняется чертежами.

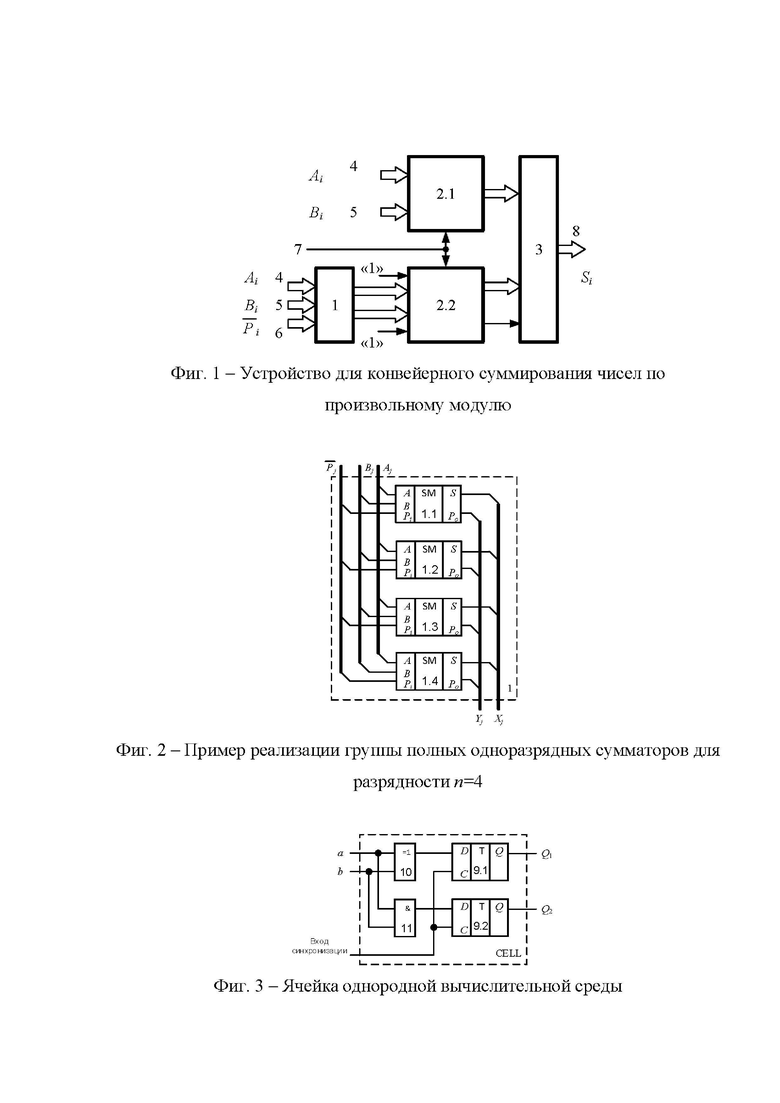

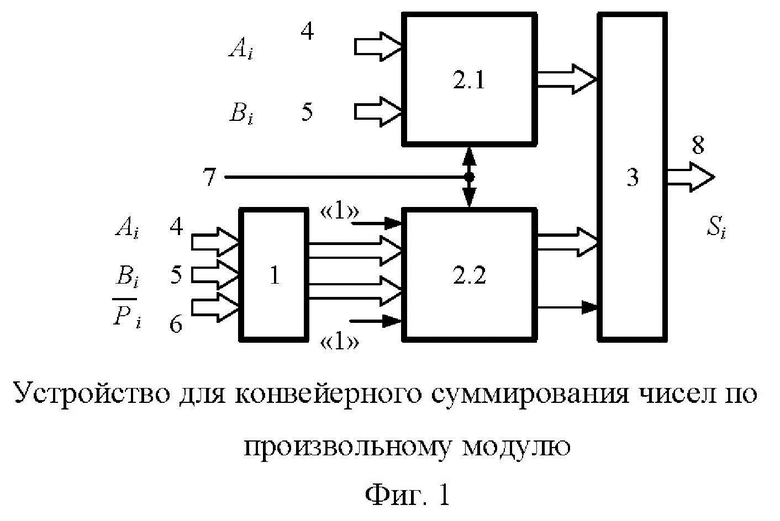

На фиг. 1 представлена схема устройства для конвейерного суммирования чисел по произвольному модулю. Устройство для конвейерного суммирования чисел по произвольному модулю содержит группу полных одноразрядных сумматоров 1, первую однородную вычислительную среду 2.1 разрядности n, где n - разрядность обрабатываемых чисел, вторую однородную вычислительную среду 2.2 разрядности (n+1), мультиплексор 3 разрядности n, первые 4, вторые 5 и третьи 6 информационные входы устройства, тактовый вход 7 и информационные выходы 8 устройства. Первые информационные входы 4 устройства соединены с первыми информационными входами первой однородной вычислительной среды 2.1 и с первыми информационными входами группы полных одноразрядных сумматоров 1. Вторые информационные входы 5 устройства соединены со вторыми информационными входами первой однородной вычислительной среды 2.1 и со вторыми информационными входами группы полных одноразрядных сумматоров 1. Третьи информационные входы 6 устройства соединены с третьими информационными входами группы полных одноразрядных сумматоров 1, первые информационные выходы которой соединены с младшими n разрядами первых информационных входов второй однородной вычислительной среды 2.2, вторые информационные выходы соединены со вторыми информационными входами второй однородной вычислительной среды 2.2 со сдвигом на один разряд в сторону старшего. Тактовый вход устройства соединен со входами синхронизации первой 2.1 и второй 2.2 однородной вычислительной среды. Младшие n разрядов информационных выходов второй однородной вычислительной среды 2.2 соединены со вторыми информационными входами мультиплексора 3, а выход разряда переноса соединен с управляющим входом мультиплексора 3, первые информационные входы которого соединены с информационными выходами первой однородной вычислительной среды 2.1, а выходы соединены с информационными выходами 8 устройства. На (n+1)-й разряд первых информационных входов и на первый разряд вторых информационных входов второй вычислительной среды 2.2 подается сигнал логической единицы. На первые информационные входы 4 устройства подается поток кодов чисел Aj, j=1,2,3,…, на вторые информационные входы 5 устройства подается поток кодов чисел Bj, на третьи информационные входы 6 устройства подается поток инверсных кодов модулей Pj. С информационных выходов 8 устройства снимаются коды суммы Sj чисел Aj и Bj, по модулю Pj.

Осуществление изобретения

Устройство для конвейерного суммирования чисел по произвольному модулю работает следующим образом (см. фиг. 1).

В исходном состоянии все ячейки первой 2.1 и второй 2.2 однородной вычислительной среды обнулены.

На тактовый вход устройства 7 поступают тактовые импульсы j=1,2,3,…,. На первые информационные входы 4 устройства и вторые информационные входы 5 устройства с каждым тактовым импульсом подаются соответственно числа Aj и Bj, для которых необходимо вычислить сумму Sj по модулю Pj. На третьи информационные входы 6 устройства подаётся инверсный код модуля Pj. Сумма Sj по модулю Pj чисел Aj и Bj снимается с информационных выходов 8 устройства.

Длина конвейера и латентный период работы конвейера зависит от структуры однородных вычислительных сред 2.1 и 2.2.

Для каждой пары чисел Aj и Bj, первая однородная вычислительная среда 2.1 вычисляет сумму (Aj+Bj). Для каждой тройки чисел Aj, Bj, и Pj вторая однородная вычислительная среда 2.2 совместно с группой полных одноразрядных сумматоров 1 вычисляет значение (Aj+Bj-Pj). Сумма (Aj+Bj) и значение (Aj+Bj-Pj) появляются синхронно на каждом такте на первых и вторых информационных входах мультиплексора 3. В случае, если сумма (Aj+Bj)≥Pj, то на выходе разряда переноса второй однородной вычислительной среды 2.2 появится сигнал переноса, который, поступая на управляющий вход мультиплексора 3, скоммутирует с его информационными выходами его вторые информационные входы, в результате на информационных выходах устройства окажется значение (Aj+Bj-Pj). В противном случае с информационными выходами мультиплексора 1 будут скоммутированы его первые информационные входы и на информационных выходах устройства окажется значение (Aj+Bj).

Рассмотрим реализацию устройства для случая, когда разрядность обрабатываемых чисел n равна 4.

На фиг. 2 представлена структура группы полных одноразрядных сумматоров 1, состоящая из четырех полных одноразрядных сумматоров 1.1÷1.4. Каждый полный одноразрядный сумматор 1.1÷1.4 имеет два информационных входа A и B, вход переноса Pi, выход суммы S и выход переноса Po. На первые информационные входы A полных одноразрядных сумматоров 1.1÷1.4 поступают с первых информационных входов 4 устройства коды чисел Aj, на вторые информационные входы B поступают со вторых информационных входов 5 устройства коды чисел Bj, на входы переноса Pi, поступают с третьих информационных входов 6 устройства инверсные коды модулей Pj. Каждый полный одноразрядный сумматор 1.1÷1.4 формирует на своих выходах значение суммы и значение переноса в зависимости от значений входных сигналов, которые поступают на первые и вторые информационные выходы соответственно группы полных одноразрядных сумматоров 1, обозначенные как Xj и Yj соответственно. При этом в соответствии с правилами сложения чисел разряды Xj и Yj будут вычислены как

xi

,

j

=ai,j

yi

,

j

=ai,jbi,j

где i = 0, 1, 2, 3 - номер разряда в двоичном представлении чисел;

j=1, 2, 3, …, - номер такта работы устройства;

xi , j - i-ый разряд j-го числа Xj,

yi , j - i-ый разряд j-го числа Yj;

ai , j - i-ый разряд j-го числа Aj;

bi , j - i-ый разряд j-го числа Bj;

pi , j - i-ый разряд j-го числа Pj;

символ

символ

Тогда вычисление значения (Aj+Bj-Pj), состоящего из трех операндов, может быть сведено к вычислению значения (2n+1+Xj+2Yj+1), состоящего из двух операндов и двух констант, с увеличением на одну единицу разрядности вычислителя.

В качестве ячейки (CELL) для однородной вычислительной среды может быть использована ячейка, представленная на фиг. 3 [2, фиг. 1] и содержащая первый 9.1 и второй 9.2 триггеры, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 10, элемент И 11, два информационных входа a и b, вход синхронизации и два информационных выхода Q1 и Q2. Ячейка однородной структуры реализует следующую систему логических функций:

Q

1= a

Q 2= a⋅b. (11)

Пример реализации первой однородной вычислительной среды 2.1 на базе ячейки однородной структуры для разрядности n=4 в соответствии с [2, фиг. 3] представлен на фиг. 4. Первая однородная вычислительная среда 2.1 для разрядности n=4 содержит 4 строки и 6 столбцов ячеек однородной структуры CELL n, m с соответствующими связями. Линии синхронизации подключены к каждой ячейке и на фиг. 4 не показаны. Информационные входы a и b ячеек первого столбца являются входами для разрядов суммируемых чисел Aj и Bj. Информационные выходы Q1 ячеек шестого столбца являются информационными выходами суммы Sj для случая, когда Sj<Pj.

Пример реализации второй однородной вычислительной среды 2.2 на базе ячейки однородной структуры в соответствии с [2, фиг. 3] представлен на фиг. 5. Вторая однородная вычислительная среда 2.2 для разрядности входных чисел n=4 имеет входную разрядность равную пяти и содержит 6 строк и 6 столбцов ячеек однородной структуры CELL n, m с соответствующими связями, позволяющую формировать также сигнал переноса. Линии синхронизации подключены к каждой ячейке и на фиг. 5 не показаны. Информационные входы a и b ячеек первого столбца являются входами для разрядов суммируемых чисел Xj и Yj. Вторая однородная вычислительная среда 2.2 выполняет операцию (25+Xj+2Yj+1). На младшие 4 разряда первых информационных входов однородной вычислительной среды 2.2 с первых информационных выходов группы полных одноразрядных сумматоров 1 поступают значения Xj, вычисленные в соответствии с (8). На пятый разряд подается значение логической 1. Значения Yj, вычисленные в соответствии с (9), со вторых информационных выходов группы полных одноразрядных сумматоров 1 поступают на вторые информационные входы однородной вычислительной среды 2.2 со сдвигом на один разряд в сторону старших, а на самый младший разряд подается сигнал логической 1. Информационные выходы Q1 ячеек шестого столбца являются информационными выходами суммы Sj однородной вычислительной среды 2.2 для случая, когда Sj≥Pj. В качестве разрядов суммы Sj используются первые четыре разряда информационных выходов однородной вычислительной среды 2.2, а в качестве разряда переноса используется информационный выход шестого разряда. Сигнал переноса с выхода переноса однородной вычислительной среды 2.2 управляет работой мультиплексора 3. Если сигнал переноса равен нулю, то это означает, что (Aj+Bj)<Pj. B этом случае мультиплексор 3 коммутирует с первых информационных входов на свои выходы и далее на информационные выходы 8 устройства значение суммы (Aj+Bj) с информационных выходов первой однородной вычислительной среды 2.1. В случае, если сигнал переноса равен единице, то это означает, что (Aj+Bj)≥Pj. B этом случае мультиплексор 3 коммутирует со вторых информационных входов на свои выходы и далее на информационные выходы 8 устройства значение (Aj+Bj)-Pj с информационных выходов второй однородной вычислительной среды 2.2. Таким образом, на информационных выходах 8 устройства всегда будет сформировано корректное значение Sj в соответствии с (7).

Рассмотрим примеры работы устройства на конкретных значениях суммируемых чисел и модуля. В качестве первого примера рассмотрим случай, когда сумма входных чисел не превышает значения модуля. В качестве входных данных выберем для разрядности n=4 числа A=310 (00112), B=710 (01112) и модуль P=1210 (11002, инверсный код 00112). Состояния элементов устройства при вычислении суммы для первого примера представлены в табл. 1-4.

В первом столбце таблицы 1 числами 1÷4 обозначены номера строк, а в строке 1 числами 1÷6 обозначены номера столбцов первой однородной вычислительной среды 2.1. На пересечении соответствующей строки и столбца указан сигнал на соответствующем входе соответствующей ячейки. В последнем столбце приведены значения сигналов на выходах суммы ячеек шестого столбца. Значения сигналов приведены для одного набора данных для шести тактовых состояний.

В первом столбце таблицы 2 обозначения 1.1÷1.4 указывают на номера сумматоров в группе полных одноразрядных сумматоров 1. Значения сигналов приведены для одного набора данных для первого такта.

Структура таблицы 3 аналогична структуре таблице 1.

В таблице 4 приведены значения сигналов на информационных входах и на информационных выходах мультиплексора 3 на шестом такте. На управляющий вход мультиплексора в соответствии с таблицей 3 поступает сигнал s5=0. В результате на информационные выходы 8 устройства на шестом такте поступает число 10102=1010. Непосредственной проверкой устанавливаем 3+7 10 mod 12.

10 mod 12.

В качестве второго примера рассмотрим случай, когда сумма входных чисел превышает значение модуля. В качестве входных данных выберем для разрядности n=4 числа A=8 (1000)2, B=9 (1001)2 и модуль P=1210 (11002, инверсный код 00112). Состояния элементов устройства при вычислении суммы для второго примера представлены в табл. 5-9.

В первом столбце таблицы 5 числами 1÷4 обозначены номера строк, а в строке 1 числами 1÷6 обозначены номера столбцов первой однородной вычислительной среды 2.1. На пересечении соответствующей строки и столбца указан сигнал на соответствующем входе соответствующей ячейки. В последнем столбце приведены значения сигналов на выходах суммы ячеек шестого столбца. Значения сигналов приведены для одного набора данных для шести тактовых состояний.

В первом столбце таблицы 6 обозначения 1.1÷1.4 указывают на номера сумматоров в группе полных одноразрядных сумматоров 1. Значения сигналов приведены для одного набора данных для первого такта.

Структура таблицы 7 аналогична структуре таблице 5.

В таблице 8 приведены значения сигналов на информационных входах и на информационных выходах мультиплексора 3 на шестом такте. На управляющий вход мультиплексора 3 в соответствии с таблицей 7 поступает сигнал s5=1. В результате на информационные выходы 8 устройства на шестом такте поступает число 01012=510. Непосредственной проверкой устанавливаем 8+9 5 mod 12.

5 mod 12.

Изобретение позволяет выполнять операции конвейерного суммирования чисел по любым модулям, а не только по модулям простых чисел, кроме того, изобретение позволяет оперативно для каждой пары чисел задавать свой модуль, не требуя при этом дополнительных операций по предварительной настройке, что расширяет функциональные возможности устройства при конвейерной обработке информации.

Источники информации.

1. Патент на изобретение RU 2310223 С1. МПК G06F 7/72 (2006.01). Однородная вычислительная структура для выполнения операций по заданному модулю. Опубликован 10.11.2007. Бюл. №31.

2. Патент на изобретение RU 2477513 С1. МПК G06F 7/72 (2006.01). Ячейка однородной вычислительной среды, однородная вычислительная среда и устройство для конвейерных арифметических вычислений по заданному модулю. Опубликован 10.03.2013. Бюл. №7.

| название | год | авторы | номер документа |

|---|---|---|---|

| КОНВЕЙЕРНЫЙ НАКАПЛИВАЮЩИЙ СУММАТОР ПО ПРОИЗВОЛЬНЫМ МОДУЛЯМ | 2024 |

|

RU2823911C1 |

| Многоканальный накапливающий сумматор по произвольным модулям | 2024 |

|

RU2837596C1 |

| КОНВЕЙЕРНЫЙ СУММАТОР ПО МОДУЛЮ | 2023 |

|

RU2799035C1 |

| КОНВЕЙЕРНЫЙ УМНОЖИТЕЛЬ ПО МОДУЛЯМ | 2024 |

|

RU2838847C1 |

| НАКАПЛИВАЮЩИЙ СУММАТОР ГРУППОВОЙ СТРУКТУРЫ ПО ПРОИЗВОЛЬНОМУ МОДУЛЮ С ПОСЛЕДОВАТЕЛЬНЫМ ПЕРЕНОСОМ | 2024 |

|

RU2833212C1 |

| КОНВЕЙЕРНЫЙ УМНОЖИТЕЛЬ ПО МОДУЛЮ | 2023 |

|

RU2797164C1 |

| МНОГОРАЗРЯДНЫЙ СУММАТОР ПО МОДУЛЮ | 2023 |

|

RU2804379C1 |

| НАКАПЛИВАЮЩИЙ СУММАТОР ПО ПРОИЗВОЛЬНОМУ МОДУЛЮ | 2024 |

|

RU2835073C1 |

| ОДНОРОДНАЯ ВЫЧИСЛИТЕЛЬНАЯ СРЕДА ДЛЯ КОНВЕЙЕРНЫХ ВЫЧИСЛЕНИЙ СУММЫ M N-РАЗРЯДНЫХ ЧИСЕЛ | 2012 |

|

RU2486576C1 |

| СУММАТОР ГРУППОВОЙ СТРУКТУРЫ ПО ПРОИЗВОЛЬНОМУ МОДУЛЮ С ПОСЛЕДОВАТЕЛЬНЫМ ПЕРЕНОСОМ | 2024 |

|

RU2822292C1 |

Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных устройствах конвейерного типа для построения однородных вычислительных сред, а также в устройствах цифровой обработки сигналов и в криптографических приложениях. Техническим результатом является реализация суммирования чисел по произвольному модулю. Устройство содержит группу полных одноразрядных сумматоров, первую однородную вычислительную среду разрядности n, где n - разрядность обрабатываемых чисел, вторую однородную вычислительную среду разрядности (n+1), мультиплексор разрядности n, первые, вторые и третьи информационные входы, тактовый вход и информационные выходы с соответствующими связями. 5 ил., 8 табл.

Устройство для конвейерного суммирования чисел по произвольному модулю, содержащее первую однородную вычислительную среду разрядности n, где n – разрядность обрабатываемых чисел, первые, вторые и третьи информационные входы, информационные выходы и тактовый вход, который соединен со входом синхронизации первой однородной вычислительной среды, отличающееся тем, что в него введены вторая однородная вычислительная среда разрядности (n+1), группа полных одноразрядных сумматоров и мультиплексор разрядности n, причем первые информационные входы устройства соединены с первыми информационными входами первой однородной вычислительной среды и с первыми информационными входами группы полных одноразрядных сумматоров, вторые информационные входы устройства соединены со вторыми информационными входами первой однородной вычислительной среды и со вторыми информационными входами группы полных одноразрядных сумматоров, третьи информационные входы устройства соединены с третьими информационными входами группы полных одноразрядных сумматоров, первые информационные выходы которой соединены с младшими n разрядами первых информационных входов второй однородной вычислительной среды, вторые информационные выходы соединены со вторыми информационными входами второй однородной вычислительной среды со сдвигом на один разряд в сторону старшего, на (n+1)-й разряд первых информационных входов и на первый разряд вторых информационных входов второй вычислительной среды подается сигнал логической единицы, вход синхронизации второй однородной вычислительной среды соединен с тактовым входом устройства, младшие n разрядов информационных выходов соединены со вторыми информационными входами мультиплексора, а выход разряда переноса соединен с управляющим входом мультиплексора, первые информационные входы которого соединены с информационными выходами первой однородной вычислительной среды, а выходы соединены с информационными выходами устройства.

| ЯЧЕЙКА ОДНОРОДНОЙ ВЫЧИСЛИТЕЛЬНОЙ СРЕДЫ, ОДНОРОДНАЯ ВЫЧИСЛИТЕЛЬНАЯ СРЕДА И УСТРОЙСТВО ДЛЯ КОНВЕЙЕРНЫХ АРИФМЕТИЧЕСКИХ ВЫЧИСЛЕНИЙ ПО ЗАДАННОМУ МОДУЛЮ | 2011 |

|

RU2477513C1 |

| ОДНОРОДНАЯ ВЫЧИСЛИТЕЛЬНАЯ СТРУКТУРА ДЛЯ ВЫПОЛНЕНИЯ ОПЕРАЦИЙ ПО ЗАДАННОМУ МОДУЛЮ | 2005 |

|

RU2310223C2 |

| КОНВЕЙЕРНЫЙ СУММАТОР ПО МОДУЛЮ | 2023 |

|

RU2799035C1 |

| Конвейерный сумматор | 1982 |

|

SU1067499A1 |

| US 4887233 A1, 12.12.1989 | |||

| US 7007059 B1, 28.02.2006 | |||

| WO 2002008885 A1, 31.01.2002. | |||

Авторы

Даты

2023-10-24—Публикация

2023-07-11—Подача