Область техники, к которой относится изобретение

Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных устройствах конвейерного типа для построения однородных вычислительных сред, в устройствах цифровой обработки сигналов, в криптографических приложениях, а также при построении многоканальных синтезаторов частот.

Уровень техники

Из существующего уровня техники известно техническое решение однородной вычислительной структуры для выполнения операций по заданному модулю, которая содержит N2 полных сумматоров, N/2(N-1)2 элементов И, (N-2)(N-1) элементов ИЛИ, N/2(N-1)2 управляющих входов [1], предназначенное для выполнения арифметических операций по заданному модулю. Технической проблемой, которая не может быть решена при использовании данного технического решения, является низкая производительность арифметических операций по произвольным модулям, так как основной арифметической операции при работе устройства предшествует дополнительный режим коммутации, который определяет структуру устройства в зависимости от выбранного модуля.

Из существующего уровня техники также известно устройство для конвейерных арифметических вычислений по заданному модулю, содержащее однородную вычислительную среду, три таблицы подстановок, информационные входы и информационные выходы, тактовый вход, позволяющее выполнять суммирование чисел по произвольным простым модулям [2, фиг. 5]. Технической проблемой, которая не может быть решена при использовании данного технического решения при конвейерной обработке информации, является ограниченность функциональных возможностей устройства, так как устройство позволяет выполнять операции суммирования чисел только по модулям простых чисел. Кроме того, использование таблиц подстановки требует при каждой смене модуля изменять содержимое таблиц подстановки, что не позволяет оперативно менять модуль при организации конвейерных вычислений.

Наиболее близким к заявленному техническому решению по технической сущности и достигаемому техническому результату является устройство для конвейерного суммирования чисел по произвольному модулю, выбранное в качестве прототипа, содержащее группу полных одноразрядных сумматоров, первую однородную вычислительную среду разрядности n, где n - разрядность обрабатываемых чисел, вторую однородную вычислительную среду разрядности (n+1), мультиплексор разрядности n, первые, вторые и третьи информационные входы, тактовый вход и информационные выходы с соответствующими связями, позволяющее выполнять суммирование чисел по модулю в конвейерном режиме [3]. Технической проблемой, которая не может быть решена при использовании данного технического решения при конвейерной обработке информации, является ограниченность функциональных возможностей устройства, так как устройство не позволяет осуществлять накапливающее суммирование чисел по модулю в конвейерном режиме.

Техническим результатом, обеспечиваемым приведенной совокупностью признаков, является расширение функциональных возможностей устройства при конвейерной обработке информации за счет реализации операции конвейерного накапливающего суммирования.

Раскрытие сущности изобретения.

Указанный технический результат при осуществлении изобретения достигается тем, что в конвейерном накапливающем сумматоре по произвольным модулям, содержащем первую однородную вычислительную среду разрядности n, вторую однородную вычислительную среду разрядности (n+1), группу полных одноразрядных сумматоров и мультиплексор разрядности n, где n - разрядность обрабатываемых чисел, первые и вторые информационные входы, информационные выходы и тактовый вход, который соединен со входом синхронизации первой и второй однородных вычислительных сред, причем первые информационные входы устройства соединены с первыми информационными входами первой однородной вычислительной среды и с первыми информационными входами группы полных одноразрядных сумматоров, вторые информационные входы устройства соединены со вторыми информационными входами группы полных одноразрядных сумматоров, первые информационные выходы которой соединены с младшими n разрядами первых информационных входов второй однородной вычислительной среды, вторые информационные выходы соединены со вторыми информационными входами второй однородной вычислительной среды со сдвигом на один разряд в сторону старшего, на (n+1)-й разряд первых информационных входов и на первый разряд вторых информационных входов второй вычислительной среды подается сигнал логической единицы, младшие n разрядов информационных выходов второй однородной вычислительной среды соединены со вторыми информационными входами мультиплексора, а выход разряда переноса соединен с управляющим входом мультиплексора, первые информационные входы которого соединены с информационными выходами первой однородной вычислительной среды, а информационные выходы соединены с информационными выходами устройства, дополнительно информационные выходы мультиплексора соединены со вторыми информационными входами первой однородной вычислительной среды и с третьими информационными входами группы полных одноразрядных сумматоров.

Сущность изобретения заключается в реализации следующего способа конвейерного накапливающего суммирования чисел Ak,i по модулям Pk, где (i=1, 2, 3,…) - такты работы устройства, k - количество потоков чисел.

Поступающие на вход конвейерного накапливающего сумматора неотрицательные целые числа Ak,i (i=1, 2, 3,…), 0 ≤ Ak,i < Pk, где Pk ≥ 2 - произвольное натуральное число, называемое модулем, потактово суммируются в k раздельных потоках с числами, записанными в его памяти на предыдущих тактах, образуя k независимых выходных последовательностей чисел Sk,i, причем 0 ≤ Sk,i < Pk. При этом

Sk,i  (∑ Ak,(i−k+1)) mod Pk, i=1, 2, 3,… ,(1)

(∑ Ak,(i−k+1)) mod Pk, i=1, 2, 3,… ,(1)

где Ak,(i−k+1) = 0 при (i−k+1) ≤ 0.

Накапливающее суммирование может быть реализовано рекуррентным способом, тогда выражение (1) может быть записано в следующем виде:

Sk,i  (Sk,(i−k) + Ak,(i−k+1)) mod Pk, i=1, 2, 3,… ,(2)

(Sk,(i−k) + Ak,(i−k+1)) mod Pk, i=1, 2, 3,… ,(2)

при этом считаем, что Sk,(i−k) = 0 при (i−k) ≤ (k-1), а Sk,i = 0 при i ≤ (k-1).

В качестве сумматора в конвейерном режиме суммирования может выступать однородная вычислительная среда [2, фиг. 3] со структурой ячеек, представленной в [3, фиг. 3].

Выполняя с помощью одной однородной вычислительной среды операцию суммирования (Sk,(i−k) + Ak,(i−k+1)), а с помощью второй однородной вычислительной среды операцию (Sk,(i−k) + Ak,(i−k+1)) - Pk, можно по результатам вычисления второй однородной вычислительной среды выбирать корректное значение в выражении (2) для суммы Sk,i.

Краткое описание чертежей.

Сущность изобретения поясняется чертежами.

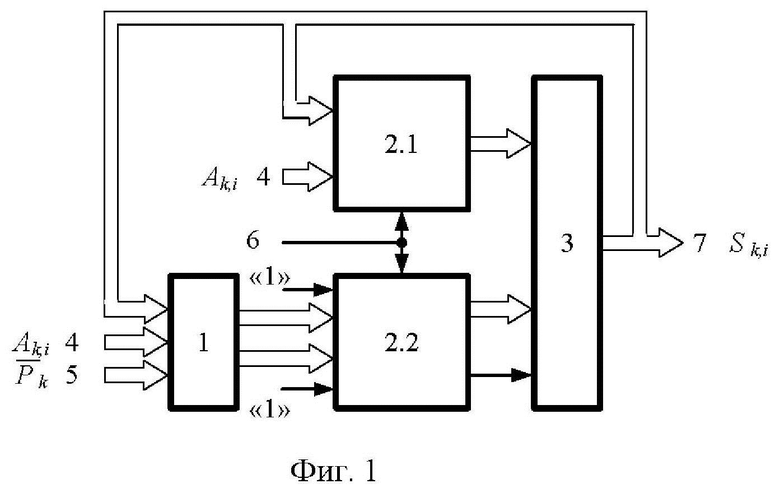

На фиг. 1 представлена схема конвейерного накапливающего сумматора по произвольным модулям. Конвейерный накапливающий сумматор по произвольным модулям содержит группу полных одноразрядных сумматоров 1, первую однородную вычислительную среду 2.1 разрядности n, где n - разрядность обрабатываемых чисел, вторую однородную вычислительную среду 2.2 разрядности (n+1), мультиплексор 3 разрядности n, первые 4 и вторые 5 информационные входы устройства, тактовый вход 6 и информационные выходы 7 устройства. Первые информационные входы 4 устройства соединены с первыми информационными входами первой однородной вычислительной среды 2.1 и с первыми информационными входами группы полных одноразрядных сумматоров 1. Вторые информационные входы 5 устройства соединены со вторыми информационными входами группы полных одноразрядных сумматоров 1. Первые информационные выходы группы полных одноразрядных сумматоров 1 соединены с младшими n разрядами первых информационных входов второй однородной вычислительной среды 2.2, вторые информационные выходы соединены со вторыми информационными входами второй однородной вычислительной среды 2.2 со сдвигом на один разряд в сторону старшего. Тактовый вход устройства 6 соединен со входами синхронизации первой 2.1 и второй 2.2 однородной вычислительной среды. Младшие n разрядов информационных выходов второй однородной вычислительной среды 2.2 соединены со вторыми информационными входами мультиплексора 3, а выход разряда переноса соединен с управляющим входом мультиплексора 3, первые информационные входы которого соединены с информационными выходами первой однородной вычислительной среды 2.1. Информационные выходы мультиплексора 3 соединены с информационными выходами устройства 7, со вторыми информационными входами первой однородной вычислительной среды 2.1 и с третьими информационными входами группы полных одноразрядных сумматоров 1. На (n+1)-й разряд первых информационных входов и на первый разряд вторых информационных входов второй вычислительной среды 2.2 подается сигнал логической единицы. На первые информационные входы 4 устройства подается поток кодов чисел A k,i, j=1, 2, 3, …, на вторые информационные входы 5 устройства подается поток инверсных кодов модулей Pk. С информационных выходов 7 устройства снимаются коды суммы S k, i чисел Ak, i по модулю P k.

Осуществление изобретения.

Конвейерный накапливающий сумматор по произвольным модулям работает следующим образом (см. Фиг. 1).

В исходном состоянии все ячейки первой 2.1 и второй 2.2 однородной вычислительной среды обнулены.

На тактовый вход устройства 6 поступают тактовые импульсы i=1, 2, 3, …, . На первые информационные входы 4 устройства с каждым тактовым импульсом подаются числа Ak,i, для которых необходимо вычислить сумму Sk,i по модулю Pk. На вторые информационные входы 5 устройства подается инверсный код модуля Pk. Сумма Sk,i по модулю Pk чисел Ak,i снимается с информационных выходов 7 устройства.

Длина конвейера k определяет его латентный период работы и зависит от структуры однородных вычислительных сред 2.1 и 2.2.

На первом такте с первых информационных входов 4 устройства на первые информационные входы первой однородной вычислительной среды 2.1 поступит число A1,1, а на ее вторые информационные входы с выхода мультиплексора 3 поступит значение S1,0, равное, в соответствии с (2), нулю. В первый столбец однородной вычислительной среды 2.1 запишется вектор значений, зависящий от структуры построения однородной вычислительной среды 2.1 и значений чисел A1,1 и S1,0, который можно определить, как первую частичную сумму A1,1 и S1,0. Полная сумма этих чисел появится на информационных выходах однородной вычислительной среды 2.1 через k тактов работы устройства. Одновременно число A1,1 поступает на первые информационные входы группы полных одноразрядных сумматоров 1, на вторые информационные входы которых со вторых информационных входов 5 устройства подается инверсный код значения модуля P1, а на третьи информационные входы с выхода мультиплексора 3 подается нулевое значение S1,0. На первых и вторых информационных выходах группы полных одноразрядных сумматоров 1 будут формироваться числа Xi и Yi соответственно. При этом в соответствии с правилами сложения разряды чисел Xi и Yi будут вычислены как:

xj,i=aj,i  bj,i

bj,i  pj,i, (3)

pj,i, (3)

yj,i=aj,ibj,i bj,ipj,i

bj,ipj,i aj,ipj,i. (4)

aj,ipj,i. (4)

где j = 0, 1, 2, 3 - номер разряда в двоичном представлении чисел;

i =1, 2, 3, …, - номер такта работы устройства;

xj,i - j-ый разряд i-го числа Xi,

yj,i - j-ый разряд i-го числа Yi;

aj,i - j-ый разряд i-го числа Ak,i;

bj,i - j-ый разряд i-го числа Sk,i;

pj,i - j-ый разряд числа Pk на i-ом такте;

символ  означает суммирование по модулю два;

означает суммирование по модулю два;

символ  означает логическую дизъюнкцию.

означает логическую дизъюнкцию.

Тогда вычисление значения ((Sk,(i−k) + Ak,(i−k+1)) - Pk),состоящего из трех операндов, может быть сведено к вычислению значения (2n+1 +Xj +2 Yj + 1), состоящего из двух операндов и двух констант, с увеличением на одну единицу разрядности вычислителя.

Числа X1 и Y1 поступают на первые и вторые информационные входы второй однородной вычислительной среды 2.2. В первый столбец второй однородной вычислительной среды 2.2 по окончании первого тактового импульса запишется вектор значений, зависящий от структуры построения однородной вычислительной среды 2.2 и значений чисел X1 и Y1. Полное значение выражения ((A1,1 + S1,0) - P1) появится на информационных выходах однородной вычислительной среды 2.2 через k тактов работы устройства.

В общем случае, если (Sk,(i−k) + Ak,(i−k+1))  Pk, то на выходе переноса второй однородной вычислительной среды 2.2 образуется сигнал переноса, который поступит на управляющий вход мультиплексора 3 и скоммутирует вторые информационные входы на информационные выходы и на информационных выходах мультиплексора 3 появится разность (Sk,(i−k) + Ak,(i−k+1)) - Pk, а иначе на его информационных выходах появится сумма (Sk,(i−k) + Ak,(i−k+1)). Результат Sk,i поступит на информационные выходы устройства 7, на вторые информационные входы первой вычислительной среды 2.1 и на третьи информационные входы группы полных одноразрядных сумматоров 1. На следующих тактах работа устройства продолжится аналогичным образом.

Pk, то на выходе переноса второй однородной вычислительной среды 2.2 образуется сигнал переноса, который поступит на управляющий вход мультиплексора 3 и скоммутирует вторые информационные входы на информационные выходы и на информационных выходах мультиплексора 3 появится разность (Sk,(i−k) + Ak,(i−k+1)) - Pk, а иначе на его информационных выходах появится сумма (Sk,(i−k) + Ak,(i−k+1)). Результат Sk,i поступит на информационные выходы устройства 7, на вторые информационные входы первой вычислительной среды 2.1 и на третьи информационные входы группы полных одноразрядных сумматоров 1. На следующих тактах работа устройства продолжится аналогичным образом.

Таким образом, на информационных выходах 7 устройства в соответствии с выражением (2) на каждом такте работы устройства будут появляться значения Sk,i, образующие k независимых потоков накапливающих сумм входных чисел Ak,i по k различным модулям Pk.

Изобретение позволяет расширить функциональные возможности прототипа при конвейерной обработке информации за счет реализации операции конвейерного накапливающего суммирования.

Источники информации.

1. Патент на изобретение RU 2310223 С1. МПК G06F 7/72 (2006.01). Однородная вычислительная структура для выполнения операций по заданному модулю. Опубликован 10.11.2007. Бюл. № 31.

2. Патент на изобретение RU 2477513 С1. МПК G06F 7/72 (2006.01). Ячейка однородной вычислительной среды, однородная вычислительная среда и устройство для конвейерных арифметических вычислений по заданному модулю. Опубликован 10.03.2013. Бюл. № 7.

3. Патент на изобретение RU 2805939 С1. МПК G06F 7/72 (2006.01). Устройство для конвейерного суммирования чисел по произвольному модулю. Опубликован 24.10.2023. Бюл. № 30.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный накапливающий сумматор по произвольным модулям | 2024 |

|

RU2837596C1 |

| УСТРОЙСТВО ДЛЯ КОНВЕЙЕРНОГО СУММИРОВАНИЯ ЧИСЕЛ ПО ПРОИЗВОЛЬНОМУ МОДУЛЮ | 2023 |

|

RU2805939C1 |

| Устройство для деления чисел | 1990 |

|

SU1795456A1 |

| ДВУХКАНАЛЬНЫЙ НАКАПЛИВАЮЩИЙ СУММАТОР ПО МОДУЛЮ | 2024 |

|

RU2823898C1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ НАТУРАЛЬНОГО ЛОГАРИФМА КОМПЛЕКСНОГО ЧИСЛА | 1991 |

|

RU2010312C1 |

| НАКАПЛИВАЮЩИЙ СУММАТОР ГРУППОВОЙ СТРУКТУРЫ ПО ПРОИЗВОЛЬНОМУ МОДУЛЮ С ПОСЛЕДОВАТЕЛЬНЫМ ПЕРЕНОСОМ | 2024 |

|

RU2833212C1 |

| Конвейерное вычислительное устройство | 1989 |

|

SU1693601A1 |

| КОНВЕЙЕРНЫЙ ФОРМИРОВАТЕЛЬ ОСТАТКОВ ПО ПРОИЗВОЛЬНОМУ МОДУЛЮ | 2022 |

|

RU2791440C1 |

| Конвейерный вычислитель | 2023 |

|

RU2797163C1 |

| КОНВЕЙЕРНЫЙ ВЫЧИСЛИТЕЛЬ | 2023 |

|

RU2804380C1 |

Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных устройствах конвейерного типа для построения однородных вычислительных сред, в устройствах цифровой обработки сигналов, в криптографических приложениях, а также при построении многоканальных синтезаторов частот. Техническим результатом, обеспечиваемым приведенной совокупностью признаков, является расширение функциональных возможностей устройства при конвейерной обработке информации за счет реализации операции конвейерного накапливающего суммирования. Технический результат достигается за счет того, что конвейерный накапливающий сумматор по произвольным модулям содержит группу полных одноразрядных сумматоров, первую однородную вычислительную среду разрядности n, где n - разрядность обрабатываемых чисел, вторую однородную вычислительную среду разрядности (n+1), мультиплексор разрядности n, первые и вторые информационные входы, тактовый вход и информационные выходы с соответствующими связями. 1 ил.

Конвейерный накапливающий сумматор по произвольным модулям, содержащий первую однородную вычислительную среду разрядности n, вторую однородную вычислительную среду разрядности (n+1), группу полных одноразрядных сумматоров и мультиплексор разрядности n, где n - разрядность обрабатываемых чисел, первые и вторые информационные входы, информационные выходы и тактовый вход, который соединен со входом синхронизации первой и второй однородных вычислительных сред, причем первые информационные входы устройства соединены с первыми информационными входами первой однородной вычислительной среды и с первыми информационными входами группы полных одноразрядных сумматоров, вторые информационные входы устройства соединены со вторыми информационными входами группы полных одноразрядных сумматоров, первые информационные выходы которой соединены с младшими n разрядами первых информационных входов второй однородной вычислительной среды, вторые информационные выходы соединены со вторыми информационными входами второй однородной вычислительной среды со сдвигом на один разряд в сторону старшего, на (n+1)-й разряд первых информационных входов и на первый разряд вторых информационных входов второй вычислительной среды подается сигнал логической единицы, младшие n разрядов информационных выходов второй однородной вычислительной среды соединены со вторыми информационными входами мультиплексора, а выход разряда переноса соединен с управляющим входом мультиплексора, первые информационные входы которого соединены с информационными выходами первой однородной вычислительной среды, а информационные выходы соединены с информационными выходами устройства, отличающийся тем, что информационные выходы мультиплексора соединены со вторыми информационными входами первой однородной вычислительной среды и с третьими информационными входами группы полных одноразрядных сумматоров.

| ЯЧЕЙКА ОДНОРОДНОЙ ВЫЧИСЛИТЕЛЬНОЙ СРЕДЫ, ОДНОРОДНАЯ ВЫЧИСЛИТЕЛЬНАЯ СРЕДА И УСТРОЙСТВО ДЛЯ КОНВЕЙЕРНЫХ АРИФМЕТИЧЕСКИХ ВЫЧИСЛЕНИЙ ПО ЗАДАННОМУ МОДУЛЮ | 2011 |

|

RU2477513C1 |

| ФИЛЬТР-ПРЕСС ДЛЯ ОЧИСТКИ ГАЗА ОТ ПЫЛИ | 0 |

|

SU202071A1 |

| ОДНОРОДНАЯ ВЫЧИСЛИТЕЛЬНАЯ СТРУКТУРА ДЛЯ ВЫПОЛНЕНИЯ ОПЕРАЦИЙ ПО ЗАДАННОМУ МОДУЛЮ | 2005 |

|

RU2310223C2 |

| WO 2014143042 A1, 18.09.2014. | |||

Авторы

Даты

2024-07-30—Публикация

2024-03-01—Подача