Изобретение относится к вычислительной технике и может быть использовано при построении средств автоматики, функциональных узлов систем управления и др.

Известны мажоритарные модули [1,2], которые содержат мажоритарные элементы и реализуют мажоритарную функцию семи аргументов - входных двоичных сигналов.

К причине, препятствующей достижению указанного ниже технического результата при использовании известных мажоритарных модулей, относятся ограниченные функциональные возможности, обусловленные тем, что не обеспечивается реализация мажоритарной функции одиннадцати аргументов - входных двоичных сигналов.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является принятый за прототип мажоритарный модуль [3], который содержит два элемента исключающее ИЛИ, четыре мажоритарных элемента и реализует мажоритарную функцию семи аргументов - входных двоичных сигналов.

К причине, препятствующей достижению указанного ниже технического результата при использовании прототипа, относятся ограниченные функциональные возможности, обусловленные тем, что не обеспечивается реализация мажоритарной функции одиннадцати аргументов - входных двоичных сигналов.

Техническим результатом изобретения является расширение функциональных возможностей за счет обеспечения реализации мажоритарной функции одиннадцати аргументов - входных двоичных сигналов.

Указанный технический результат при осуществлении изобретения достигается тем, что в мажоритарном модуле, содержащем два элемента исключающее ИЛИ и четыре мажоритарных элемента, i-й ( ) вход j-го (

) вход j-го ( ) мажоритарного элемента и i-й вход мажоритарного модуля соединены соответственно с i-ым входом j-го элемента исключающее ИЛИ и i-ым входом первого мажоритарного элемента, особенность заключается в том, что в него дополнительно введены четыре элемента исключающее ИЛИ, пять мажоритарных элементов и два элемента НЕ, i-й вход k-го (

) мажоритарного элемента и i-й вход мажоритарного модуля соединены соответственно с i-ым входом j-го элемента исключающее ИЛИ и i-ым входом первого мажоритарного элемента, особенность заключается в том, что в него дополнительно введены четыре элемента исключающее ИЛИ, пять мажоритарных элементов и два элемента НЕ, i-й вход k-го ( ), второй вход (

), второй вход ( )-го и выход j-го мажоритарных элементов соединены соответственно с i-ым входом k-го элемента исключающее ИЛИ, выходом (

)-го и выход j-го мажоритарных элементов соединены соответственно с i-ым входом k-го элемента исключающее ИЛИ, выходом ( )-го и первым входом (

)-го и первым входом ( )-го мажоритарных элементов, третий вход и выход (

)-го мажоритарных элементов, третий вход и выход ( )-го мажоритарного элемента, вход и выход j-го элемента НЕ соединены соответственно с выходом (

)-го мажоритарного элемента, вход и выход j-го элемента НЕ соединены соответственно с выходом ( )-го и (

)-го и ( )-ым входом девятого мажоритарных элементов, выходом j-го и вторым входом (

)-ым входом девятого мажоритарных элементов, выходом j-го и вторым входом ( )-го элементов исключающее ИЛИ, первый, третий входы (

)-го элементов исключающее ИЛИ, первый, третий входы ( )-го и второй вход (

)-го и второй вход ( )-го мажоритарных элементов соединены соответственно с выходами (

)-го мажоритарных элементов соединены соответственно с выходами ( )-го, (

)-го, ( )-го и выходом j-го элементов исключающее ИЛИ, а i-й вход второго, второй вход седьмого и первый, третий входы (

)-го и выходом j-го элементов исключающее ИЛИ, а i-й вход второго, второй вход седьмого и первый, третий входы ( )-го мажоритарных элементов соединены соответственно с (

)-го мажоритарных элементов соединены соответственно с ( )-ым, одиннадцатым и (

)-ым, одиннадцатым и ( )-ым, (

)-ым, ( )-ым входами мажоритарного модуля, выход которого соединен с выходом девятого мажоритарного элемента.

)-ым входами мажоритарного модуля, выход которого соединен с выходом девятого мажоритарного элемента.

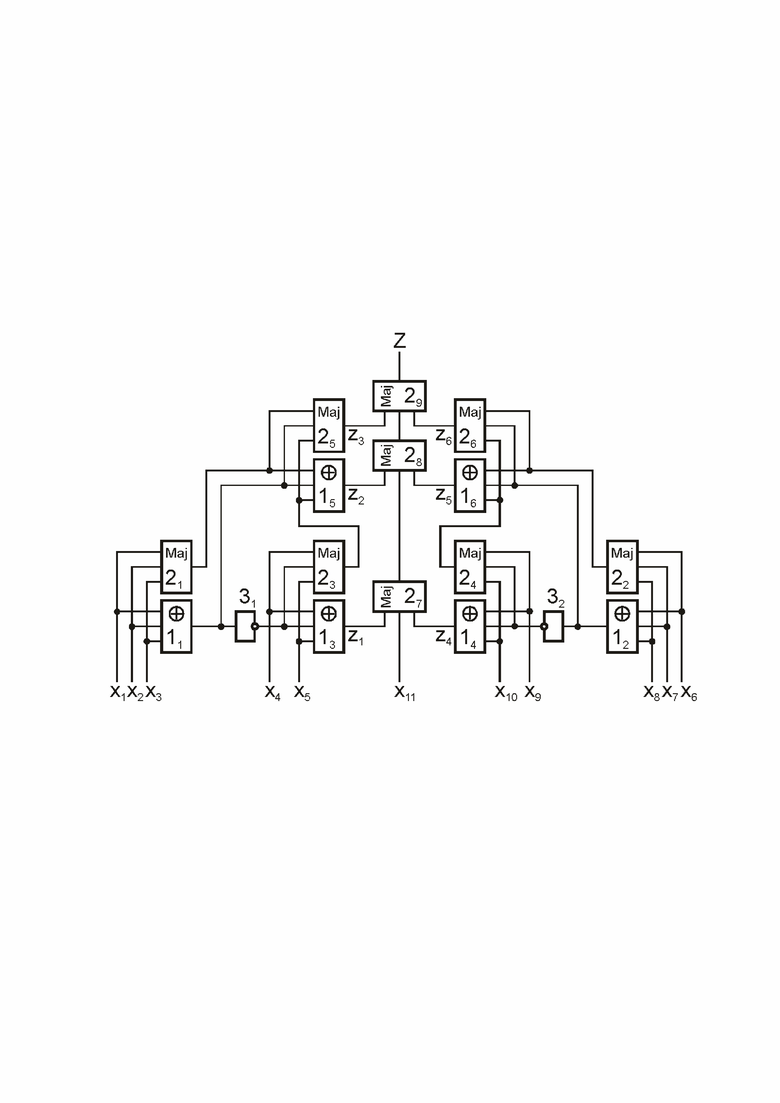

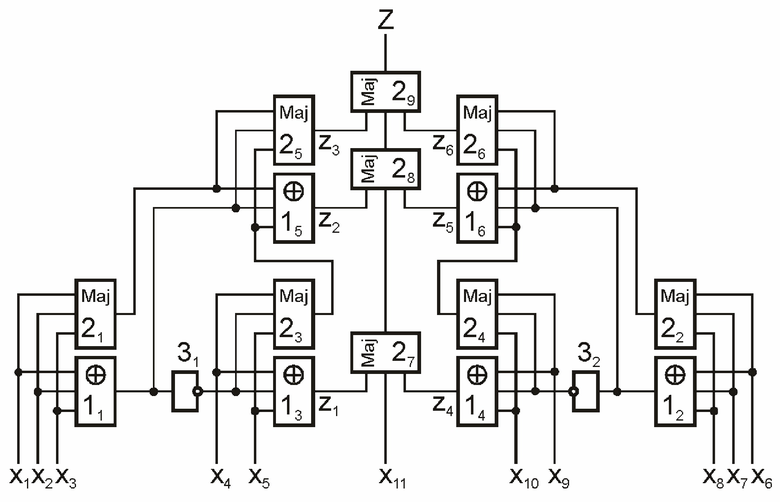

На чертеже представлена схема предлагаемого мажоритарного модуля.

Мажоритарный модуль содержит элементы исключающее ИЛИ 11,…,16, мажоритарные элементы 21,…,29 и элементы НЕ 31, 32, причем i-й ( ) вход и выход элемента 2j (

) вход и выход элемента 2j ( ) соединены соответственно с i-ым входом элемента 1j и первым входом элемента 2j+4, i-й вход элемента 2k (

) соединены соответственно с i-ым входом элемента 1j и первым входом элемента 2j+4, i-й вход элемента 2k ( ) и второй вход элемента 2j+7 подключены соответственно к i-му входу элемента 1k и выходу элемента 2j+6, третий вход и выход элемента 2j+4, вход и выход элемента 3j соединены соответственно с выходом элемента 2j+2 и (

) и второй вход элемента 2j+7 подключены соответственно к i-му входу элемента 1k и выходу элемента 2j+6, третий вход и выход элемента 2j+4, вход и выход элемента 3j соединены соответственно с выходом элемента 2j+2 и ( )-ым входом элемента 29, выходом элемента 1j и вторым входом элемента 1j+2, первый, третий входы элемента 2j+6 и второй вход элемента 2j+4 подключены соответственно к выходам элементов 12×j+1, 12×j+2 и выходу элемента 1j, а i-й вход элемента 21, i-й вход элемента 22, второй вход элемента 27 и первый, третий входы элемента 2j+2 соединены соответственно с i-ым, (

)-ым входом элемента 29, выходом элемента 1j и вторым входом элемента 1j+2, первый, третий входы элемента 2j+6 и второй вход элемента 2j+4 подключены соответственно к выходам элементов 12×j+1, 12×j+2 и выходу элемента 1j, а i-й вход элемента 21, i-й вход элемента 22, второй вход элемента 27 и первый, третий входы элемента 2j+2 соединены соответственно с i-ым, ( )-ым, одиннадцатым и (

)-ым, одиннадцатым и ( )-ым, (

)-ым, ( )-ым входами мажоритарного модуля, выход которого подключен к выходу элемента 29.

)-ым входами мажоритарного модуля, выход которого подключен к выходу элемента 29.

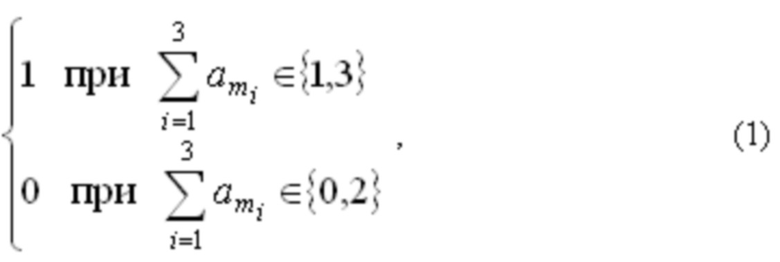

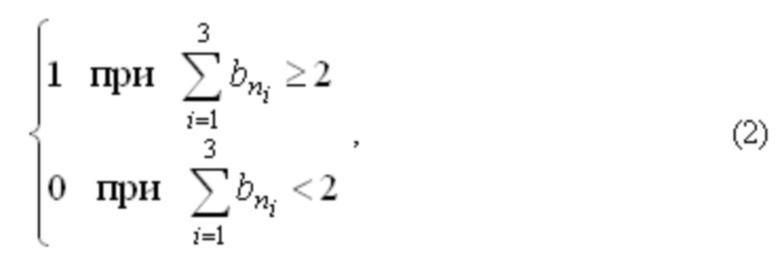

Работа предлагаемого мажоритарного модуля осуществляется следующим образом. На его первый,…,одиннадцатый входы подаются соответственно двоичные сигналы  . На выходах элементов 1m (

. На выходах элементов 1m ( ), 2n (

), 2n ( ) имеем

) имеем

где  - сигналы на их i-ых входах. В представленных ниже табл.1 и табл.2 приведены соответственно значения внутренних сигналов

- сигналы на их i-ых входах. В представленных ниже табл.1 и табл.2 приведены соответственно значения внутренних сигналов  (

( ) предлагаемого мажоритарного модуля, полученные с учетом (1), (2) для всех возможных наборов значений сигналов

) предлагаемого мажоритарного модуля, полученные с учетом (1), (2) для всех возможных наборов значений сигналов  , и значения его выходного сигнала Z, полученные с учетом (2) для всех возможных наборов значений сигналов

, и значения его выходного сигнала Z, полученные с учетом (2) для всех возможных наборов значений сигналов  .

.

Согласно данным, приведенным в табл.1, табл.2, имеем

,

,

где  есть мажоритарная функция одиннадцати аргументов

есть мажоритарная функция одиннадцати аргументов  .

.

Вышеизложенные сведения позволяют сделать вывод, что предлагаемый мажоритарный модуль обладает более широкими по сравнению с прототипом функциональными возможностями, так как реализует мажоритарную функцию одиннадцати аргументов - входных двоичных сигналов.

Источники информации:

1. Патент РФ 2700554, кл. H03K19/23, 2019 г.

2. Патент РФ 2757819, кл. H03K19/23, 2021 г.

3. Патент РФ 2747107, кл. G06F7/57, 2021 г.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЛОГИЧЕСКИЙ МОДУЛЬ | 2023 |

|

RU2812687C1 |

| МАЖОРИТАРНЫЙ МОДУЛЬ | 2022 |

|

RU2789750C1 |

| ПОРОГОВЫЙ МОДУЛЬ | 2023 |

|

RU2812688C1 |

| ПОРОГОВЫЙ МОДУЛЬ | 2023 |

|

RU2812760C1 |

| МАЖОРИТАРНЫЙ МОДУЛЬ | 2023 |

|

RU2812683C1 |

| МАЖОРИТАРНЫЙ МОДУЛЬ | 2022 |

|

RU2789728C1 |

| ЛОГИЧЕСКИЙ МОДУЛЬ | 2023 |

|

RU2809482C1 |

| МАЖОРИТАРНЫЙ МОДУЛЬ | 2023 |

|

RU2803610C1 |

| ЛОГИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ | 2023 |

|

RU2803625C1 |

| ЛОГИЧЕСКИЙ МОДУЛЬ | 2022 |

|

RU2789730C1 |

Мажоритарный модуль предназначен для реализации мажоритарной функции, аргументами которой являются входные двоичные сигналы, и может быть использован в системах цифровой вычислительной техники как средство предварительной обработки информации. Мажоритарный модуль содержит шесть элементов исключающее ИЛИ (11,…,16), девять мажоритарных элементов (21,…,29) и два элемента НЕ (31, 32). За счет этих элементов и новой схемы их соединения обеспечивается реализация указанной функции для одиннадцати аргументов. В результате расширены функциональные возможности мажоритарного модуля. 1 ил., 2 табл.

Мажоритарный модуль, содержащий два элемента исключающее ИЛИ и четыре мажоритарных элемента, причем i-й ( ) вход j-го (

) вход j-го ( ) мажоритарного элемента и i-й вход мажоритарного модуля соединены соответственно с i-м входом j-го элемента исключающее ИЛИ и i-м входом первого мажоритарного элемента, отличающийся тем, что в него дополнительно введены четыре элемента исключающее ИЛИ, пять мажоритарных элементов и два элемента НЕ, i-й вход k-го (

) мажоритарного элемента и i-й вход мажоритарного модуля соединены соответственно с i-м входом j-го элемента исключающее ИЛИ и i-м входом первого мажоритарного элемента, отличающийся тем, что в него дополнительно введены четыре элемента исключающее ИЛИ, пять мажоритарных элементов и два элемента НЕ, i-й вход k-го ( ), второй вход

), второй вход  -го и выход j-го мажоритарных элементов соединены соответственно с i-м входом k-го элемента исключающее ИЛИ, выходом (

-го и выход j-го мажоритарных элементов соединены соответственно с i-м входом k-го элемента исключающее ИЛИ, выходом ( )-го и первым входом (

)-го и первым входом ( )-го мажоритарных элементов, третий вход и выход (

)-го мажоритарных элементов, третий вход и выход ( )-го мажоритарного элемента, вход и выход j-го элемента НЕ соединены соответственно с выходом (

)-го мажоритарного элемента, вход и выход j-го элемента НЕ соединены соответственно с выходом ( )-го и

)-го и  -м входом девятого мажоритарных элементов, выходом j-го и вторым входом (

-м входом девятого мажоритарных элементов, выходом j-го и вторым входом ( )-го элементов исключающее ИЛИ, первый, третий входы (

)-го элементов исключающее ИЛИ, первый, третий входы ( )-го и второй вход (

)-го и второй вход ( )-го мажоритарных элементов соединены соответственно с выходами

)-го мажоритарных элементов соединены соответственно с выходами  -го, (

-го, ( )-го и выходом j-го элементов исключающее ИЛИ, а i-й вход второго, второй вход седьмого и первый, третий входы (

)-го и выходом j-го элементов исключающее ИЛИ, а i-й вход второго, второй вход седьмого и первый, третий входы ( )-го мажоритарных элементов соединены соответственно с (

)-го мажоритарных элементов соединены соответственно с ( )-м, одиннадцатым и (

)-м, одиннадцатым и ( )-м, (

)-м, ( )-м входами мажоритарного модуля, выход которого соединен с выходом девятого мажоритарного элемента.

)-м входами мажоритарного модуля, выход которого соединен с выходом девятого мажоритарного элемента.

| МАЖОРИТАРНЫЙ МОДУЛЬ | 2021 |

|

RU2776922C1 |

| МАЖОРИТАРНЫЙ МОДУЛЬ | 2020 |

|

RU2757819C1 |

| US 2002116683 A1, 22.08.2002 | |||

| US 2017024294 A1, 26.01.2017. | |||

Авторы

Даты

2023-12-07—Публикация

2023-03-22—Подача