Изобретение относится к вычислительной технике и может быть использовано для построения средств автоматики, функциональных узлов систем управления и др.

Известны логические модули (см., например, патент РФ 2709669, кл. G06F7/57, 2019г.), которые содержат элементы исключающее ИЛИ, мажоритарные элементы и с помощью константной настройки реализуют любую из простых симметричных булевых функций

К причине, препятствующей достижению указанного ниже технического результата при использовании известных логических модулей, относятся ограниченные функциональные возможности, обусловленные тем, что не обеспечивается реализация любой из функций

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является принятый за прототип логический модуль (патент РФ 2776920, кл. G06F7/57, 2022г.), который содержит элементы исключающее ИЛИ, мажоритарные элементы и с помощью константной настройки реализует любую из простых симметричных булевых функций

К причине, препятствующей достижению указанного ниже технического результата при использовании прототипа, относится схемная сложность, обусловленная тем, что прототип имеет три настроечных входа.

Техническим результатом изобретения является упрощение схемы логического модуля за счет уменьшения количества настроечных входов при сохранении функциональных возможностей и элементного базиса прототипа.

Указанный технический результат при осуществлении изобретения достигается тем, что в логическом модуле, содержащем два элемента исключающее ИЛИ и шесть мажоритарных элементов, i-й (

На чертеже представлена схема предлагаемого логического модуля.

Логический модуль содержит мажоритарные элементы 11,…,17 и элементы исключающее или 21, 22, причем i-й (

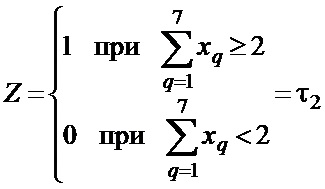

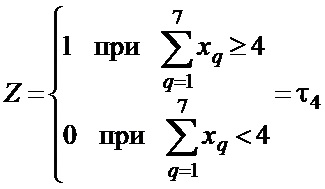

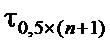

Работа предлагаемого логического модуля осуществляется следующим образом. На его первый,…,седьмой информационные и первый, второй настроечные входы подаются соответственно двоичные сигналы

Таблица 1

Таблица 2

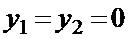

Если

где

Вышеизложенные сведения позволяют сделать вывод, что предлагаемый логический модуль построен в элементном базисе прототипа и с помощью константной настройки реализует любую из простых симметричных булевых функций

| название | год | авторы | номер документа |

|---|---|---|---|

| ЛОГИЧЕСКИЙ МОДУЛЬ | 2023 |

|

RU2809209C1 |

| ЛОГИЧЕСКИЙ МОДУЛЬ | 2013 |

|

RU2542920C2 |

| ЛОГИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ | 2021 |

|

RU2768627C1 |

| ЛОГИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ | 2022 |

|

RU2787338C1 |

| ЛОГИЧЕСКИЙ МОДУЛЬ | 2021 |

|

RU2778678C1 |

| ЛОГИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ | 2023 |

|

RU2803625C1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ СИММЕТРИЧЕСКИХ БУЛЕВЫХ ФУНКЦИЙ | 1992 |

|

RU2047894C1 |

| ЛОГИЧЕСКИЙ МОДУЛЬ | 2023 |

|

RU2812687C1 |

| Многофункциональный логический модуль | 1985 |

|

SU1259243A1 |

| ЛОГИЧЕСКИЙ МОДУЛЬ | 2022 |

|

RU2789730C1 |

Изобретение относится к логическому модулю для реализации простых симметричных булевых функций. Технический результат заключается в упрощении схемы логического модуля за счет уменьшения количества настроечных входов при сохранении функциональных возможностей и элементного базиса прототипа. Логический модуль содержит семь мажоритарных элементов, два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и имеет два настроечных входа. За счет указанных элементов и новой схемы их соединения обеспечивается упрощение схемы логического модуля и реализация любой из простых симметричных булевых функций

Логический модуль, предназначенный для реализации простых симметричных булевых функций, содержащий два элемента исключающее ИЛИ и шесть мажоритарных элементов, причем i-й (

| ЛОГИЧЕСКИЙ МОДУЛЬ | 2021 |

|

RU2776920C1 |

| БУКВОПЕЧАТАЮЩИЙ ТЕЛЕГРАФНЫЙ АППАРАТ ТИПА ПИШУЩЕЙ МАШИНЫ | 1926 |

|

SU5179A1 |

| ЛОГИЧЕСКИЙ МОДУЛЬ | 2012 |

|

RU2472209C1 |

| 1972 |

|

SU411993A1 | |

| CN 104301089 B, 27.04.2018. | |||

Авторы

Даты

2023-12-12—Публикация

2023-06-15—Подача